# EXPLOITING VOLTAGE DRIVEN SWITCHING OF FERROMAGNETS FOR NOVEL SPIN BASED DEVICES AND CIRCUITS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Akhilesh Jaiswal

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Kaushik Roy, Chair

School of Electrical and Computer Engineering

- Dr. Anand Raghunathan School of Electrical and Computer Engineering

- Dr. Dinesh Somasekhar

Intel Corporation

Dr. Vijay Raghunathan School of Electrical and Computer Engineering

## Approved by:

Dr. Pedro Irazoqui

Head of the School Graduate Program

Dedicated to H. H. Sri Sai Narayan Baba and to my Parents

#### ACKNOWLEDGMENTS

I would like to express my sincerest gratitude to my advisor Prof. Kaushik Roy for being a 'Mentor', a 'Teacher' and an 'Inspiration'. His uncanny ability to see through the details while not losing the sight on the big-picture has been instrumental in shaping my perspective to approach a given research problem, in general. He has always been keen to listen to new ideas and give pertinent suggestions. His *mentorship through questions* has been very effective in guiding me toward the right direction while still allowing me to think independently and figure out the specific details. Needless to say, without him in the background, this research would not have been possible in the first place.

I would also like to thank my doctoral dissertation committee: Prof. Anand Raghunathan, Dr. Dinesh Somashekhar and Prof. Vijay Raghunathan for their valuable feedback that have helped me improve the quality of my research work. My sincerest thanks to my undergraduate mentors Prof. Ramchandra Manthalkar and Prof. Suhas Gajre for believing in my abilities and for their constant encouragement. It was by chance I stumbled upon them and ended up having lifelong 'Role Models' to look upon. I would also thank Dr. Xuanyao Fong for introducing me to spin device physics and helping me develop the simulation models. I would also take this opportunity to thank my manager and mentor Dr. Ajey Jacob during my internship at Globalfoundries Research Lab. I am grateful for his encouragement to motivate me to think and come up with new ideas and for his help to develop those ideas in formal research projects.

Finally, a big thanks to my collaborators and fellow lab-mates at Nano-electronics Research Lab, Purdue for making my stay at Purdue enjoyable. I would also like to thank my friends Akshay Pohekar, Amol More, Bharat Shinde, Harshad Surana and many others, who I might have missed, for all the smiles and laughters. To my parents and sisters and their families my sincerest thanks for their love, support and patience.

## TABLE OF CONTENTS

|    |       |          | F                                                                                  | Page  |

|----|-------|----------|------------------------------------------------------------------------------------|-------|

| LI | ST O  | F TAB    | LES                                                                                | ix    |

| LI | ST O  | F FIGU   | URES                                                                               | х     |

| A] | BSTR  | ACT      | · · · · · · · · · · · · · · · · · · ·                                              | cviii |

| 1  | Intro | oduction | n and Motivation                                                                   | 1     |

| 2  | VCN   | /IA Phy  | rsics and Modeling                                                                 | 5     |

|    | 2.1   | Intro    | duction to VCMA mechanism                                                          | 5     |

|    |       | 2.1.1    | VCMA mechanism: Voltage asymmetry                                                  | 5     |

|    |       | 2.1.2    | VCMA mechanism: Precessional switching                                             | 7     |

|    | 2.2   | Device   | e Modeling                                                                         | 9     |

|    |       | 2.2.1    | Magnetization Dynamics based on stochastic LLGS equation including the VCMA effect | 9     |

|    |       | 2.2.2    | MTJ Resistance model                                                               | 10    |

|    |       | 2.2.3    | Self-Consistent SPICE Compatible Magnetization Dynamics and<br>Resistance Model    | 11    |

| 3  |       | ,        | nemory Stateful Vector Logic Operations based on Voltage Con-<br>netic Anisotropy  | 13    |

|    | 3.1   | Intro    | duction and Related Work                                                           | 13    |

|    | 3.2   | Prope    | osed <i>in-situ</i> , in-memory Stateful Vector Logic Operations                   | 16    |

|    |       | 3.2.1    | Stateful vector IMP gates                                                          | 16    |

|    |       | 3.2.2    | Stateful parallel NOT gates                                                        | 20    |

|    |       | 3.2.3    | Other Logic Gates                                                                  | 23    |

|    |       | 3.2.4    | Stateful XOR Gate                                                                  | 24    |

|    | 3.3   | Result   | 55                                                                                 | 26    |

|    | 3.4   | Summ     | ary                                                                                | 29    |

| 4  | Mag   | neto-ele | ectric Switching Mechanism and Modeling                                            | 30    |

## Page

|   | 4.1  | Introduction to Magneto-electric Switching of Ferro-magnets                                                                           | 30 |

|---|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 4.2  | Modeling and Simulation                                                                                                               | 32 |

|   | 4.3  | Device Characteristics                                                                                                                | 37 |

|   |      | 4.3.1 Scalability                                                                                                                     | 37 |

|   |      | 4.3.2 Switching Speed                                                                                                                 | 38 |

| 5 | A St | cochastic Leaky-Integrate-Fire Neuron using Magneto-electric Switching                                                                | 39 |

|   | 5.1  | Introduction and Related Work                                                                                                         | 39 |

|   | 5.2  | Proposed Stochastic Leaky-Integrate-Fire Neuron                                                                                       | 41 |

|   | 5.3  | SNN Topology for pattern recognition                                                                                                  | 47 |

|   | 5.4  | Synaptic Learning Mechanism                                                                                                           | 47 |

|   | 5.5  | Hardware Implementation                                                                                                               | 48 |

|   | 5.6  | Simulation Methodology                                                                                                                | 49 |

|   | 5.7  | Summary                                                                                                                               | 51 |

| 6 | MES  | SL: Proposal for a Non-volatile Cascadable $\underline{M}$ agneto- $\underline{E}$ lectric $\underline{S}$ pin $\underline{L}$ ogic . | 52 |

|   | 6.1  | Introduction and Related Work                                                                                                         | 52 |

|   | 6.2  | ME Logic Family and Cascadability                                                                                                     | 55 |

|   | 6.3  | Results and Discussions                                                                                                               | 59 |

|   | 6.4  | Summary                                                                                                                               | 60 |

| 7 | Volt | age-Driven Domain-Wall Motion based Neuro-Synaptic Devices                                                                            | 61 |

|   | 7.1  | Introduction and Related Work                                                                                                         | 61 |

|   | 7.2  | Magneto-Electric DW motion based on Elastic Coupling                                                                                  | 63 |

|   | 7.3  | Magneto-Electric DW motion based Neuro-Synaptic Devices                                                                               | 66 |

|   |      | 7.3.1 LIF Neuron                                                                                                                      | 66 |

|   |      | 7.3.2 Programmable Synapse                                                                                                            | 68 |

|   | 7.4  | Device Modeling and Simulation                                                                                                        | 71 |

|   | 7.5  | Results                                                                                                                               | 75 |

|   |      | 7.5.1 Neuro-synaptic behavior of the proposed devices                                                                                 | 75 |

|   | 7.6  | Conclusion                                                                                                                            | 78 |

## Page

| 8  | Ener | gy-Efficie | ent Memories   | using Ma   | gneto-l | Electri | ic Sw | ritchi | ng d | of Fe | erroi | na | gne | ts | 79 |

|----|------|------------|----------------|------------|---------|---------|-------|--------|------|-------|-------|----|-----|----|----|

|    | 8.1  | Introdu    | ction          |            |         |         |       |        |      |       |       | •  |     |    | 79 |

|    | 8.2  | ME de      | vices under co | nsideratio | on      |         |       |        |      |       |       | •  |     |    | 80 |

|    | 8.3  | Device (   | Characteristic | s          |         |         |       |        |      |       |       | •  |     |    | 83 |

|    |      | 8.3.1      | Writability    |            |         |         |       |        |      |       |       | •  |     |    | 83 |

|    |      | 8.3.2 l    | Readability .  |            |         |         |       |        |      |       |       | •  |     |    | 84 |

|    |      | 8.3.3      | Switching Spe  | ed         |         |         |       |        |      |       |       | •  |     |    | 85 |

|    | 8.4  | ME Me      | mory Design .  |            |         |         |       |        |      |       |       | •  |     |    | 87 |

|    |      | 8.4.1 I    | ME Dual Port   | Memory     |         |         |       |        |      |       |       | •  |     |    | 87 |

|    |      | 8.4.2 I    | ME CAM         |            |         |         |       |        |      |       |       | •  |     |    | 88 |

|    | 8.5  | Summar     | су             |            |         |         |       |        |      |       |       | •  |     |    | 90 |

| 9  | Sum  | mary and   | l Future Work  | ٢          |         |         |       |        |      |       |       | •  |     |    | 91 |

| А  | App  | endix .    |                |            |         |         |       |        |      |       |       | •  |     |    | 93 |

|    | A.1  | Introdu    | ction          |            |         |         |       |        |      |       |       | •  |     |    | 93 |

|    | A.2  | Propose    | d Spin Dice .  |            |         |         |       |        |      |       |       | •  |     |    | 94 |

|    | A.3  | Results    |                |            |         |         |       |        |      |       |       | •  |     |    | 96 |

| RI | EFER | ENCES      |                |            |         |         |       |        |      |       |       | •  |     | 1  | 01 |

| VI | TA   |            |                |            |         |         |       |        |      |       |       | •  |     | 1  | 12 |

## LIST OF TABLES

| Tabl | Page                                                                                                |

|------|-----------------------------------------------------------------------------------------------------|

| 2.1  | MTJ parameters used in the simulation model for analyzing the VCMA effect                           |

| 3.1  | Average energy consumption per-bit and latency in the IMP and NOT vector operations                 |

| 4.1  | Summary of Parameters used for our simulations for analyzing the ME effect<br>35 $$                 |

| 5.1  | Summary of parameters used in our simulations for analysis of ME based<br>Neuron                    |

| 7.1  | Parameters used for simulations adopted from [110,112] for studying ME-<br>DW Neuro-Synaptic Device |

| 8.1  | Summary of Parameters used for our simulations                                                      |

| 8.2  | Variation of MTJ Resistance with $t_{MgO}$                                                          |

| 8.3  | Comparison of proposed ME-XNOR CAM                                                                  |

#### LIST OF FIGURES

### Figure

2

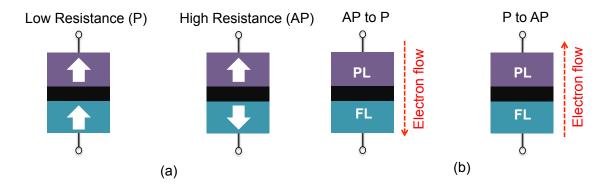

- 1.1 (a) The depiction of change in resistance in the P and the AP state of the MTJ. (b) The switching of the MTJ stack from P to AP state due top electron flow from the PL to the FL and vice-versa.

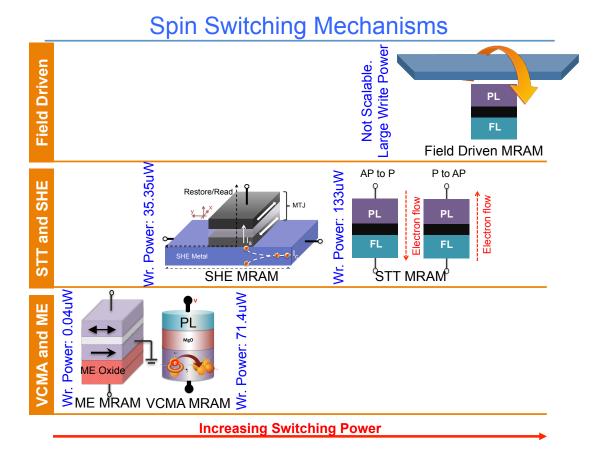

- 1.2 Various spin based switching mechanisms and devices (Field driven, Current driven: STT and SHE (Spin Hall Effect), Voltage Driven: VCMA and ME) and comparative switching power consumption for each device [12].

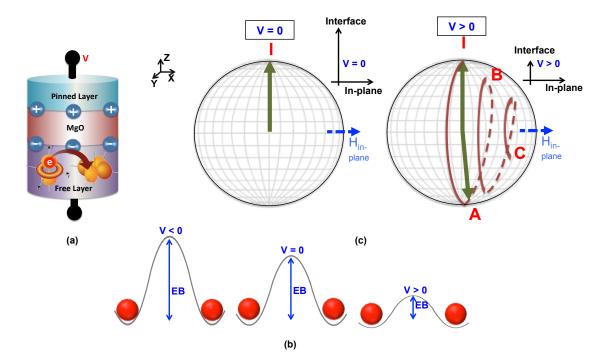

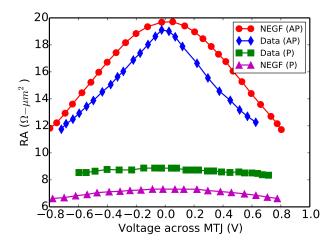

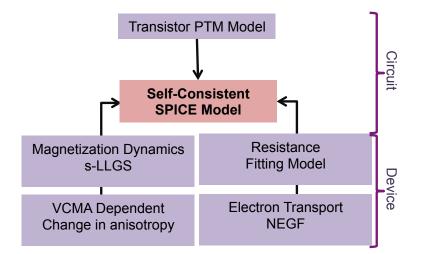

- (a) A VCMA based MTJ. The MTJ consists of a *pinned layer* and a *free* 2.1*layer* separated by a non-magnetic spacer. When a voltage is applied across the MTJ, there is a redistribution of electrons in the d-orbitals thus making the interface anisotropy sensitive to the applied voltage. (b) Schematic representation of the voltage asymmetry of the VCMA based MTJs. When a positive (negative) voltage is applied across the VCMA MTJ the energy barrier (EB) decreases (increases) due to the lowering (enhancement) of the interface anisotropy. Thus, VCMA mechanism makes the MTJ asymmetric with respect to voltage polarity, a positive voltage assists in switching the MTJ whereas a negative voltage makes it much harder to switch the MTJ. (c) Figure representing the precessional switching mechanism. When a positive voltage is applied across the MTJ such that the interface anisotropy is sufficiently lowered, the magnetization vector becomes free to precess around the *hard axis* due to the effective inplane field  $(H_{in-plane})$ . Inset shows the lowering of the interface anisotropy on application of sufficiently high positive voltage (V>0). While the magnetization vector is precessing around the hard-axis, if the voltage pulse is switched OFF when the magnetization is close to point A, it would slowly dampen towards -z direction, thereby switching the direction of magnetization by  $180^{\circ}$ ..... 6 2.2The NEGF based MTJ-resistance model [40] benchmarked against experimental data from [41]. 122.3A graphical representation of the various components of our self-consistent magnetization dynamics and resistance transport model. . . . . . . . . . . . . . . . . . 12

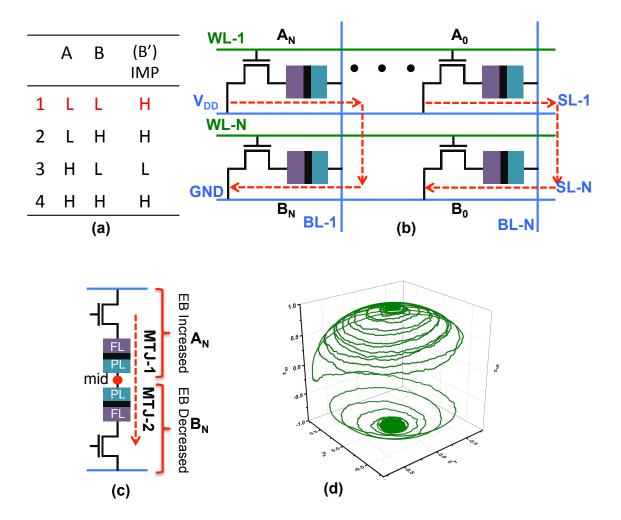

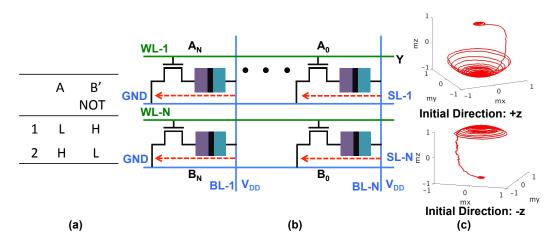

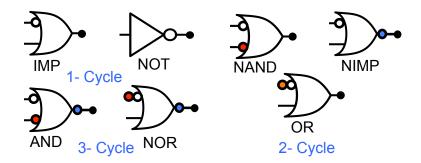

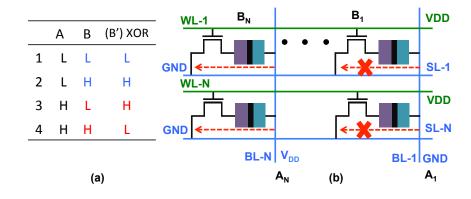

3.1(a) The truth table for two input IMP operation. The columns B and B' are the same except for row 1, highlighted in red. (b) The array configuration showing the voltages at various SLs and WLs and the current flow during the stateful computation of the bit-wise IMP operation. (c) A simplified circuit showing the voltage divider configuration resulting due to the applied voltages at the SLs and WLs. (d) A typical magnetization dynamics during the switching of the MTJ-2 from the P to the AP state, when MTJ-1 is in the P state. Note, this switching dynamics is a typical STT dominated switching, VCMA effect lowers the EB for MTJ-2, thereby allowing the small current flowing through the MTJ-2 to be able 17(a) The truth table for NOT operation. (b) The array configuration show-3.2ing the voltages at various BLs and WLs and the current flow during the stateful computation of the massively parallel NOT operation. (c) A typical magnetization dynamics showing the precessional switching behavior of the VCMA MTJs mimicking the NOT operation. On application of proper voltages, irrespective of the initial state of the magnetization direction (+z or -z), the magnetization vector switches by 180° thereby implementing the desired stateful NOT operation. . . . . . . . . . . . . . 203.3 Based on the proposed stateful operations as described in the above subsections an IMP and NOT operation can be completed in one cycle, whereas a two cycle operation can implement the NAND, NIMP and NOT logic. Similarly, a three cycle operation can be used for the AND and NOR logic computation. For multi-cycle logic, the part of logic highlighted in red can be computed in the first cycle, the part in white can be computed in second cycle, while the part highlighted in blue would be computed in the third cycle. 23(a) A truth table for XOR gate. The logic output B' retains its original 3.4value when the operand A is 'L', whereas if the operand A is 'H', the new value for B' is the complement of its original value B. (b) Figure shows the array structure used for implementing the XOR operation. The voltages on BLs represent the bits corresponding to the operand A, while the data stored in the MTJs represent the bits corresponding to the operand B. The values in the MTJs are inverted conditionally only if the bits corresponding to the operand A are 'H' *i.e.* only if the respective SLs are pulled high. Note, in the example shown, the bit value for  $A_1$  is 'L', as such, BL-1 is kept low. Therefore, no current flows through the column corresponding to BL-1 and hence the bits corresponding to BL-1 consume no energy. . . . 24

Page

Fie

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.5  | (a)Probability of B's final state being 'H' (or digital '1') for the four initial cases of A and B (00,01,10,11) in the vector IMP operation, as a function of the voltage pulse. At a pulse width of $\sim 25$ ns, the correct IMP result is obtained. (b) Probability of inverting the state of the VCMA MTJ due to precessional switching as a function of the pulse duration. The switching probability peaks at $\sim 2$ ns due to the half-cycle rotation of the magnetization dynamics.                                                                                          | . 27 |

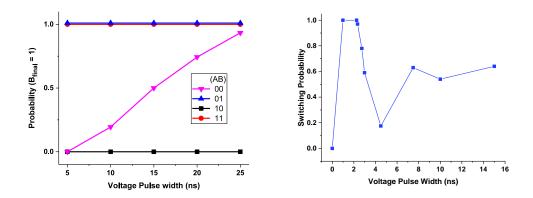

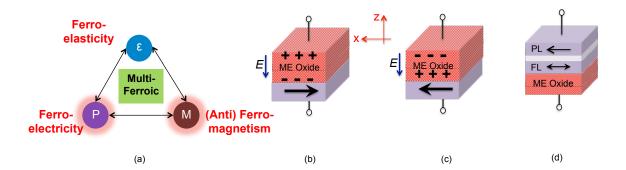

| 4.1  | (a) A graphical representation of a multi-ferroic material. Multi-ferroic are those materials that exhibit more than one ferroic order (ferro-electricity, ferro-magnetism and ferro-eleasticity). (b-c) A ferro-magnet in physical contact with an ME oxide. When an electric field is applied in the +z direction the ferro-magnet switches to the +x direction and <i>vice-versa</i> (d) Schematic for an ME-MTJ. By applying appropriate voltage across the ME oxide the state of the MTJ can be changed from parallel (P) to anti-parallel (AP).                                   | . 30 |

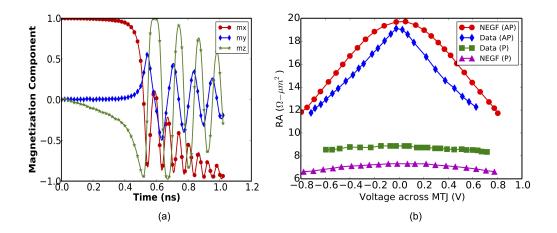

| 4.2  | (a) A typical evolution of magnetization components $mx$ , $my$ , $mz$ on application of a voltage pulse. The magnet is being switched from +x direction to -x direction. (b) The parallel and anti-parallel resistance obtained from our NEGF model [40] and benchmarked to experimental data from [69]. The resistance-voltage characteristics of Fig 4(b), were abstracted into a behavioral model for simulation.                                                                                                                                                                   | . 34 |

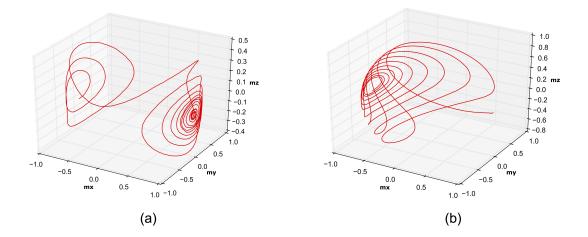

| 4.3  | (a) A typical trajectory followed by the magnetization vector when switched<br>using STT mechanism. The STT mechanism initially acts as an anti-<br>damping torque and subsequently as a damping torque thereby switching<br>the state of the ferro-magnet. (b) A typical trajectory followed by the<br>magnetization vector when switched using the ME mechanism. With ap-<br>plication of an external voltage the magnetization tries to orient itself<br>towards the direction of the ME field and finally dampens, resulting in a<br>180 <sup>o</sup> switching of the ferro-magnet |      |

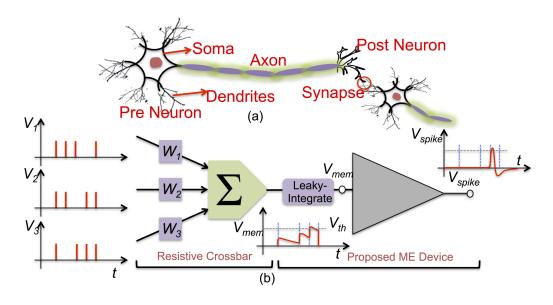

| 5.1  | (a) A biological neuron with interconnecting synapses. (b) A represen-<br>tative model for a biological neural network. $V_i$ s are the input spikes<br>generated by pre-neurons. The neuron emits a spike, if the membrane po-<br>tential $(V_{mem})$ crosses a certain threshold $(V_{th})$ . The weighted summation<br>is usually carried out by a resistive crossbar array. Our proposed ME<br>device aims to emulate the LIF and thresholding behavior of a biological<br>neuron                                                                                                   | . 39 |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

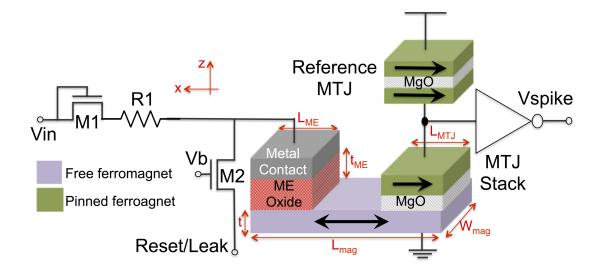

| 5.2  | Schematic of the proposed LIF ME neuron. Thick ME oxide (5nm) sand-<br>wiched between the metal contact and the ferro-magnet, acts as a capac-<br>itor. Diode connected transistor M1 prevents back flow of charges stored<br>on the ME capacitor, while resistor R1 determines the rising time constant<br>for the capacitor. M2 constitutes the leak path, when the voltage on the<br>Leak/Reset terminal is zero.                                                                                                                                                                           | . 42 |

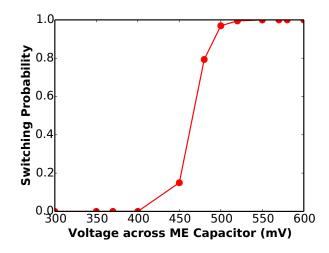

| 5.3  | The stochastic switching behavior of the proposed ME neuron as a func-<br>tion of the voltage across ME capacitor. The switching probability was<br>obtained for 10,000 runs using magnetization dynamics model with ther-<br>mal noise and pulse duration of 1ns                                                                                                                                                                                                                                                                                                                              | . 45 |

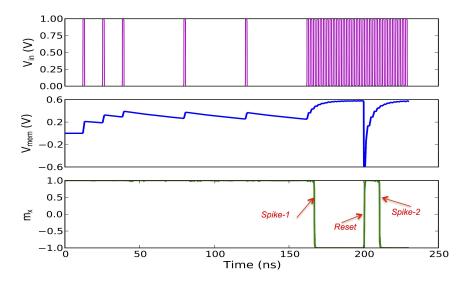

| 5.4  | Simulation results for the ME neuron, shown in Fig. 5.2. Top panel<br>shows the input spikes fed to the $V_{in}$ terminal of the device. Middle panel<br>shows the voltage across the ME capacitor, exhibiting the typical leaky-<br>integrate dynamics. Bottom panel, illustrates the switching of the ferro-<br>magnet from +x to -x direction generating a spike annotated as <i>Spike-1</i> .<br>No more spikes are generated until the device is reset to its initial position<br>by applying a negative voltage. After reset, device emits a second spike<br>annotated as <i>Spike-2</i> |      |

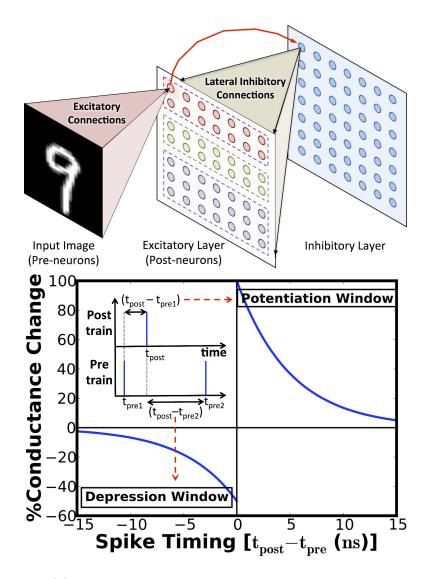

| 5.5  | <ul> <li>(a) SNN topology for pattern recognition. The input neurons are fully connected to the excitatory post-neurons, each of which is connected to the corresponding inhibitory neuron in a one-on-one manner. There are lateral inhibitory connections from each inhibitory neuron to all the excitatory post-neurons except the one from which it received a forward connection.</li> <li>(b) STDP learning algorithm, wherein the change in synaptic conductance is exponentially related to the difference in the spike times of the pre- and post-neuronal pair.</li> </ul>           | . 46 |

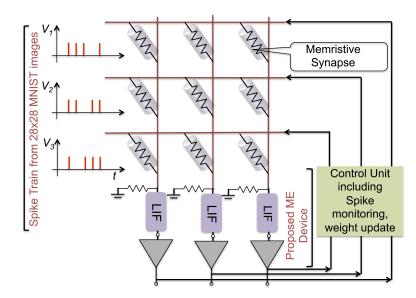

| 5.6  | A typical crossbar implementation of the SNN topology using the pro-<br>posed ME neuron. Memristive devices constitute the synapses, while the<br>proposed device mimics the LIF post-neurons. The on-chip learning cir-<br>cuit programs the synaptic conductance based on spike timing. Inputs to<br>the system are spike trains corresponding to the 28×28 image pixels from<br>the MNIST dataset                                                                                                                                                                                           |      |

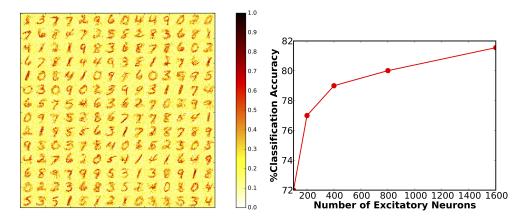

| 5.7  | (a) Synaptic weights connecting the $28 \times 28$ input pre-neurons to each of the 200 excitatory post-neurons towards the end of the training phase. (b) Classification accuracy verses the number of excitatory post-neurons                                                                                                                                                                                                                                                                                                                                                                |      |

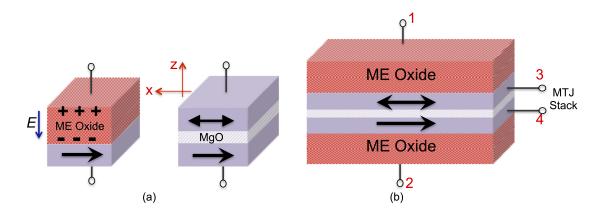

| 6.1 | (a) (Left) Figure illustrating the ME switching of a ferro-magnet with applied electric field. A positive voltage on the upper terminal switches the magnet in positive x direction and <i>vice-versa</i> (Right) An MTJ stack consisting of an MgO sandwiched between two nano-magnets. The resistance of the MTJ is a function of the voltage and the relative orientation of the magnetization directions. (b) The proposed four terminal logic-device. The upper (lower) nano-magnet can be switched by application of a voltage pulse on terminal 1 (2). The resistance of the MTJ stack can be sensed between terminals 3 and 4. The thickness of the ME oxide and the MgO spacer can be tuned independently to improve the write-efficiency and the sensing margin simultaneously. | 54 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

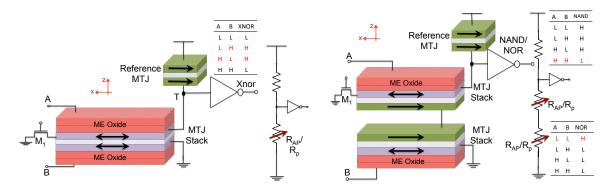

| 6.2 | (a) Proposed ME XNOR gate. Only when both the ferro-magnets point in the same direction, the output of the inverter goes high, thus implementing an XNOR function. Inset shows the truth table for the XNOR function. L represents a digital 0 and H represents a digital 1. (b) Proposed ME NAND/NOR gate. For NAND operation, the inverter is sized such that the output goes low only if both the MTJ stacks are in anti-parallel (high-resistance) state. Whereas, for NOR operation, the sizing of the output inverter is such that it goes high only if both the MTJ stacks are in parallel (low-resistance) state.                                                                                                                                                                 | 55 |

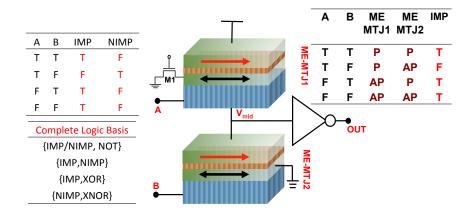

| 6.3 | (Left) Truth table for an IMP and NIMP logic gate. (Bottom) The set<br>of logic gates forming a complete logic basis along with the IMP/NIMP<br>gate. (Right) The proposed 2 input ME IMP gate. Inset shows the state<br>of the ME-MTJs under various inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 57 |

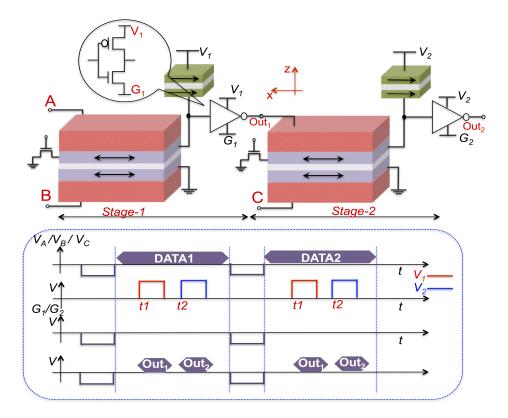

| 6.4 | Figure illustrating cascading of two ME XNOR gates. Initially, a reset operation is carried out by applying negative voltage pulses on terminals 'A', 'B', 'C', 'G <sub>1</sub> ' and 'G <sub>2</sub> '. On the other hand, when data is applied the two stages are activated in a typical domino-style, one after another. A representative timing diagram illustrates the waveforms on various nodes.                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

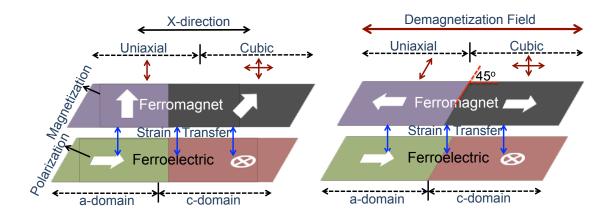

| 7.1 | (a) The replication of the domain pattern of the FE layer into the FM layer due to local strain coupling. An effective uniaxial anisotropy is induced in the region of the FM above the a-domain, while a cubic anisotropy is induced in the region over the c-domain. (b) Due to high aspect ratio the demagnetization anisotropy of the FM tends to align the magnetization of the FM along the length of the magnet, thereby resulting in almost 180° angle between the magnetizations in the two regions of the FM                                                                                                                                                                                                                                                                    | 64 |

Page

| XV |

|----|

|----|

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

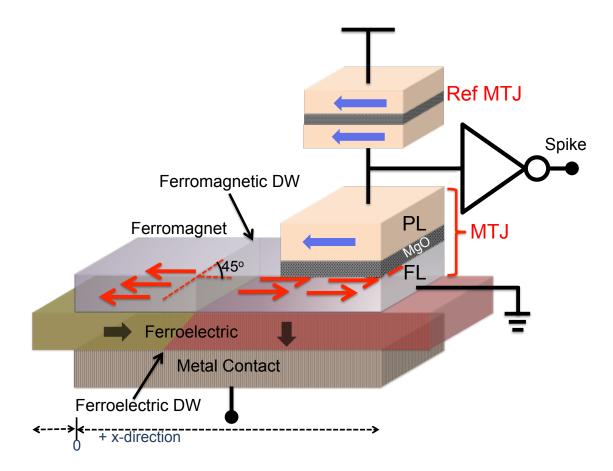

| 7.2  | The proposed non-volatile LIF neuron based on elastic coupling between<br>the FE-DW and FM-DW. The position of the FM-DW represents the<br>membrane-potential, while the switching activity of the MTJ emulates<br>the firing behavior of the neuron.                                                                                                                                                                                                                                    | . 67 |

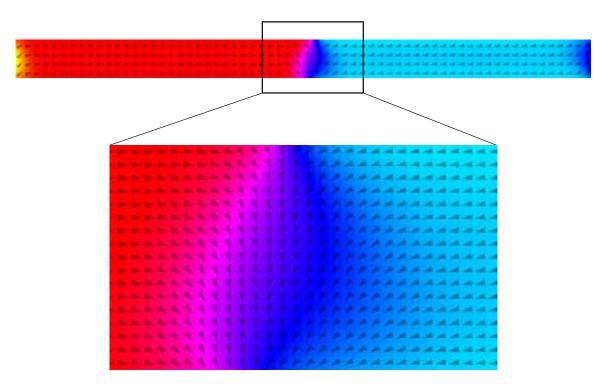

| 7.3  | Micromagnetic simulation showing the domain wall shape and structure. The zoomed image shows a $90^{\circ}$ domain wall which has been transformed to a $180^{\circ}$ domain wall due to shape anisotropy.                                                                                                                                                                                                                                                                               | . 69 |

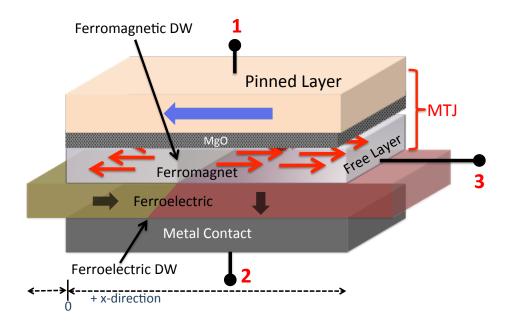

| 7.4  | The proposed non-volatile programmable synapse based on elastic cou-<br>pling between the FE-DW and FM-DW. The position of the FM-DW<br>modulates the conductane between Terminal-1 and 3 of the device. The<br>FM-DW position, and thus the conductance of the synapse, can be modi-<br>fied by applying a +ve or -ve voltage across Terminal-2 and 3                                                                                                                                   | . 70 |

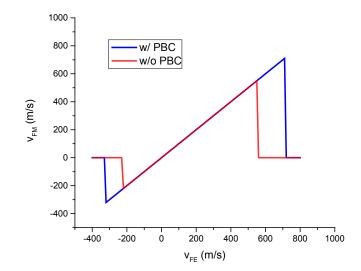

| 7.5  | Depinning velocities of the magnetic domain wall, for positive and neg-<br>ative velocities. The blue plot was obtained by using periodic boundary<br>conditions and parameters from [112]. The red plot was obtained without<br>periodic boundary conditions and scaled dimensions                                                                                                                                                                                                      | . 74 |

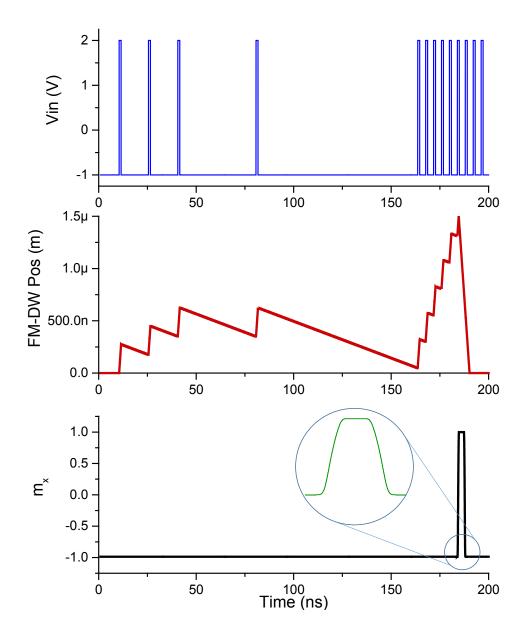

| 7.6  | Leaky integrate and fire behavior of the proposed neuron in response to<br>input train of spikes. (a) Input voltage spike train received by the neu-<br>ron. (b) FM-DW position (acts as membrane potential variable). (c)<br>x-component of magnetization under the MTJ stack. Once the MTJ<br>switches, the neuron fires, and the domain wall is reset to its initial po-<br>sition. The inset shows the average magnetization under the MTJ when<br>the domain wall traverses the MTJ | . 76 |

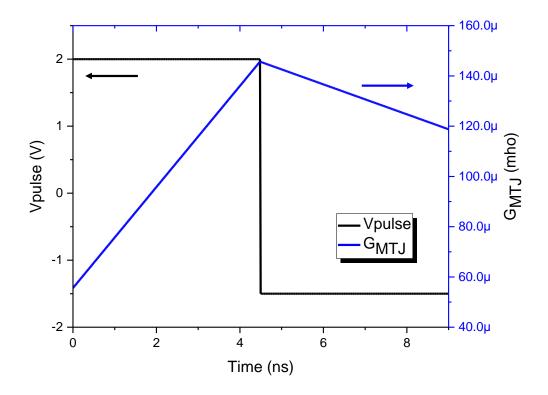

| 7.7  | Plot of MTJ conductance $G_{MTJ}$ of the synaptic device in response to voltage pulses exhibits a controlled behavior of the synaptic weights. This can be used for better learning algorithms like 'ASP' for precise tuning of synaptic weight values. The leaky behavior of the synaptic weights can be implemented using a small -ve voltage across the device.                                                                                                                       | . 77 |

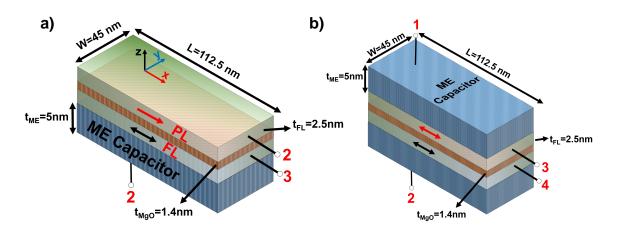

| 8.1  | (a) Schematic of the ME-MTJ and (b) ME-XNOR. The ferromagnets in contact with respective ME oxides can be switched by applying appropriate voltages across the ME oxides. The direction of switching can be reversed by changing the polarity of the applied voltage. Due to shape anisotropy the easy axis of the ferro-magnets lie along the $\pm x$ axis                                                                                                                              | . 81 |

| Figur | ce                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

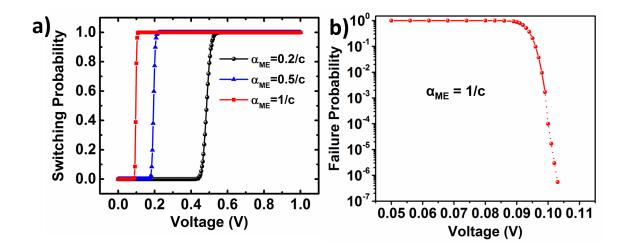

|       | (a) Switching probability versus voltage applied across the ME capacitor. It can be seen larger the ME co-efficient lower is the voltage required to switch the direction of magnetization. (b) The failure probability obtained versus voltage. Each point on the graph was obtained by 1,000 simulations of the stochastic LLG equation. The voltage was applied for a duration of 500ps and the state of the magnet was investigated after the application of the voltage pulse to verify if the magnet has switched within the applied pulse duration. |      |

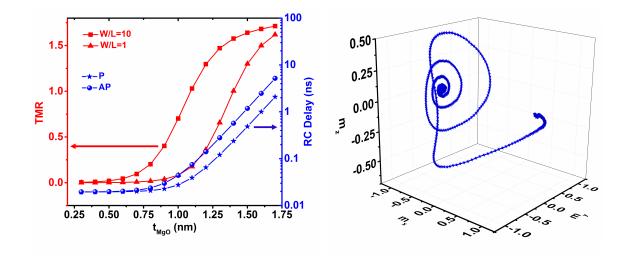

|       | (a) (Left axis) Bit-cell TMR versus MgO thickness obtained from our NEGF based transport model. In each case, a transistor in series is used with Width/Length (W/L) ratio as specified in the figure. (Right axis) The RC time constant as a function of the MgO thickness. (b) A typical 3D switching trajectory of the magnetization under influence of applied voltage.                                                                                                                                                                                |      |

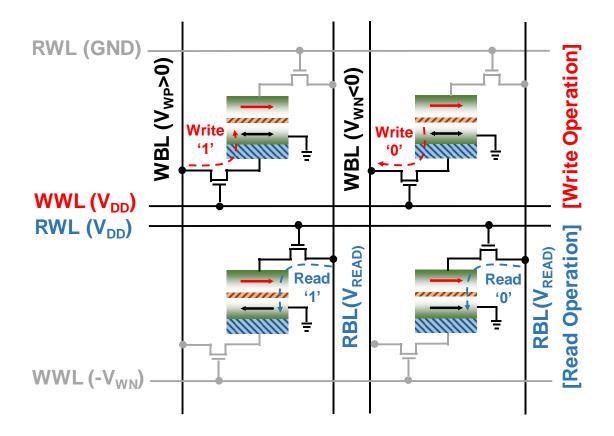

|       | 1-Read / 1-Write dual port memory using decoupled read/write path of ME-MTJs. The top row of ME-MTJs are being written into by activating the RWL, while the bottom row of ME-MTJs can be simultaneously read by activating WWL.                                                                                                                                                                                                                                                                                                                           |      |

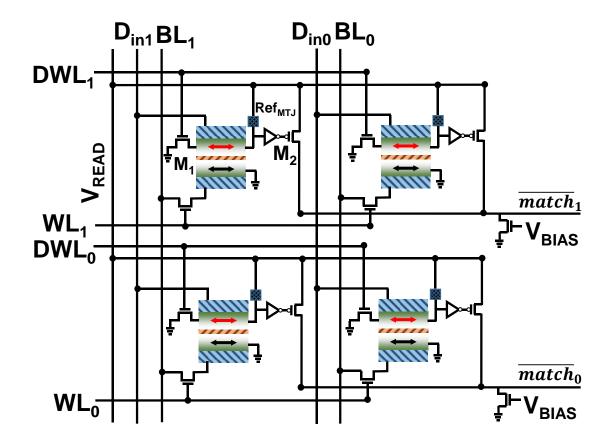

|       | Proposed CAM based on ME-XNOR device. The upper and lower ferro-<br>magnets comprising the ME-XNOR device can be used to store the input<br>data and the data to be matched, respectively. The $\overline{match}$ signal goes low<br>if and only if all the p-MOSes of a particular row are turned OFF                                                                                                                                                                                                                                                     |      |

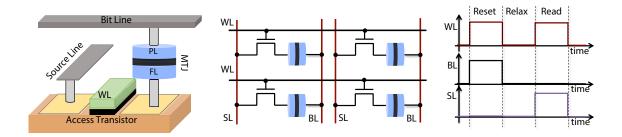

|       | Schematic of an STT-MRAM bit cell being utilized as VC-SD. The bit-<br>cell consists of the MTJ in series with an access transistor. The proposed<br>TRNG can be implemented using a standard STT-MRAM array. The<br>operation consists of "Reset", "Relax" and "Read" operations. The cor-<br>responding control signals WL, BL and SL have been shown                                                                                                                                                                                                    |      |

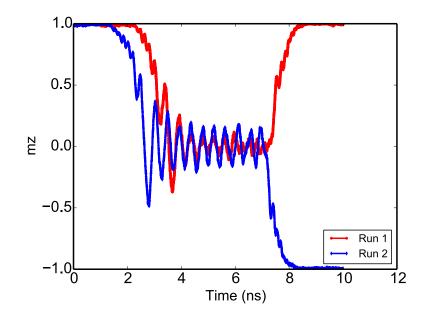

|       | Magnetization dynamics of the same VC-SD device for two different simulation runs                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 94 |

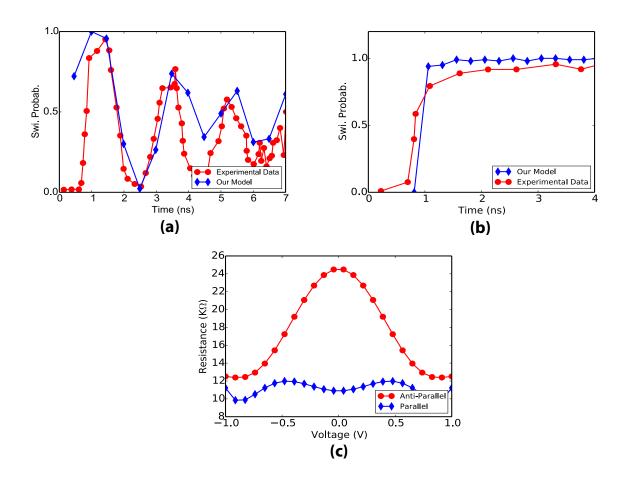

| A.3 | Our benchmarked results for (a) only VCMA-induced switching, and (b) combined VCMA and STT switching. (c) NEGF results obtained from our transport model. We have matched the parallel and anti-parallel resistance to the reported value of $11K\Omega$ and $25K\Omega$ respectively. All the benchmarking is done with respect to the experiment [38]. The MTJ is of circular cross-sectional area with diameter $40nm$ and FL thickness $0.9nm$ . The oxide thickness is $1.3nm$ . An external field of magnitude $31mT$ is applied to provide the necessary in-plane magnetic field. It is worth noting here that the external field was only considered during the benchmarking process. For VC-SD operation, no external field was provided by the demagnetization field of the magnet. The MTJ operating voltage is $0.7V$ . 97 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

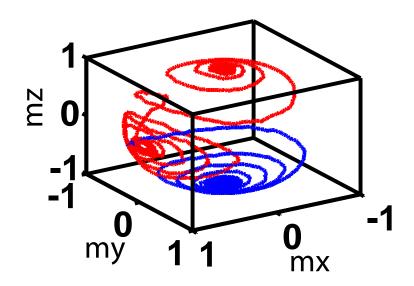

| A.4 | A sample SD trajectory for the proposed TRNG. The magnetization switches to "hard-axis" and subsequently relaxes to one of the stable magnetization states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

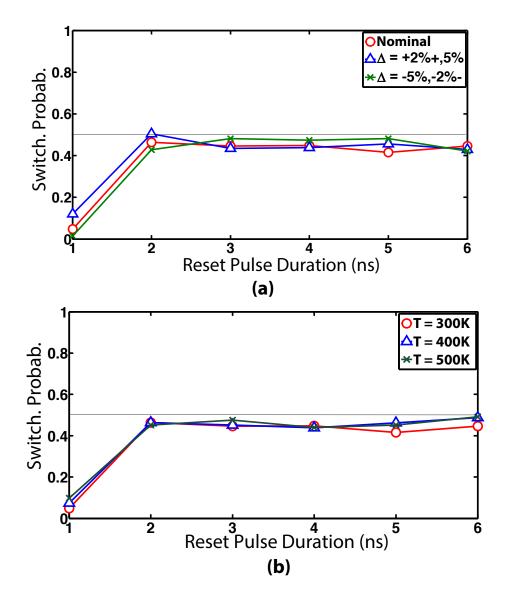

| A.5 | Switching probability (measured over 500 independent stochastic LLG simulations) for varying "reset" pulse width $(1 - 6ns)$ . The randomness offset remains limited within reasonable bounds (< 10%) even with (a) variations in cross-sectional area (5%) and thickness (2%), and (b) temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Page

#### ABSTRACT

Akhilesh Jaiswal Ph.D., Purdue University, May 2019. Exploiting Voltage Driven Switching of Ferromagnets for Novel Spin based devices and circuits. Major Professor: Dr. Kaushik Roy.

The *spin* of an electron has for long excited researchers both with respect to its fundamental physics and technological applications. Consequently, the traditional field driven switching of ferromagnets gave way for more scalable current driven switching based on the well-known spin transfer torque phenomenon. However, in the quest for better energy-efficiency, the manipulation of electron spin through pure voltage driven or voltage-assisted mechanisms are being intensely explored. In this research, we demonstrate that the very physics and the characteristics of such voltage driven devices enable interesting possibilities with respect to memory, neuromorphic and logic applications. We rely on the recent experimental demonstrations of two novel voltage effects on nano-magnets – the voltage controlled magnetic anisotropy (VCMA) and the pure voltage driven magneto-electric (ME) effect. Specifically, we propose in-situ, in-memory, vector logic operations by exploiting the voltage asymmetry and precessional switching dynamics of the VCMA effect to construct 'stateful' logic gates. Stateful logic are those in which the same device acts as a storage element and compute engine, simultaneously. In addition, we show that the pure voltage driven mono-domain switching and domain-wall motion of nano-magnets through the ME effect can be leveraged to construct neuro-mimetic devices exhibiting leakyintegrate-fire dynamics of biological neurons and as well as non-volatile synaptic elements. Further, we propose a voltage driven logic-device using the ME switching and demonstrate that the proposed logic-device can be used to construct a complete cascadable logic family including XNOR, IMP (implication), NAND and NOR gates. Additionally, we present an energy and area efficient content addressable memory using a logic compatible ME-XNOR device. The presented research shows that voltage driven switching can augment the very functionality and widen the application scope of spin based devices and circuits.

## 1. INTRODUCTION AND MOTIVATION

Right from the very inception of the idea of an electron having an intrinsic 'spin' in early 1920s [1], electron spin has intrigued physicist and technologist alike. Seminal theoretical and experimental works by the likes of Paul Dirac [2], Stern-Gerlach [3], Albert Fert [4] and others made possible the first field driven magnetic storage devices. However, such field driven devices were not very scalable due to the requirement of an external magnetic field for switching the state of the magnetic memories. It was Slonczewski's theoretical work published in 1996 that predicted current driven switching of ferromagnets by the spin transfer torque (STT) mechanism [5]. The discovery of the STT phenomenon lead to an entire paradigm shift in spin based devices and their applications.

Let us have a quick look at the STT mechanism. The basic magnetic device is a magnetic heterostructure consisting of two nano-magnets separated by an insulating oxide, as shown in Fig. 1.1(a), called the magnetic tunnel junction. The direction of magnetization in one of the nano-magnets is fixed (the pinned layer), while the direction of magnetization for the other nano-magnet can be changed (the free layer). When the pinned and the free layer point in the same direction (Fig. 1.1(a)), MTJ is in the low resistance state (P state or digital '0') whereas, when the directions of magnetization in the two layers are anti-parallel, the MTJ is in the high resistance state (AP state or digital '1'). A read operation is accomplished by applying a small voltage across the MTJ and sensing its resistance. For writing a digital bit into the MTJ, a state transition may be required from the P to AP state or the AP to P state. For an AP to P transition, the electrons flow from the pinned layer (PL) into the free layer (FL), as shown in Fig. 1.1(b). The pinned layer acts as a polarizer and the electrons flowing from the pinned layer to the free layer are polarized in the direction of the pinned layer. This spin-polarized current exerts a torque on the free layer [5] making

Fig. 1.1. (a) The depiction of change in resistance in the P and the AP state of the MTJ. (b) The switching of the MTJ stack from P to AP state due top electron flow from the PL to the FL and vice-versa.

its magnetization parallel to that of the pinned layer. For writing a digital '1' (P to AP), current direction has to be reversed. In this case, spins pointing in the direction of the pinned layer easily pass through the MTJ leading to accumulation of opposite spins in the free layer. These accumulated spins exert a torque on the free layer making it anti-parallel with respect to the pinned layer. Thanks to the rich physics of the STT effect and its associated magnetization dynamics many non-volatile memories [6], non-volatile logic [7], logic-in memory [8], non-Boolean computations [9], neuromorphic applications [10], combinatorial optimization [11] *etc.* have became possible.

STT mechanism, however, suffers from relatively high switching power consumption owing to the current induced nature of the switching mechanism [13]. In order to reduce the switching power various voltage driven or voltage assisted switching mechanisms are being actively investigated [14, 15]. As shown in Fig. 1.2, voltage driven schemes allows lowering of power consumption with respect to switching the state of the device from one stable state to the other. We would be considering two different voltage driven effects 1) the voltage controlled magnetic anisotropy (VCMA) and 2) the magneto-electric (ME) effect. VCMA mechanism allows one to modulate the energy barrier of an MTJ by application of an electric field. Lower the energy barrier, lower is the switching current requirement. On the other hand, the ME effect lever-

Fig. 1.2. Various spin based switching mechanisms and devices (Field driven, Current driven: STT and SHE (Spin Hall Effect), Voltage Driven: VCMA and ME) and comparative switching power consumption for each device [12].

ages the coupling between different order parameters (ferroelectricity, ferromagnetism and ferroelasticity) to achieve pure voltage driven switching of ferromagnets.

In this research, we demonstrate that the voltage driven switching of ferromagnets not only helps in achieving energy-efficiency, it opens up new avenues for memory, neuromorphic and logic applications. Specifically, chapter 2 describes the physics and modeling of the VCMA effect [16, 17]. In chapter 3, we propose *in-situ*, in-memory, stateful logic operations by exploiting the very physics of the VCMA mechanism [17]. Chapter 4 discusses the ME effect and its modeling [18]. Chapters 5 and 6 propose novel ME devices as neuromorphic [19] and Boolean logic primitives [18, 20], respectively. Chapter 7 introduces a novel neuro-synaptic device based on pure voltage driven domain-wall motion using elastically coupled ferroelectric and ferromagentic layers [21]. In chapter 8, we present a 1-Read /1-Write dual port memory and an energy- and area-efficient content addressable memory using ME devices [22]. Chapter 7 elaborates on the future work and summarizes the research work. In Appendix, we present an energy-efficient true random number generators using the VCMA effect [23].

## 2. VCMA PHYSICS AND MODELING

### 2.1 Introduction to VCMA mechanism

### 2.1.1 VCMA mechanism: Voltage asymmetry

The basic device structure under consideration is the two terminal magnetic tunnel junction (MTJ). An MTJ consists of two nano-magnets separated by an insulating oxide as shown in Fig. 2.1(a). The MTJ is called a perpendicular MTJ if the magnetization directions of the two nano-magnets are perpendicular to the plane of the nano-magnets. One of the nano-magnets is fixed called the *pinned layer* (PL), while the other nano-magnet can be switched by applying a voltage across the MTJ called the *free layer* (FL). The MTJ has two stable states called the parallel (P) state and the anti-parallel (AP) state. When the magnetization of the two nano-magnet is in the same direction the MTJ is in low resistance P state and *vice-versa*.

Conventionally, the state of the MTJ has been switched using the current induced spin transfer torque (STT) phenomenon [24]. The basic physics associated with the STT phenomenon relies on the fact that a *spin polarized* current passing through the FL exerts a torque on the FL thereby flipping the state of the MTJ from the P to the AP state and *vice-versa*. This exerted torque by the STT mechanism has to be sufficient to overcome the energy barrier (EB) associated with the FL. In perpendicular MTJ, it is the interface anisotropy that creates the required energy barrier between the two stable states of the MTJ. In general, higher the EB, higher is the current required to switch the MTJ. One of the key challenges associated with the STT phenomenon is the high switching current requirement [25]. In order to reduce the current requirement for switching the nano-magnet various voltage driven switching phenomenon are under intense research investigation [26, 27]. One of the most

Fig. 2.1. (a) A VCMA based MTJ. The MTJ consists of a *pinned layer* and a *free layer* separated by a non-magnetic spacer. When a voltage is applied across the MTJ, there is a redistribution of electrons in the d-orbitals thus making the interface anisotropy sensitive to the applied voltage. (b) Schematic representation of the voltage asymmetry of the VCMA based MTJs. When a positive (negative) voltage is applied across the VCMA MTJ the energy barrier (EB) decreases (increases) due to the lowering (enhancement) of the interface anisotropy. Thus, VCMA mechanism makes the MTJ asymmetric with respect to voltage polarity, a positive voltage assists in switching the MTJ whereas a negative voltage makes it much harder to switch the MTJ. (c) Figure representing the precessional switching mechanism. When a positive voltage is applied across the MTJ such that the interface anisotropy is sufficiently lowered, the magnetization vector becomes free to precess around the hard axis due to the effective in-plane field  $(H_{in-plane})$ . Inset shows the lowering of the interface anisotropy on application of sufficiently high positive voltage (V>0). While the magnetization vector is precessing around the hard-axis, if the voltage pulse is switched OFF when the magnetization is close to point A, it would slowly dampen towards -z direction, thereby switching the direction of magnetization by  $180^{\circ}$ .

promising technique and easy to incorporate in the two terminal MTJ stack is the voltage controlled magnetic anisotropy (VCMA) effect [26].

VCMA effect is the phenomenon of being able to modulate the interface anisotropy of the MTJ stack by applying a voltage across the MTJ [28]. Application of an electric field modulates the relative occupancy of the valence d-orbitals, as shown schematically in Fig. 2.1(a), thereby effectively changing the interface anisotropy [29,30]. Recall, in perpendicular MTJs it is the interface anisotropy that is primarily responsible for creating the required EB. A large EB is required for maintaining the non-volatility of the MTJ devices. However, a large EB also makes it harder to switch the nano-magnets during the write process. VCMA effect allows one to temporarily reduce the EB by reducing the interface anisotropy in response to electric field. The reduced EB makes it easier to switch the nano-magnets, thereby reducing the switching current requirement. On the other hand, if the direction of the electric field is reversed, EB increases due to the VCMA effect making it much more difficult to switch the nano-magnet. This increase or decrease in the EB due to application of an electric voltage across the MTJ is shown schematically in Fig. 2.1(b). The figure shows that, the VCMA effect makes the MTJ stack *asymmetric* with respect to the voltage polarity. With favorable voltage polarity (pinned layer at higher potential than the free layer) the MTJ can be easily switched while if the voltage polarity is reversed the MTJ would be difficult to switch. In fact, it has been experimentally shown that when the EB is increased by applying a voltage, the MTJ breaks down at sufficiently higher voltages but does not switch [31]. In later section, we would describe how this voltage asymmetry of the VCMA based MTJs would be used to construct stateful IMP (implication) logic for vector operations.

#### 2.1.2 VCMA mechanism: Precessional switching

VCMA effect allows for a new switching dynamics, called the *precessional switching*, in contrast to the typical STT based switching phenomenon [16]. The precessional switching dynamics can be understood with respect to Fig. 2.1(c). Let us assume the magnetization of the FL is initially pointing in +z-direction due to the interface anisotropy that tends to align the magnetization direction perpendicular to the plane of the nano-magnet. As a consequence of the VCMA effect, when a voltage is applied across the MTJ, the interface anisotropy decreases. If the decrease in the interface anisotropy is sufficient, the magnetization would no longer be bound by the interface anisotropy and would be free to deviate from its initial position (+z)in this case). Now, assume there is a small in-plane field in +x-direction (denoted as  $H_{in-plane}$  in Fig. 2.1(c)) either due to the shape anisotropy, or such in-plane field can be engineered in the MTJ stack as experimentally demonstrated in [32]. Since, the interface anisotropy has been reduced by voltage application (V>0 in Fig. 2.1(c)) and there is an effective field in the +x direction, the magnetization would tend to align itself to the effective field. It would do so by precessing and slowly damping towards the +x direction. This behavior is graphically depicted in Fig. 2.1(c), where the magnetization initially starts from position 'I' and then follows the trajectory marked by points A-B-C on application of electric filed across the MTJ (V>0).

If we turn OFF the applied voltage when the magnetization is at point A in Fig. 2.1(c), the magnetization would slowly dampen and point in the -z direction due to the interface anisotropy. Thus, by timing the voltage pulse such that magnetization makes a half-cycle around the *hard-axis* (+x in this case), it can be switched by  $180^{\circ}$ . This switching due to the precession of the magnetization across the hard-axis is called precessional switching. VCMA based precessional switching has several advantages including low energy-requirement and high switching speed [33]. We would later describe how this precessional switching of the VCMA MTJs can be used to construct a massively parallel NOT operation.

### 2.2 Device Modeling

In this section, we describe the coupled device-circuit simulation model developed for analyzing VCMA based MTJ and associated circuits. The model integrates and self-consistently solves the magnetization dynamics and electron transport model in a SPICE platform, enabling a rigorous circuit simulation for evaluating of energy and performance metrics.

## 2.2.1 Magnetization Dynamics based on stochastic LLGS equation including the VCMA effect

The magnetization vector in a mono-domain nanomagnet follows the dynamics governed by the well-known *Landau-Lifshitz-Gilbert-Slonczewski (LLGS)* equation [34,35]. LLGS equation can be written as follows:

$$\frac{\partial \widehat{m}}{\partial t} = -|\gamma|\widehat{m} \times \overrightarrow{H}_{EFF} + \alpha \widehat{m} \times \frac{\partial \widehat{m}}{\partial t} + \overrightarrow{STT}$$

(2.1)

$$\overrightarrow{H}_{EFF} = \overrightarrow{H}_{ext} + \overrightarrow{H}_{demag} + \overrightarrow{H}_{ani} + \overrightarrow{H}_{thermal}$$

(2.2)

$$\overrightarrow{STT} = |\gamma|\beta(\widehat{m} \times (\epsilon \widehat{m} \times \widehat{P} + \epsilon' \widehat{P}))$$

(2.3)

where  $\widehat{m}$  is the unit magnetization vector,  $\alpha$  is the Gilbert damping constant,  $\gamma$  is the gyromagnetic ratio,  $H_{EFF}$  is the effective magnetic field experienced by the nanomagnet and  $\overrightarrow{STT}$  is the STT torque acting on the nanomagnet. The first term on the right hand side of Eq. 2.1 relates to magnetization precession along  $H_{EFF}$  while the second and last terms describe the damping torque and STT, respectively.  $H_{EFF}$ includes an external field  $(H_{ext})$ , demagnetization field due to shape anisotropy [36]  $(H_{demag})$ , the interface perpendicular anisotropy field [13]  $(H_{ani})$  and stochastic field due to thermal noise  $(H_{thermal})$ , as described in Eq. 2.2. The  $\overrightarrow{STT}$  torque is expressed in Eq. 2.3, where  $\beta$  is the rate of spin transfer into the MTJ-FL,  $\epsilon$  is the spin injection efficiency,  $\widehat{P}$  is the polarization of the incoming spin current and  $\epsilon'$  describes the STT field-like torque. Further, as detailed in Section 2.1, VCMA effect modulates the interface anisotropy of the MTJ stack in response to an applied voltage. VCMA effect is thus modeled using a voltage dependent anisotropy constant  $(K_i)$ , which is incorporated in the LLGS equation through  $H_{ani}$ , as follows:

$$K_{i} = K_{i0} - \xi \frac{V_{MTJ}}{t_{MgO}}$$

(2.4)

$$H_{ani} = \frac{2K_i m_z}{M_s t_{FL}} \hat{z} \tag{2.5}$$

where  $\xi$  is the VCMA coefficient,  $V_{MTJ}$  is the voltage applied across the MTJ stack,  $t_{MgO}$  is the spacer oxide thickness,  $K_{i0}$  is the nominal value of anisotropy constant at zero voltage (no VCMA),  $M_s$  is saturation magnetization and  $t_{FL}$  is thickness of the FL nanomagnet. The thermal noise was included in the LLGS equation using a thermal field given by Brown's model [37] as:

$$\overrightarrow{H}_{thermal} = \overrightarrow{\zeta} \sqrt{\frac{2\alpha k_B T}{|\gamma| M_S \rho_{mtj} dt}}$$

(2.6)

where  $\overrightarrow{\zeta}$  is a vector having components that are Gaussian random variables with zero mean and standard deviation of 1,  $\rho_{mtj}$  is the volume of the nanomagnet, T is the ambient temperature,  $k_B$  is the Boltzmann's constant and dt is the simulation time step. The device dimensions and other parameters used in simulation are tabulated in Table 2.1.

### 2.2.2 MTJ Resistance model

The resistance of the MTJ was modeled using the non-equilibrium Green's function (NEGF) approach, benchmarked against experimental data from [41], as illustrated in Fig. 2.2. The details of various equations used in our NEGF model can be found in [40]. Our NEGF model is based on a potential profile wherein a non-magnetic barrier separates two nano-magnets. The non-magnetic barrier is characterized by its energy-barrier while the nano-magnets by their *band-splitting* energy. The results obtained by the NEGF calculations were encapsulated in an analytical fitting model

| Parameters                             | Value                             |

|----------------------------------------|-----------------------------------|

| MTJ Diameter $(W_{MTJ})$               | 40nm                              |

| MTJ-FL thickness $(t_{FL})$            | 0.9nm                             |

| MTJ-spacer thickness $(t_{MgO})$       | 1.3nm                             |

| MTJ-PL polarization                    | 0.4                               |

| Saturation Magnetization $(M_S)$       | $1257.3 emu/cm^3$ [38]            |

| Gilbert Damping Factor ( $\alpha$ )    | 0.02                              |

| Tunneling Magnetoresistance (TMR)      | 125%                              |

| VCMA coefficient $(\xi)$               | $3.72e - 8 \ ergV^{-1}/cm^2$ [39] |

| Interface Anisotropy, at 0V $(K_{i0})$ | $1.1 erg/cm^3$                    |

| External field $(H_{ext})$             | $100Oe\ \widehat{y}$              |

Table 2.1. MTJ parameters used in the simulation model for analyzing the VCMA effect.

such that the resulting MTJ resistance was modeled as a SPICE compatible voltage dependent resistance.

## 2.2.3 Self-Consistent SPICE Compatible Magnetization Dynamics and Resistance Model

A SPICE compatible device-circuit model was developed in Verilog-A for the VCMA-MTJ. The Verilog-A model concurrently solves the LLGS equation, the MTJ resistance model and the associated circuit equations. Predictive transistor models [42] were used for the access transistors, thus completing the 1-T 1-VCMA MTJ bit-

Fig. 2.2. The NEGF based MTJ-resistance model [40] benchmarked against experimental data from [41].

Fig. 2.3. A graphical representation of the various components of our self-consistent magnetization dynamics and resistance transport model.

cell model. Fig. 2.3 shows graphically the various building blocks associated with our self-consistent device-circuit simulation framework.

## 3. *IN-SITU*, IN-MEMORY STATEFUL VECTOR LOGIC OPERATIONS BASED ON VOLTAGE CONTROLLED MAGNETIC ANISOTROPY

### 3.1 Introduction and Related Work

Shanon in his seminal work on Boolean logic laid the foundation for digital logic design as a part of his master's thesis [43]. The underlying idea being the fact that the basic Boolean gates like AND and OR can be easily implemented using electronic switches. With the invention of transistor switches [44], almost a decade after Shanon's work, digital logic quickly gained ground and has become the workhorse of today's information processing [45].

In general, the state-of-art digital processors rely heavily on Boolean gates constituting the *computational unit* which is separate from the *storage unit* consisting of numerous memory cells. This decoupled architecture wherein memory and compute units are physically separated is named after its inventor as the *von-Neumann architecture* [46]. The von-Neumann architecture forms the backbone of almost all the available commercial processors. Despite the tremendous strides made in computing efficiency powered by the von-Neumann machines, it fails to deliver the required speed and efficiency demanded by the recent developments in big-data, artificial intelligence, Internet-of-things (IoT) *etc* [47]. The major limitation associated with the von-Neumann architecture is the so-called *von-Neumann bottleneck* [48]. This bottleneck mainly arises from the limited data transfer rate between the physically decoupled compute and memory units. The frequent *to-and-fro* data transfer between the compute and the memory units, not only limits the overall throughput but also results in large energy overhead associated with each data transfer. In order to mitigate the limitations associated with the von-Neumann bottleneck one promising approach is to enable *in-memory* vector computations [49, 50].

These novel computing paradigms termed as *in-memory* computations aim to implement some (or all) aspects of Boolean logic computations as close to the memory units as possible, thereby avoiding expensive data transfer between the compute and memory units, resulting in higher throughput and better energy-efficiency. Such inmemory computations using conventional silicon based complementary-metal-oxidesemiconductor (CMOS) technology has been demonstrated in [51]. The basic idea behind the in-memory compute mechanism proposed in [51] is to activate multiple rows of memory-cells and read-out a voltage which is proportional to the desired logic computations. However, silicon technology is itself facing tremendous challenges due to aggressive scaling of the CMOS transistors [52-54]. As such, novel memory technologies like spin based magnetic random access memories (MRAMs) [6,41], resistive RAMs [55], phase change materials based memories [56] are being actively investigated for possible replacement of silicon based technologies. A key benefit of these novel technologies is their *non-volatility*. The non-volatile characteristics of these memory units make them well-suitable for ultra-low leakage applications ultimately increasing the energy-efficiency [57].

Exploration of in-memory compute designs using such non-volatile technologies are crucial to meet the energy and throughput requirement demanded by the emerging data intensive applications. Spin-transfer-torque MRAM (STT-MRAM) based in-memory Boolean computations have been proposed in [8, 58]. These in-memory architecture rely on the peripheral read circuits to implement the actual computations. Nevertheless, the peripheral circuits being close to the memory array does provide energy and throughput benefits. The logic computation results are only available when the data is being read from the memory array. This implies if one were to do multiple logic operations which are dependent on the intermediate results, one would require to do a read operation for every logic computation. Thus each in-memory logic operation is inevitably associated with a memory read operation even for intermediate results leading to decreased memory throughput and energy-efficiency.

As opposed to the aforementioned works which use the memory peripheral circuits to do the actual logic computations there are other classes of in-memory compute designs that do computations 'in-situ' using 'stateful' memory devices wherein the same device acts both as a memory element and compute unit. The well known memristive implication (IMP) logic demonstrated in [59] is a good example of such stateful computations. However, the limited endurance of memristors in general make these devices unsuitable for on-chip cache or IoT applications that have extreme longevity requirement. Out of all the non-volatile technologies, spin based devices are the only devices that have high switching speed as well as unlimited endurance. Few works on stateful computations using spin devices can be found in [60], [61]. Specifically, the work presented in [60] uses a three terminal device exploiting the spin Hall effect and the voltage controlled magnetic anisotropy in spin devices to do stateful computations. However, one of the inputs to these devices is an electrical quantity *i.e.* input charge current. This in turn implies if we were to compute say the vector AND operation on the logic states stored in two separate memory rows, one of the memory rows will have to be read first, then converted into electrical signal (a current in this case) before the actual logic computation can be completed. This requirement of 'read before compute' would lead to degraded benefits in throughput and energy.

In this work, we employ the very physics of voltage controlled magnetic anisotropy to construct *in-situ*, in-memory, stateful computations using a two terminal spin device. Specifically, we use the voltage asymmetry of the VCMA effect to construct IMP (implication) logic and the precessional dynamics of the VCMA switching process to propose a *massively parallel* NOT and XOR operation. The key highlights of the work presented in this chapter and its advantages over previous works are as follows:

1. We propose *in-situ*, in-memory stateful IMP vector computations using the voltage asymmetry of the VCMA effect on two terminal magnetic tunnel junctions (MTJs). In addition, we propose a *massively parallel* NOT and XOR operation by exploiting the precessional switching dynamics of VCMA based MTJs.

- 2. Further, the massively parallel behavior of the proposed NOT gate allows multicycle computation of other Boolean functions including AND, OR, NAND, NOR, NIMP(complement of IMP), thereby constructing a rich logic functionality embedded within the memory array in a stateful manner.

- 3. One of the major advantages of the proposed *in-situ*, in-memory stateful vector computations is the fact that we rely on the well known 1 transistor 1 MTJ bitcell without making any changes in the magnetic device or the bit-cell circuit. This is turn makes our proposal attractive from manufacturability point of view. Further, as opposed to [8,58] our logic computations do not rely on complex read operations given the fact that reading MTJ devices in general is a complex circuit problem. In addition, as opposed to the work in [60], we do not need to represent the logic operands by an electrical input, rather both the logic operands can be stored in the memory array leading to higher throughput.

- 4. We have developed a detailed device-circuit model comprising of self-consistent magnetization dynamics and electron transport model integrated seamlessly in SPICE environment to study the feasibility of the proposed logic computations.

## 3.2 Proposed *in-situ*, in-memory Stateful Vector Logic Operations

### 3.2.1 Stateful vector IMP gates

Let us assume we have two VCMA based MTJs – 'MTJ-1' and 'MTJ-2' storing two input data bits 'Bit-1' and 'Bit-2', respectively. We wish to compute the implication (IMP) of bits 'Bit-1' and 'Bit-2' such that the new value of the MTJ-2 would correspond to the IMP of the original values of bits 'Bit-1' and 'Bit-2'. Further, let us assume that this logic computation has to be done in a 'stateful' manner such that

Fig. 3.1. (a) The truth table for two input IMP operation. The columns B and B' are the same except for row 1, highlighted in red. (b) The array configuration showing the voltages at various SLs and WLs and the current flow during the stateful computation of the bit-wise IMP operation. (c) A simplified circuit showing the voltage divider configuration resulting due to the applied voltages at the SLs and WLs. (d) A typical magnetization dynamics during the switching of the MTJ-2 from the P to the AP state, when MTJ-1 is in the P state. Note, this switching dynamics is a typical STT dominated switching, VCMA effect lowers the EB for MTJ-2, thereby allowing the small current flowing through the MTJ-2 to be able to selectively switch the MTJ-2 as desired.

the same VCMA MTJs (that function as memory elements storing bits 'Bit-1' and 'Bit-2') also act as logic computation units.

In order to understand the proposed stateful computations, let us consider the truth table of a two input IMP gate shown in Fig. 3.1(a). Note, the first column (A) would physically represent possible states of MTJ-1 and the second column (B) would represent states of MTJ-2. The third column (B') represents the new state of MTJ-2 after the logic operation has been completed. Interestingly, in Fig. 3.1(a), column B is same as B' except for row 1 (highlighted in red). Further, we assume the low digital level (L) is mapped to the P state of the MTJ and high digital level (H) is mapped to the AP state. This implies in order to do the stateful computations, when the operand 'A' (MTJ-1) is in the P state and operand 'B' (MTJ-2) is also in the P state, the state of MTJ-2 should change from P to AP, thereby mimicking the logic operation corresponding to row 1 of Fig. 3.1(a). Further, for all other cases since B = B', the state of the MTJ-2 should not change. Thus, if we can retain the state of MTJ-2 for rows 2, 3, 4 and change the state from P to AP for row 1 we would have effectively accomplished the IMP operation.

Fig. 3.1(b) and (c), illustrates the device-circuit technique to do the aforementioned IMP computation. Let us assume we have two vector input operands 'A' and 'B'. The bits 'A<sub>0</sub>' to 'A<sub>N</sub>' corresponding to the input 'A' are stored in upper row of the memory array as shown in Fig. 3.1(b). Similarly, bits 'B<sub>0</sub>' to 'B<sub>N</sub>' corresponding to the input 'B' are stored in lower row of the memory array. In order to do the bitwise IMP computations for operands 'A' and 'B' we would activate the corresponding word-lines WL-1 and WL-N. Simultaneously, a voltage  $V_{DD}$  would be applied to SL-1, while SL-N would be grounded resulting in a current flow as marked by the red arrow in Fig. 3.1(b). A simplified version of the resulting circuit configuration, considering one column consisting of one bit from the vector operand 'A' and corresponding bit from the vector operand 'B', is shown in Fig. 3.1(c).

Fig. 3.1(c) is basically a voltage divider, the voltage at node 'mid' depends on the resistance states of MTJ-1 and MTJ-2. Note, in this circuit configuration the pinned-layer of MTJ-1 has a lower voltage than the free-layer, while for MTJ-2 the pinned-layer is at a higher voltage than the free-layer. This in turn implies, with reference to Fig. 2.1(b), MTJ-1 has a higher energy barrier (EB) while MTJ-2 has a lowered energy barrier owing to the VCMA effect. As such, it is much easier to switch MTJ-2 while the state of MTJ-1 would remain intact due to increase in its EB. Further, the voltage at node 'mid' would be higher (lower) when MTJ-1 is in the P (AP) state due to the voltage-divider effect. By appropriate choice of  $V_{DD}$  and the MTJ resistances, the circuit in Fig. 3.1(c) can be designed such that MTJ-2 switches from the P to the AP state only when MTJ-1 is in the P state. A higher voltage at node 'mid' (corresponding to the P state of MTJ-1) would imply enhanced lowering of the EB for MTJ-2 allowing the small current flowing through the MTJ-2 to be able to deterministically switch the MTJ-2 from the P to the AP state as desired.