# TECHNIQUES FOR MANAGING IRREGULAR CONTROL FLOW ON GPUS

by

Jad Hbeika

## A Thesis

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical and Computer Engineering West Lafayette, Indiana May 2019

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Milind Kulkarni, Chair

School of Electrical and Computer Engineering

Dr. Timothy Rogers

School of Electrical and Computer Engineering

Dr. Samuel Midkiff

School of Electrical and Computer Engineering

Dr. Arun Prakash School of Civil Engineering

# Approved by:

Dr. Pedro Irazoqui Head of the Graduate Program I dedicate this work to my dad, Georges, my mom, Wadad, my brother, Imad, and my sister, Maya.

## ACKNOWLEDGMENTS

I would like to express my great appreciation to professor Milind Kulkarni, my advisor, for his valuable guidance, continuous encouragement, and patience. I could have not imagined having a better advisor ...

I would love also to thank the members of my PhD committee, Professor Samuel Midkiff, Professor Arun Prakash, and Professor Timothy Rogers, for their insightful comments and questions.

I thank my fellow lab mates for the simulating discussions and for all the fun we have had in the past years

This work was supported in part by the U.S. Department of Energy's (DOE) Office of Science, Office of Advanced Scientific Computing Research, Under DOE Early Career Award DE-SC0010295 and DOE DE-FC02-12ER26104

# TABLE OF CONTENTS

| LIST O | F FIGURES                                       |           |

|--------|-------------------------------------------------|-----------|

| ABSTR  | ACT                                             |           |

| 1. INT | FRODUCTION                                      |           |

| 1.1    | The Basics                                      |           |

| 1.2    | Breakdown of the Dennard Scaling and its Effect |           |

| 1.3    | From ILP to TLP                                 |           |

| 1.4    | Contributions                                   | 14        |

| 1.5    | Organization                                    |           |

| 2. OV  | VERVIEW: THE GPU ARCHITECTURE AND THE SIMT      | EXECUTION |

| MODE   | L                                               |           |

| 2.1    | GPU Architecture                                |           |

| 2.2    | Core Architecture                               | 19        |

| 2.3    | SIMT Stack                                      |           |

| 2.4    | Warp Scheduling                                 |           |

| 2.5    | Operand Collector                               |           |

| 3. CO  | NTROL DIVERGENCE IN THE LITERATURE              |           |

| 3.1    | Introduction                                    |           |

| 3.2    | Dynamic Warp Formation (DWF)                    |           |

| 3.3    | Thread Block Compaction (TBC)                   |           |

| 3.4    | Large Warp Microarchitecture (LWM)              | 40        |

| 3.5    | Simultaneous Warp Interweaving                  | 40        |

| 3.6    | Conditional Streams                             |           |

| 3.7    | SIMD Lane Permutation                           |           |

| 3.8    | Multi-Path Parallelism                          |           |

| 3.9    | Dynamic Warp Subdivision                        |           |

| 3.10   | Dual Path Execution and Multi Path Execution    |           |

| 3.11   | Likely Convergence Points                       |           |

| 3.12   | Vector Thread Architecture                      |           |

| 3.13   | Temporal SIMT                                   |           |

| 3.14  | Variable Warp Sizing                               |          |

|-------|----------------------------------------------------|----------|

| 3.15  | SIMT Stack Alternatives and Divergence Management: | 49       |

| 4. OP | PORTUNISTIC INTER-PATH RE-CONVERGENCE              | 52       |

| 4.1   | Introduction                                       | 52       |

| 4.2   | Background                                         | 54       |

| 4.3   | Opcode-Convergent Threads                          | 57       |

| 4.4   | Compiler Support                                   | 58       |

| 4.5   | ISA Support                                        |          |

| 4.6   | Scoreboard Modifications                           | 63       |

| 4.7   | SIMT Stack Modifications                           | 65       |

| 4.8   | Register File Modifications                        | 68       |

| 4.9   | Nested Divergence                                  | 68       |

| 5. OP | PORTUNISTIC INTER-PATH RE-CONVERGENCE IMPLEM       | ENTATION |

| AND R | ESULTS                                             | 70       |

| 5.1   | Methodology                                        | 70       |

| 5.2   | Experimental Results                               |          |

| 5.3   | Conclusion                                         | 75       |

| 6. LO | CALITY-AWARE TASK-PARALLEL EXECUTION ON GPUS       |          |

| 6.1   | Introduction                                       | 76       |

| 6.2   | Related Works                                      | 78       |

| 6.3   | Background and Motivation                          | 80       |

| 6.3   | .1 GPU Architecture and Limitations                | 80       |

| 6.3   | 2 Task Parallelism                                 | 83       |

| 6.4   | Data Parallel GPU Execution of Task Parallel Code  |          |

| 6.4   | 1 Basic Technique                                  |          |

| 6.4   | 2 Generating GPU Task Queues                       | 86       |

| 6.4   | .3 Mixing Data Parallelism and Task Parallelism    |          |

| 6.5   | Scheduling for Locality                            |          |

| 6.6   | Implementation                                     |          |

| 6.6   | .1 Determining the Queue Threshold                 |          |

| 6.6   | 2 Queue Merging                                    | 91       |

| 6.6.3    | Queue Size Reduction  | 91 |

|----------|-----------------------|----|

| 6.7 Eva  | aluation              |    |

| 6.7.1    | Fast Multipole Method |    |

| 6.7.2    | Point Correlation     |    |

| 6.7.3    | Nearest-Neighbor      |    |

| 6.8 Co   | nclusion              |    |

| APPENDIX | A                     |    |

| APPENDIX | B                     |    |

| REFERENC | ES                    |    |

|          |                       |    |

# LIST OF FIGURES

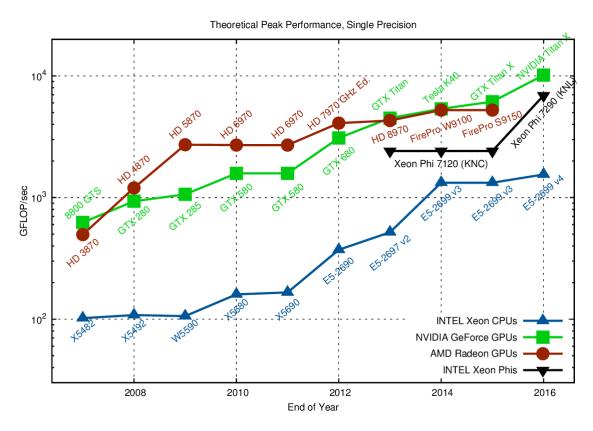

| Figure 1: Theoretical peak GFLOP/sec for CPU vs GPU [36]                        | 14       |

|---------------------------------------------------------------------------------|----------|

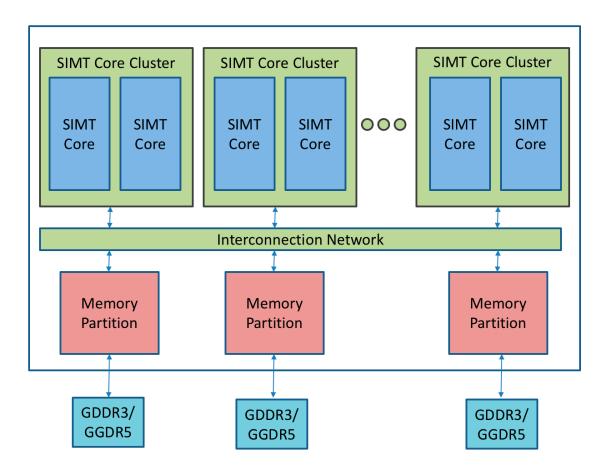

| Figure 2: A generic GPU architecture                                            | 17       |

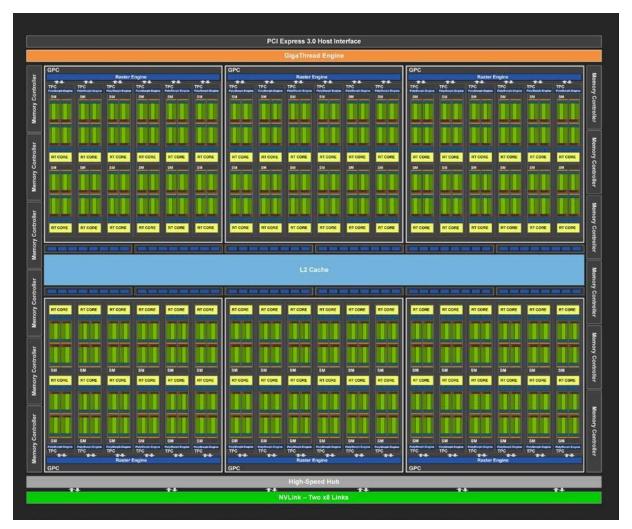

| Figure 3: Turing TU102 full GPU with 72 SM units.                               | 18       |

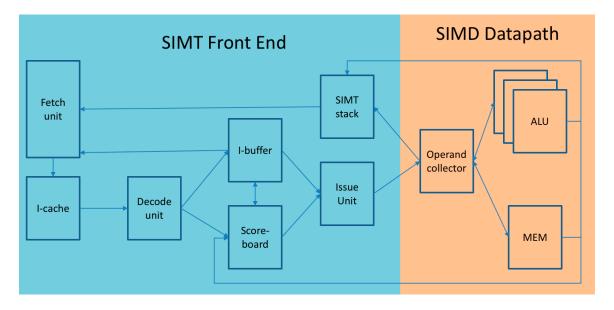

| Figure 4: Microarchitecture of a generic GPGPU core                             | 19       |

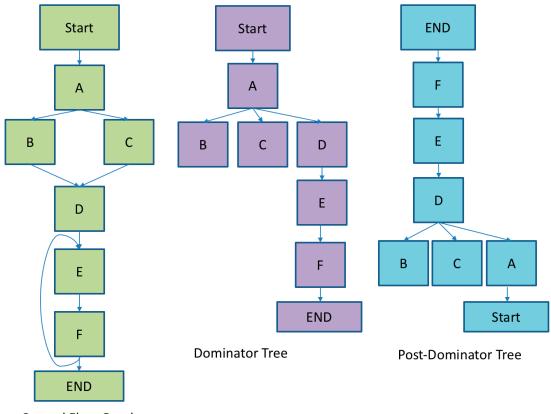

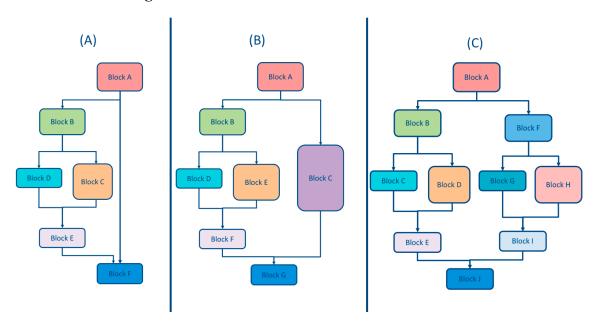

| Figure 5: (A) Control flow graph. (B) Dominator tree (C) Post dominator tree    |          |

| Figure 6: Example CUDA source code                                              |          |

| Figure 7: Example PTX assembly code                                             |          |

| Figure 8: CFG of the sample code shown in fig 6                                 | 25       |

| Figure 9: Different states of the SIMT stack                                    | 25       |

| Figure 10: Timeline of the execution                                            |          |

| Figure 11: Architecture of naïve banked register file                           |          |

| Figure 12: Issue time of different instructions                                 |          |

| Figure 13: Distribution of registers across the banks of the register file      |          |

| Figure 14: Operand collector microarchitecture (based on Tor M. Aamodt)         | 30       |

| Figure 15: Timeline of accessing a naive register file                          |          |

| Figure 16: Timeline of accessing the operand collector                          |          |

| Figure 17: DWF example: 2 CFGs showing 2 warps diverging differently            | 34       |

| Figure 18: DWF example: (A) Basic Blocks executed by warp 1. (B) Basic Blocks   | executed |

| by warp 2. (C) Execution Flow of 2 warps                                        | 34       |

| Figure 19: DWF example : Warp compaction                                        |          |

| Figure 20: DWF example: Execution flow using DWF                                | 35       |

| Figure 21: DWF example: The effect of Memory divergence                         | 35       |

| Figure 22: Register file of DWF (based on Figure 10 from Fung et al. [6])       |          |

| Figure 23: High level operation of TBC                                          |          |

| Figure 24: TBC execution Time (based on Figure 7 from Fung et al. [7])          |          |

| Figure 25: Simultaneous Branch Interweaving micro-architecture (based on Figure | e 3 from |

| Brunie et al.)                                                                  | 41       |

| Figure 26: DPE example: Control Flow Graph                                      |          |

| Figure 27: DPE example: Execution flow                                          | 43       |

| Figure 28: Dynamic Warp Subdivision example                                        | 44       |

|------------------------------------------------------------------------------------|----------|

| Figure 29: CFG annotated with path probabilities                                   | 46       |

| Figure 30: SIMT stack of the Likely convergence example (based on Figure 3.1       | 9 from   |

| Aamodt et al.)                                                                     | 47       |

| Figure 31: Abstract model of a vector-thread architecture (base on Figure 1 of Kra | shinsky  |

| et al.)                                                                            | 48       |

| Figure 32: Temporal SIMT micro-architecture (based on Figure 1 from Keckler et     | al.). 49 |

| Figure 33: (B) Baseline CFG. (C) CFG using predication                             | 51       |

| Figure 34: (A) CFG of original code VS (B) CFG of transformed code                 | 55       |

| Figure 35: The different states of the SIMT stack                                  | 56       |

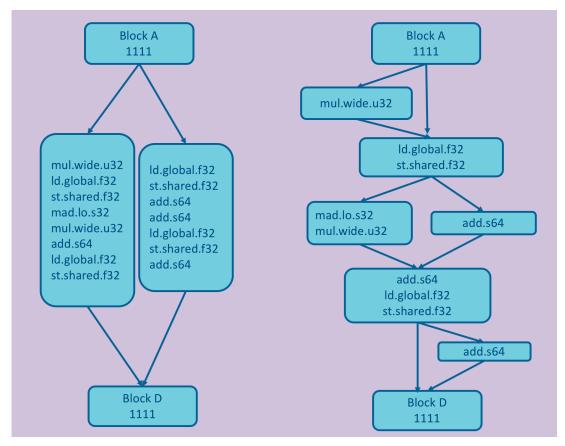

| Figure 36: (A) CFG and its corresponding transformed CFG (B)                       | 60       |

| Figure 37: LCS table and its corresponding CFG                                     | 60       |

| Figure 38: LCS applied to divergent blocks in Cholesky                             | 61       |

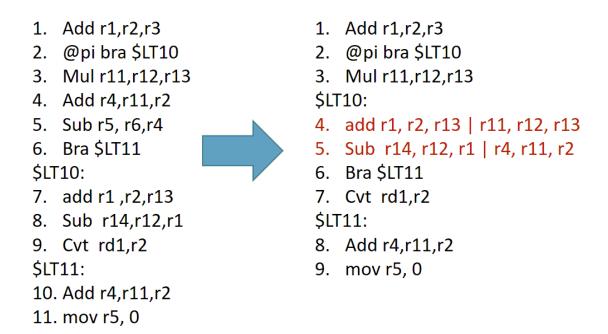

| Figure 39: Original piece of code VS its transformed version                       | 62       |

| Figure 40: Transformed CFG shows a false data dependency                           | 63       |

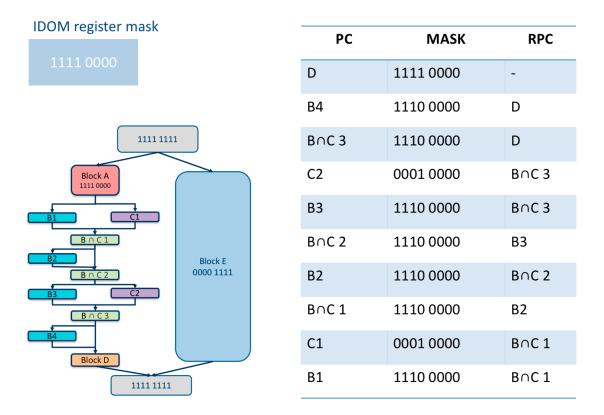

| Figure 41: The modified SIMT stack upon divergence at end of block A               | 66       |

| Figure 42: Re-convergence stack of <i>opcode_convergent_threads</i>                | 67       |

| Figure 43: Nested Divergence Scenarios                                             | 68       |

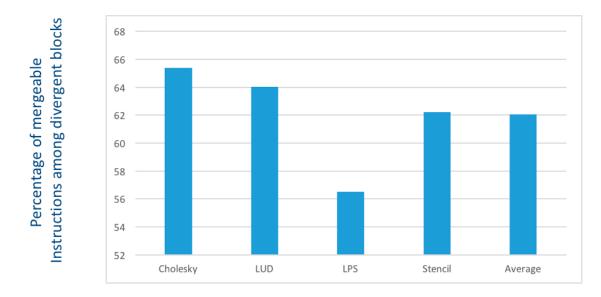

| Figure 44: Static analysis: Percentage of mergeable instructions                   | 72       |

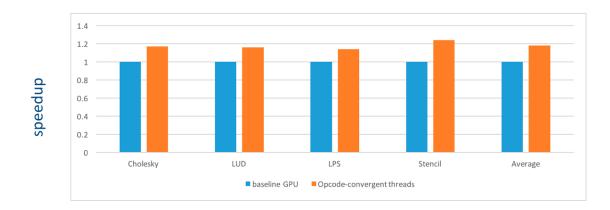

| Figure 45 : Speedup upon exploiting opcode convergence                             | 73       |

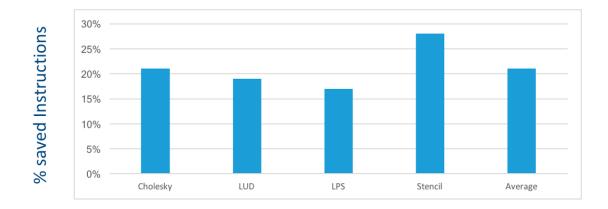

| Figure 46: Percentage of saved instructions                                        | 74       |

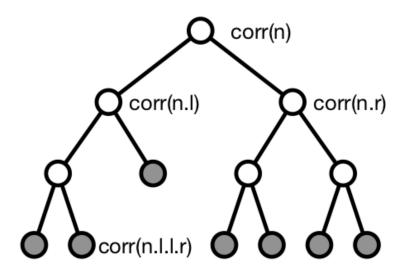

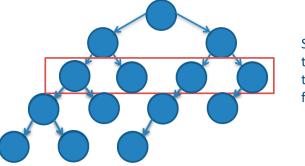

| Figure 47: Task-parallel implementation of point correlation                       | 82       |

| Figure 48: Computation tree for point-Correlation                                  | 83       |

| Figure 49: Partial expansion of the computation tree by the CPU                    | 85       |

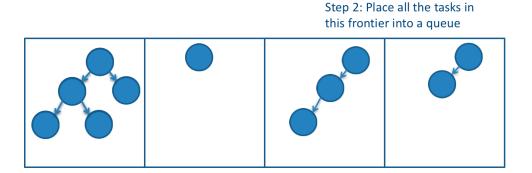

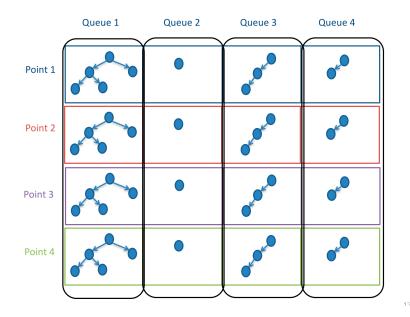

| Figure 50: Different tasks are assigned to different queues                        | 85       |

| Figure 51: Transformed point correlation algorithm to enable GPU task queue        | 86       |

| Figure 52: Locality aware queue                                                    | 90       |

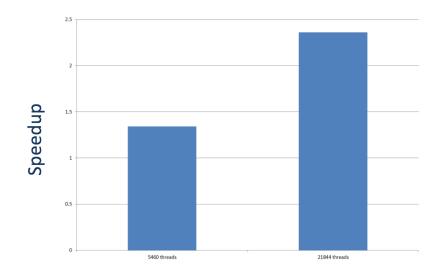

| Figure 53: Speedup of locality-aware FMM over locality-agnostic FMM                | 93       |

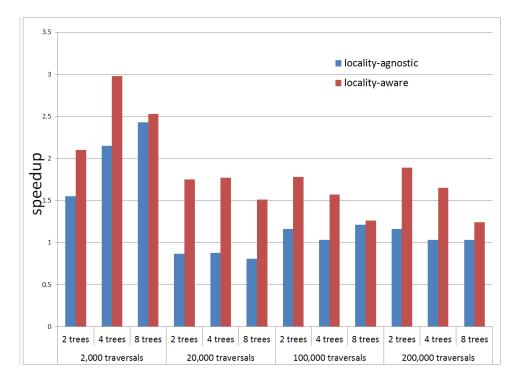

| Figure 54: Speedup of PC over data-parallel GPU baseline                           | 94       |

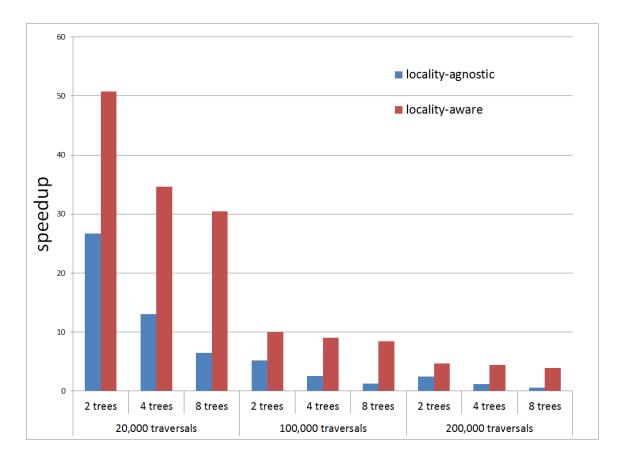

| Figure 55: Speedup of NN over data-parallel GPU baseline                           | 95       |

| Figure 56: LCS example                                                             | 96       |

### ABSTRACT

Author: Hbeika, Jad. PhD Institution: Purdue University Degree Received: May 2019 Title: Techniques for Managing Irregular Control Flow on GPUs Committee Chair: Milind Kulkarni

GPGPU is a highly multithreaded throughput architecture that can deliver high speed-up for regular applications while remaining energy efficient. In recent years, there has been much focus on tuning irregular applications and/or the GPU architecture to achieve similar benefits for irregular applications as well as efforts to extract data parallelism from task parallel applications. In this work we tackle both problems.

The first part of this work tackles the problem of Control divergence in GPUs. GPGPUs' SIMT execution model is ineffective for workloads with irregular control-flow because GPGPUs serialize the execution of divergent paths which lead to thread-level parallelism (TLP) loss. Previous works focused on creating new warps based on the control path threads follow, or created different warps for the different paths, or ran multiple narrower warps in parallel. While all previous solutions showed speedup for irregular workloads, they imposed some performance loss on regular workloads. In this work we propose a more fine-grained approach to exploit *intra-warp* convergence: rather than threads executing the same code path, opcode-convergent threads execute the same instruction, but with potentially different operands. Based on this new definition we find that divergent control blocks within a warp exhibit substantial opcode convergence. We build a compiler that analyzes divergent blocks and identifies the common streams of opcodes. We modify the GPU architecture so that these common instructions are executed as convergent instructions. Using software simulation, we achieve a 17% speedup over baseline GPGPU for irregular workloads and do not incur any performance loss on regular workloads.

In the second part we suggest techniques for extracting data parallelism from irregular, task parallel applications in order to take advantage of the massive parallelism provided by the GPU. Our technique involves dividing each task into multiple sub-tasks each performing less work and touching a smaller memory footprint. Our framework performs a locality-aware scheduling that works on minimizing the memory footprint of each warp (a set of threads performing in lock-step). We evaluate our framework with 3 task-parallel benchmarks and show that we can achieve significant speedups over optimized GPU code.

#### **1. INTRODUCTION**

#### 1.1 The Basics

GPUs were initially developed to enable real-time rendering in video games. While graphic acceleration is still among its main purpose, GPUs proved to be efficient in different computation domains and today we can find GPUs in many systems like: supercomputers, datacenters, laptops and even smart phones. The use of GPUs as general purpose computation platforms started around the year 2006 with the breakdown of the Dennard scaling.

#### **1.2** Breakdown of the Dennard Scaling and its Effect

While improvements in architecture, microarchitecture, compilers and algorithms all led to computer systems increased performance over the last decades, the major improvements can be contributed to transistor scaling which allowed drastic raise in clock frequencies.

Dennard (1974) [1] concluded that voltage and current should be proportional to dimensions of a transistor. As transistors were scaling down in size the reduction of voltage allowed running circuits at higher frequency while keeping the dynamic power the same.

Power = $\alpha CFV^2$

C: capacitance

F: frequency

V: voltage

Alpha: percent rime switched

Dennard scaling ignored the leakage current and threshold voltage which could not be reduced further as transistor size were scaling further down. This created a "Power wall" that limited CPUs clock frequencies to around 4 GHZ around 2006.

Improving performance beyond this point relies mainly on new efficient architectures and the use of hardware accelerators. Since the "power wall" Multicore systems as well as the use of GPUs outside of the graphics world became hot research topics.

#### **1.3** From ILP to TLP

For decades the main approach in exploiting parallelism was through extracting instruction level parallelism (ILP) from a single thread. Extracting ILP requires complex scheduling logic, branch prediction, larger caches etc. and aims at speeding up the execution of a single thread.

Over the recent years the attention shifted toward exploiting thread level parallelism (TLP) due to the diminished returns of further exploiting ILP [2]. Thread level parallelism relies on

- Software developer's effort to write their applications as a set of threads that can execute in parallel

- 2) Hardware support that allows execution of these threads in parallel

GPUs offer a throughput oriented architecture, that exploit TLP through fine grain multithreading. As shows in Figure 1, GPUs offers a high theoretical computation power compared to conventional CMPs. This theoretical computation power coupled with the programmability that improved with the introduction of new programming models opened new opportunities to speed up performance. Note that the margin between the theoretical peak GFLOP/sec of GPUs and CPUs shown in Figure 1 did shrink with the introduction of Xeon CPUs (2012) which are based on the Sandy bridge architecture and the introduction of dual-issue floating point units (2014).

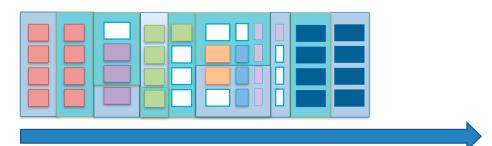

The order of magnitude of speedup that GPUs offer over CPUs for regular applications does not hold for irregular applications. GPUs batch a group of threads and execute the batch, known as a *warp*, in lockstep in order to amortize the cost of fetch, decode and accessing the register files. Applications with threads following different control paths are known as *irregular applications*. Irregular applications, when running on a GPU, alter the lockstep execution since different threads follow different paths. Baseline GPUs serialize the execution of diverging threads within a warp, resulting in TLP loss. Hence, a major challenge for GPUs is efficiently handling irregular control flow.

Figure 1: Theoretical peak GFLOP/sec for CPU vs GPU [36]

#### 1.4 Contributions

The contributions of this thesis can be divided into two main parts:

- The contributions of the first part titled "Opportunistic Inter-Path Reconvergence" are:

- a. We propose a more fine-grained approach to exploit *intra-warp* convergence by introducing the concept of *opcode-convergent threads* which execute the same instruction, but with potentially different operands.

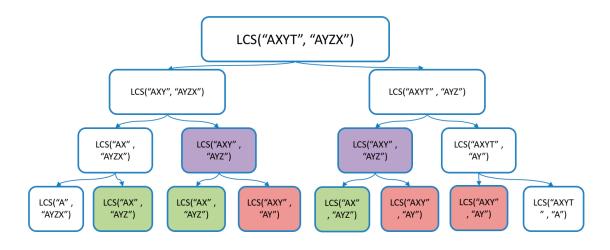

- b. We develop a compiler analysis based on longest common subsequence (LCS) [40] that identifies opcode convergence among divergent basic blocks and annotates the code so that it runs on our modified architecture.

- c. We modify the GPU architecture so that opcode convergent instructions are executed as convergent instructions.

- d. We quantify the percentage of common sub-blocks that exist among divergent basic blocks in a set of irregular GPU applications.

- e. Using software simulation, we run irregular GPGPU workloads taking advantage of opcode convergence and we achieve 17% speedup over baseline architecture without introducing any performance loss on regular workloads.

- The contributions of the second part titled "Locality-aware task-parallel execution on GPUs" are:

- a. We propose a locality-aware, task-queue abstraction for mapping taskparallel applications to GPUs.

- i. The proposed technique first extract data parallelism from the task parallel application by expanding task parallel work on the CPU} to generate a large number of tasks.

- ii. These tasks are then inserted into one or more task queues according to the type of computation they perform and, crucially, the locality properties of the tasks.

- iii. These queues are then merged into a single queue that is sent to the GPU, where they are executed in a data-parallel manner, with each task executing to completion on the GPU.

- b. We evaluate this queue abstraction on three applications: the fast multipole method, nearest-neighbor and two-point correlation. Our technique shows significant speedup for all three applications. And it yields to 50x speedup for one implementation of nearest neighbor.

#### 1.5 Organization

The rest of the thesis is organized as follows:

- Chapter 2 provides a detailed discussion of the GPU architecture and the SIMT execution model.

- Chapter 3 provides an overview of the previously suggested solutions to the problem of control divergence in the literature.

- Chapter 4 describes our proposed solution "Opportunistic Inter-Path Reconvergence".

- Chapter 5 describes the simulation methodology, the three tools that we built (or modified in case of GPGPU-sim) and our experimental results.

- Chapter 6 is dedicated for our work on "Locality-aware task-parallel execution on GPUs", where we explain the proposed idea, the implementation and show the results of three task parallel applications.

# 2. OVERVIEW: THE GPU ARCHITECTURE AND THE SIMT EXECUTION MODEL

## 2.1 GPU Architecture

Figure 2: A generic GPU architecture

GPUs are throughput oriented machines; in other words, they get their improved performance, compared to superscalar out of order CPUs, from using heavy multithreading. In order to run thousands of threads, GPUs are made of many cores. Figure 3 below shows a modern Turing TU102 GPU by NVIDIA, which consist of 72 cores. A core in a GPU is usually made up of 32 (or 64) lanes which allows running 32(or 64) threads in lockstep in any given cycle. By context switching between different warps a set of 32(or 64) threads executing in lockstep each core in a GPU is capable of running thousands of threads. Threads executing on a given core can communicate results through a scratchpad memory. Moreover, different warps running on a given core can synchronize using fast barrier operations. Each core has its own instruction cache and L1 data cache. Memory uses multiple channels in order to increase the data transfer rate. The parallelism in the memory system is a must in order to sustain the high computation throughput. The GPU cores and memory partitions are connected via an on-chip interconnection network.

Figure 3: Turing TU102 full GPU with 72 SM units.

## 2.2 Core Architecture

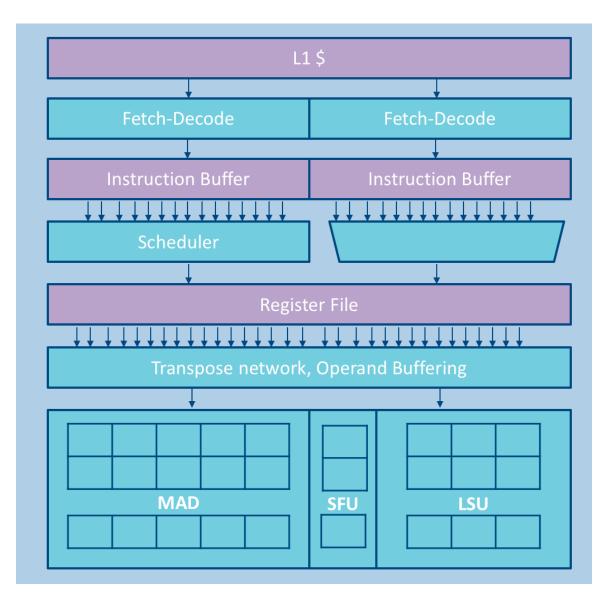

GPGPU cores are simpler cores than the cores used in a CPU. They do not implement any of the fancy architecture features that speedup the execution of single threads (i.e. no out of order execution, branch prediction, big caches). The high performance of regular applications running on GPUs is achieved through multithreading, as we mentioned earlier. Figure 4 shows the microarchitecture of a generic GPGPU core. Below is an explanation of each of the modules.

Figure 4: Microarchitecture of a generic GPGPU core

As discussed previously the threads are grouped in warps, consisting of 32 threads (usually) that execute in lockstep. A core will have multiple warps at any given time waiting to be scheduled. Each cycle, a warp is selected for scheduling. Having multiple warps helps hide long execution latencies. In other words, when a warp is waiting for an access to off chip memory, the core will be running different warps. Unfortunately, the number of warps that can "live" concurrently on a core is limited by the resources. A warp must ensure that the core has enough resources and registers before it starts executing.

Given that number of warps that can co-exist is limited by the resources available, and that we would like to hide latencies of long instructions, it becomes helpful if we can schedule subsequent instruction from a warp while earlier instructions from the same warp have not yet completed. For this to be possible we need to know whether the next instruction of a warp is dependent on an earlier instruction that has not yet finished. This dependency information requires fetching the instruction from memory and decoding it to check whether it has such dependency. For this reason, GPUs use what is called an instruction buffer. Upon a cache fill or hit the instruction information is placed into the instruction buffer. The i-buffer haS dedicated slots for each warp. GPUs make use of a *scoreboard* to detect the dependencies. One naïve option of implementing the scoreboard would be to represent each register by one bit in the scoreboard and upon read or write each instruction checks the corresponding bits and if they are set to one the instruction is stalled. Unfortunately, this simple solution is not practical in GPUs because each warp in a GPU has 128 registers and a core can run up to 64 warps simultaneously, which means we need 8192 bits for the scoreboard. Moreover, because of the high number of warps running on a core, it could be that each warp has some instructions waiting on any of its four operands which means we may have up to 64(number of warps) \*4(number of operands) = 256 scoreboard probes every cycle which would require 256 read ports.

A more feasible implementation would dedicate some entries in the scoreboard for each warp, usually around four entries. Upon fetching an instruction and placing it in the i-buffer, the scoreboard entries corresponding to the instruction's warp are checked. If any of the instructions' operands matches the scoreboard entry, then a ready bit in the buffer is set to 0 which means that the corresponding operand is not yet ready. when the entry is cleared from the scoreboard upon write back the ready bit in the i-buffer is set to 1. Once all the operands for a specific instruction in the i-buffer are ready. the scheduler starts considering the instruction for issuing.

Note that in the considered architecture, there are two scheduling decisions. The first is to select a warp and fetch its next instruction from the instruction cache and send it to the i-buffer. Usually this is done in a round robin manner among the warps that have no valid entries in the i-buffer. The second scheduling decision is selecting the instruction to be issued. This scheduler must select an instruction from the ready instructions in the i-buffer. Warp scheduling will be discussed in more detail in section 2.4.

Note that in the case of the GPGPU-sim simulator that we use to run my experiments, the i-buffer dedicates two entries per warp. Each i-buffer entry has two control bits, namely: a ready bit and a valid bit. The later indicates that the instruction is decoded but not yet issued. While the ready bit is set to 1 if the valid instruction is ready for execution, in other words if the data dependencies for this instruction are met and the instruction is ready to be issued.

The SIMT (single instruction multiple threads) execution model, used in GPU, provides the abstraction that each thread execute completely independently. This programming model is achieved via the use of a SIMT stack along with predication.

**Control Flow Graph**

Figure 5: (A) Control flow graph. (B) Dominator tree (C) Post dominator tree.

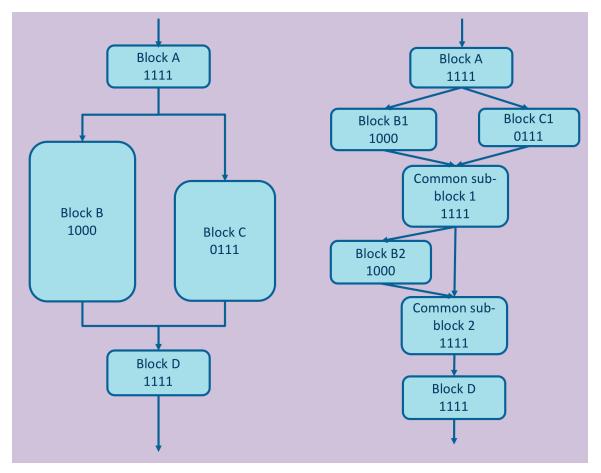

As mentioned previously, threads in a warp execute in lockstep. However, upon a branch instruction different threads in a warp can follow different control path. This scenario is known as control divergence. Current GPUs handle control divergence by

serializing execution of threads that follow different control paths. While upon divergence it is possible for thread to stay divergent until the end of the program, this solution is not efficient. Hence, divergent threads in a GPU will try re-converge at the earliest possible opportunity. The *immediate post dominator* is the earliest re-convergence point that can be guaranteed at compile time. Note that some works [7] in the literature looked at earlier possible re-convergence points that can be defined at run-time.

The definition of post dominator is: an instruction 'b' is considered a post dominator of an instruction 'a' if every path from instruction 'a' to the end of the program has to go through 'b'. The immediate post dominator (IPDOM) is first instruction in the code that post dominates instruction 'a'.

#### 2.3 SIMT Stack

It is through the use of a *SIMT stack* that GPUs handle serialized execution of divergent threads, re-convergence as well as the execution of nested branches. Figure 6 shows a CUDA code excerpt (Figure 7 shows its assembly equivalent). Different warp threads could diverge at the 'if' statement of line 6 as well as at line 8 at the nested 'if' statement. Figure 8 represents the control flow graph of this code excerpt. Note that the numbers in each basic block box of this control flow graph represent the mask of the threads of the currently running warp. A bit set to one represents the thread that actually execute the block while a bit set to zero represents a thread skipping the execution. Figure 9 represents the case where the execution is within basic block A and where all the bits of the mask are set to 1, which means that all the threads are executing this basic block. Once we reach the conditional statements at the end of basic block A, threads 1 through 3 take the branch while thread 4 goes in the fall through direction.

Upon this divergence we insert in the SIMT stack two new entries corresponding to the different paths that the threads are following (Figure 9a). Upon the insertion of these entries, threads 1,2,3 start executing block B while thread 4 is waiting. Every cycle, we compare the current PC to the re-convergence PC at the top entry of the SIMT stack. If the two PCs are equal we pop this entry of the SIMT stack, since the divergent block would have reached its re-convergence point. Once we reach the end of basic block B we have another conditional statements and now the threads diverge again with thread 1 taking the jump while threads 2 and 3 going in the fall through direction.

Upon this 'nested' divergence, the SIMT stack is updated by popping the top entry and pushing three new entries representing basic blocks C, D, and E with their corresponding masks (Figure 9b). the execution continues with block C which is popped from the stack when it reaches its re-convergence point next block D is executed for threads 2 and 3 until it reaches its re-convergence PC. Figure 9c shows the SIMT stack while the program is executing block E which eventually will reach its re-convergence point and have its entry popped from the SIMT stack. At this point the execution will move to block F, and eventually all the threads will re-converge again once basic block F is done.

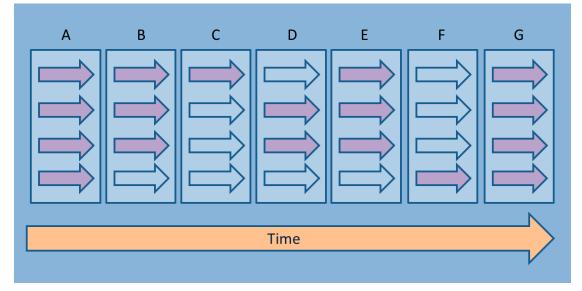

Figure 10 shows the serialized execution of threads upon divergence. it also shows the decreased lane utilization and the inefficiency of the SIMT programing model for applications with irregular control flow.

The literature describes different implementations of the SIMT stack which can be managed in software through the use of special dedicated instructions [37] or in hardware [6], [7]. In this work we consider the SIMT stack managed fully by hardware mainly because the SIMT stack in the simulator used in this work is hardware managed.

| 1.  | Do {                                          |     |  |

|-----|-----------------------------------------------|-----|--|

| 2.  | T1=tid*4;                                     | //A |  |

| 3.  | T2=T1+I;                                      |     |  |

| 4.  | T3=DATA1[T2];                                 |     |  |

| 5.  | T4=0;                                         |     |  |

| 6.  | IF(T3 != T4) {                                |     |  |

| 7.  | T5=DATA2[T2];                                 | //B |  |

| 8.  | IF(T5 != T4) {                                |     |  |

| 9.  | X +=1;                                        | //C |  |

| 10. | } ELSE {                                      |     |  |

| 11. | Y +=2;                                        | //D |  |

| 12. | }                                             |     |  |

| 13. | } ELSE{                                       |     |  |

| 14. | Z +=3;                                        | //F |  |

| 15. | }                                             |     |  |

| 16. | <i>l++;</i>                                   | //G |  |

| 17. | }WHILE (I <n)< td=""><td></td><td></td></n)<> |     |  |

|     |                                               |     |  |

Figure 6: Example CUDA source code

| 1.  | A: | mul.lo.u32    | t1, tid, N; |

|-----|----|---------------|-------------|

| 2.  |    | add.u32       | t2, t1, l;  |

| 3.  |    | ld.global.u32 | t3, [t2];   |

| 4.  |    | mov.u32       | t4, 0;      |

| 5.  |    | setp.eq.u32   | p1, t3, t4; |

| 6.  |    | @p1 bra       | F;          |

| 7.  | B: | ld.global.u32 | t5, [t2];   |

| 8.  |    | setp.eq.u32   | p2, t5, t4; |

| 9.  |    | @p2 bra       | D;          |

| 10. | C: | add.u32       | x, x, 1;    |

| 11. |    | bra           | E;          |

| 12. | D: | add.u32       | y, y, 2;    |

| 13. | E: | bra           | G;          |

| 14. | F: | add.u32       | z, z, 3;    |

| 15. | G: | add.u32       | I, I, 1;    |

| 16. |    | setp.le.u32   | p3, I, N;   |

| 17. |    | @p3 bra       | A;          |

|     |    |               |             |

Figure 7: Example PTX assembly code

Figure 8: CFG of the sample code shown in fig 6

| RPC | Next PC | Active Mask |     |

|-----|---------|-------------|-----|

| -   | G       | 1111        |     |

| G   | F       | 0001        | 9-A |

| G   | В       | 1110        |     |

| RPC | Next PC | Active Mask |     |

| -   | G       | 1111        |     |

| G   | F       | 0001        |     |

| G   | E       | 1110        | 9-B |

| E   | D       | 0110        |     |

| E   | C       | 1000        |     |

| RPC | Next PC | Active Mask |     |

| -   | G       | 1111        |     |

| G   | F       | 0001        | 9-C |

| G   | E       | 1110        |     |

Figure 9: Different states of the SIMT stack

Figure 10: Timeline of the execution

#### 2.4 Warp Scheduling

As mentioned earlier, GPUs are throughput oriented machines that use simple cores and heavy multithreading in order to hide the latency of slow memory operations. Two questions that arise are how many warps should live on a core at the same time so that the core remains busy at all time? And how should the warps be scheduled? The answer to both question would be simple if the memory system is ideal and responds to memory requests within a fixed time. If this were the case we could simply find out the number of needed warps by using a round robin scheduling algorithm to schedule the warps. The round robin scheduling will allow roughly equal time for each warp before being re-scheduled. Hence the minimum number of warps required to keep the core busy would be equal to the latency of the slowest instruction. However, the memory system is not ideal and the response to memory requests depends on the locality properties of the application. Furthermore, allowing a different warp to execute every cycle requires that each warp has its own registers. Otherwise we have to copy the state of the warp back and forth every time it is scheduled which is both energy and time consuming. The requirement of having dedicated registers for each running warp puts a limit on the number of warps that can live concurrently on a core because otherwise the chip area devoted for the registers will increase relative to the chip area devoted for the functional units which will limit the computation power of the chip. Thus the number warps is

limited by the resources and that is why GPUs allow scheduling instructions from the same warp even if previous instructions from the same warp have not finished executing. This will allow better hiding of latencies without increasing the number of warps and hence without increasing the number of required registers.

Since not all latencies can be hidden due to the limited number of warps that can live concurrently on a core, it becomes important to pick the scheduling algorithm that results in the least cache misses, i.e. a scheduling algorithm that takes advantage of locality. This has been the topic of considerable research. when different warps access nearby data at a similar point in the execution, it becomes beneficial that all these warps make equal progress to take advantage of the locality. Round robin warp scheduling can help taking advantage of locality in this case [3].

However, when different warps access disjoint data, like in the case of recursive tree based algorithms, it may be beneficial that a warp get scheduled repeatedly to maximize locality within the warp [4].

#### 2.5 Operand Collector

Switching between warps every cycle requires physical registers to be devoted for each warp in order not to waste time and energy on moving state between memory and the register file. Devoting physical registers to each warp makes the register file big, it is almost 256 KB on recent GPUs like Kepler from NVIDIA.

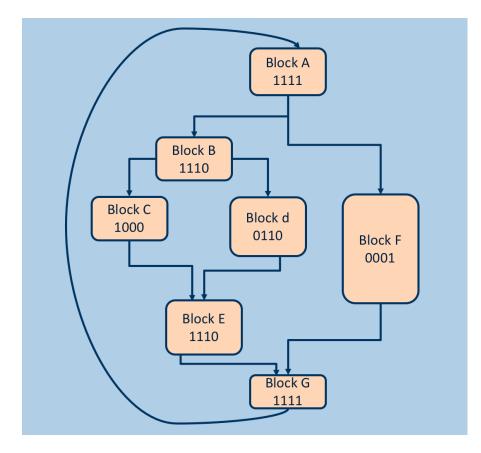

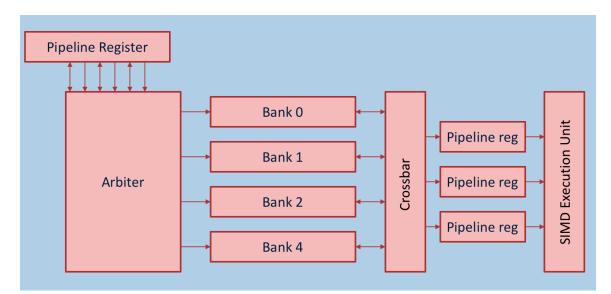

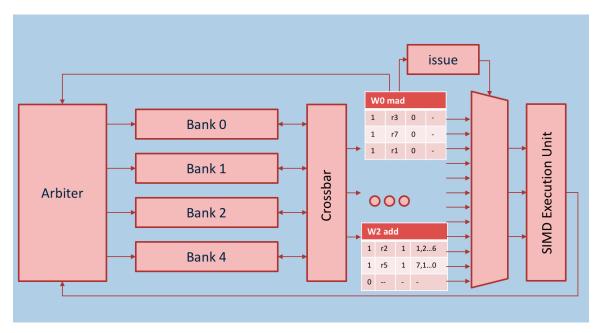

One way to reduce the area of the register file is to use multiple banks of singleported memories. GPUs use an operand collector to manage collecting the operands from the register file. The role of the operand collector is to help increase the bank level parallelism. This will be explained through the following example. Let us first consider we do not have operand collectors and that we just have a banked register file like the one shown in Figure 11.

Figure 11: Architecture of naïve banked register file

In this microarchitecture we have 4 banks where each has a single port connected to a crossbar which route results to the pipeline registers. While this naïve microarchitecture will work fine, it will hurt performance due to little bank parallelism. To illustrate this let us consider having four warps running, the code show in the Figure 12 and let us consider the register layout shown in Figure 13

| Cycle | Warp | Instruction        |

|-------|------|--------------------|

| 0     | w0   | mad r1, r2, r4, r6 |

| 1     | w1   | mad r1, r2, r4, r6 |

| 2     | w2   | mad r1, r2, r4, r6 |

| 3     | w3   | mad r1, r2, r4, r6 |

Figure 12: Issue time of different instructions

| Bank 1 | Bank 2 | Bank 3 | Bank 4 |

|--------|--------|--------|--------|

| w0: r1 | w0: r2 | w0: r3 | w0: r4 |

| w0: r5 | w0: r6 | w0: r7 | w1:r1  |

| w1:r2  | w1:r3  | w1:r4  | w1:r5  |

| w1:r6  | w1:r7  | w2:r1  | w2:r2  |

| w2:r3  | w2:r4  | w2:r5  | w2:r6  |

| w2:r7  | w3:r1  | w3:r2  | w3:r3  |

| w3:r4  | w3:r5  | w3:r6  | w3:r7  |

Figure 13: Distribution of registers across the banks of the register file

In clock cycle 1, warp zero instruction 1 can access both registers r2 and r4 however it cannot access register r6 because there is bank conflict with r2. In clock cycle 2, warp 0 accesses its last operand and now is ready to execute. In cycle 3, warp one accesses register r2 and r4 and again it cannot access r6 due to a conflict at bank 1. In cycle 4, warp 1 still cannot access r6 because the write of warp 0 conflict in bank 1 and the write has priority over the read. In cycle 5, warp 1 accesses register 6 and now it is ready to compute.

Now that warp 1 has all its operands, warp 2 can start accessing its operands, and it does access r4 and r6 at clock cycle. Warp r2 cannot access r2 in the same cycle due to a bank conflict in bank 4. In cycle 7, warp 2 still cannot access its 3<sup>rd</sup> operand due to the higher priority of the write of warp 1, which has a bank conflict with the read of r2 needed by warp 2. In cycle 8, warp 2 access its last operand and it is ready to issue. In cycle 9, warp 3 only accesses two of its operands and cannot access the 3<sup>rd</sup> due to bank conflict. In cycle 10, warp 2 writes its result to bank 3, which bans warp 3 from accessing its third operand. in cycle 11, warp 3 access its last operands and issues. Warp three writes its result back at cycle 13.

While this microarchitecture works fine, it is inefficient in terms of taking advantage of bank parallelism. GPUs use an operand collector which is similar to the architecture shown in Figure 14

Figure 14: Operand collector microarchitecture (based on Tor M. Aamodt)

The major difference between this new microarchitecture and the previous one shown in Figure 11 is the presence of the collector units. Each issued instruction will be given one collector unit to collect its operands. This will allow multiple instructions to collect their operands in parallel and hence will take advantage of bank parallelism. Given the same example discussed above for the naïve microarchitecture, if we use the collector unit microarchitecture we get a 62% speedup. In cycle 1, only warp 0 has issued and warp 0 will read its first operand. In cycle 2, warp 0 reads its second operand and at the same time warp 1 can read r2 since it does not conflict with the bank that warp 0 is reading from. In cycle 3, warp 0 reads its third operand and is ready to execute, while warp 1 reads r6 and warp 2, which just issued, reads its first operand, r4. In cycle 4, warp 1 reads r4 and is ready to execute, warp 2 reads its second operand, which is r6, and warp 3, which just issued, reads its first operand, r4. In cycle 5, warp 0 writes back its result, warp 2 reads r2 from bank4, and warp 3 reads r2 from bank 3. In cycle 6, warp 1 writes its result while warp 3 reads its 3<sup>rd</sup> and last operand. In cycle 7, warp 2 writes its result and in cycle 8, warp 3 writes its result. In total the execution took 8 cycles while in the case of the naïve microarchitecture it took 13 cycles. Figure 15 and Figure 16 shows the timing in the naïve microarchitecture and of the operand collector respectively.

|      |       | Cycle |       |       |       |       |       |       |       |       |       |    |       |

|------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|----|-------|

| Bank | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11    | 12 | 13    |

| 4    | w0:r4 |       |       |       |       | w2:r6 | w1:r1 | w2:r2 |       |       |       |    |       |

| 3    |       |       | w1:r4 |       |       |       |       |       | w3:r2 | w2:r1 | w3:r6 |    |       |

| 2    | w0:r2 | w0:r6 |       |       |       | w2:r4 |       |       |       |       |       |    |       |

| 1    |       |       | w1:r2 | w0:r1 | w1:r6 |       |       |       | w3:r4 |       |       |    | w3:r1 |

Figure 15: Timeline of accessing a naive register file

|        | Cycle |       |       |       |       |       |       |       |  |  |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|

|        | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     |  |  |

| Bank 4 |       |       | w0:r4 | w2:r6 | w2:r2 | w1:r1 |       |       |  |  |

| Bank 3 |       |       |       | w1:r4 | w3:r2 | w3:r6 | w2:r1 |       |  |  |

| Bank 2 | w0:r2 | w0:r6 | w2:r4 |       |       |       |       |       |  |  |

| Bank 1 |       | w1:r2 | w1:r6 | w3:r4 | w0:r1 |       |       | w3:r1 |  |  |

Figure 16: Timeline of accessing the operand collector

Note that each collector unit has space to buffer all source operands of the allocated instruction. Given that we have multiple instructions and multiple operands per instruction, the arbiter is able to achieve high level of bank-level parallelism.

Note that the register layout affects the amount of bank level parallelism, hence previous works has suggested that the same registers from different warps be assigned to different banks. Why? Because with round robin scheduling most probably warps will be making similar progress, which means that at any point in time most warps will be executing the same instructions and hence accessing the same registers. If the equivalent registers from different warps are mapped to same banks, then we will have bank conflicts between different warps. That is why Narasiman et al. [3] suggested allocating equivalent registers to different banks.

The operand collector as explained above can cause a write after read hazard, if two instructions from the same warp are present in the operand collector at the same time and the second instruction writes a register that the first instruction reads. If the second instruction gets issued first because its operands were ready before the first instruction, then the first instruction will be reading a wrong value eventually (the value updated by instruction two). In order to prevent this write after read hazard, Mishkin et al. [5] suggested that instructions must be issued from the operand collector in program order. The different schemes suggested by Mishkin et al. [5] resulted in some slowdown that reached a factor of two for some schemes.

## **3. CONTROL DIVERGENCE IN THE LITERATURE**

#### 3.1 Introduction

As discussed earlier GPUs serialize the execution of threads in a warp when different threads go in different direction upon a conditional statement. The SIMT stack is responsible of ensuring correct execution of divergent threads as well as reconvergence at the earliest re-convergence point that can identified at compile time which is known as the immediate post dominator.

The use of the SIMT stack as explained previously causes lower SIMD efficiency since only a subset of the lanes will be active at any divergent point. Moreover, the serialization is not required for correctness, in other words the threads within a warp do not have any implicit data dependency. In case of needed communication, this has to be done explicitly through the use of barriers and shared memory.

The SIMT stack area per warp is 32 by 64 = 2048 bits. A SIMT stack is required for each running warp, So in order to allow 64 warps to run concurrently we need 64 \* 2048 = 16 KB. In the following section, we explain the major works from the literature that tackled the problem of control divergence:

#### **3.2** Dynamic Warp Formation (DWF)

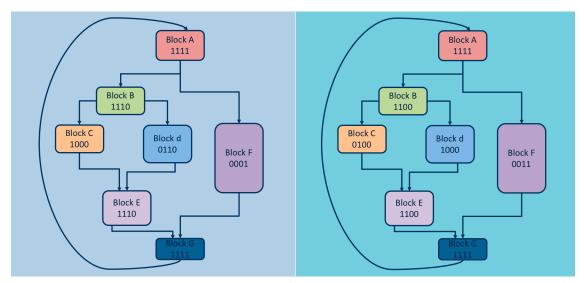

GPUs use fine grained multithreading to hide memory latencies, this means that hundreds of threads are running usually on a given core. These threads are divided into warps, where a warp is a set of threads that execute in all threads. All warps usually execute the same code and not only the threads within one warp, is this due to the way threads are spawned. In current GPUs each warp handles divergence among its own thread. The observation that Fung et al. [6] make in this work is that among the hundreds of threads that run on a core each divergent branch target is executed by large number of threads that are scattered among the different warps. Thus, they suggest forming new warps dynamically upon divergence. The newly formed warps all share the same target upon the divergent branch, i.e these dynamically formed warps are convergent.

Figure 17: DWF example: 2 CFGs showing 2 warps diverging differently

Figure 18: DWF example: (A) Basic Blocks executed by warp 1. (B) Basic Blocks executed by warp 2. (C) Execution Flow of 2 warps

Figure 19: DWF example : Warp compaction

Figure 20: DWF example: Execution flow using DWF

Figure 21: DWF example: The effect of Memory divergence

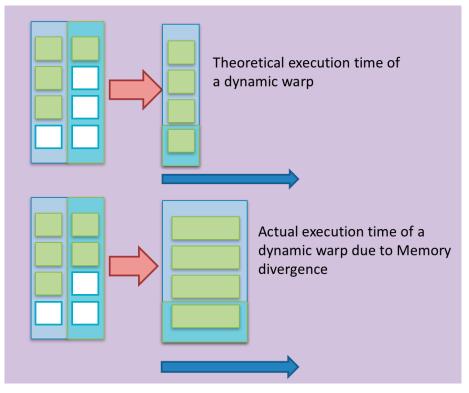

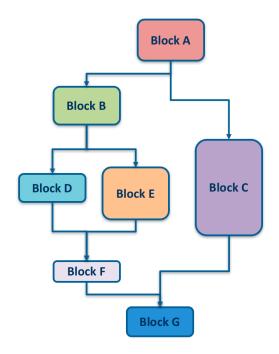

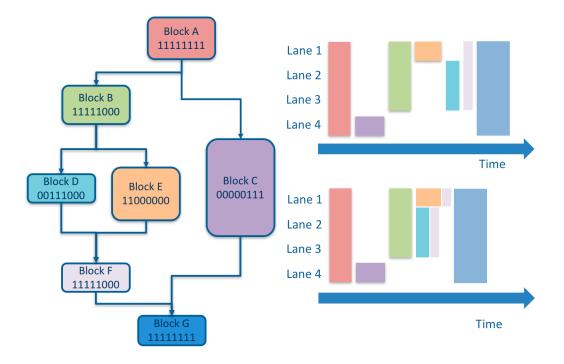

Figure 17 and 18 shows an example of Dynamic warp formation. Having two warps 1 and 2 each constituting of four threads. Both warps are convergent at block A. At the end of block 'A', the first three threads of warp '1' jump to block 'B' while the fourth thread jumps to block 'F'. Warp '2' has its first two thread jump to block 'B' and the other two threads jump to 'F'. Furthermore, at the end of block 'B' the first thread of warp '1' jumps to block 'C' and the 2<sup>nd</sup> and the 3<sup>rd</sup> threads jump to block 'D'. Warp '2' also diverges at the end of block 'B' with thread 3 jumping to block 'C' and thread 4 jumping to block 'D'. By looking at each basic block of the control flow graph shown in Figure 1,7 we can see that if divergence is dealt with across different warps we can get a better lane utilization. For example block F will be executed once for 1 thread of warp '1' and another time for 2 threads from warp '2'. Hence the total number of threads executing block 'F' is three threads which is lower than the number of threads per warp. Thus if these threads belonged to 1 warp we could have executed block 'F' once instead of two times. Similarly block 'C' can be executed once instead of twice, and the same applies to block 'D'. Note that with dynamic warp formation, block 'B' and block 'E' will be executed twice like in the case of static warp because the number of threads executing these blocks is five, which is bigger than the number of threads per warp, so we need two warps to execute these blocks, and thus DWF does not help with these two basic blocks (Figure 19 shows how threads can be merged into dynamic warps) Figure 20 shows the theoretical execution time of Dynamic warp formation vs the baseline GPU architecture and Figure 21 shows that some dynamic warps will take extra time executing due to memory divergence resulting from compacting threads from different warps.

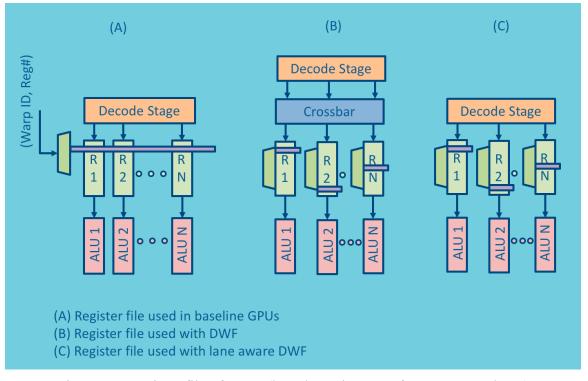

DWF requires changes to the register file. When grouping different threads from different static warps into the newly formed warps, these new threads perform the same instructions but they need to access different registers. In their paper on DWF, Fung et. al restricted threads to stick to their original assigned lane when moved to a new warp. Otherwise the register file needs to be designed to have a crossbar (Figure 22-B), which complicates the register file access, Moreover, if two threads from same 'home' lane are grouped into the same warp, these two threads will have a bank conflict since each lane is assigned a bank. Even with the restriction that the threads stick to their home lanes, the

traditional register (Figure 22 - A) file is not sufficient. Registers accessed by the threads of initially created warps are at the same offset within the lane, thus we need one decoder. However, in newly dynamic formed warps, the offset to access registers in a warp is not the same in each lane, thus a common decoder for all lanes is not possible (Figure 22-c).

Figure 22: Register file of DWF (based on Figure 10 from Fung et al. [6])

The first major drawback of dynamic warp formation is that some threads can starve while waiting to be grouped with other threads in a new warp. These threads will not progress because no other threads are following the control path. The second major drawback of Dynamic warp formation is increased memory divergence. In the GPU world, when different threads from a warp load from memory it could be the case that some threads hit in cache while other miss and since the SIMT programming model requires the threads of a given warp to execute in lockstep, the threads that hit in cache must wait for the threads that miss in cache. This phenomenon is known as memory divergence. It turned out that grouping threads from different warp will increase the memory footprint of the warp which will increase the probability of memory divergence to occur. Moreover, even if all thread miss in cache, the probability that the different threads belonging to different warps to access nearby data is low which will increase non coalesced memory accesses and shared memory conflicts. These drawbacks of dynamic warp formation causes slow down for many applications despite increasing the lane utilization. One last drawback of Dynamic warp formation is that applications that require implicit synchronization between the threads of a static warp will execute incorrectly.

One solution that was proposed by the authors of DWF is to rearrange the threads back to their 'home' warps when executing the non-divergent portions of the application. Moreover, many scheduling techniques were studied to avoid thread starvation.

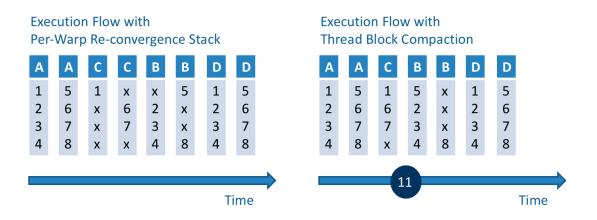

## **3.3** Thread Block Compaction (TBC)

Thread block compaction [7] is based on the same observation as dynamic warp formation. However, it limits the warp formations to threads belonging to the same core. Thread block compaction creates the new warps mainly by modifying the SIMT stack so that it encompasses all warps executing in the same core. New warps are formed upon a divergent branch. Note that synchronizing all threads of a block at each divergent branch reduces the available TLP. In other words, the scheduler may not find instructions to execute since all the threads are waiting for synchronization. Thread block compaction restrict the compaction of threads to threads belonging to the same thread block. This restriction is a compromise between the TLP availability and the SIMD utilization. In other words, if we do not regroup thread into new warps, the lane utilization will be low because of the divergence. And if we synchronize all the threads in a core upon divergence in order to create the new warps we end up with the TLP loss explained above. By restricting the compaction within a block, TBC claim that other blocks could be executing and moving forward while the threads in a divergent block are waiting to synchronize at the divergent branch. Figure 24 below shows the high level operations of Thread block compaction.

| Control Flow<br>Graph                 | Block-wide<br>Reconvergence Stack |     |               |     | Warp After<br>Compaction |  |  |

|---------------------------------------|-----------------------------------|-----|---------------|-----|--------------------------|--|--|

| Block A                               | РС                                | RPC | Active Thread | Α   | 1.2.3.4                  |  |  |

| 1234<br>5678<br>3                     | А                                 |     | 12345678      | A   | 5.6.7.8 2                |  |  |

|                                       | РС                                | RPC | Active Thread |     |                          |  |  |

| Block B<br>x 2 3 4 Block C<br>1 x x x | D                                 |     | 12345678      |     |                          |  |  |

| 5xx8 x67x                             | В                                 | D   | 23458         |     |                          |  |  |

|                                       | С                                 | D   | 167           | 1 C | 1.6.7.x                  |  |  |

| 9 Block D                             |                                   |     |               |     |                          |  |  |

| 1234                                  | РС                                | RPC | Active Thread |     |                          |  |  |

| 5678                                  | D                                 |     | 12345678      | В   | 5.2.3.4                  |  |  |

|                                       | В                                 | D   | 23458         | В   | x.x.x.8                  |  |  |

|                                       |                                   |     |               |     |                          |  |  |

|                                       | РС                                | RPC | Active Thread | D   | 1.2.3.4                  |  |  |

|                                       | D                                 |     | 12345678      | D   | 5.6.7.8                  |  |  |

|                                       |                                   |     |               |     |                          |  |  |

|                                       |                                   |     |               |     |                          |  |  |

Figure 23: High level operation of TBC

Figure 24: TBC execution Time (based on Figure 7 from Fung et al. [7])

Part B of Figure 23 shows the control flow graph as well as the block wide reconvergence SIMT stack of example code shown in Figure 23(A). The two warps executing each has 4 threads. While executing block A there is no divergence and both warps are scheduled independently. At the end of block A both warps synchronize since this is a potential point of divergence. When both warps execute the branch instruction two new entries are inserted in the stack. Each of these new entries contain all the threads jumping to its corresponding PC, even if these threads belonged previously to different warps. The threads are then compacted into new warps. When these new warps reach their re-convergence point their corresponding entries in the stack are popped. So first we have one warp executing block C and then we have two warps executing block B. when block B terminates the threads are reassigned to their initial warps.

Figure 24 compares the execution time of traditional per warp re-convergence stack and the execution time of thread block compaction. In this example the execution time is reduced by 12.5% using TBC.

#### **3.4** Large Warp Microarchitecture (LWM)

Like Thread Block Compaction, LWM [3] extends each SIMT stack so that it handles more than one warp. However unlike Thread block compaction, which synchronizes threads at the branch instructions and at the re-convergence points, the group of warps in LWM all execute in lockstep. In other words, they are synchronizing at each instruction. This compaction at every instruction reduces thread level parallelism even more than in the case of thread block compaction. This lockstep execution of warps within a group allows performing compaction using predicate instructions. Large warp microarchitecture tracks register dependency at thread granularity in order to allow some warps to execute before some other warps belonging to the same group. This decreases the thread level parallelism loss caused by the lockstep execution.

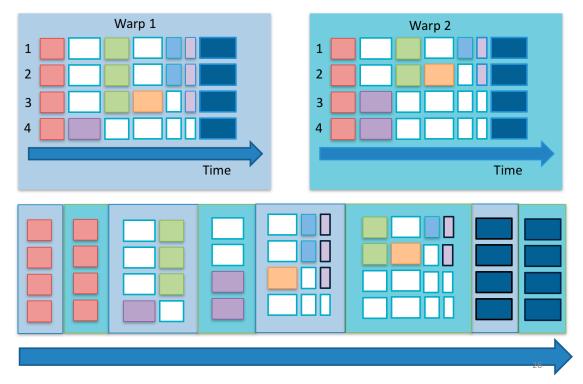

## 3.5 Simultaneous Warp Interweaving

As shown in Figure 25 simultaneous branch interweaving [8] support issuing 2 different instructions where the instructions come from warps that are divergent so that they fill the branch gaps. This complicates the front-end of the GPU.

Figure 25: Simultaneous Branch Interweaving micro-architecture (based on Figure 3 from Brunie et al.)

# 3.6 Conditional Streams

Different works focused on using warp compaction in software in order to improve SIMD efficiency. Conditional streams [9], has its kernel splits it data steam into many streams based on the result of a divergent branch and then each sub-stream is processed by a different kernel which merge back at re-convergence.

## 3.7 SIMD Lane Permutation

As mentioned earlier the problem with most thread compaction techniques is that threads must remain in the same lane when a new dynamic warp is formed otherwise the register file state of the thread must be moved to a different lane. Rhu and Erez [10] observe that threads that take the same path tend to belong mostly to the same home lane and thus they conclude that the sequential mapping of thread IDs to consecutive threads in a warp is not optimal for any dynamic warp formation technique. So in this work they propose different thread mapping and improve the rate of compaction.

#### 3.8 Multi-Path Parallelism

Upon divergence threads with same branch targets are grouped into warp splits. Warp splits are executed sequentially in baseline GPU. This serialization is not required for correctness. It is just used because it allows using a simple hardware and because graphics applications which GPUs were first built for were mostly regular application with little control divergence. Actually different warp splits can even execute in parallel because each thread has its own registers. Allowing an interleaved execution of these warp splits will give the warp scheduler more scheduling opportunities in order to hide the long latency memory instructions. In other words, interleaving the execution of divergent paths will boost thread level parallelism without improving the SIMD efficiency.

Multi-path execution boosts performance of memory bound applications, where the cores are idle waiting for memory accesses and were the limited resources of the cores does not allow more warps to co-exist and hide each other's latencies.

Figure 26: DPE example: Control Flow Graph

Figure 27: DPE example: Execution flow

Figure 27-A shows the performance when using baseline GPU while Figure 27-B shows the performance when allowing interleaving between different divergent blocks.

So while block C is executing in case it is waiting for memory access the threads that went in the other direction of the branch (block B) can start executing. similarly, block D and Block E have their execution interleaved, while D waits on its long latency access, threads that went in the E direction are executing.

Figure 28: Dynamic Warp Subdivision example

### 3.9 Dynamic Warp Subdivision

Dynamic warp subdivision [11] split a divergent warp into two warp splits that execute in parallel. In order to achieve this, the re-convergence stack is extended with a warp split table. Dynamic warp subdivision allows warps splits also at memory divergence when different threads in a warp have different memory access latencies due to some threads hitting in cache while others missing. The threads that hit in level one data cache form a warp split and are allowed to move forward while the complementary warp split is waiting for its memory access to resolve. Note that in this case the threads that move forward may pre-fetch for the warp split that is still waiting for its access to resolve. As shown in Figure 28 above the warp splits are allowed to go beyond the immediate post dominator (block F in Figure 28) and not converge with the other warpsplits. This may create the pre-fetch effect we discussed previously but it also risks pipeline under-utilization.

### 3.10 Dual Path Execution and Multi Path Execution

Dual path execution [12] restricts DWS so that each warp executes only two concurrent warp-splits. This restriction allows capturing most of the benefits of DWS while keeping the hardware simple. DPE requires some extension for the SIMT stack so that both entries of a divergent branch are at the top of the stack. In other words, so that the warp scheduler can interleave the execution of both branch target. While DPE does not increase the SIMD utilization it does offer higher level of parallelism to the warp scheduler which helps at better hiding the latency of long memory accesses. Other than the SIMT re-convergence stack, DPE requires some extensions to the scoreboard so that dependencies are tracked for each warp split separately. Multi path execution [13] follows DPE but gets rid of the dual path limitation.

## 3.11 Likely Convergence Points

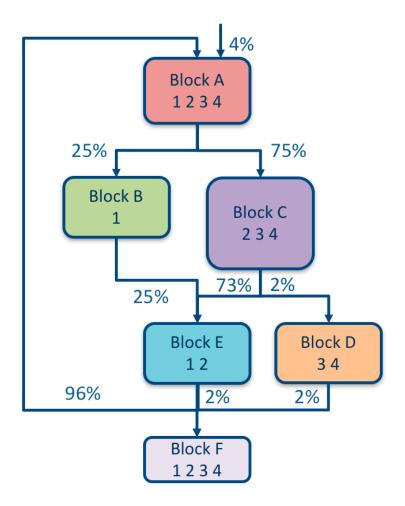

As we discussed earlier, the immediate post dominator is the earliest reconvergence point that it is safe to re-converge at and that can be identified at compile time. However, re-convergence can happen earlier than IPDOM in reality. Figure 29 shows a situation where threads can re-converge at an earlier point than the IPDOM. The IPDOM of both block A and block C is block F however in most cases the threads can reconverge at block E since 73% of the times block C jumps to block E and 25% of the time block B jumps to block E and 96% of the times block E jumps back to block A. Hence, the path from block C to block D is rarely followed and in most cases at runtime we can re-converge at block E.

Figure 29: CFG annotated with path probabilities

Fung et al. proposes extending the re-convergence stack with LCP (likely reconvergence points) and a pointer that points to the stack position of a special likely convergence entry that is created when a branch has an LCP that is not equal to the IPDOM. When a warp diverges, three entries are added to the stack. The first one is the likely point of convergence. The other two correspond to the two sides of the divergent branch as shows in Figure 29-a. Now when the warp diverges at block C, two new entries are created (4). When the execution reaches the LPC, the entry of E is removed from the stack (5). When thread 3 and thread 4 reaches block F, the stack is popped (7). Then block B executes and its entry is popped once the PC = LPC. Finally, the likely convergence entry is executed until it reaches the IPDOM.

|   | PC | RPC | LPC | LPos | Act. Thd |   | PC | PC RPC | PC RPC LPC | PC RPC LPC LPos |

|---|----|-----|-----|------|----------|---|----|--------|------------|-----------------|

|   | F  | -   | -   | -    | 1234     |   | F  | F -    | F          | F               |

|   | Е  | F   | -   | -    | -        |   | Е  | E F    | E F -      | E F             |

| 2 | В  | F   | E   | 1    | 1        |   | В  | B F    | B F E      | B F E 1         |

|   | С  | F   | Е   | 1    | 234      |   | F  | F F    | FF E 7     | FFE7            |

|   |    |     |     |      |          |   |    |        |            |                 |

|   | PC | RPC | LPC | LPos | Act. Thd |   | PC | PC RPC | PC RPC LPC | PC RPC LPC LPos |

|   | F  | -   | -   | -    | 1234     |   | F  | F -    | F          | F               |

| 5 | Е  | F   | -   | -    | 2        |   | Е  | E F    | E F -      | E F             |

|   | В  | F   | Е   | 1    | 1        |   | Æ  | E F    | EFE9       | E F E g E       |

|   | D  | F   | Е   | 1    | 3 4      |   |    |        |            |                 |

| 4 | £  | F   | £   | 1    | 2        |   | PC | PC RPC | PC RPC LPC | PC RPC LPC LPos |

|   |    |     |     |      |          |   | F  | F -    | F          | F               |

|   |    |     |     |      |          | F |    | F      | -          | -               |

Figure 30: SIMT stack of the Likely convergence example (based on Figure 3.19 from Aamodt et al.)

## 3.12 Vector Thread Architecture

The vector thread architecture [14] combines MIMD and SIMD, i.e. the front end can fetch instructions from the shared L1 instruction (Figure 31) cache and issue an instruction to be executed across all threads or it can switch to a MIMD architecture where a lane fetches instructions from its private level zero cache and executes its own instructions. Vector thread architecture have comparable efficiency to SIMT machines when running regular applications but outperforms GPUs when executing irregular applications.

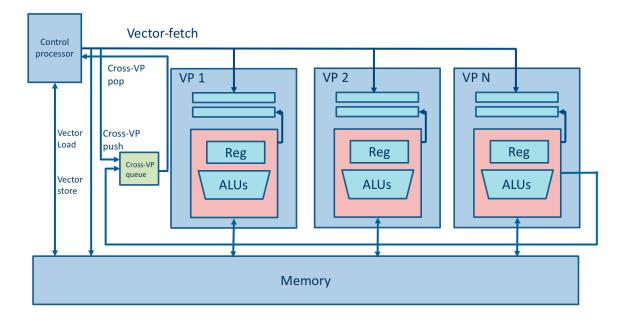

Figure 31: Abstract model of a vector-thread architecture (base on Figure 1 of Krashinsky et al.)

## 3.13 Temporal SIMT

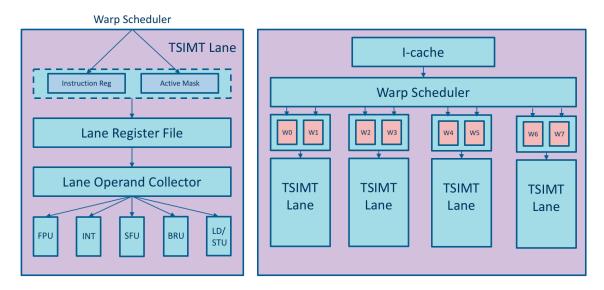

Temporal SIMT [15] machines (Figure 32) are similar to vector thread machines in the sense that they allow each lane to execute in MIMD fashion. Each lane, however, runs one warp. In other words, the warp with all its threads is time multiplexed in one lane and thus the machine amortizes the control flow overhead across time, while traditional GPUs amortize the overhead across the lanes.

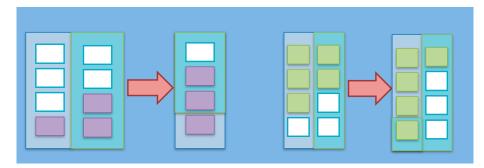

#### 3.14 Variable Warp Sizing

In variable warp sizing, Rogers et al. [16] propose narrow warps, called slices, where each slice consist of 4 lanes. Each slice contains fetch and decode units. These slices can be grouped into gangs. If the application has no branch divergence, the warps belonging to a gang execute in lockstep and use a shared fetch unit and a shared level one of cache. Every time the control flow diverges the gang splits into multiple gangs. The split gang can split further if it counters divergence again. Splitting can continue until each warp is in its own gang. Upon reaching this point, each single warp gang start using its own fetch unit and private level zero cache. The gangs are merged back when the PC are equal in different gangs

Figure 32: Temporal SIMT micro-architecture (based on Figure 1 from Keckler et al.)

### **3.15 SIMT Stack Alternatives and Divergence Management:**

The size of the SIMT stack scales with the number of threads per warp as well as the number of warps that co-exist in a specific core. The area requirement of a baseline re-convergence stack is 32\*64 bits. While this is not huge in comparison to the size of the register file, many proposals discussed alternative mechanisms of implementing the reconvergence stack, mainly in order to take advantage of the area dedicated to the stack when an application does not diverge.

Among these proposals is the AMD's GCN [37] which proposes the use of a scalar register file whose registers are used as predication registers to control the execution in each warp. The compiler uses this structure to emulate the re-convergence stack in software. In the absence of divergence, the compiler can make use of the registers for other computations. Moreover, they minimize the size of the stack by prioritizing the execution of the path that has lower number of active threads.

Another proposition was a stack-less SIMT coupled with temporal SIMT architecture [39]. In this proposition threads execute in lockstep when they are convergent and shift to a MIMD execution upon divergence. The instruction set architecture is extended with a

sync-warp instruction that the compiler places at the re-convergence point, so that divergent threads re-converge. The compiler analyzes the code to determine convergent and divergent regions and detects the branches that are taken by all threads by following these steps:

- 1) All basic blocks are considered thread invariant at the beginning

- 2) Mark all threads dependent on thread ID as thread variant.

- Iteratively mark all instructions dependent on thread-variant instructions as thread variants as well

- All instructions in a BB that are control dependent on a thread variant branch are also thread variant

This stack-less technique does not catch all possible re-convergence points in the case of nested divergent branches, but performs comparably to the SIMT stack solution when the applications are fairly regular.

Old GPUs actually did not use a full SIMT stack. Instead they used predication. Predication is a known technique in the CPU world used to reduce pipeline stalls due to a control hazard. In the world of CPU, when a branch is miss-predicted, the penalty is large. The CPU stalls the pipeline and starts fetching instructions from the branch target. With the use of hardware branch prediction, the number of stalls decreases, however the rate of miss-prediction remains between 5 and 10 percent, which can slow down a processor by as much as 30%. Predication solves this problem by removing the branch instruction itself and executing both possible paths of the branch. The instructions, however, will have a predicate tag appended by the compiler and will only be allowed to commit their results and change the program state if their corresponding predicate is true. The value of the predicate will be only true in one of the paths. Predication relies on parallel executions of two instructions, each belonging to a different side of the branch, and thus it requires an architecture that feature multiple instruction issue. The following example (Figure 33) illustrates the idea of predication. In a baseline CPU, the code is divided into 4 blocks, while with the use of predication it will executed as a single block (Figure 33- c). Note that the two predicates are complimentary of each other, thus only one can be true at a given time and thus only one path will commit its results.

In GPUs, predication can be used as a low overhead way to implement simple conditional code sections. It saves the overhead of pushing and popping from the re-convergence stack.

Using predication allows the compiler to interleave the execution of the both paths coming out of the branch. This increases the Tthread level parallelism like the DPE work mentioned above without the advanced SIMT stack that DPE requires. Note that this is possible with predication because divergent blocks use different predication registers.

Predication increases the pressure on the register file, which will result in a lower number of warps that can co-exist.

Predication affects the dynamic number of instructions. It results in removing the pop and push instructions required to manage the re-convergence stack. On the other hand, checking the uniform branches increases the number of dynamic instructions.

Figure 33: (B) Baseline CFG. (C) CFG using predication

# 4. OPPORTUNISTIC INTER-PATH RE-CONVERGENCE

### 4.1 Introduction

GPGPUs deliver high speed up for regular applications while remaining energy efficient. The single instruction multiple thread (SIMT) execution model used in GPUs amortizes the energy and bandwidth cost per instruction over a set of threads executing in lockstep, known as a warp, Moreover. GPUs use fine-grained multithreading to hide long off-chip latency. This high performance-energy promise does not hold for irregular control divergent applications. When different threads in a warp decide to jump to different targets upon executing a branch instruction the lockstep execution is altered. Current GPUs serialize the execution of threads following different paths within a given warp.

While this solution is simple and could be handled using a simple SIMT re-convergence stack in hardware, this technique leads to lower SIMD efficiency and needless serialization.

Different solutions were proposed in the literature to deal with control divergence. These solutions can be divided into three major categories:

- The first is based on warp compaction: GPU is a highly multithreaded throughput architecture, which means that any core has hundreds of threads running at the same time and executing the same kernel. Hence any target of a branch instruction is reached by many threads but that are scattered among multiple warps. Hence it makes sense, to compact threads that follow the same control path into new warps upon a divergent branch.

- The second family of works, focused on improvements to the SIMT reconvergence stack: The observation behind these works is that divergent threads within a warp are independent and thus their execution can be interleaved. The interleaved execution makes use of the idle cycles. These techniques are helpful mainly because the number of warps that can co-exist is limited by the resources which makes it hard for the scheduler to hide long off-chip latency.

The third family of works adds a MIMD capability to traditional GPUs: In other words, the GPU performs in a SIMD mode the convergent parts of a warp and upon divergence it switches to a MIMD mode which allows all threads to make progress and not be serialized.

Detailed description of these different solutions is presented in chapter 3. While all these techniques improve the performance of some applications with divergent control flow, they had some drawbacks like increased non-coalesced memory accesses in case of thread compaction works which results in slow down for some applications, reduction in lock-stepping effect and hence GPGPUs' bandwidth and energy amortization in case of adding MIMD capabilities. While some inefficiency for irregular workloads may be unavoidable some works imposed some loss on regular workloads.

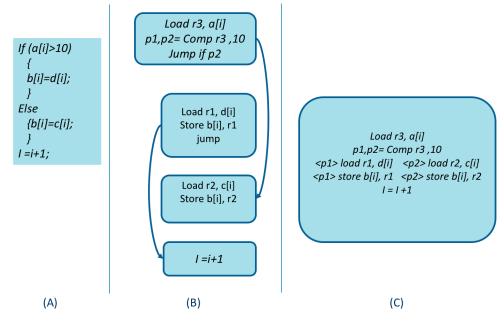

In this work we introduce the concept of *opcode-convergent threads* which are threads that execute the same instructions but could be accessing different operands. We find out that divergent basic blocks exhibit substantial opcode convergence. For example, in the case of LUD 65%, of the divergent instructions are actually opcode convergent. This means that upon serializing the execution of two divergent basic blocks, many instructions are re-executed in the same order but potentially accessing different operands.

This high percentage of opcode convergence among divergent blocks is due to the simple instruction set used in GPUs. GPUs are RISC machines. The large semantic gap between the high level language used in writing the application, CUDA in our case, and the assembly code running on the GPU results in basic blocks that exhibit a lot of opcode convergence even though the divergent basic blocks could be performing completely different computation at a high level.

We build a compiler that analyzes divergent blocks and identify the common streams of opcodes using the longest common subsequence (LCS) algorithm. We modify the GPU architecture so that these common instructions are executed as convergent instructions. Using software simulation, we achieve a 17% speedup over baseline GPGPU for irregular workloads and we do not incur any performance loss on regular workloads. In this work we make the following contributions:

- a. We propose a more fine-grained approach to exploit *intra-warp* convergence by introducing the concept of *opcode-convergent threads* which execute the same instruction, but with potentially different operands.

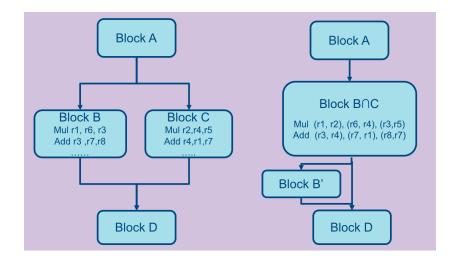

- b. We develop a compiler analysis based on *longest common* subsequence (LCS) [40] that identifies opcode convergence among divergent basic block and annotates the code so that it runs on our modified architecture.