# GROWTH AND CHARACTERIZATION OF TWO-DIMENSIONAL III-V SEMICONDUCTOR PLATFORMS FOR MESOSCOPIC PHYSICS AND QUANTUM DEVICES

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Saeed Fallahi

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Michael J. Manfra

Department of Physics and Astronomy

- Dr. Gabor A. Csathy Department of Physics and Astronomy

- Dr. Francis J. Robicheaux

Department of Physics and Astronomy

Dr. Supriyo Datta

School of Electrical and Computer Engineering

# Approved by:

Dr. John P. Finley

Department of Physics and Astronomy

### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor, Professor Michael J. Manfra for the support, guidance and encouragement he has given me through out this work.

Special thanks to Professor Gabor A. Csathy, Professor Supriyo Datta, and Professor Francis J. Robicheaux for serving on my graduate committee and providing useful suggestions.

I would also like to thank my colleagues Dr. John Watson and Dr. Geoff Gardner who taught me on the operation and maintenance of MBE machine.

Many thanks to James Nakamura for his help in noise characterization of measured devices and useful discussion on many aspects of measurement results.

I would also like to thank Dr. Candice Thomas, Dr. Sergei Gronin and Tian Wang for the growth of high quality superconductor-semiconductor heterostructures and Dr. Ray Kallaher for fabrication of nanostructured devices on these hybrid heterostructures. Thanks to Michael Yannell, Dr. Tai-Lung Wu and Teng Zhang for their help in operation of Oxford and BlueFors dilution refrigerators.

I must express my very profound gratitude to my parents and to my wife Ghazaleh for providing me with constant support and continuous encouragement throughout my years of study. This accomplishment would not have been possible without them.

To my beloved daughter Elma for being such a good girl always bringing so much joy laughter and happiness into my life.

# TABLE OF CONTENTS

|    |      | Pa                                                                                                         | age |

|----|------|------------------------------------------------------------------------------------------------------------|-----|

| LI | ST O | F TABLES                                                                                                   | V   |

| LI | ST O | F FIGURES                                                                                                  | vi  |

| AI | BSTR | ACT                                                                                                        | xii |

| 1  | MOI  | LECULAR BEAM EPITAXY OF ULTRA PURE GAAS AND $AL_XGA_{1-X}$ .                                               | AS  |

|    | 1.1  | Introduction                                                                                               | 1   |

|    | 1.2  | High Mobility GaAs MBE System                                                                              | 3   |

|    | 1.3  | RGA spectra in MBE system                                                                                  | 5   |

|    | 1.4  | High mobility heterostructure design and growth campaigns $\ldots$ .                                       | 8   |

| 2  |      | V NOISE SI DOPED GAAS/ALGAAS HETEROSTRUCTURES FOR                                                          | 23  |

|    | 2.1  | Introduction                                                                                               | 23  |

|    | 2.2  | Low frequency noise in GaAs nanodevices                                                                    | 24  |

|    |      | 2.2.1 Bias cooling technique                                                                               | 29  |

|    |      | 2.2.2 Global top gate technique                                                                            | 34  |

|    | 2.3  | Impact of silicon doping on low frequency charge noise and conductance drift in GaAs/AlGaAs nanostructures | 38  |

|    | 2.4  | Summary and outlook                                                                                        | 51  |

| 3  |      | UCED SUPERCONDUCTING GAP IN HYBRID SUPERCONDUCTOR-<br>ICONDUCTOR HETEROSTRUCTURES                          | 53  |

|    | 3.1  | Introduction                                                                                               | 53  |

|    | 3.2  | MBE growth of hybrid Al/Al_{0.15}In_{0.85}As/InAs heterostructures                                         | 58  |

|    | 3.3  | Transport properties and gate response of 2DEG                                                             | 59  |

|    | 3.4  | Measurement of the induced superconducting gap                                                             | 61  |

| LI | ST O | F REFERENCES                                                                                               | 71  |

1

# LIST OF TABLES

| Table |                                                                                                                                                                                                                                                                                                        | Page |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Characteristics of studied wafers including Si doping concentration $N_D$ ,<br>doping width W, 2DEG density n, mobility $\mu$ , operating gate voltage $V_g$ ,<br>number of QPCs measured and Ohmic contact resistance for each wafer.<br>The size of each Ohmic contact is $150\mu m \times 150\mu m$ | 40   |

| 3.1   | Characteristics of studied wafers with different $Al_{0.15}In_{0.85}As$ barrier thickness ranging from 3 nm to 9 nm.                                                                                                                                                                                   | 60   |

| 3.2   | Induced gap vs barrier thickness extracted from SNS device measurement at 10 mK                                                                                                                                                                                                                        | 65   |

# LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

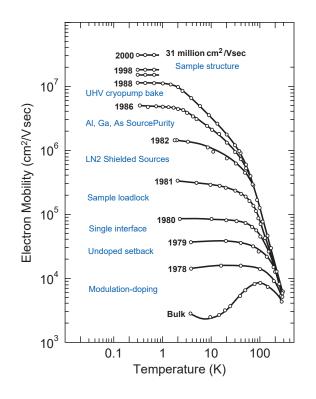

| 1.1    | A historical view of the upward electron mobility in GaAs heterostructures<br>and the steps leading to this improvement. Reprinted from Physica E, vol.<br>20, L. Pfeiffer, and K. W. West, 'The role of MBE in recent quantum Hall<br>effect physics discoveries', 5764, Copyright 2013, with permission from<br>Elsevier.                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

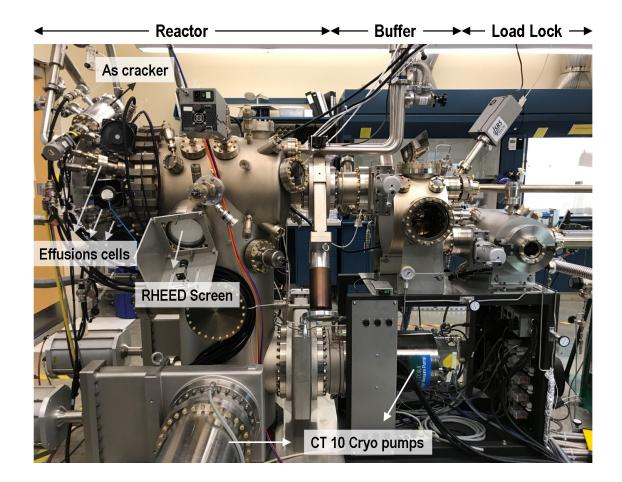

| 1.2    | Modified Veeco Gen II MBE system at Purdue University                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4  |

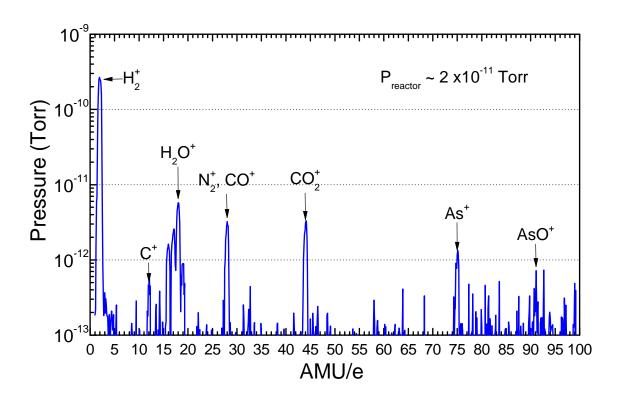

| 1.3    | Clean RGA spectra from Reactor at idle condition with $P_{reactor} \sim 2 \times 10^{-11}$<br>Torr. The dominant species are labeled which all have partial pressures<br>below $1 \times 10^{-11}$ Torr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6  |

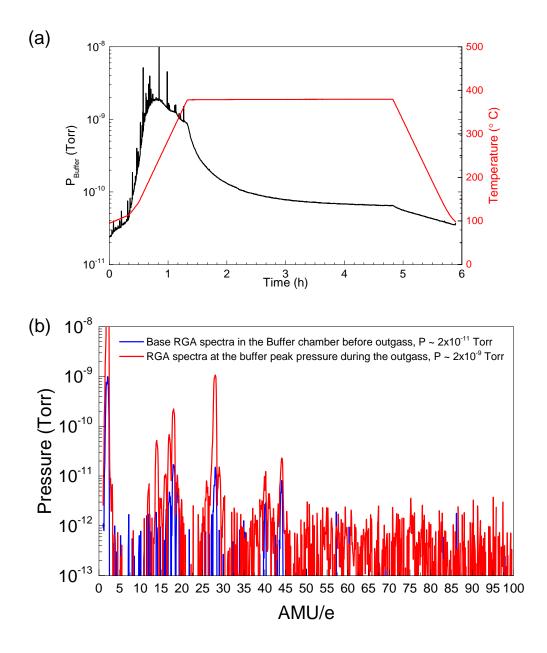

| 1.4    | New GaAs wafer outgass in the buffer chamber. (a) Buffer chamber pres-<br>sure (black solid line) and thermal treatment profile (red solid line) during<br>wafer outgass at 380 °C for $\sim$ 5h. (b) An overlay of base RGA spectra in<br>the buffer chamber with RGA spectra at the buffer chamber peak pressure<br>during during wafer outgass                                                                                                                                                                                                                                                                                                                                                                                                 |    |

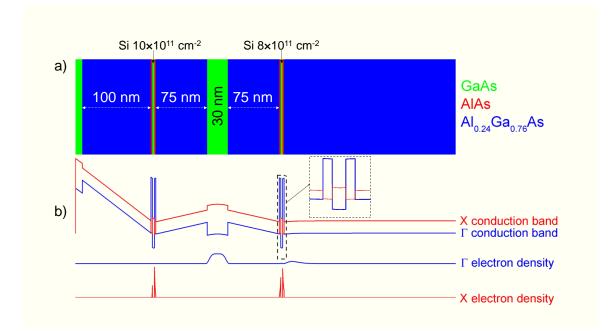

| 1.5    | (a) The active region layer stack used to grow a high mobility 2DEG with<br>electron density $n = 3.0 \times 10^{11} cm^{-2}$ .; and (b) $\Gamma$ and X conduction band<br>minimum along the growth direction. Electron density in the main GaAs<br>quantum well ( $\Gamma$ band) and electron density in the screening AlAs layers<br>(X band) are shown accordingly. Reprinted from J. Cryst. Growth, vol.<br>441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified<br>MBE hardware and techniques and role of gallium purity for attainment of<br>two dimensional electron gas mobility > $35 \times 10^6 cm^2/Vs$ in AlGaAs/GaAs<br>quantum wells grown by MBE', 71-77, Copyright 2016, with permission<br>from Elsevier. |    |

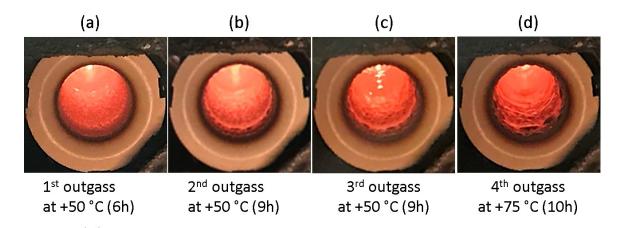

| 1.6    | a), b), c) and d) Creep of Al melt during the the successive outgassing of Al cell. e) Al has crept all the way up covering the crucible lip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12 |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

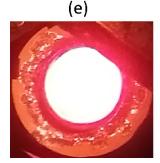

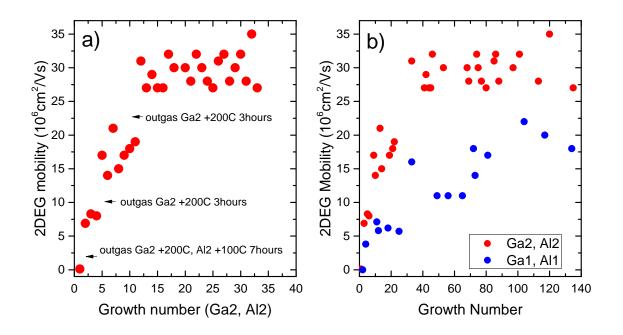

| 1.7  | Evolution of 2DEG mobility for single interface heterojunction (SHJ) and<br>doping well structures as a function of growth number in the first cam-<br>paign. Ga1 and Al1 refers to the particular cells used in the MBE for<br>growing these heterostructures. Reprinted from J. Cryst. Growth, vol.<br>441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified<br>MBE hardware and techniques and role of gallium purity for attainment of<br>two dimensional electron gas mobility $> 35 \times 10^6 cm^2/Vs$ in AlGaAs/GaAs<br>quantum wells grown by MBE', 71-77, Copyright 2016, with permission<br>from Elsevier. | 14   |

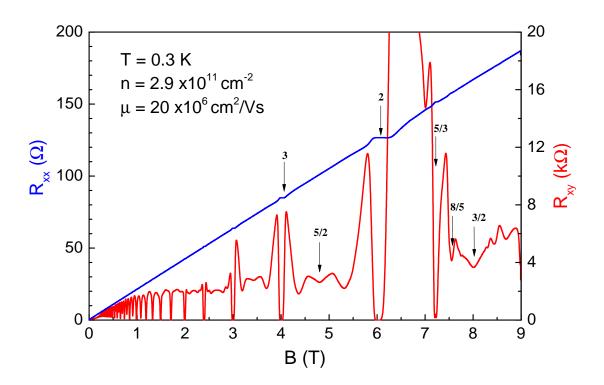

| 1.8  | Magnetotransport measurement results at 0.3K from a sample with mobility of $20 \times 10^6 cm^2/Vs$ and 2DEG density of $2.9 \times 10^{11} cm^{-2}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 15   |

| 1.9  | (a) Four filaments substrate heater in the $1^{st}$ growth campaign. (b) Six filaments substrate heater in the $2^{nd}$ growth campaign. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility $> 35 \times 10^6 cm^2/Vs$ in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.                                                                                                                                       |      |

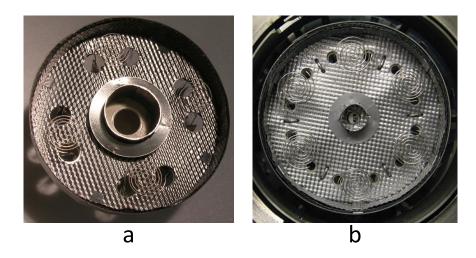

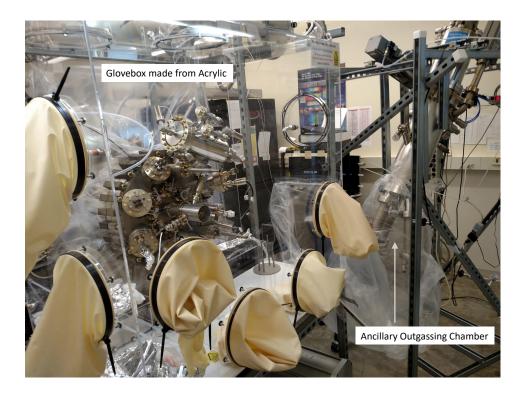

| 1.10 | The glove box enclosure which seals to the source flange of the MBE cham-<br>ber and connects via a tunnel bag to UHV outgassing chamber. Reprinted<br>from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Wat-<br>son, and M. J. Manfra, 'Modified MBE hardware and techniques and role<br>of gallium purity for attainment of two dimensional electron gas mobil-<br>ity $> 35 \times 10^6 cm^2/Vs$ in AlGaAs/GaAs quantum wells grown by MBE',<br>71-77, Copyright 2016, with permission from Elsevier                                                                                                                    | 18   |

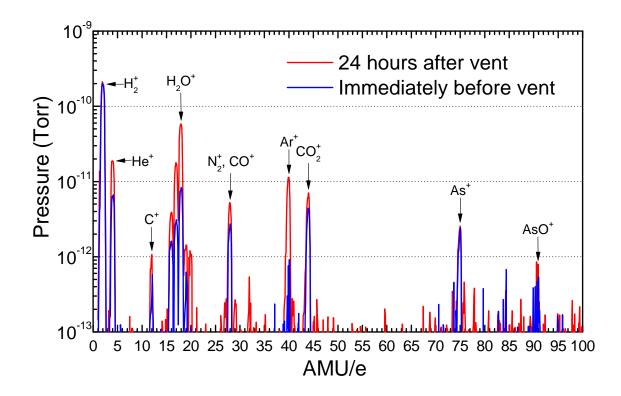

| 1.11 | Comparison of RGA spectra before vent and 24h after venting the growth chamber                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 19   |

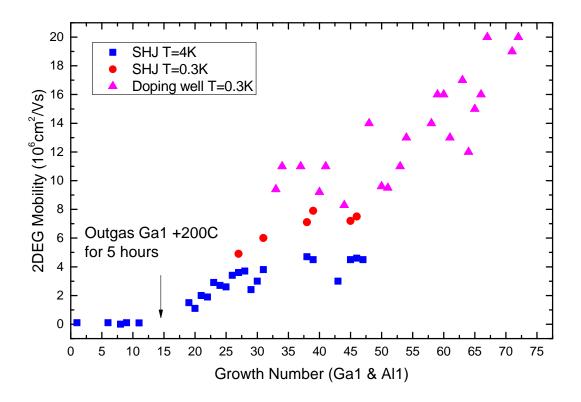

| 1.12 | (a) Discrete jumps in mobility are demonstrated using our high temper-<br>ature outgassing procedure. (b) Plot of 2DEG mobility as a function of<br>growth number demonstrates the difference in improvements between the<br>two different gallium source materials despite receiving the same treat-<br>ment. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S.<br>Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and<br>techniques and role of gallium purity for attainment of two dimensional<br>electron gas mobility > $35 \times 10^6 cm^2/Vs$ in AlGaAs/GaAs quantum wells                             | 00   |

|      | grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20   |

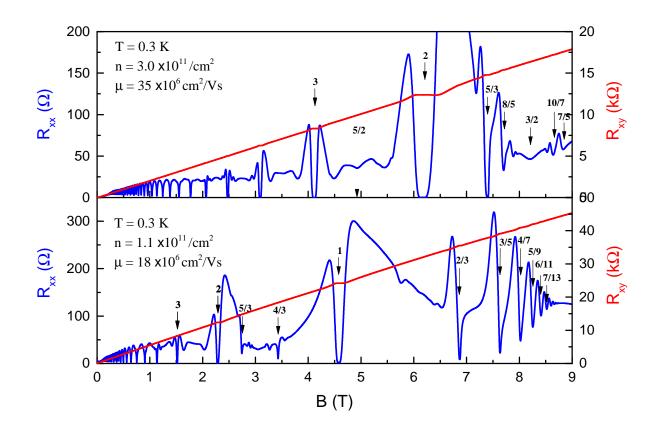

- 1.13 The top panel shows transport data from a sample with mobility of  $35 \times 10^6 cm^2/Vs$  and a density of  $3.0 \times 10^{11} cm^{-2}$ . The bottom panel shows transport data from a sample with lower density of  $1.1 \times 10^{11} cm^{-2}$  and mobility of  $18 \times 10^6 cm^2/Vs$  displaying strong fractional state development near  $\nu = 1/2$ . Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$  in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

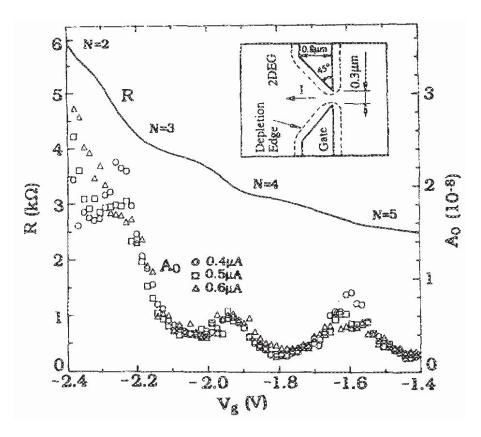

- 2.1 R vs V<sub>g</sub> and A<sub>0</sub> vs V<sub>g</sub>. A<sub>0</sub> is obtained by fitting  $S_I = A_0 I^2/f + S_0$  for I = 0.4, 0.5, and 0.6  $\mu$ A. The approximate plateaus in R are assigned to the quantized resistances  $h/2e^2N$ , with N = 2,3,4, and 5. Inset shows the device geometry. Reprinted from Yuan P. Li et al., 'Low-frequency noise in transport through quantum point contacts', Appl. Phys. Lett. 57, 774 (1990), with the permission of AIP Publishing. . . . . . . . . . . . . . . . .

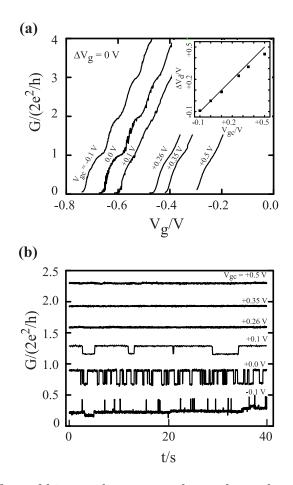

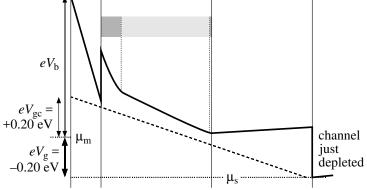

- 2.3 Effect of bias cooling on random telegraph noise. (a) QPC gate voltage characteristics for bias voltages  $V_{gc}$  applied during cool down. Inset: shift  $\Delta V_d$  of the depletion threshold voltage measured for each cooling bias; line shows shift equal to the applied bias. (b) Time traces taken at maximum sensitivity of QPC conductance for each bias. Traces are shifted vertically for clarity. Reprinted figure with permission from M. Pioro-Ladrire et al., Phys. Rev. B 72, 115331 (2005) Copyright (2005) by the American Physical Society.

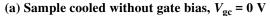

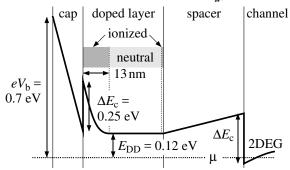

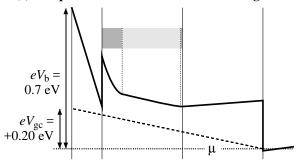

- 2.4 Profiles of conduction bands under a large gate (a) for a sample without bias cooling, (b) during cooling with a positive gate bias of  $V_{gc} = +0.2V$ , and (c) after removing the applied bias in (b). The chemical potential of metal gate  $\mu_m$  is pinned at an energy  $eV_b$  below the GaAs conductance band by the large surface states while the semiconductor potential  $\mu_s$  is pinned by DX centers at an energy  $E_{DD}$  below the conduction band in the neutral (un-ionized) region of the doped layer. Reprinted figure with permission from M. Pioro-Ladrire et al., Phys. Rev. B 72, 115331 (2005) Copyright (2005) by the American Physical Society. . . . . . . . . .

25

28

22

30

31

- 2.5 (a) Conduction band profile for a gate voltage of  $V_g = 0.4V$  applied to a sample without bias cooling. Electrons can are able to tunnel from the gate into the doped region. (b) Conduction band profile for the same operating point after a bias cool of  $V_{gc} = +0.2V$ . Because of the built-in gate voltage, only  $V_g = 0.2V$  is needed to reach the same effective gate voltage of 0.4 V. Tunneling into the doped layer is no longer possible. Reprinted figure with permission from M. Pioro-Ladrire et al., Phys. Rev. B 72, 115331 (2005) Copyright (2005) by the American Physical Society.

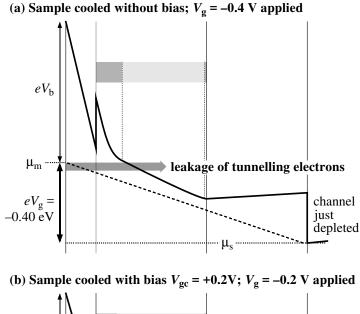

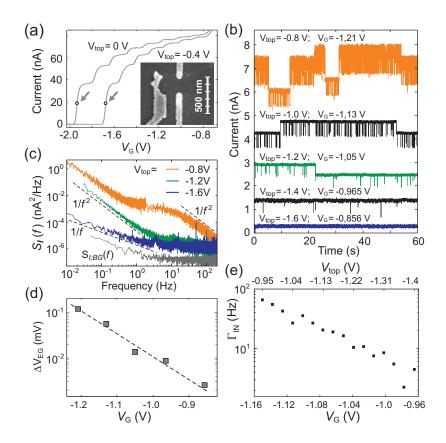

- 2.6 (a) QPC pinch-off curves (two terminal,  $V_{SD} = 0.8 \text{mV}$ , T = 40 mK). The operating point is marked at the first riser of quantum conductance plateau. Inset: a Scanning Electron Micrograph of a typical device layout before deposition of the insulated top gate. (b) QPC time traces for indicated gate voltages, offset for clarity. (c) Power spectra density  $S_I(f)$  from FFT of time traces; setup noise background  $S_{I;BG}(f)$  recorded at zero  $V_{SD}$ . (d) Equivalent gate voltage noise  $\Delta V_{EG}$ . (e) Measured trapping rate in extracted from time traces as in (b), but for a different QPC. Reprinted figure with permission from C. Buizert et al., Phys. Rev. Lett. 101, 226603 (2008) Copyright (2008) by the American Physical Society. . . .

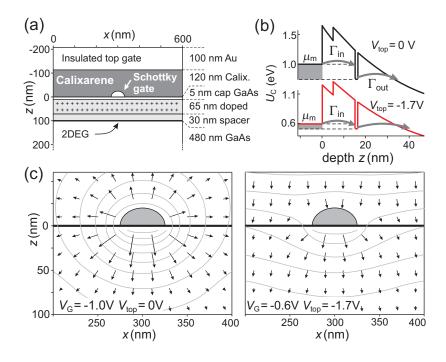

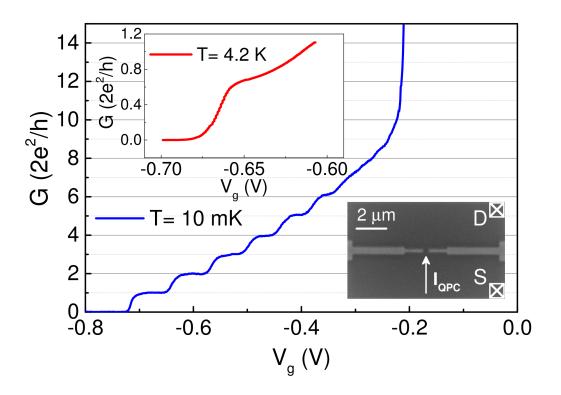

- 2.7 (a) Simulated 2D device structure with  $Al_{0.26}Ga_{0.74}As$  doped- and spacer layer. Si doping  $n_{Si} = 0.3 \times 10^{18} cm^{-3}$ ; Calixarene simulated as SiO<sub>2</sub> with  $\epsilon_r = 7.1$ . (b) Simulated conduction band profile under the Schottky gate at x=300 nm. Tunneling into a localized trap with fixed energy below U<sub>C</sub> occurs most easily from the quasi-Fermi level in the metal lead ( $\mu_m$ ) where the barrier is lowest (this is generally an inelastic process). (c) Quiver plot of the simulated electric field and equipotential lines near the Schottky gate (gray shaded) for the indicated voltage configurations. Reprinted figure with permission from C. Buizert et al., Phys. Rev. Lett. 101, 226603 (2008) Copyright (2008) by the American Physical Society. . . . . . .

###

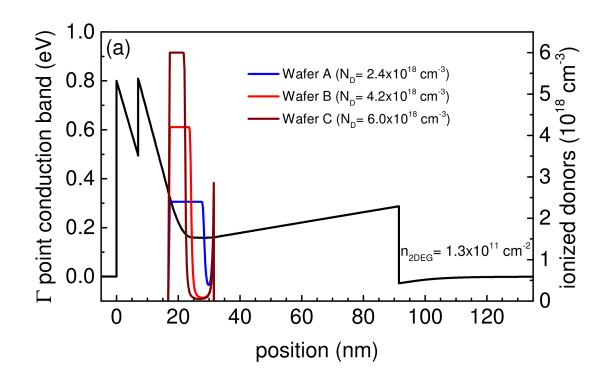

| 2.9  | Conductance G of a QPC as a function of gate voltage $V_g$ at T=10mK.      |    |

|------|----------------------------------------------------------------------------|----|

|      | Top inset: first riser of QPC conductance at $T=4.2K$ . Bottom inset: SEM  |    |

|      | image of fabricated QPC on Wafer B                                         | 42 |

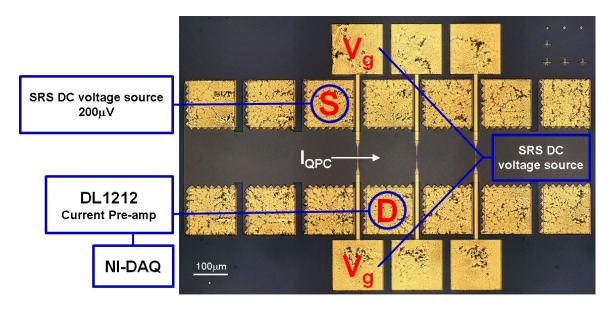

| 2.10 | Device layout and schematic picture of experimental setup for noise mea-   |    |

|      | surements. Three QPCs are being charachterized on single Hall bar device.  |    |

|      | Low noise DC source is used which is an essential component for ultra sen- |    |

|      | sitive noise measurements.                                                 | 43 |

34

36

37

ix

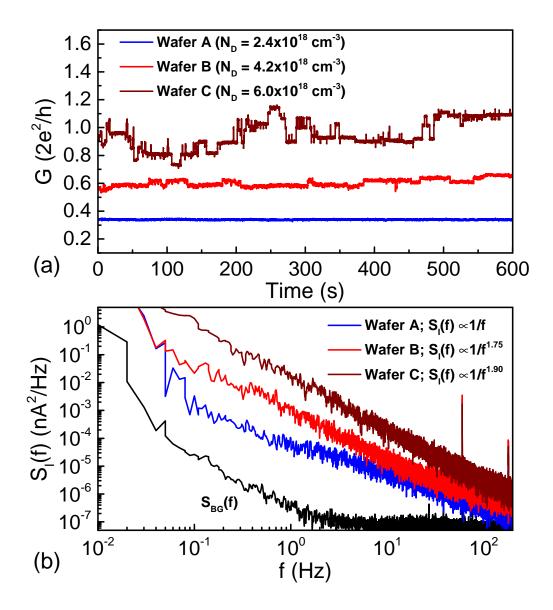

| 2.11 | (a) QPC time traces for structures with different doping densities, offset<br>for clarity (Wafer B is offset by $0.2 \times (2e^2/h)$ and Wafer C is offset by<br>$0.4 \times (2e^2/h)$ ) (b) Noise power spectral density $S_I(f)$ obtained from FFT<br>of time traces, experimental background noise $S_{I;BG}(f)$ measured at zero<br>source drain voltage (black trace)                                                               | 45 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

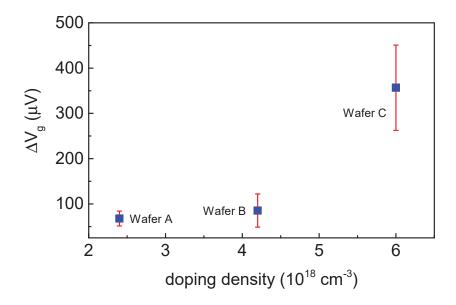

| 2.12 | Equivalent gate voltage noise $\Delta V_g$ vs. doping density for Wafers A, B and C. Each data point represents the average of different QPCs from each wafer. Six QPCs were measured from Wafers A and C, and three QPCs were measured from Wafer B. Error bars represent the standard error computed from the measurements of different QPCs from each wafer.                                                                           | 47 |

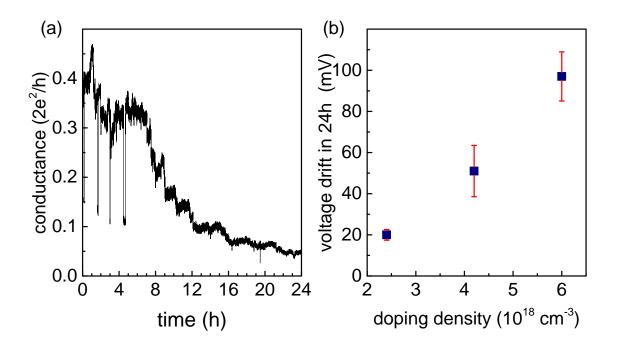

| 2.13 | (a) Long time scale conductance drift. (b) Total amount of gate voltage drift within 1st 24 hours of operation of QPCs for wafers A, B and C with different doping densities.                                                                                                                                                                                                                                                             | 48 |

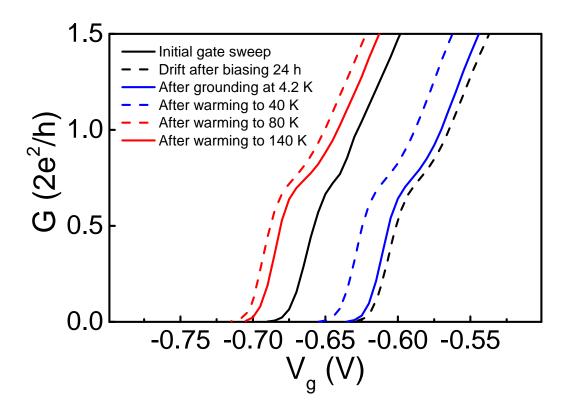

| 2.14 | QPC conductance plot vs gate voltage for Wafer B after warming up the QPC to $T = 40K$ , 80K and 140K.                                                                                                                                                                                                                                                                                                                                    | 49 |

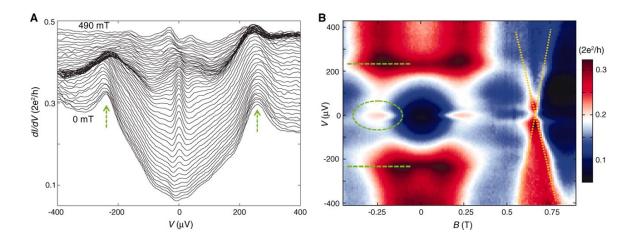

| 3.1  | (A) dI/dV versus V at 70 mK taken at different B fields. Arrows indicate the induced gap peaks. (B) Color-scale plot of dI/dV versus V and B. The ZBP is highlighted by a dashed oval; green dashed lines indicate the gap edges. From V. Mourik, K. Zuo, S. M. Frolov, S. R. Plissard, E. P. A. M. Bakkers, and L. P. Kouwenhoven, Science 336, 10031007 (2012). Reprinted with permission from AAAS                                     | 55 |

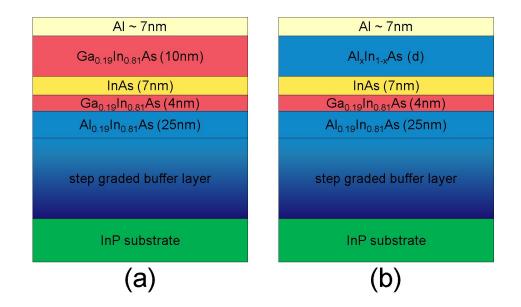

| 3.2  | a) 2D heterostructure used in Ref. [94] to create lithographically defined SC wire for observing Majorana zero modes. A 10nm $In_{0.81}Ga_{0.19}As$ barrier was used to separate 2DEG from the Al film. b) proposed heterostructure to control the amount of hybridization between electronic wave function in the semiconductor and the Al film using $Al_x In_{1-x}As$ barrier with 15% Al content and thickness ranges from 3nm to 9nm | 57 |

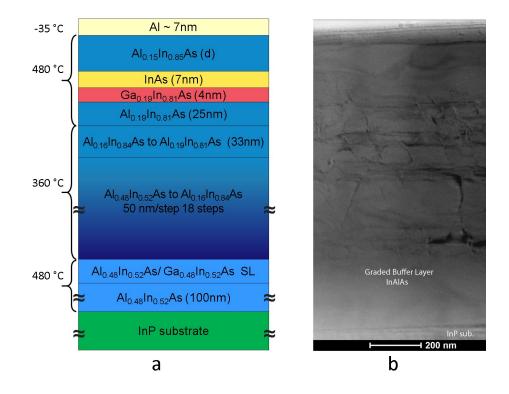

| 3.3  | a) Scheme of hybrid $Al/Al_{0.15}In_{0.85}As/InAs$ layer sequence indicating the composition, thickness and growth temperature of each layer. b) Scanning transmission electron micrograph of a heterostructure with similar step-graded buffer region showing the misfit dislocations $\ldots \ldots \ldots$                                                                                                                             | 58 |

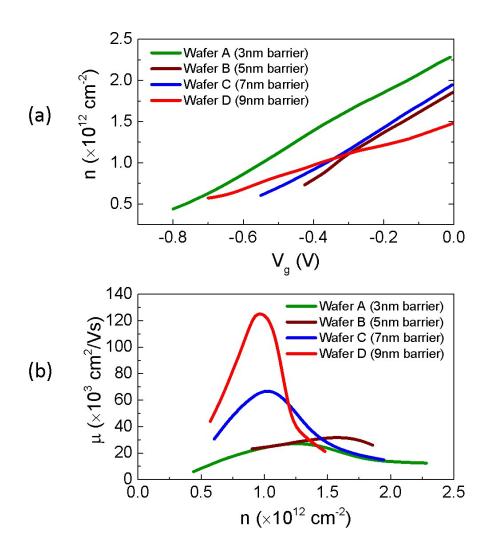

| 3.4  | a) Gate voltage dependence of 2DEG density in InAs QW for wafers with $Al_{0.15}In_{0.85}As$ barrier thickness ranging from 3 nm to 9 nm. b) mobility vs 2DEG density for fabricated Hall bars $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                  | 61 |

Page

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

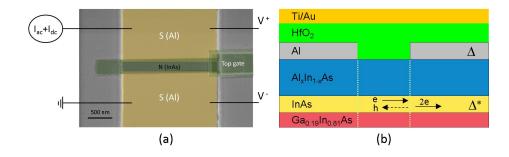

| 3.5    | a) False-color scanning electron micrograph of the S-N-S junction where<br>the normal region is 2DEG in within InAs QW. b) Cross sectional schematic<br>of the SNS device in . Due to the proximity effect, the part of QW covered<br>by Al become superconducting with gap $\Delta^*$ . Andreev reflections happen<br>at interface between the covered and Al stripped regions                                                                                                                                                                                                       | 63 |

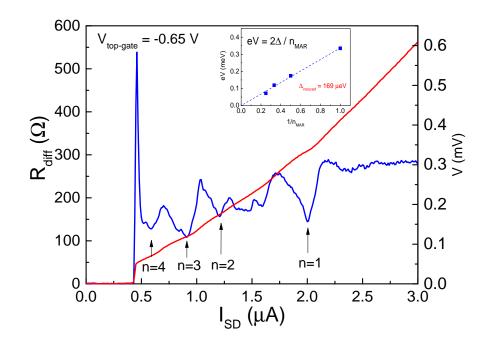

| 3.6    | The Differential resistance and DC component of the voltage drop across<br>the SNS junction. Multiple Andreev reflections (MAR) corresponding to<br>the induced gap $\Delta^*$ are shown. The inset shows a linear fit to the MAR<br>resonances from which the induced gap $\Delta^*$ is extracted                                                                                                                                                                                                                                                                                    | 64 |

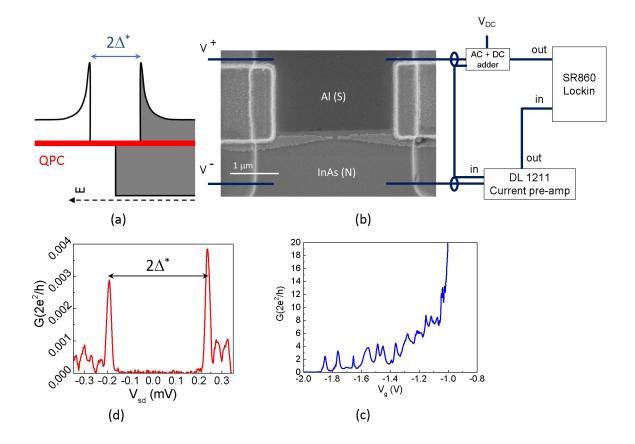

| 3.7    | a) Schematic of local density of states in the normal metal an supercon-<br>ductor. b) False-colored scanning electron micrograph of the S-QPC-N<br>device, showing the measurement configuration. The normal metal is<br>2DEG located in the InAs QW and superconducting part is the prox-<br>imitized 2DEG by Al thin film which is superconducting with induced<br>gap $\Delta^*$ . QPC is used to tune the NS interface into the tunneling regime<br>with $G_{QPC} << 2e^2/h$ . c) 2DEG depletion curve and QPC pinch off. d)<br>Differential conductance in the tunneling regime | 66 |

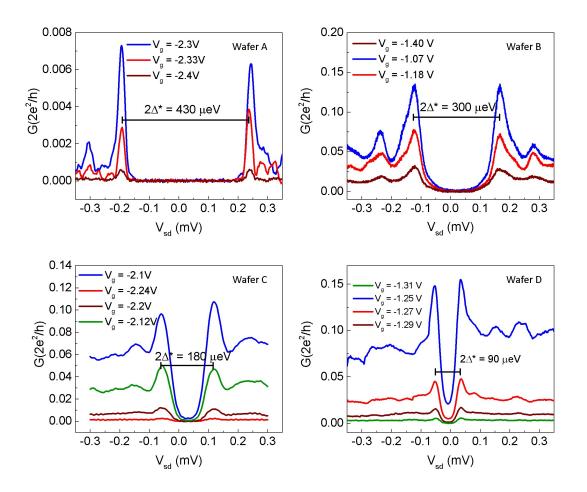

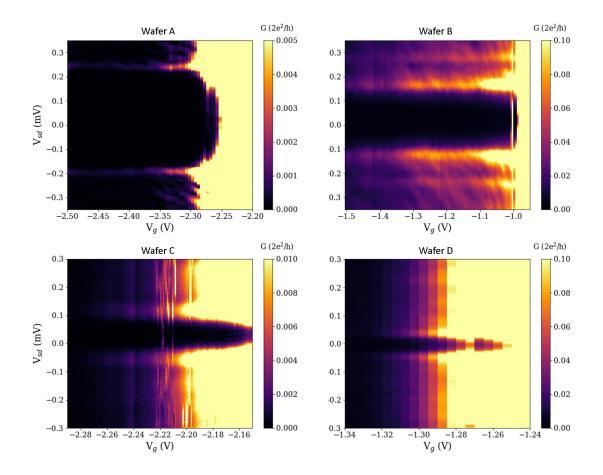

| 3.8    | Finite bias spectroscopy showing BCS-like coherence peaks for heterostruc-<br>ture with different barrier thickness 3 nm (Wafer A), 5 nm (Wafer B), 7<br>nm (Wafer C) and 7 nm (Wafer D)                                                                                                                                                                                                                                                                                                                                                                                              | 67 |

| 3.9    | 2D tunneling conductance as a function of QPC gate voltage and source-<br>rain bias. The BCS-like coherence peaks survived at more negative QPC<br>gate bias.                                                                                                                                                                                                                                                                                                                                                                                                                         | 68 |

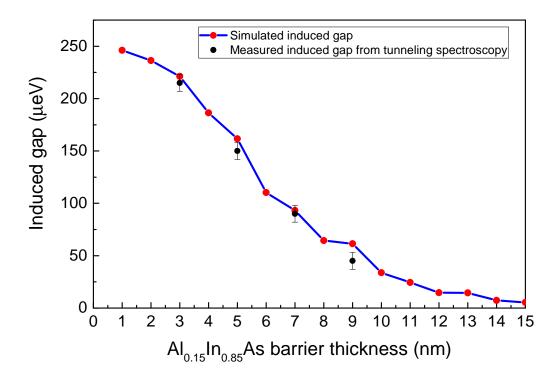

| 3.10   | Measured and simulated induced gap dependence vs $Al_{0.15}In_{0.85}As$ top barrier thickness.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 69 |

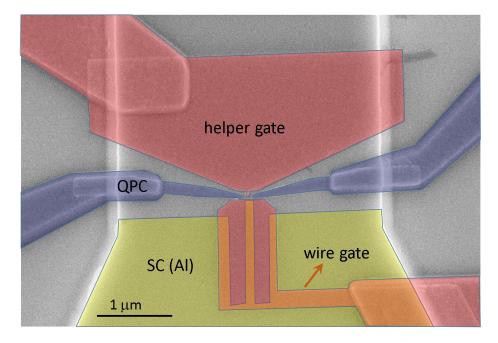

| 3.11   | Lithographically defined SC wire to measure the effective g-factor. QPC are used to tune the conductance into the tunneling regime and helper gate is utilized to fine tune the potential landscape around the QPC. Wire gate is used to deplete the 2DEG in the normal region such that the SC wire becomes isolated.                                                                                                                                                                                                                                                                | 70 |

### ABSTRACT

Saeed Fallahi Ph.D., Purdue University, August 2019. Growth and Characterization of Two-Dimensional III-V Semiconductor Platforms for Mesoscopic Physics and Quantum Devices. Major Professor: Michael J. Manfra.

Achievements in the growth of ultra-pure III-V semiconductor materials using state of the art molecular beam epitaxy (MBE) machine has led to the discovery of new physics and technological innovations. High mobility two-dimensional electron gas (2DEG) embedded in GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructures provides an unparalleled platform for many-body physics including fractional quantum Hall effect. On the other hand, single electron devices fabricated on modulation doped GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructures have been extensively used for fabrication of quantum devices such as spin qubit with application in quantum computing. Furthermore, epitaxial hybrid superconductor-semiconductor heterostructures with ultra clean superconductor-semiconductor interface have been grown using MBE technique to explore rare physical quantum state of the matter namely Majorana zero modes with non-abelian exchange statistics.

Chapter 1 in the manuscript starts with description of GaAs MBE system at Purdue University and continues with the modifications have been made to MBE hardware and growth conditions for growing heterostructures with 2DEG mobility exceeding  $35 \times 10^6 cm^{-2}/Vs$ . Utilizing an ultra-high pure Ga source material and its further purification by thermal evaporation in the vacuum are determined to have major impact on growth of high mobility GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructures.

Chapter 2 reports a systematic study on the effect of silicon doping density on low frequency charge noise and conductance drift in laterally gated nanostructures fabricated on modulation doped  $GaAs/Al_xGa_{1-x}As$  heterostructures grown by Molecular Beam Epitaxy (MBE). The primary result of this study is that both charge noise and conductance drift are strongly impacted by the silicon doping used to create the two-dimensional electron gas. These findings shed light on the physical origin of the defect states responsible for charge noise and conductance drift. This is especially significant for spin qubit devices, which require minimization of conductance drift and charge noise for stable operation and good coherence.

Chapter 3 demonstrates measurements of the induced superconducting gap in 2D hybrid Al/Al<sub>0.15</sub>In<sub>0.85</sub>As/InAs heterostructures which is a promising platform for scaling topological qubits based on Majorana zero modes. The 2DEG lies in an InAs quantum well and is separated from the epitaxial Al layer by a barrier of Al<sub>0.15</sub>In<sub>0.85</sub>As with thickness d. Due to hybridization between the wave functions of 2DEG and superconductor, the strength of induced gap in the 2DEG largely depends on the barrier thickness. This chapter presents a systematic study of the strength of the induced gap in hybrid Al/Al<sub>0.15</sub>In<sub>0.85</sub>As/InAs superconductor/semiconductor heterostructures as a function of barrier thickness.

# 1. MOLECULAR BEAM EPITAXY OF ULTRA PURE GAAS AND $AL_XGA_{1-X}AS^{-1}$

### 1.1 Introduction

Molecular beam epitaxy (MBE) is a state of the art material growth technique to grow advanced heterostructures with composition and doping profiles controlled on a nanometer scale. The growth of materials takes place under ultra-high vacuum (UHV) conditions on a heated crystalline substrate by the interaction of adsorbed species supplied by atomic or molecular beams. The main focus of this chapter is devoted to MBE growth of high-purity GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterostructures embedding two-dimensional electron gas (2DEG). The lattice-matched crystalline material in GaAs-Al<sub>x</sub>Ga<sub>1-x</sub>As system (lattice mismatch between GaAs and the AlAs is ~ 0.1%) enables growing heterostructures with negligible mechanical stresses and with very few interface states.

High purity semiconductor materials are necessary for the fabrication of various state of the art quantum devices, such as spin-qubits and investigation of many body effects, such as those leading to fractional quantum Hall effect. The development of high purity GaAs and  $Al_xGa_{1-x}As$  is closely related to the identification of residual impurities in these materials and the utilization of various tools and techniques to purify the source materials. The most commonly employed characterization of material quality is the electron mobility i.e. how fast the electrons move when an electric field is applied, in 2DEG embedded in the GaAs/Al<sub>x</sub>Ga<sub>1-x</sub>As heterojunction. Crudely speaking, mobility measures an electrons ability to carry current without undergoing

<sup>&</sup>lt;sup>1</sup>THIS CHAPTER IS ADAPTED FROM J. CRYST. GROWTH, VOL. 441, G. C. GARDNER, S. FALLAHI, J. D. WATSON, AND M. J. MANFRA, 'MODIFIED MBE HARDWARE AND TECHNIQUES AND ROLE OF GALLIUM PURITY FOR ATTAINMENT OF TWO DIMENSIONAL ELECTRON GAS MOBILITY >  $35 \times 10^6 CM^2/VS$  IN ALGAAS/GAAS QUANTUM WELLS GROWN BY MBE', 71-77, COPYRIGHT 2016, WITH PERMISSION FROM ELSEVIER.

large-angle scattering. Mobility is related to the momentum relaxation time  $\tau$  via  $\mu = e\tau/m^*$ , where e and  $m^*$  are the charge and the effective mass of electron respectively. In the systems with sufficiently small remote ionized scattering, the mobility is known to be limited by residual background charged impurities at temperatures below 1K where the phonon scattering vanishes [1–3]. Decades of technological innovation made it possible to reach low-temperature mobility  $\sim 31 \times 10^6 cm^2/Vs$  at Bell Laboratories [4] via utilizing symmetric auxiliary doping wells above and below the primary quantum well embedding the 2DEG. These results have been confirmed later by Umansky and coworkers [5]. The upward mobility history of GaAs is shown in Fig 1.1 indicating the steps leading to the improvement of 2DEG quality.

Fig. 1.1. A historical view of the upward electron mobility in GaAs heterostructures and the steps leading to this improvement. Reprinted from Physica E, vol. 20, L. Pfeiffer, and K. W. West, 'The role of MBE in recent quantum Hall effect physics discoveries', 5764, Copyright 2013, with permission from Elsevier.

Many useful textbooks have been published on the subject of MBE growth technique, historical review of MBE growth, UHV systems and MBE components and Materials. [6–12]. In this chapter, a compact description of GaAs MBE system at Purdue University is presented and modification to MBE hardware and growth conditions to attain 2DEG mobility exceeding  $\sim 35 \times 10^6 cm^2/Vs$  is explained. More detailed information on MBE growth technique can be found in well written thesis by my colleagues Dr. John Watson [13] and Dr. Geoff Gardner [14].

## 1.2 High Mobility GaAs MBE System

GaAs MBE system at Purdue University is a modified Veeco Gen II MBE system specifically designed to produce ultra-high quality 2DEG. As it is shown in Fig. 1.2, it consists of a growth chamber, a buffer chamber and an introduction chamber (loadlock), with the vacuum level improving progressively towards the growth chamber.

The quick-entry load-lock chamber is used to transfer wafers into and out of the growth chamber without breaking the UHV conditions, which would otherwise require days or weeks to recondition the growth chamber. Load-lock chamber is equipped with a heating filament to outgass (desorb) most of the water vapor and other gases which are loosely bonded to the GaAs substrate and the Ta-block that the substrate is mounted on. A CT-8 cryopump pumps the load-lock space down to  $\sim 5 \times 10^{-9}$  Torr and the wafer outgasses at 120 °C for 10h.

The substrates are then transferred to the buffer chamber for additional outgassing at 350 °C for 3.5h to further remove water vapor and other gasses as well as  $As_2O_3$ which presents in native oxide. A CT-8 cryopump pumps the buffer chamber down to  $\sim 2 \times 10^{-11}$  Torr. The buffer chamber is equipped with SRS residual gas analyzer (RGA) to perform gas analysis, leak detection and vacuum processing such as Ta block outgassing at elevated temperatures. RGA is an extremely useful tool to probe the cleanness of the outgassed wafer by acquiring live spectra of the species partial pressure coming off the wafer/Block during the outgass in a range from 1 to 200

Fig. 1.2. Modified Veeco Gen II MBE system at Purdue University.

AMU. In the next section, an example of RGA spectra is shown during the standard wafer outgass in buffer chamber (i.e. 3.5h at 380 °C) before transferring to growth chamber.

The growth chamber is pumped through custom all-metal gate valves by 3 Brooks CT-10 cryopumps which each has a pumping speed of 3000 l/s for air. Growth chamber also contains an additional titanium sublimation pump which can effectively reduce the hydrogen partial pressure by an order of magnitude from  $\sim 1 \times 10^{-11}$  Torr to  $1 \times 10^{-12}$  Torr. The Growth chamber contains of hollow-walled internal liquid-nitrogen-filled cyropanel which is cooled to 77K to help in reducing the base pressure

and to serve as thermal isolation between cells from cross talk and is maintained in this condition for several years with proper planning and good fortune. The base pressure of growth chambers reaches  $< 2 \times 10^{-11}$  Torr when the system in idle condition and no growth is happening. All effusion cells and large capacity arsenic cell are custom designed to reduce thermal load into the growth chamber during the crystal growth. Consumption power of the Ga source to grow GaAs with 1 monolayer/s growth rate is determined to be  $\sim 120$  W and the Al cell the power output to grow Al<sub>0.24</sub>Ga<sub>0.76</sub>As is found to be  $\sim 180$  W. For both n-type and p-type doping we utilized home-built Si and C filament sources with power consumption of 70 W and 280 W respectively during the deposition. The MBE growth chamber is also equipped with large area shutter (main shutter) which is placed between the sources and the substrate manipulator to shield the substrate and manipulator from all source fluxes. The growth chamber also includes a 200 AMU SRS RGA and AMETEK Dycor RGA to monitor the residual gas partial pressure and cleanness of the UHV environment. Last but not least, the MBE growth chamber has equipped with growth rate characterization tool namely reflection high-energy electron diffraction (RHEED) to calibrate the growth rates for each heterostruture growth.

### 1.3 RGA spectra in MBE system

As mentioned in the previous section, the buffer and growth chambers in MBE system are equipped with RGA to probe and monitor the partial pressure of species and prevent growth chamber contamination by stopping transfer of blocks with a suspicious looking RGA spectra during the buffer outgass into the growth chamber.

Figure 1.3 shows a clean RGA spectra from growth chamber at MBE idle condition with reactor pressure  $\sim 2 \times 10^{-11}$  Torr. Dominant species include Water, Nitrogen Carbon Dioxide, and Arsenic. The amount of C and AsO species which are dominant source of electron trap in the bulk of GaAs is minimal with their partial pressures below  $1 \times 10^{-12}$  Torr and are close to the noise floor of RGA spectra. This prototype

Fig. 1.3. Clean RGA spectra from Reactor at idle condition with  $P_{reactor} \sim 2 \times 10^{-11}$  Torr. The dominant species are labeled which all have partial pressures below  $1 \times 10^{-11}$  Torr

RGA spectra serves as a reference to compare with situations in which the quality of grown wafers degrades (as determined by low-temperature electron mobility) and it is used to troubleshoot the source of contamination.

The source of contamination is always external and is related to the cleanness of the substrates that are loaded into the MBE system and extra care should be taken during mounting new wafers on Ta block. The possible contamination are rooted in the tools that have been used for mounting new wafer. These tools include tweezers, Ga melt that is used to stick the substrate on Ta block, Ga container and the glove. Previously a Teflon applier were used to apply Ga on the Ta block to wet the surface and it is found to be a source of Fluorine (F) contamination with 19 AMU/e which is extremely hard to remove from the vacuum chamber. A custom applier from Ta

Fig. 1.4. New GaAs wafer outgass in the buffer chamber. (a) Buffer chamber pressure (black solid line) and thermal treatment profile (red solid line) during wafer outgass at 380 °C for  $\sim$  5h. (b) An overlay of base RGA spectra in the buffer chamber with RGA spectra at the buffer chamber peak pressure during during wafer outgass.

sheet is made to replace Teflon spatula for applying Ga melt on the blocks. During the substrate mount process, a clean lab coat should be worn and head net should be put on to prevent falling any dust or hair on the substrate. After following all of these hygiene protocols, there is still a chance that the loaded wafer is contaminated from unknown source and one should always monitor the RGA spectra during the block outass in the buffer chamber to give it a green pass to enter the growth chamber.

A characteristic RGA spectra for a clean outgassed wafer in the buffer chamber is shown in Fig. 1.4. Figure 1.4(a) shows temperature profile and buffer chamber pressure trend during wafer outgass at 380 °C. Buffer chamber base pressure is ~  $2 \times 10^{-11}$  Torr before starting the wafer outgass and it peaks at ~  $2 \times 10^{-9}$  Torr before temperature reaches 380 °C and the pressure falls down during 3.5h sitting at 380 °C and reaches ~  $4 \times 10^{-11}$  Torr at the end of the outgass. RGA spectra at the buffer peak pressure is shown in Fig. 1.4(b) (red solid line) indicating that the major species that come off the wafer are Nitrogen (mass 28) and water (mass 18). These species might also be trapped between the wafer and the block that has been mounted on with Ga glue and they get a chance to be release during the outgass as visible with pressure spikes in Fig. 1.4(a). This RGA spectra at peak pressure is characteristics of a clean wafer outgass in the buffer chamber and has green pass permit to enter the growth chamber.

### 1.4 High mobility heterostructure design and growth campaigns

The high mobility heterostructure consists of a 30 nm GaAs quantum well surrounded by AlAs/GaAsSi delta-doped/AlAs (3nm/2nm/3nm) doping wells which symmetrically located at 75nm above and below the main 30nm quantum well. This doping scheme was first proposed by Baba in 1983 [15] and modified by Friedland in 1996 [16] to reduce impurity scattering in remotely doped GaAs single quantum wells due to accumulation of heavy-mass X electrons within the AlAs layers. This doping scheme also prevents the formation of DX centers and enhances doping efficiency. DX centers are deep level traps associated with donors in IIIV semiconductors. Formation of DX centers in Al<sub>x</sub>Ga<sub>1-x</sub>As with x0.22 is responsible for the reduced conductivity as well as the persistent photoconductivity observed in this material at low temperatures [17, 18]. Confining the electrons in a thin 3 nm GaAs well raises the quantized electron energy level in the well and allows charge transfer to the main 30 nm GaAs quantum well embedding 2DEG. Fig. 1 shows the layer stack of active region and simulated band profile for high mobility 2DEG heterostructure using the nextnano<sup>3</sup> software package [19].

Fig. 1.5. (a) The active region layer stack used to grow a high mobility 2DEG with electron density  $n = 3.0 \times 10^{11} cm^{-2}$ .; and (b)  $\Gamma$ and X conduction band minimum along the growth direction. Electron density in the main GaAs quantum well ( $\Gamma$  band) and electron density in the screening AlAs layers (X band) are shown accordingly. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$  in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

The main GaAs quantum well is separated by 75nm  $Al_{0.24}Ga_{0.76}As$  spacer layer from doping regions at the top and the bottom. The 24% Al mole fraction with 200 meV conduction band offset relative to GaAs QW is sufficient to confine electrons in the main quantum well before populating higher sub-bands at  $n > 3.0 \times 10^{11} cm^{-2}$ . At the same time, 24% Al content of AlGaAs layer reduces interface roughness and incorporation of unintentional impurities associated with higher mole fraction barriers. The Si doping density is  $1 \times 10^{12} cm^{-2}$  in the top doping well and  $0.8 \times 10^{12} cm^{-2}$  in the lower doping well which results in total charge transfer of  $n = 3.0 \times 10^{11} cm^{-2}$  into the main 30nm GaAs quantum well. Approximately  $6 \times 10^{11} cm^{-2}$  electron density transfer to the GaAs surface to compensate the surface states. A significant fraction (approximately 50%) of the electrons resides in the X-band of the AlAs layers flanking the narrow GaAs doping wells. These residual electrons screen the disorder potential created by the ionized dopants. The screening electrons do not form parallel conduction channel in low-temperature transport measurements due to their low mobility arising from their proximity to their parent silicon ions and their large effective mass in the X band of AlAs. All the layers except doping wells are grown at substrate temperature of 635 °C as measured by optical pyrometry. The substrate temperature is rapidly decreases to 450 °C for deposition of Si atoms to reduce the Si dopant migration [20], and a thin layer of GaAs is deposited following the silicon to reduce subsequent surface segregation. The growth proceeded at 1m/hr growth rate and the As flux ratio to Ga flux are set to 20 which corresponds to beam-equivalent pressure of  $6.0 \times 10^{-6}$  Torr for arsenic. Reducing the As flux below  $6.0 \times 10^{-6}$  Torr results in a hazy end-product in regions with low As beam exposure.

This active region is grown on top of the buffer layer separating it from the substrate. The buffer layer consists of two different superlattices (SL) namely 10nm GaAs SL and (10nm/3nm)  $Al_{0.24}Ga_{0.76}As/GaAs$  SL with 20 s pause between each SL layer. The role of GaAs SL layer is to smooth out the pristine GaAs substrate which becomes rougher during the initial oxide removal at substrate temperature  $580 - 620^{\circ}C$  under arsenic flux. The role of  $Al_{0.24}Ga_{0.76}As/GaAs$  SL is to block impurities from migrating to the active region due to the high chemical reactivity of the aluminum-containing layers and more smoothing of the surface.

It has been theoretically predicted that for AlGaAs spacer layer thicker than 70 nm, the mobility is limited by unintentional background impurities in the vicinity of the 2DEG [21,22] and achieving electron mobility  $> 30 \times 10^6 cm^2/Vs$  requires a uniform background impurity density below  $2 \times 10^{13} cm^{-3}$ . It has been shown that remote ionized impurity scattering is only responsible for 10% of the total scattering rate [1,2]. This has been our motivation to purify the source materials either in-situ and/or ex-situ in order to grow high quality materials with minimal impurities.

In our first growth campaign starting from Jan 2011 to Dec 2013, we loaded commercially available Ga source with 7N purity (99.99999%) [23] and Al source with 6N5 purity (99.99995%) [24] and Arsenic source with 7N5 purity (99.999995%) [25] into MBE system. Impurity levels are measured by glow discharge mass spectrometry (GDMS). The early grown wafers showed very low quality transport results with electron mobility  $\sim 1 \times 10^5 cm^2/Vs$  despite establishing very good UHV condition. This corresponds to p-type impurity concentration of  $\sim 1 \times 10^{15} cm^{-3}$  as determined by electrical characterization of unintentionally doped bulk GaAs layers (5-10  $\mu$ m). Hence the purest commercially available material is still dirty when it is considered to be loaded into the growth chamber and the source materials need to be additionally purified before using it for high mobility crystal growth.

A commonly used approach for cleaning up the source materials is via extended outgassing at high temperatures. Since most impurities like carbon and oxygen have higher vapour pressure than the source materials (Ga, Al and Si sources), the extended outgassing will clean up the materials by evaporating the impurities at higher temperatures. The As source is not subjected to outgassing treatment because it has high vapor pressure at temperature above 275 °C.

After loading the source materials into the growth chamber, the gallium sources were initially outgassed at 100 °C above their normal growth temperature for 7 h and finally outgassed at 200 C above growth temperature for 5 h. Outgassing at +200 C corresponds to a GaAs growth rate of 20  $\mu$ m/h. During the entire outgassing process, the substrate manipulator is kept in the transfer position such that the wafer puck points away from the sources and the beam flux gauge faces towards the sources. The main shutter that has been introduced previously is placed immediately in front of the ion gauge to protect it and other critical components on the manipulator from the elevated flux. During the outgass, the shutter in front of the Ga source effusion cells is opened. A small arsenic flux  $\sim 2 \times 10^{-6}$  Torr is maintained during the cell outgassing to minimize deposition of liquid metal on critical components such as BF ion gauges electrical connections. The whole outgassing process is visually inspected to check the cleanness of crucible lips and the amount of droplet formation inside the crucible interior.

Creep of Al covering up the crucible lip that occurred during the time that the Al shutter was closed

Fig. 1.6. a), b), c) and d) Creep of Al melt during the the successive outgassing of Al cell. e) Al has crept all the way up covering the crucible lip.

Special care should be taken during outgassing of Al source as it tends to climb up the crucible side walls and leads to possible flowing Al out of the crucible. Keeping the crucible lip colder than the melt increases the viscosity and slows down the Al creep. This is the reason the source shutter should be open during the entire outgassing. Figure 1.6 shows the gradual creeping of Al during the outgassing of Al source. It clearly shows that successive outgassing of Al cell results in building up Al puddles near the crucible lip. Figure 1.6e shows a catastrophic event when the Al shutter was closed during normal growth of GaAs/AlGaAs heterostrcutures but at growth rate. Ga cells do not suffer from metal creep up but it forms massive amount of Ga droplets that become bigger and bigger for an extended outgassing period. larger Ga droplets that form at the crucible orifice roll back into the hot melt and spit small particles of Ga on the wafer.

Figure 1.7 shows the improvement of 2DEG mobility for single interface heterojunction (SHJ) and doping well structures as a function of growth number in the first growth campaign. The first couple of single interface heterojunctions (SHJ) grown before Ga source outgassing showed insulating behaviour indicating a large amount of p-type impurities presents in the sample who eat up the charge carriers. However, after outgassing of Ga1 at +200 °C for 5h, the SHJ samples showed an electron mobility of  $\sim 1 \times 10^6 cm^2/Vs$  and improved upon growing more wafers. Outgassing Al cell had minimal impact on the mobility improvement since the 2DEG electronic wave function exists primarily in the GaAs quantum well and not in the AlGaAs barrier. The rapid raise of mobility after outgassing Ga cell is believed to be due to the evaporation of high vapour pressure impurities in the Ga source. Further improvement in the mobility upon each growth is due to the self-clean up mechanism which happens at normal growth temperatures of Ga and Al source. After approximately 75 2DEG growths, the mobility reached  $\sim 20 \times 10^6 cm^2/Vs$ , where it saturated for the remainder of the first growth campaign. Low-temperature magneto-transport measurement of this high mobility 2DEG revealed development of fractional quantum states as is shown in Fig. 1.8.

Fig. 1.7. Evolution of 2DEG mobility for single interface heterojunction (SHJ) and doping well structures as a function of growth number in the first campaign. Ga1 and Al1 refers to the particular cells used in the MBE for growing these heterostructures. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$  in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

The first growth campaign ended after As source is totally depleted. Total number of growths in the first campaign reached 420 growths with different heterostructures designs for several research projects including spin qubit and fractional quantum Hall effect [26–32].

Fig. 1.8. Magnetotransport measurement results at 0.3K from a sample with mobility of  $20 \times 10^6 cm^2/Vs$  and 2DEG density of  $2.9 \times 10^{11} cm^{-2}$ .

In the  $2^{nd}$  growth campaign started from Aug 2013 until now, several modifications were made to MBE hardware as well as source materials to reduce the background impurities in gown wafers predominantly emanating from the source materials. We designed a substrate heater with a relatively dense resistive heater elements to reduce the thermal load in the growth chamber.

Apart from the effusion cells thermal load, the substrate heater also produces a substantial thermal load  $\sim 150$  W which varies for different Ta substrate holders and depends on the history of the holder. There is an experimental report by Umansky who has conducted a research on the effect of thermal load on the mobility of grown wafers and interestingly obtained an increase in mobility  $\sim 40\%$  after reducing the

۲

heating power by ~ 30% [1]. This finding suggested to redesign our MBE substrate heater in order to reduce the overall thermal load in the growth chamber. In our new design of substrate heater which is shown in Fig. 1.9, we increased the number of resistive heater elements from 4 to 6. Additionally, we doubled the number of heat shielding layers between the filament and the reminder of the substrate manipulator. Also, the opening to the filaments feet in the heat shield is reduced from 0.19" to 0.12" in diameter to prevent leakage of thermal radiation. As a result of these modifications, the required power to reach normal growth temperature of 635 °C decreased from 150 W to 120 W.

Fig. 1.9. (a) Four filaments substrate heater in the  $1^{st}$  growth campaign. (b) Six filaments substrate heater in the  $2^{nd}$  growth campaign. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$  in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

We built an ancillary chamber to outgass and clean the effusion cells and the crucibles to be loaded into the growth chamber. This ultra-clean UHV chamber is pumped by a CT-8 cryopump and can reach pressures below X-ray limit of a standard ion gauge (i.e.  $2 \times 10^{-11}$ Torr). This chamber is equipped with 200 AMU RGA and it

contains 4 source ports and it is designed to allow evaporated gallium to be captured in a vessel at the bottom of the chamber.

We constructed a custom glovebox to minimize introducing detrimental gas such as oxygen and water vapor pressure into the growth chamber. Commonly used technique for loading new source materials required using glovebag which is sometimes cumbersome and it suffers from poor visibility. This custom built glovebox that is shown in Fig. 1.10, provides significant advantages for major MBE maintenance operations including excellent visibility, robustness and the necessary manual dexterity for handling source materials and loading the crucible inside the effusion cell. This glovebox consists of a big opening in the back that seals on the source ports assembly and it is equipped with multiple ports for handling and assembling source flanges on growth chamber ports. We use a balloon made of polyethylene plastic to actively purge the entire volume of glovebox via inflating the ballon using pure Argon gas. The purity of Argon gas used for purging the glovebox is 99.9999% (6N) and it has been further purified after passing through a heated titanium gettering furncae, model 2G-100-SS by Centorr [33]. After couple of outgassing attempts 10, the amount of oxygen level inside the glovebox reaches below 30 pmm as measured by the trace oxygen analyzer [34].

By improving our MBE maintenance techniques and utilizing custom-made tools, we dramatically reduced the introduction of water vapor and oxygen gas into the growth chamber during charging the source materials and removed the necessity to bake the system at 200 °C after maintenance. This is particularly beneficial in an arsenic-filled MBE which readily absorbs water vapor and oxygen onto large surface areas covered with arsenic. By eliminating the baking process we keep the sources and the manipulator clean because the bake process can potentially redistributes the contaminants over the entire deposition chamber including the sources and substrate manipulator.

We quantified the the efficiency of the improved maintenance technique by comparing the RGA spectra before and after venting the growth chamber. After warming

Fig. 1.10. The glove box enclosure which seals to the source flange of the MBE chamber and connects via a tunnel bag to UHV outgassing chamber. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$  in Al-GaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

the MBE cryo shroud to room temperature and before venting the growth chamber, the pressure in the growth chamber was  $\sim 1 \times 10^{-10}$  Torr. After venting and loading new sources, the growth chamber is pumped back down and the pressure in the growth chamber returned to below  $2 \times 10^{-10}$  Torr within 24 h. The RGA spectra in Fig. 1.11 shows minimal change in the constituent partial pressures indicating the cleanness of the utilized MBE maintenance technique. The only species that have noticeable increase in partial pressure are water (18 AMU/e) and Argon (40 AMU/e). Note that Argon has been used as the vent gas. Water and Argon partial pressure recovers after back-filling the cryo shroud with liquid nitrogen and after couple days pumping of the growth chamber.

Fig. 1.11. Comparison of RGA spectra before vent and 24h after venting the growth chamber.

We studied the effect of Ga source material purity on the quality of our high mobility structure by loading two distinct gallium ingots with different nominal purity. One gallium effusion cell labeled as Ga1 is loaded with 7N gallium ingots supplied by Alcan [23] and it was the same lot that has been used in the first growth campaign. The second gallium effusion cell labeled as Ga2 is loaded with 8N gallium ingots supplied by Molycorp Rare Metals Inc. [35]. These ingots were packaged with tantalum sleeves of our own design between the ingot and the plastic packaging to reduce the risk of the plastic contaminating the gallium. Two aluminum effusion cells labeled as

All and Al2 are loaded with ULVAC [24] material from the same lot used in the first growth campaign.

Fig. 1.12. (a) Discrete jumps in mobility are demonstrated using our high temperature outgassing procedure. (b) Plot of 2DEG mobility as a function of growth number demonstrates the difference in improvements between the two different gallium source materials despite receiving the same treatment. Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$ in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

Figure 1.12 shows the evolution of electron mobility for high mobility heterostructure as a function of growth number and its variation after each high temperature outgassing exercise. Discrete jumps in mobility are seen in Fig. 1.12a with each outgassing of the Ga2 cell (Molycorp source material with 8N purity). It is obvious that each mobility jump is related to each outgassing experiment. High mobility heterostructures grown with Ga2 source reaches above  $20 \times 10^6 cm^2/Vs$  after 10 growths and 2 high temperature outgassings  $(+200 \circ 3 \text{ hours})$  experiments. After the 3rd outgassing experiment, the mobility increased above  $30 \times 10^6 cm^2/Vs$  for high mobility structures grown with Ga<sub>2</sub>. Similar discrete jumps were also observed for the Ga<sub>1</sub> cell (Alcan source material with 7N purity), albeit with lower absolute value of mobility when compared to Ga2. Despite receiving the same number and intensity of high temperature outgassing, Ga2 was consistently able to produce samples of higher mobility than Ga1. The highest mobility achieved with Ga1 saturated at approximately  $20 \times 10^6 cm^2/Vs$ . We note that the aluminum cell outgassing (Al1 or Al2) did not influence this conclusion. The differences between Ga1 and Ga2 are most clearly seen in Fig. 1.12b, where the evolution of mobility for each Ga cell is shown over the course of the campaign. It seems that more outgassing of Ga cells can potentially lead to growth of even higher mobility but it comes at a cost of damaging moving parts on substrate manipulator due to material buildup. We continued the rest of campaign by growing heterostructures utilized to study fractional quantum Hall effect [36-40], spin-qubit [41-50], high electron mobility transistors [51] and other mesoscopic physics research [52–55].

Magnetotransport results for high mobility GaAs quantum well grown at the peak mobility of  $2^{nd}$  growth campaign reveals well developed fractional quantum Hall states for both low and high electron density wafer. To obtain a low 2DEG density wafer  $1.1 \times 10^{11} cm^{-2}$ , the setback of doping layer in the high mobility heterostructre has been increased from 75 nm to 225 nm in order to reduce the charge transfer to the main quantum. Figure 1.13 shows the measurement results at 0.3K for high 2DEG density and low 2DEG density samples grown in  $2^{nd}$  growth campaign. Electron mobility exceeding  $35 \times 10^6 cm^2/Vs$  is achieved at  $n = 3.0 \times 10^{11} cm^{-2}$  with welldeveloped fractional quantum Hall states. Based on the calculation in Ref. [22] our data suggests that the density of background charged impurity has been reduced to  $\sim 1 \times 10^{13} cm^{-3}$ . Particularly noteworthy is the development of the fractional quantum Hall series converging to  $\nu = 1/2$  in the low density sample. The appearance of many

Fig. 1.13. The top panel shows transport data from a sample with mobility of  $35 \times 10^6 cm^2/Vs$  and a density of  $3.0 \times 10^{11} cm^{-2}$ . The bottom panel shows transport data from a sample with lower density of  $1.1 \times 10^{11} cm^{-2}$  and mobility of  $18 \times 10^6 cm^2/Vs$  displaying strong fractional state development near  $\nu = 1/2$ . Reprinted from J. Cryst. Growth, vol. 441, G. C. Gardner, S. Fallahi, J. D. Watson, and M. J. Manfra, 'Modified MBE hardware and techniques and role of gallium purity for attainment of two dimensional electron gas mobility >  $35 \times 10^6 cm^2/Vs$  in AlGaAs/GaAs quantum wells grown by MBE', 71-77, Copyright 2016, with permission from Elsevier.

higher order fractions (e.g. up to  $\nu = 11/21$  at T = 0.3 K) is an indication of not only high mobility but also of high 2DEG density uniformity and proper screening of residual potential fluctuations caused by the remote ionized donors.

# 2. LOW NOISE SI DOPED GAAS/ALGAAS HETEROSTRUCTURES FOR SPIN QUBIT

## 2.1 Introduction

Laterally gated semiconductor quantum dots are essential components for mesoscopic physics and are used to realize solid state qubit for quantum information processing. The term "qubit" represents the quantum analog of the classical bit (which refers to a basic unit of information with two states represented as 0 and 1, and is independent of the physical medium used to convey this binary information). For example, the spin state of an electron in a quantum dot is an ideal physical system for storing and processing quantum information [56,57]. Despite the conceptual similarities between qubits and classical bits, they differ in their practical use. As with classical bits, qubits convey information through binary states (typically these are the same states used by bits: 0 and 1). However, whereas the state of a bit may be either 0 or 1, a qubit may also occupy a superpositional state (simultaneously both 0 and 1) [58].

When a qubit is initialized in a superposition of two states and allowed to evolve, it precesses with a frequency proportional to the energy difference between the two states. Qubits are extremely sensitive to fluctuations in their local environment. When they interact with noisy environments, they experience decoherence. This leads to qubit oscillations decay, which limits the time scale in which qubits can be used for quantum information processing.

Two main sources of noise in semiconductors exist: charge noise and spin noise. Charge noise arises from occupation fluctuation of impurity trap centers (trapping and de-trapping of charge states) in the vicinity of qubits and results in the fluctuation of local electric fields. Due to spin-orbit interaction, charge noise can potentially cause qubit spin dephasing. Spin noise can arise from fluctuations in the nuclear spins of the host material which is dominant in GaAs/AlGaAs heterostructures. Spin noise results in magnetic field fluctuation experienced by electron spin through hyperfine interaction. In general, charge noise results in large noise powers but only at low frequencies and the spin noise gives much weaker noise powers but over a much wider bandwidth [59].

This chapter investigates methods for minimizing charge fluctuation to produce reliably tunable and quiet platform for laterally gated nanodevices such as quantum point contacts (QPC) and quantum dots (QD). The chapter does not investigate phenomena related to spin noise. Because charge noises are dominant at low frequency regimes, the next section reviews low frequency noise studies for GaAs devices and describes various techniques which have been developed to reduce low frequency noise. The total number of silicon donors has been identified as an important parameter influencing low-frequency charge noise in modulation-doped GaAsAl<sub>x</sub>Ga<sub>1x</sub>As heterostructures. By reducing the total number of Si donors, quantum devices with minimal charge noise achieved that can serve as a robust, stable platform for spin qubit-based quantum computing.

## 2.2 Low frequency noise in GaAs nanodevices

Molecular beam epitaxy (MBE) growth is a technique for growing extremely pure GaAs/AlGaAs with minimal defects. However, the residual defects become more important as the dimensions of devices such as QPCs and QDs become smaller in nanometer scale. These residual defects may act as trap centers which randomly capture and emit charge carriers. This results in low frequency noise (such as burst and 1/f noise) and degradation of device performance at nanometer scale.

Li et al. provide the first experimental study on the noise characteristics of QPCs [60] at T=4.2K. The authors investigate low frequency noise in frequency span 100Hz<f<100kHz generated by electron transport through ballistic constriction. Ex-

perimental results shown in Fig. 2.1 demonstrate a linear increase in white noise with bias current, though lower than expected for full shot noise. Lesovik calculates

Fig. 2.1. R vs V<sub>g</sub> and A<sub>0</sub> vs V<sub>g</sub>. A<sub>0</sub> is obtained by fitting  $S_I = A_0 I^2/f$ + S<sub>0</sub> for I = 0.4, 0.5, and 0.6  $\mu$ A. The approximate plateaus in R are assigned to the quantized resistances  $h/2e^2N$ , with N = 2,3,4, and 5. Inset shows the device geometry. Reprinted from Yuan P. Li et al.,'Low-frequency noise in transport through quantum point contacts', Appl. Phys. Lett. 57, 774 (1990), with the permission of AIP Publishing.

excess noise in quantum point contact theoretically [61]. The author predicts the suppression of shot noise in ballistic transport regimes in the center of conductance plateaus and demonstrates that the noise power measured in a 1D constriction with adiabatically tapered contacts is

$$S(\omega = 0) = (2e^2/h)V \sum_{j,k=1}^{N} t_{jk}(1 - t_{jk})$$

(2.1)

where V denotes applied voltage. Therefore, shot noise vanishes on conductance plateau because  $t_{jk} = \delta_{jk}$  (i.e., there is no scattering). If a defect in the constriction backscatters or reflects an electron from the constriction, the transmission probability  $t_{jk}$  becomes less than unity. Thus, the conductance is reduced from the quantized value and noise can be observed.

In addition to shot noise, Li also reports on 1/f noise with an intensity that demonstrates minima whenever the conductance is set at a quantized conductance plateau. However, the origin of 1/f dependence of noise power and of minima in its intensity remained unclear. Subsequent work on QPC noise shows Lorentzian spectrum with  $1/f^2$  frequency dependence [62–66]. The origin of Lorentzian noise spectral density is observed from measurements in the time domain in which the QPC resistance fluctuates randomly between two (or more) discrete values, spending on average time  $\tau_d$  in low-resistive state and time  $\tau_u$  in high-resistive state. In this twostate fluctuating case namely Random Telegraph Noise (RTN), the noise spectrum is given by [67]:

$$\frac{S_V(f)}{V^2} = \left(\frac{\Delta V}{V}\right)^2 \frac{4}{(\tau_u + \tau_d)} \frac{\tau_{eff}^2}{(1 + 4\pi^2 f^2 \tau_{eff}^2)}$$

(2.2)

with  $1/\tau_{eff} = 1/\tau_u + 1/\tau_d$  and  $\Delta V$  denotes the switching amplitude.

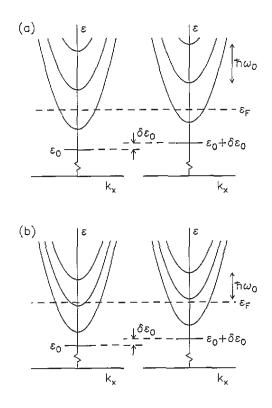

As with 1/f noise, intensity of RTN shows minima when conductance is set at a quantized conductance plateau. This aspect of the noise is universal. Reference [68] provides the explanation that the transmission of the 1D subband closest to its population threshold is more sensitive to changes in the local electrostatic potential. These potential changes are due to the fluctuation in occupancy of electron traps located at or near the point contact. The authors model the fluctuations at finite temperature via fluctuations in the effective number of transmitted channels (or equivalently in  $\epsilon_F - \epsilon_0$ ). Lateral confining potential in the point contact is approximated by a parabola of strength  $\hbar\omega_0$  and  $\epsilon_n = \epsilon_0 + (n - \frac{1}{2})\hbar\omega_0$ . Calculations below are based on assumptions of linear dependence of  $\epsilon_0$  and  $\hbar\omega_0$  with gate voltage  $V_g$ . Random changes in occupancy of trapping sites near QPC result in fluctuation of Coulomb

potential, the potential energy  $\epsilon_0$  in the point contact with noise spectral density  $S_{\epsilon_0}$ . The relationship between  $S_V/V^2$  and  $S_{\epsilon_0}$  is given to first order by

$$\frac{S_V}{V^2} = \frac{S_G}{G^2} = \frac{1}{G^2} \left(\frac{\partial G}{\partial \epsilon_0}\right)^2 S_{\epsilon_0}$$

(2.3)

$$\frac{\partial G}{\partial \epsilon_0} = \frac{2e^2}{h} \frac{1}{k_B T} \sum_n f(\epsilon_n - \epsilon_F) [1 - f(\epsilon_n - \epsilon_F)]$$

(2.4)

with  $f(\epsilon)$  the Fermi-Dirac distribution at temperature T. Both G and  $\partial G/\partial \epsilon_0$  are evaluated for the time-averaged value of  $\epsilon_n$ . The frequency dependence of  $S_V/V^2$  is contained in  $S_{\epsilon_0}$ , while the G dependence of  $S_V/V^2$  is contained in the  $(\partial G/\partial \epsilon_F)^2/G^2$ term.