## HARDWARE IMPLEMENTATION OF AUTONOMOUS

## PROBABILISTIC COMPUTERS

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Ahmed Zeeshan Pervaiz

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2019

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Supriyo Datta, Chair

School of Electrical and Computer Engineering

Dr. Joerg Appenzeller

School of Electrical and Computer Engineering

Dr. Zhihong Chen

School of Electrical and Computer Engineering

Dr. Sunil A. Bhave

School of Electrical and Computer Engineering

### Approved by:

Dr. Dimitrios Peroulis

Head of Electrical and Computer Engineering

To my parents

#### ACKNOWLEDGMENTS

The first time I met Professor Datta was in his class "Fundamental of nanoelectronics". I still remember walking out amazed, as to how little I knew about Ohms law. It would be the first of great many times, to be amazed by his approach to science. Professor Datta taught me how to learn, how to do things others would find worth learning. Under his tutelage I have grown immensely both as a researcher and as a person. It has been a privilege to have had this opportunity.

This journey would not have been possible without the love and affection of my parents. My father, a sailor whose only voyage in life has been to help find happier shores for his children and my mother whose only happiness is to have her children in front of her. They have both been so incredibly patient with me. Whatever good in me comes from them and this life and all its joys would not have been possible without them.

I have been blessed with incredible friends and colleagues at Purdue. A very special thanks to Kerem Yunus Camsari for his kindness and patience. The countless hours of his time helped sculpt a great many ideas that have shaped this thesis and even greater many perspectives that have molded me as an individual. For that I am truly indebted to him. I would like to thank Brian Sutton for being both a friend and teacher and Lakshmi Anirudh Ghantasala for helping me with my work. The long evenings spent in the lab with Shehrin Sayed motivated me to do more. The wit of Orchi Hassan and Rafatul Faria brought me joy a great many times. I would also like to thank Shuvro Chowdhury, Jan Kaiser, Samiran Ganguly and Professor Ernesto E. Marinero for many thoughtful and engaging conversations. A significant part of this thesis is in collaboration with William A. Borders, Professor Shunsuke Fukami and Professor Hideo Ohno from Tohoku university. I would like to thank them for the opportunity to collaborate with them. It has been a pleasure working with such experts.

Lastly, I would like to thank my wife, my rock, Rehma. Her love and affection are the fuse that drive me forward, and her support has given me a new lease on life itself.

## TABLE OF CONTENTS

|    |      |                 |                                                       | Page  |

|----|------|-----------------|-------------------------------------------------------|-------|

| LI | ST O | F TAB           | LES                                                   | . ix  |

| LI | ST O | F FIGU          | JRES                                                  | . x   |

| AI | BSTR | ACT             |                                                       | . xix |

| 1  | INT  | RODU            | CTION                                                 | . 1   |

|    | 1.1  | Proba           | bilistic computing                                    | . 1   |

|    | 1.2  | Organ           | ization of Thesis                                     | . 5   |

|    | 1.3  | Public          | eations associated with Thesis                        | . 6   |

| 2  |      | RDWAF<br>E LOGI | RE EMULATION OF STOCHASTIC P-BITS FOR INVERT-<br>IC   | . 8   |

|    | 2.1  | Introd          | uction                                                | . 8   |

|    | 2.2  | Metho           | ds                                                    | . 9   |

|    |      | 2.2.1           | Arduino pro mini as a p-bit                           | . 9   |

|    |      | 2.2.2           | Synapse using a microcontroller and DAC               | . 12  |

|    | 2.3  | Result          | S                                                     | . 13  |

|    |      | 2.3.1           | AND Gate as a Boltzmann Machine                       | . 13  |

|    |      | 2.3.2           | Interconnect delay and retention time                 | . 15  |

|    |      | 2.3.3           | Full Adder as a Boltzmann Machine                     | . 17  |

|    |      | 2.3.4           | Directed Networks of p-circuits                       | . 18  |

| 3  |      |                 | FACTORIZATION USING STOCHASTIC MAGNETIC TUN-<br>TIONS | . 30  |

|    | 3.1  | Introd          | uction                                                | . 30  |

|    | 3.2  | Metho           | ds                                                    | . 38  |

|    |      | 3.2.1           | MTJ fabrication                                       | . 38  |

|    |      | 3.2.2           | MTJ characterization                                  | . 40  |

vii

|   |     | 3.2.3   | p-bit construction                                                                               | 40 |

|---|-----|---------|--------------------------------------------------------------------------------------------------|----|

|   |     | 3.2.4   | p-circuit construction                                                                           | 42 |

|   |     | 3.2.5   | Factorization algorithm                                                                          | 43 |

|   |     | 3.2.6   | Factorization experiment calibration                                                             | 46 |

|   |     | 3.2.7   | Comparison between MTJ-based p-bit and CMOS-based alter-<br>natives                              | 47 |

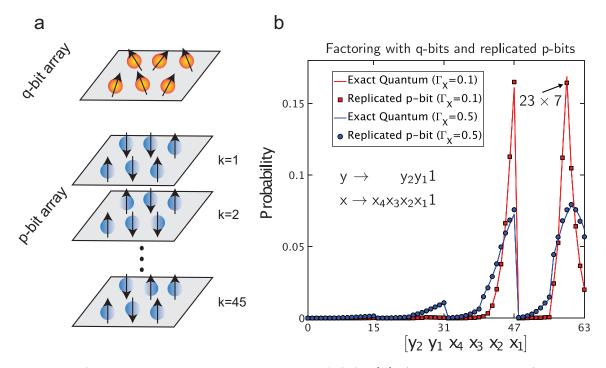

|   |     | 3.2.8   | Comparison between p-bit and quantum computing                                                   | 49 |

|   |     | 3.2.9   | Experiment versus simulation                                                                     | 53 |

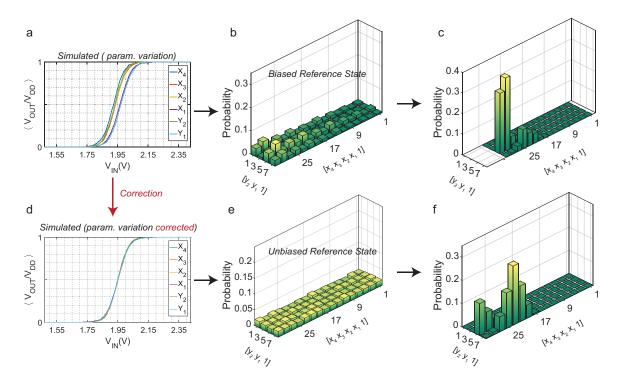

|   |     | 3.2.10  | Effect of p-bit parameter variation on system performance 5                                      | 54 |

|   |     | 3.2.11  | p-bit-based implementation of invertible AND gate                                                | 57 |

| 4 |     |         | RE EMULATION OF STOCHASTIC P-BITS FOR INVERT-CC                                                  | 61 |

|   | 4.1 | Introd  | uction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                   | 31 |

|   | 4.2 | Stocha  | stic MRAM based p-bit and its emulation $\theta$                                                 | 52 |

|   | 4.3 | Optim   | ization using Probabilistic computers                                                            | 35 |

|   | 4.4 | Integer | r Factorization $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 38 |

| 5 |     |         | D P-BITS FOR FPGA IMPLEMENTATION OF PROBABILIS-<br>IITS                                          | 72 |

|   | 5.1 | Introd  | uction $\ldots$ | 72 |

|   | 5.2 | Weight  | ted p-bit                                                                                        | 73 |

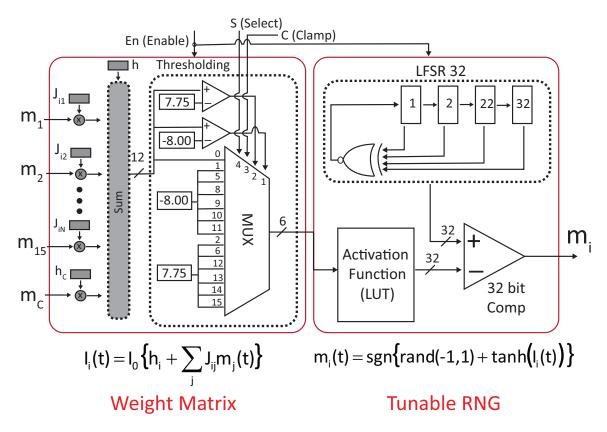

|   |     | 5.2.1   | Weight Matrix                                                                                    | 73 |

|   |     | 5.2.2   | Tunable random number generator                                                                  | 75 |

|   |     | 5.2.3   | System Tile                                                                                      | 77 |

|   |     | 5.2.4   | FPGA                                                                                             | 31 |

|   | 5.3 | Result  | s ε                                                                                              | 33 |

|   |     | 5.3.1   | AND Gate                                                                                         | 83 |

|   |     | 5.3.2   | Full Adder                                                                                       | 86 |

|   |     | 5.3.3   | N-bit Ripple Carry Adders                                                                        | 38 |

|   |     | 5.3.4   | Subset Sum Problem                                                                               | 90 |

## Page

viii

| 6  | CON  | ICLUSION                                                          | 4 |

|----|------|-------------------------------------------------------------------|---|

|    | 6.1  | Summary                                                           | 4 |

|    | 6.2  | Future Work                                                       | 7 |

| Rł | EFER | ENCES                                                             | 8 |

| А  | EXP  | PERIMENTAL DATA 10                                                | 3 |

|    | A.1  | Experimental data for s-MTJ based p-computer and its emulation 10 | 3 |

|    | A.2  | Arduino Sketches for synapse                                      | 3 |

## LIST OF TABLES

| Tabl | e                                                                      | P٤ | age |

|------|------------------------------------------------------------------------|----|-----|

| 5.1  | Truth Table for the weight matrix multiplexer                          |    | 76  |

| 5.2  | FPGA resource utilization of the p-circuits that have been implemented |    |     |

|      | in this paper                                                          | •  | 82  |

#### LIST OF FIGURES

#### Figure

$\mathbf{2}$

4

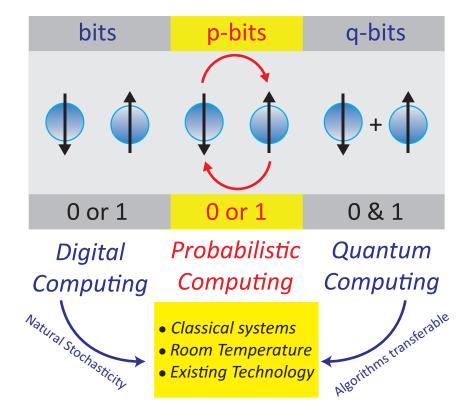

- 1.1 **Probabilistic computing.** Digital computing relies on stable deterministic units called "bits" which are either '0' or '1' at any given point in time. On the other end of the spectrum lies q-bits; quantum entities which are in a delicate super-position state of '0' and '1'. In this thesis we experimentally demonstrate probabilistic bits or "p-bits" that are robust, classical entities fluctuating between '0' and '1'. These p-bits can be used as natural hardware for many classical algorithms that introduce stochasticity using aritifical means, while a subset of problem reserved for quantum computing can also be mapped to networks of p-bits. . . . . .

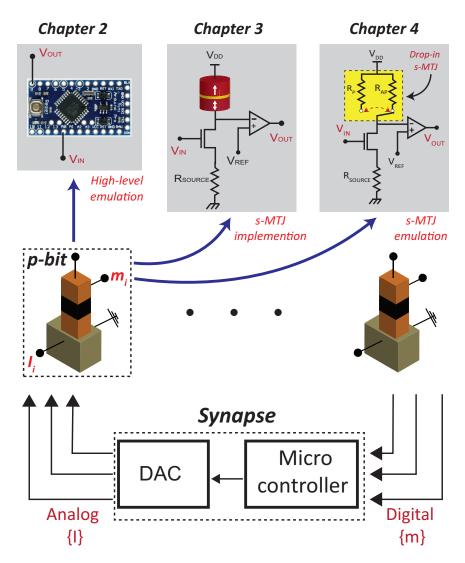

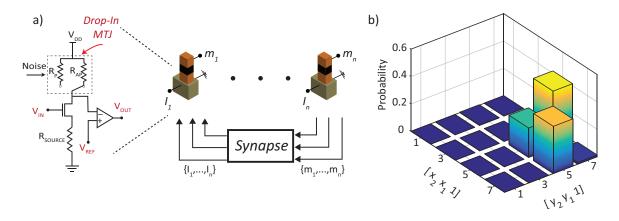

- 1.2 **Thesis Overview.** In this thesis we present an autonomous probabilistic computer which uses clock-less p-bits interconnected using a synapse as shown in the figure above. To achieve this, we first used a high-level emulation of p-bits using micro-controllers which helped establish important rules of operations for such systems. This was then followed by the "very first" experimental demonstration of a thermally unstable stochastic Magnetic Tunnel Junction (s-MTJ) based autonomous probabilistic computer. While we work towards scaling the s-MTJ based p-computer, we have built a low-level emulation of p-computers which will assist in further studying the role of device variations and new application spaces for probabilistic computers.

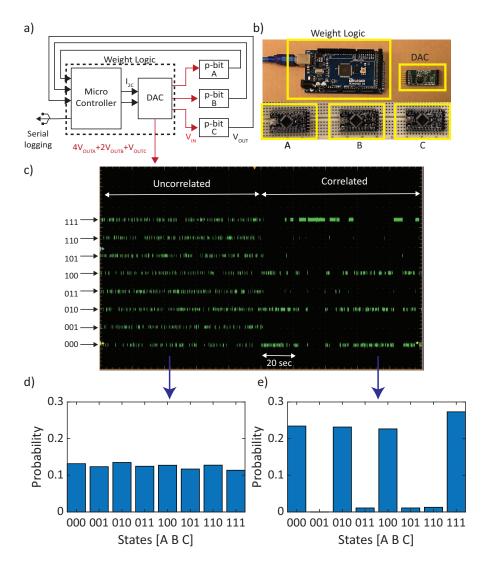

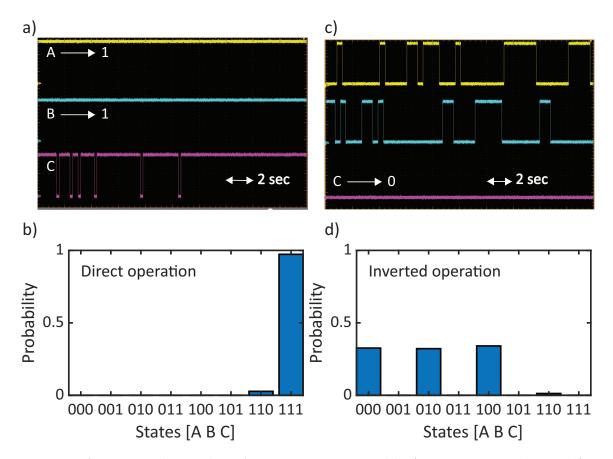

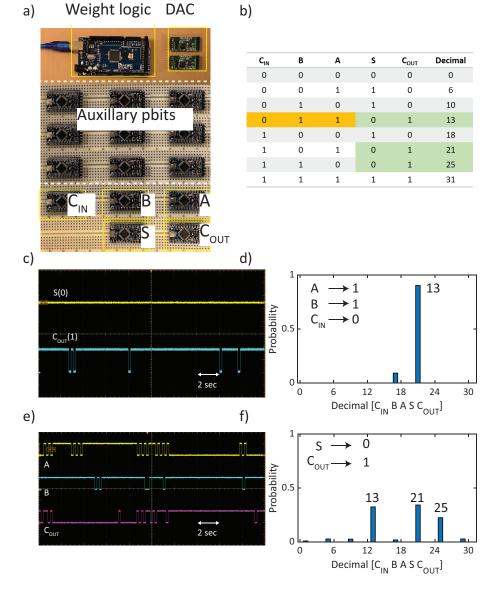

- 2.2 AND gate emulated using 3 p-bits. (a) and (b) show the block diagram and the schematic of the emulated AND gate. Each terminal of the AND gate is one p-bit. These p-bits are interconnected using a weight logic block which comprises of an Arduino Mega microcontroller and a digital-to-analog converter. The microcontroller reads the digital output voltages  $\{V_{OUT}\}$  of p-bits and provides the analog inputs  $\{V_{IN}\}$ . The weight logic is also used to observe the state of the AND gate by constructing an artifical signal  $4 \times A + 2 \times B + C$  shown in (c). The AND gate is initially left uncorrelated which results in  $2^3 = 8$  states uniformly distributed as shown with the statistics in (d). When the correlations are turned on (using an  $I_0 = 0.8$ ), the truth table of the AND gate is highlighted as shown in (e).

Page

22

| Figu | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

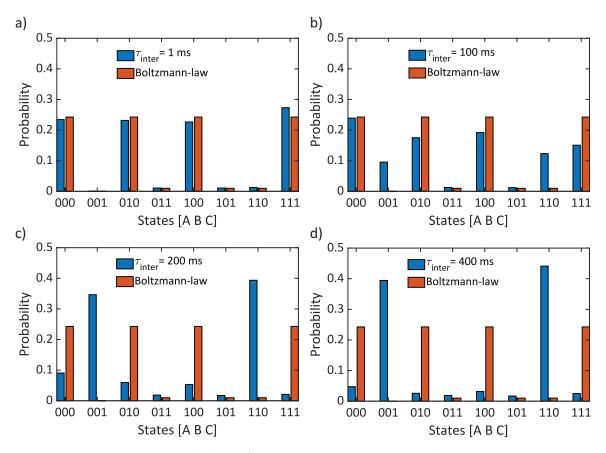

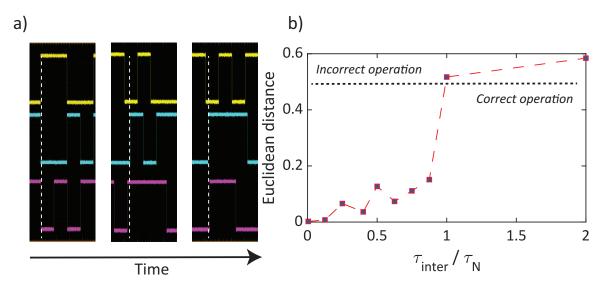

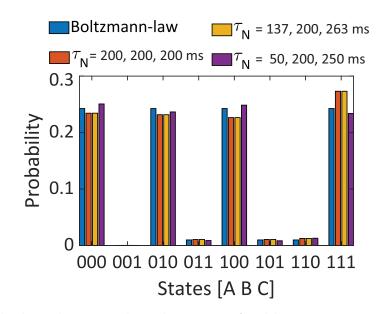

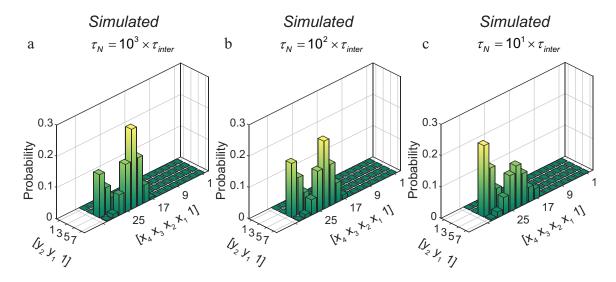

| 2.6  | Variations in retention times $\tau_N$ of p-bits. Variations in the retention time $\tau_N$ of the p-bits is expected in nano-device level implementations. These are investigated here by varying the retention times of p-bits across a wide distribution while keeping the interconnect delay significantly low, i.e $\tau_{inter} \tau_N \ll 1$ . As long as the interconnect delay is greater than the smallest retention time, the system will operate correctly.                                                                                                                  |  |  |

| 2.7  | Full Adder. 14 p-bits are used to implement a full adder shown in (a). 5 of these are the terminals of the full adder (truth table shown in (b)) while the remaining 9 are auxiliary p-bits. The full adder works both in the direct $((c)-(d))$ and inverted $((e)-(f))$ mode of operation similar to the AND gate.                                                                                                                                                                                                                                                                     |  |  |

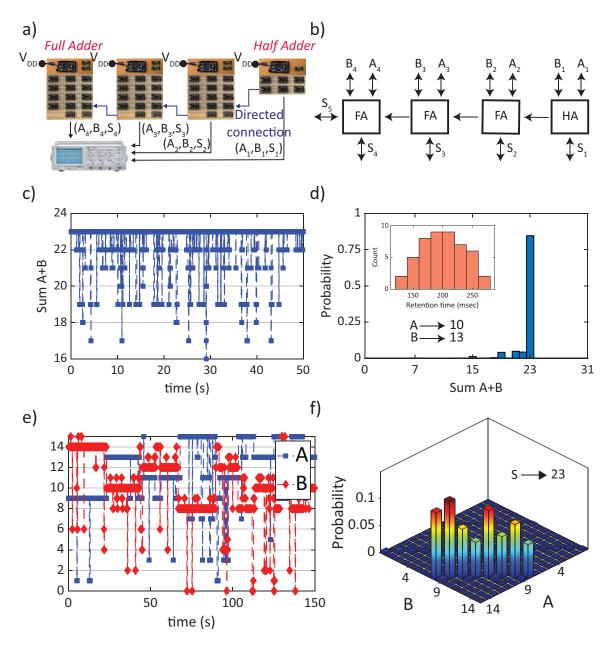

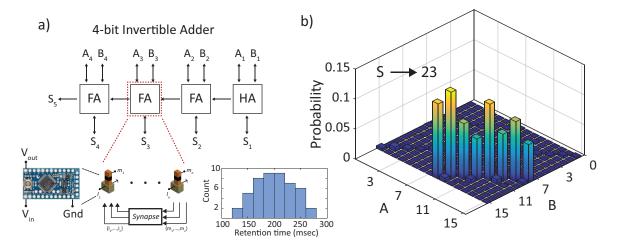

| 2.8  | 4-bit Ripple Carry Adder (RCA). A 4-bit adder is implemented using 4 autonomous p-circuits using a total of 48 p-bits (3 full adders and one half adder) shown in the schematic in (a) and block diagram in (b). Each of the 48 p-bits is given a slightly different retention time $\tau_N$ (inset of (d)). (c-d) shows the 4-bit adder working in the standard direct mode of operation where it adds two numbers. However, (e-f) shows the inverted mode in which the output S is clamped to 23. The inputs A and B fluctuate between all 8 combinations consistent with a sum of 23. |  |  |

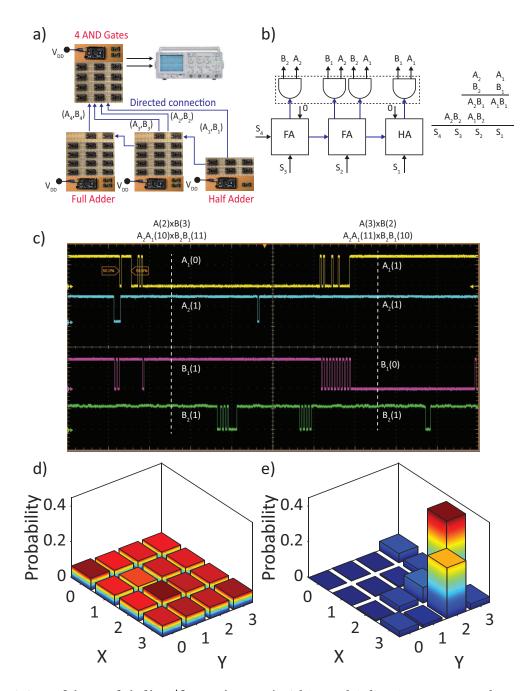

| 2.9  | <b>4-bit multiplier/factorizer.</b> A 4-bit multiplier is constructed out of 3 Full Adders and 4 AND gates. The schematic and a block diagram are shown in (a) and (b). The multiplier works in the inverted mode operates as a factorizer. When the multiplier is left in the uncorrelated state the system fluctuates between the $2^4$ states. When a product of 6 is clamped the multiplier now fluctuates between the only two combinations $(2 \times 3 = 3 \times 2)$ consistent with a product of 6                                                                              |  |  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

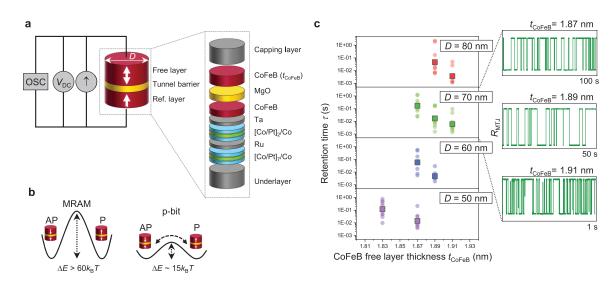

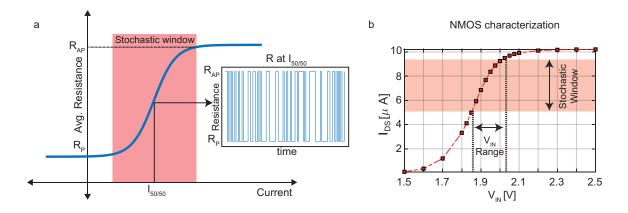

- Characteristics of stochastic magnetic tunnel junctions. (a) Mea-3.1surement setup of a stochastic MTJ, with a stack structure that is only slightly modified from current MRAM technology. A current is passed from the free layer to the reference layer, a time-averaged signal is read on the voltmeter, and a time-domain signal is measured on the oscilloscope. (b) The energy profile between the P and AP states of the magnetization orientation of the MTJ for typical MRAM technology and for the MTJs used in the p-bits for this work. (c) Experimental results showing the retention time  $\tau$  of MTJs with varying thickness of the CoFeB free layer  $t_{CoFeB}$  and diameter D. The retention time  $\tau$  is determined at an applied current of  $I_{50/50}$ , which induces equal fluctuation time of the MTJ magnetization in the AP and P states. Square symbols represent the average of the retention time for 10 MTJs at each D and  $t_{CoFeB}$ . Transparent circles represent the retention time for each device. The right-most panels show the effect of varying the free-layer thickness on the stochasticity for devices of the same size. Note that reducing the thickness below 1.8nm results in a stable binary device suitable for nonvolatile memory applications [25]. The MTJs were prepared at Tohoku University by William A. Borders, Professor Shunsuke Fukami and Professor Hideo Ohno.

Page

33

35

| Figu | lre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

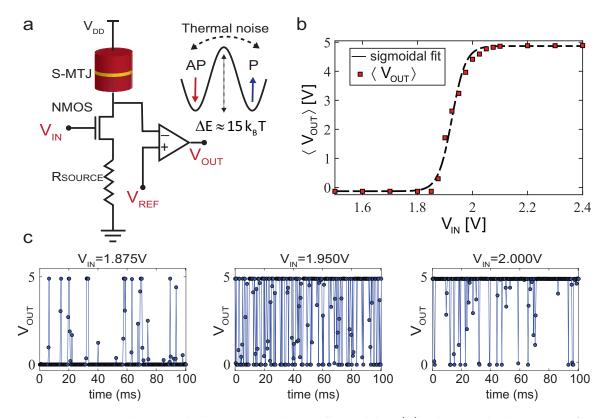

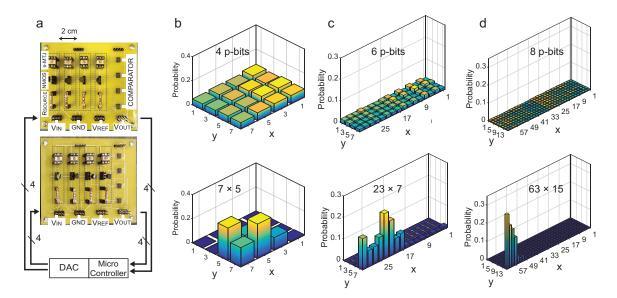

| 3.3  | <b>Experimental demonstration of integer factorization.</b> (a) A photograph of a printed circuit board for an eight-p-bit circuit, interconnected through a microcontroller and a DAC. (b-d), The uncorrelated (top) and correlated (bottom) state of the system when four, six and eight p-bits are used to factorize $35 = 5 \times 7 = 7 \times 5(P = 2, Q = 2 \text{ with four p-bits})$ (b) $161 = 23 \times 7(P = 4, Q = 2 \text{ with six p-bits})$ (c) and $945 = 63 \times 15(P = 5, Q = 3 \text{ with eight p-bits})$ (d). The x and y axes show the factors X and Y (see Methods section Factorization algorithm). All statistics are taken over a window of 15 s with over 2,000 sampling points. Each separate factorization experiment was performed more than twice to ensure reproducibility. | . 39 |

| 3.4  | <b>p-bit construction.</b> (a) A diagram of the ideal response of a stochastic MTJ as used in this work and the parameters used to characterize the MTJ. (b) The measured drain current $I_{DS}$ as a function of $V_{IN}$ of a 2N7000 NMOS transistor used in our p-bit demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 42 |

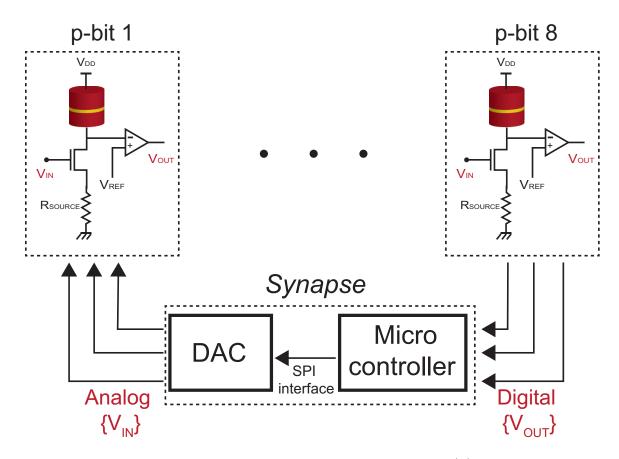

| 3.5  | Block diagram of an asynchronous p-circuit. (a) A microcontroller reads the outputs voltages $V_{OUT}$ of all p-bits and computes the synaptic weights, which are then converted to the analogue input voltages $V_{IN}$ for each p-bit, using a DAC that communicates with the microcontroller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 43 |

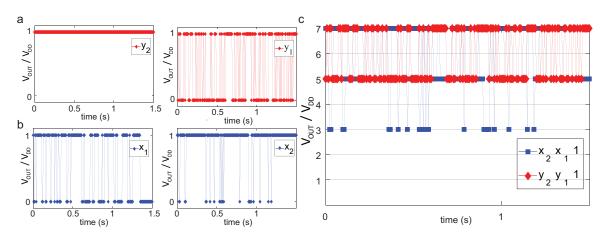

| 3.6  | <b>Experimentally observed time snapshots.</b> (a-c), Experimentally observed time snapshots of the four p-bits used to factorize 35 (a,b). These snapshots are combined to create $x$ and $y$ (c), which fluctuate between $7 \times 5$ and $5 \times 7$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 45 |

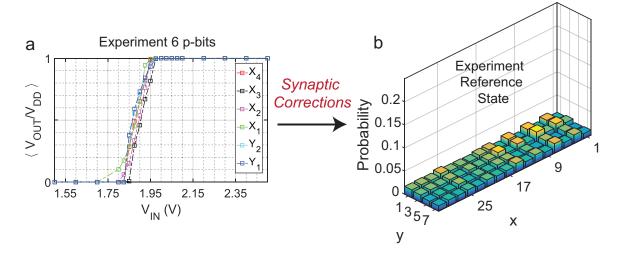

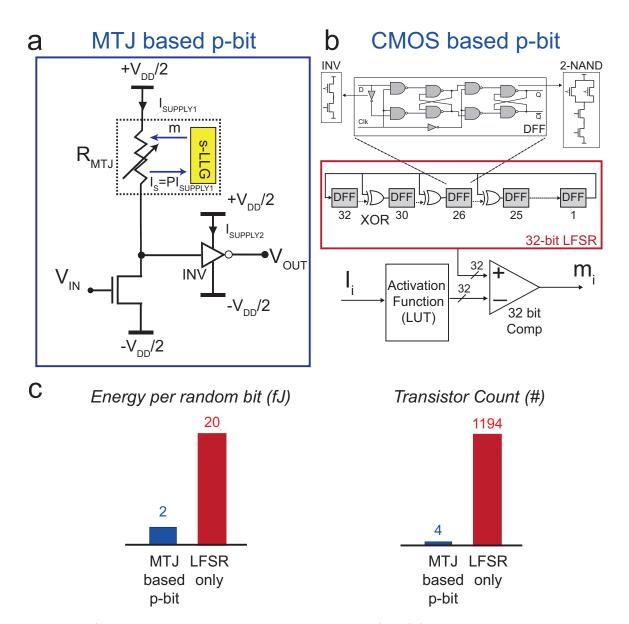

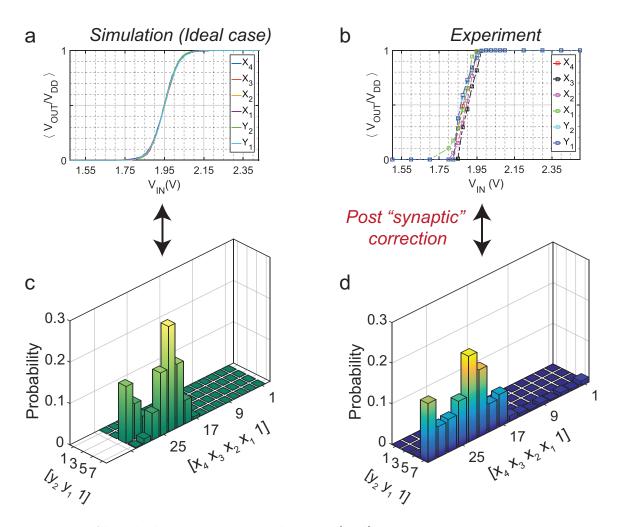

| 3.7  | Calibrating the experimental system. (a) Calibrating a reference state using synaptic weights. (a) The experimentally observed time-averaged output of six p-bits versus applied inputs (which are misaligned).(I) The output is corrected using synaptic biases leading to the reference state shown. Each data point in a and b are taken as an average over a time window of 15 s with 2,000 or more sampling points                                                                                                                                                                                                                                                                                                                                                                                        | ,    |

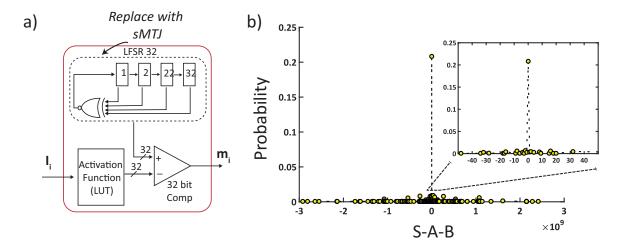

| 3.8  | Comparison between the MTJ- and CMOS-based energy per<br>random bit and cell area. (a) An MTJ-based p-bit simulated with<br>the stochastic LLG model (s-LLG, dotted box). (b) A 32-bit LFSR. The<br>look-up table (LUT) and the digital comparator of the CMOS p-bit are<br>not included in the comparison. INV, inverter; DFF, D-type flip flop                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 50 |

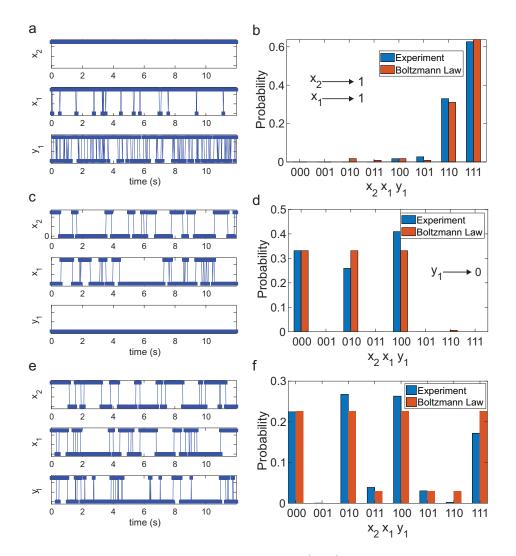

- 3.13 Invertible AND gate operation. (a-b) Time snapshot for the direct mode of operation when the inputs  $x_2$  and  $x_1$  have both been pinned to 1 (a); the statistics collected for 60 s (b). (c-d) Time snapshot for the p-bits operating the AND gate in inverted mode when the output  $y_1$  is pinned to 0 (c); the statistics collected for 60 s (d). (e-f) Time snapshot for the p-bits operating the AND gate in floating mode (e); the statistics collected for 60 s (f). All statistics shown are collected over a time window of 60 s with 2,000 or more sampling points. . . . . . . . . . . . . . . . . 60

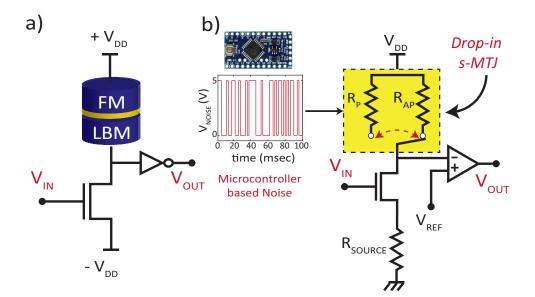

- 4.1 Emulating MRAM p-bit. (b) shows a mapping from the MRAM based design to its emulation. An analog multiplexer emulates a stochastic MTJ fluctuating between  $R_P$  and  $R_{AP}$ , where the statistics of the fluctuation is controlled by a noise signal which is generated using a microcontroller. . . 62

Page

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                         | Ра | age |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

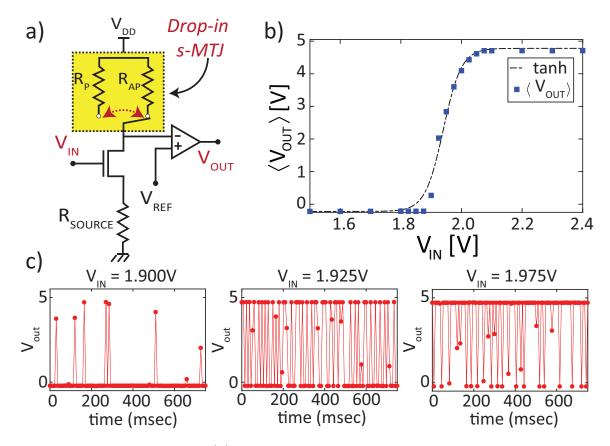

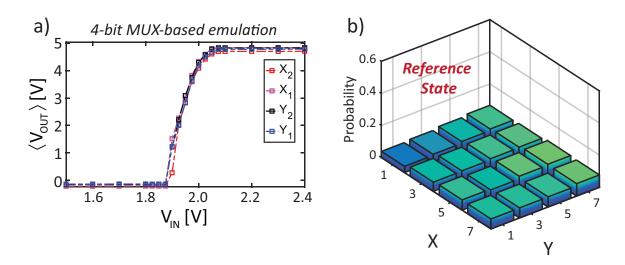

| 4.2  | <b>Emulated p-bit.</b> (a) Electrical schematic of a emulated p-bit which uses<br>a multiplexer, NMOS and a comparator. The multiplexer emulates a low<br>barrier magnet having a retention time $\tau = 50ms$ . (b) shows the average<br>output as a function of applied input with each point being a 15 second<br>average. (c) shows time snapshots for three sets of applied input voltages                            |    | 63  |

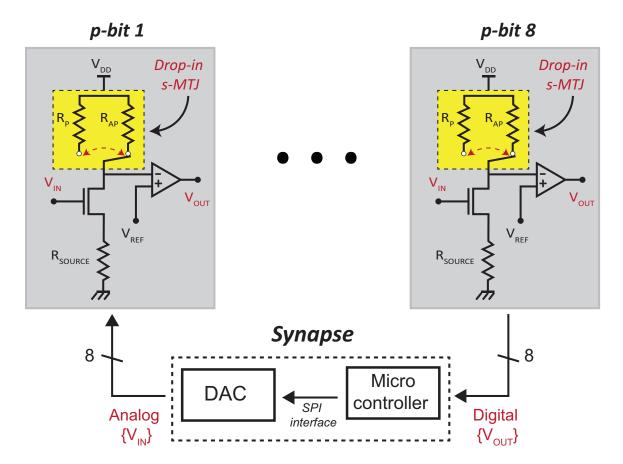

| 4.3  | Architecture of p-computers. A system level schematic for a p-circuit is shown. A microcontroller reads the output voltages of all p-bits, calculates the inputs corresponding to Eq. 4.1 and uses a DAC to set analog input voltages to the p-bits.                                                                                                                                                                       |    | 64  |

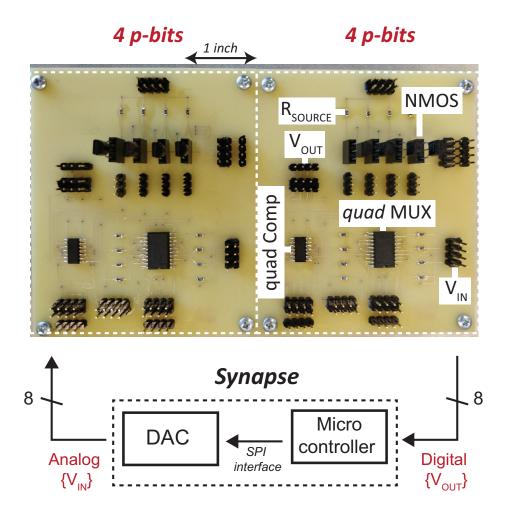

| 4.4  | <b>Photograph of p-circuit.</b> A photograph of a printed circuit board is shown that houses 4 emulated p-bits. We use two boards each housing 4 p-bits to put together an 8-bit p-computer                                                                                                                                                                                                                                |    | 65  |

| 4.5  | <b>Reference state calibration. (a)</b> shows the time average response of four p-bits which are slightly misaligned. These misalignments are corrected by adding a constant synaptic bias to each p-bit individually leading to a reference state shown in <b>(b)</b> where all p-bits are left uncorrelated.                                                                                                             |    | 66  |

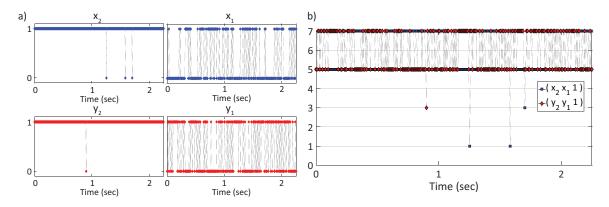

| 4.6  | Time snapshot for factorizing 35. (a) shows individual time snapshots of 4 p-bits that are fluctuating when the synapse is programmed to factorize 35. (b) shows the time snapshots of both factors $X$ and $Y$ while the synapse is programmed to factorize 35. The system spends most of its time in two states; $7 \times 5$ and $5 \times 7$ .                                                                         |    | 66  |

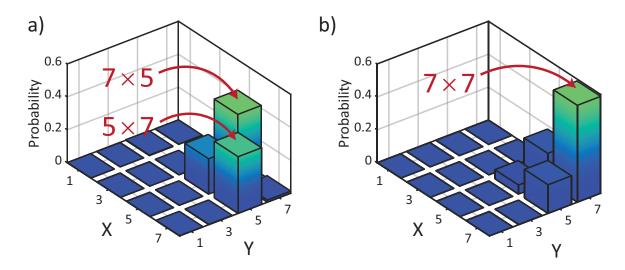

| 4.7  | Statistics for factorizing 35 and 49. (a) shows the statistics of the system when the synapse is programmed to factorize 35. In this case the two peaks corresponding to the correct factors $7 \times 5$ and $5 \times 7$ are highlighted by the system. (b) shows the statistics for the case when the system is programmed to find factors of 49. In this case only the state $7 \times 7$ is highlighted by the system |    | 67  |

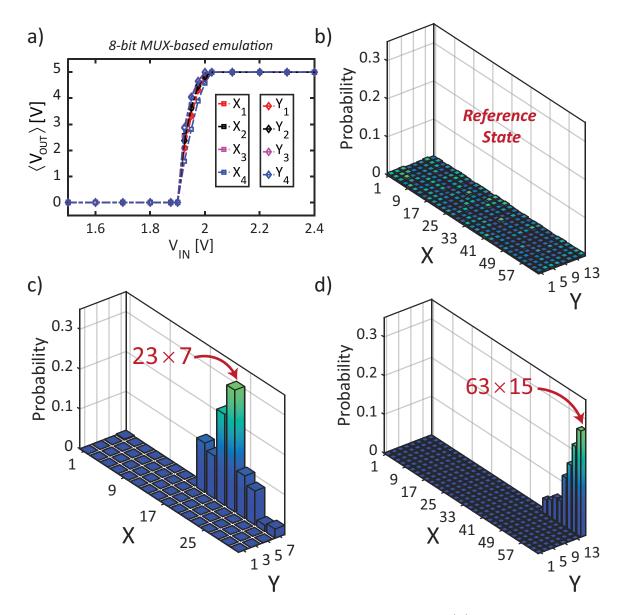

| 4.8  | Factorizing 161 and 945 with 6 and 8 p-bits. (a) shows the average response for 8 p-bits which are corrected by adding synaptic biases to produce an 8-bit reference state as shown in (b). The synapse is then programmed to factorize $161 = 23 \times 7$ and $945 = 63 \times 15$ as shown by the statistics in (c-d).                                                                                                  |    | 71  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.1  | Weighted p-bit. A weighted p-bit consists of two major subblocks, a <i>Weight Matrix</i> and a <i>Tunable RNG</i> implementing Eq. 1.2 and Eq. 1.1 as a composite unit. The weight matrix implements one column of Eq. 1.2 and adds overflow protection and clamping capabilities to the weighted p-bit while the tunable RNG subblock implements Eq. 1.1 whose terminal characteristics are further shown in Fig. 5.2. See text for a detailed description.                                             | . 75 |

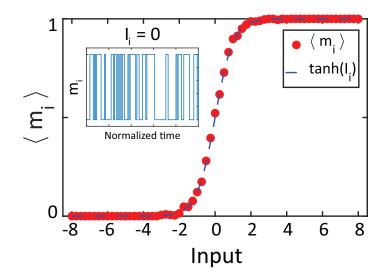

| 5.2  | <b>Sigmoid.</b> The time-averaged output $(m_i)$ of a weighted p-bit is shown as<br>a function of the applied input I <sub>i</sub> . When the I <sub>i</sub> = 0 (inset), the output m <sub>i</sub><br>shows equal amounts of 1's and 0's with a long-time average of 0.5. As<br>I <sub>i</sub> is increased above (below) 0, the average increases and saturates to 1<br>(-1). Here, the binary output of the FPGA $m_i \in \{0, 1\}$ is converted to a<br>bipolar $m_i \in \{-1, +1\}$ representation. | . 78 |

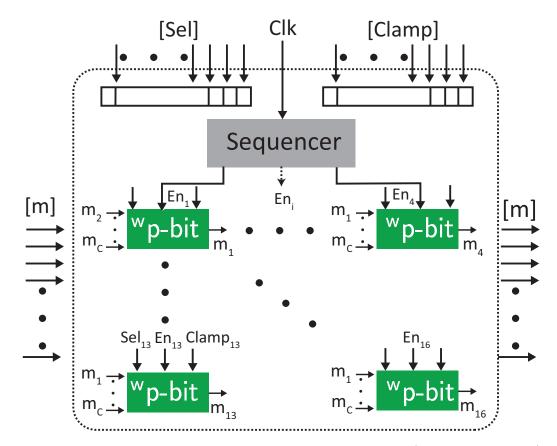

| 5.3  | 4 x 4 system tile. A 4 × 4 block of weighted p-bits (denoted by "p-bit) can be used to implement [J] matrices with a dimension of $4^2 \times 4^2$ and the sequencer block allows each of the 16 p-bits to be updated sequentially for proper system operation. Different problems can be mapped through a choice of suitable [J] and {h} matrices to construct larger p-circuits                                                                                                                        | . 80 |

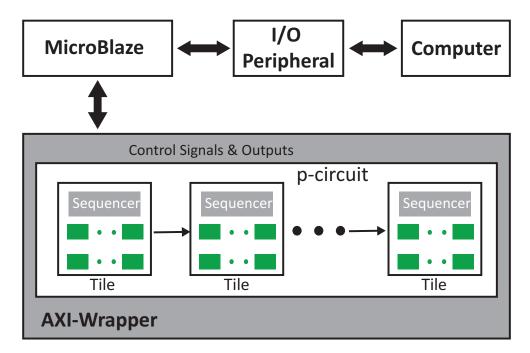

| 5.4  | I/O Architecture for FPGA. We communicate with the input and output terminals of weighted p-bits using an I/O architecture whose block diagram is shown above. Any p-circuit (tile or collection of tiles) can be converted into an AXI (universal serial bus architecture) peripheral, which can then communicate with a computer via a MicroBlaze processor that allows the collection of data from p-circuits.                                                                                        | . 82 |

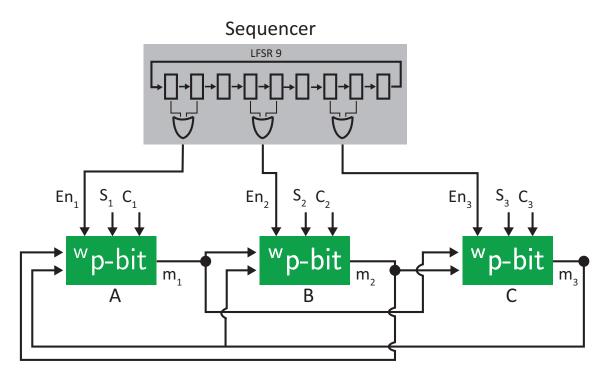

| 5.5  | <b>AND Gate.</b> Three weighted p-bits are needed to implement an AND gate whose [J] matrix is obtained from Ref. [12]. A sequencer circuit is used to force an updating sequence of $(A \rightarrow B \rightarrow C)$                                                                                                                                                                                                                                                                                   | . 83 |

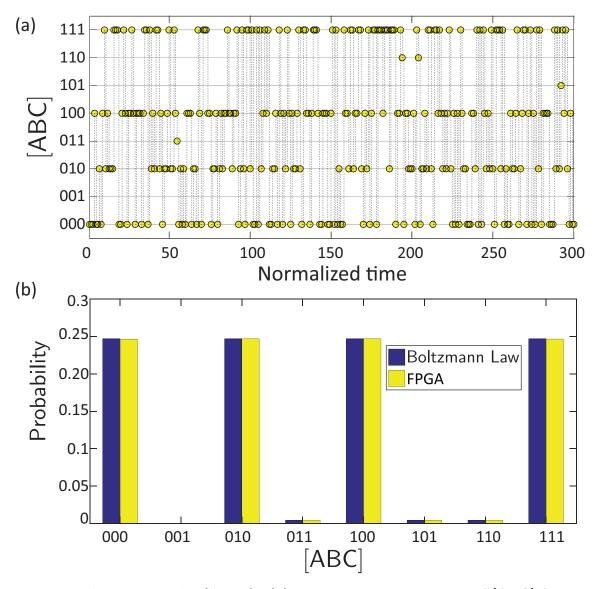

| 5.6  | <b>Floating mode (AND). (a)</b> Time dependent outputs of [ABC] for the AND gate are shown as a function of samples collected from the serial port of the FPGA. (b) The weighted p-bits are correlated and when left floating they reproduce the truth table of the AND Gate as shown by the time-averaged statistics which are collected using $10^6$ samples. The FPGA results are in excellent agreement with the Boltzmann Law of Eq. 5.3                                                            | . 85 |

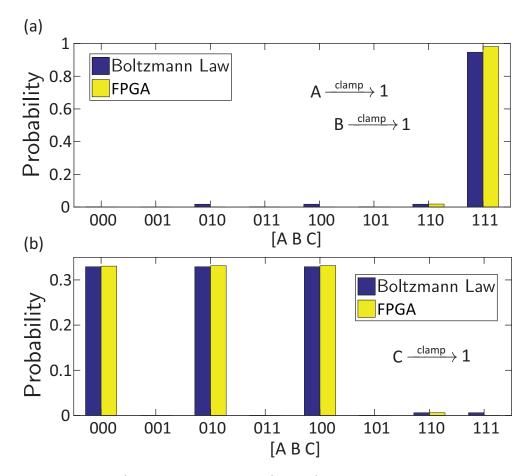

| 5.7  | Forward / Invertible mode (AND). Any weighted p-bit of the AND gate, input (A, B) or output (C) can be clamped using the bias vector $\{h\}$ through the Select and Clamp signals. (a) shows the long time statistics when the inputs A and B have been clamped to 1, while (b) shows the long time statistics when the output C has been clamped to 0. In both cases $10^6$ samples have been used.                                                                                                     | . 86 |

| xviii |  |

|-------|--|

|       |  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pag | ge |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

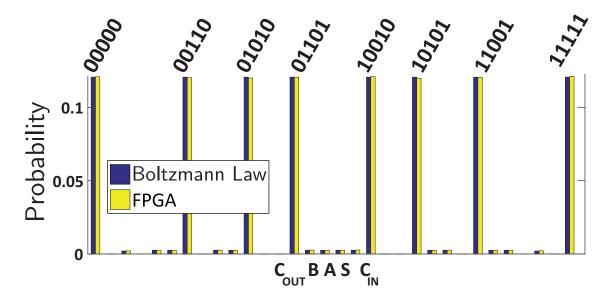

| 5.8  | Floating mode Full Adder. Long time statistics of the 14 weighted p-bit Full Adder using $10^6$ samples when all the terminals have been left floating are shown in the figure above. Similar to the AND gate, the Full Adder reproduces its truth table when all p-bits are left floating. Results show excellent agreement with Boltzmann Law (Eq. 5.3)                                                                                                                                                                                                                                                                                                                                                                                                   | . 8 | 88 |

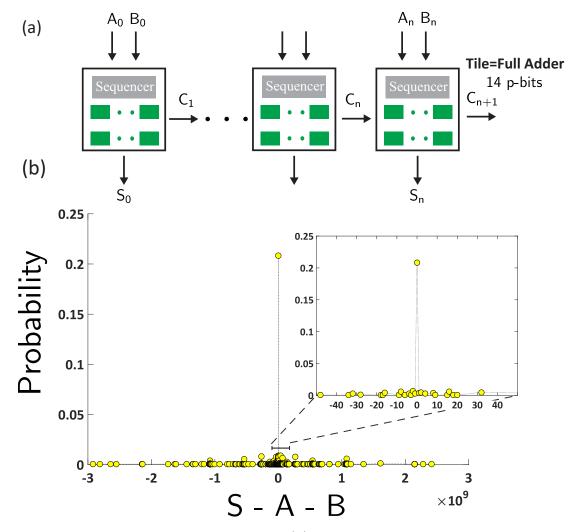

| 5.9  | <b>N-bit Ripple Carry Adder.</b> (a) Reciprocal networks of individual tiles programmed as Full Adders are interconnected in a directed manner to construct an N-bit Ripple Carry Adder (RCA). (b) The RCA is left floating and the long time statistics of the N-bit sum (S) and the inputs (A, B) get correlated in such a way to make a <i>single state</i> (inset) $S-A-B = 0$ appear with $\approx 20\%$ probability out of $10^5$ samples among billions of states ( $\pm 2^{32}$ ), as can be seen in the <i>x</i> -axis. Only $\approx 1500$ samples are shown for clarity.                                                                                                                                                                         | . ( | 91 |

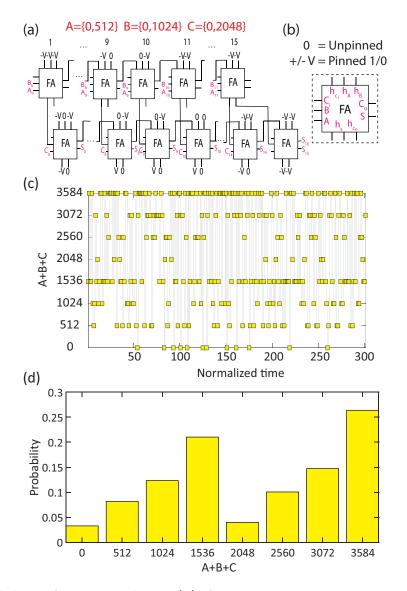

| 5.10 | Subset Sum Problem. (a) An adder that adds three 15-bit numbers A,B and C to give a 17-bit Sum S. The Sum S is first clamped to a particular number which in this case is 3584. The inputs A, B and C are constrained to particular sets using a scheme shown in (b) for each bit of the inputs. Note how the connections from the bottom layer of adders are <i>directed</i> where the sum is clamped to the top layer where the inputs A and B are added. In this example A is $\{0, 512\}$ , B is $\{0, 1024\}$ , and C is $\{0, 2048\}$ . (c) shows 300 time samples taken from a data sequence of $10^5$ from which two values of 3584 and 1536 appear more then the other 6 possible states. (d) shows the histogram corresponding to $10^5$ samples. | . ( | 92 |

| 6.1  | Microcontroller based p-bits. (a) 4-bit Invertible Adder built using 3 full adders and a half adder using 48 total p-bits, with the retention time of p-bits distributed from 120-28 ms. (b) shows the long time average statistics when the sum is clamped to 23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . ( | 94 |

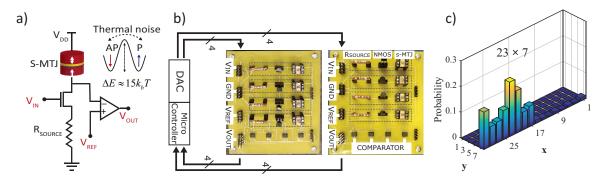

| 6.2  | <b>Probabilistic computing using STT-MRAM devices.</b> (a) shows an electrical schematic of a experimental p-bit which uses 40-60 nm stochastic MTJs. (b) shows a photograph of a printed circuit board which uses 8 p-bits to realize to a probabilistic computer. (c) shows integer factorization of $161 = 23 \times 7 \ldots \ldots$                                                                                                                                                                                                                                                                                                                                       | . ( | 95 |

| 6.3  | Analog multiplexer based p-bits. (a) shows an analog multiplexer that functions as a drop in replacement for an MTJ. (b) shows a 4 bit probabilistic computer which is used to factorize 35 using 4 p-bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . ( | 96 |

| 6.4  | <b>FPGA based probabilistic computer.</b> (a) shows a block diagram of FPGA based p-bit. A 32-bit invertible adder was built using 500 p-bits as shown in (b).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . ( | 97 |

#### ABSTRACT

Pervaiz, A. Z. Ph.D., Purdue University, December 2019. Hardware implementation of autonomous probabilistic computers. Major Professor: Supriyo Datta.

Conventional digital computers are built using stable deterministic units known as "bits". These conventional computers have greatly evolved into sophisticated machines, however there are many classes of problems such as optimization, sampling and machine learning that still cannot be addressed efficiently with conventional computing. Quantum computing, which uses q-bits, that are in a delicate superposition of 0 and 1, is expected to perform some of these tasks efficiently. However, decoherence, requirements for cryogenic operation and limited many-body interactions pose significant challenges to scaled quantum computers. Probabilistic computing is another unconventional computing paradigm which introduces the concept of a probabilistic bit or "p-bit"; a robust classical entity fluctuating between 0 and 1 and can be interconnected electrically. The primary contribution of this thesis is the first experimental proof-of-concept demonstration of p-bits built by slight modifications to the magnetoresistive random-access memory (MRAM) operating at room temperature. These p-bits are connected to form a clock-less autonomous probabilistic computer. We first set the stage, by demonstrating a high-level emulation of p-bits which establishes important rules of operation for autonomous p-computers. The experimental demonstration is then followed by a low-level emulation of MRAM based p-bits which will allow further study of device characteristics and parameter variations for proper operation of p-computers. We lastly demonstrate an FPGA based scalable synchronous probabilistic computer which uses almost 450 digital p-bits to demonstrate large p-circuits.

### 1. INTRODUCTION

#### 1.1 Probabilistic computing

Conventional digital computers are largely built from stable deterministic units know as "bits" using the standard MOS (metal-oxide-semiconductor) transistors. These computers have greatly evolved over the course of last few decades, but there are many classes of computational problems such as optimization, sampling and machine learning that cannot be addressed efficiently with conventional computers.

Richard Feynman in his seminal paper titled "Simulating physics with computers" [1] elaborated on computers which simulate the many quantum mechanical phenomenon in nature. This work is greatly credited for pioneering the field of quantum computing; a computing paradigm which uses quantum mechanical objects called "q-bits" which are in a delicate superposition of 0 and 1. While advances have been made in the field of quantum computing, decoherence, requirement for cryogenic operation and limited many-body interactions still pose significant challenges. As a prelude to quantum computers, Feynman hinted " $\cdots$  but the other way to simulate a probabilistic nature, which I'll call **R** for the moment, might still be to simulate a probabilistic nature by a computer **C** which itself is probabilistic,  $\cdots$ "

Probabilistic computing is an unconventional computing paradigm which introduces probabilistic bits or "p-bits". These p-bits are classical three-terminal units whose telegraphic output  $m_i$  is continuously fluctuating between two states 0 and 1. This output can be tuned using an analog input  $I_i$  at the input terminal. In mathematical terms,

Fig. 1.1. **Probabilistic computing.** Digital computing relies on stable deterministic units called "bits" which are either '0' or '1' at any given point in time. On the other end of the spectrum lies q-bits; quantum entities which are in a delicate super-position state of '0' and '1'. In this thesis we experimentally demonstrate probabilistic bits or "p-bits" that are robust, classical entities fluctuating between '0' and '1'. These p-bits can be used as natural hardware for many classical algorithms that introduce stochasticity using aritifical means, while a subset of problem reserved for quantum computing can also be mapped to networks of p-bits.

$$m_i(t) = \vartheta \Big[ \sigma(I_i) - r \Big]$$

(1.1)

where  $\vartheta$  is the unit step function,  $\sigma$  is the sigmoidal activation function acting on the analog input signal  $I_i$  and r is a random number uniformly distributed between 0 and 1. In the absence of the input  $I_i$ , the p-bit is just a random number generator with the statistics of the fluctuating resistance r. The input  $I_i$  functions as a bias on top of the fluctuating resistance r; in the sense that a negative input  $I_i$  will bias the output  $m_i$  negatively, resulting in more negative values at the output  $m_i$  while a positive input will bias the p-bit vice versa. Thus at the heart of a p-bit lies a classical fluctuating resistance r moving back and forth between two states.

The ability to bias the p-bits allows p-bits to get correlated to one another is what we call p-circuits. In these correlations lies the physics of the problem to be solved. So for example, the  $i^{th}$  p-bit can be driven by a synaptic input  $I_i$  derived from a problem description which is a function of all other outputs  $\{m_i, \dots, m_N\}$ . This derivation of the interconnect strengths (synapse) could be either done using first principles or also learned via machine learning principles.

An advantage of the classical nature of p-circuits lies in the various types of synapses that could be used to interconnect them. For example, linear synapses commonly used in neural networks

$$I_i = \left[\sum_j J_{i,j}m_j + h_i\right] \tag{1.2}$$

where  $J_{i,j}$  is the interconnect strength between the  $i^{th}$  and  $j^{th}$  p-bit and  $h_i$  is the on-site bias for the  $i^{th}$  p-bit; could easily be used in p-circuits. Such synapses have been used to implement invertible boolean logic gates as demonstrated in this thesis through out.

Alternately the interconnect strengths  $I_i$  for each p-bit can also be obtained using principles of calculus from an energy function E,

$$I_i = -\partial E(m_1, \cdots, m_N) / \partial m_i \tag{1.3}$$

These networks will visit different energy configurations with probabilities given by the Boltzmann law  $P(m_1, \dots, m_N)$  that are proportional to  $exp[-E(m_1, \dots, m_N)]$ , with the ground states of the energy landscape having the highest probability. This

Fig. 1.2. Thesis Overview. In this thesis we present an autonomous probabilistic computer which uses clock-less p-bits interconnected using a synapse as shown in the figure above. To achieve this, we first used a high-level emulation of p-bits using micro-controllers which helped establish important rules of operations for such systems. This was then followed by the "very first" experimental demonstration of a thermally unstable stochastic Magnetic Tunnel Junction (s-MTJ) based autonomous probabilistic computer. While we work towards scaling the s-MTJ based p-computer, we have built a low-level emulation of p-computers which will assist in further studying the role of device variations and new application spaces for probabilistic computers.

property allows such networks to be used for solving optimization problems, similar

to ising and adiabatic quantum computing, where the global minimum of the energy landscape is the configuration which minimizes the cost function identified by E.

We would like to point out that the term probabilistic computing has been used interchangeabley with stochastic computing historically. However, we would like to distinguish our "probabilistic computers" from the well known field of "stochastic computing". The expression stochastic computing was coined in the 1960s following the pioneering work of von Neumann [2], Gaines [3] and Poppelbaum et al. [4]. Stochastic computing focused on the reliable implementation of boolean algebra and probabilistic arithmetic. This was done using stochastic components whose major attraction lied in the use of low complexity units and inherent error tolerance. Stochastic computing used streams of bits to represent numbers which could be processed by simple circuits boolean gates such as AND gate. The outputs of these gates were then tabulated into probabilities. Our approach to probabilistic computing is very different to the above mentioned paradigm of stochastic computing — in the sense that we use a bit which is probabilistic in nature. For certain algorithms the probabilistic nature of our bit is needed, which is otherwise introduced artificially using pseudo random number generators at the significant expense of area and energy consumption.

#### 1.2 Organization of Thesis

In Chapter. 2 we first demonstrate a high-level emulation of p-bits using off the shelf microcontrollers. This emulation helped establish important rules of operation for autonomous p-computers such as the method of bypassing serial operation of p-bits; a mode of operation used in computer simulations.

We then present in Chapter. 3 the very first experimental proof-of-concept demonstration of probabilistic bits built using slight modifications of market ready magnetoresistive random-access memory devices. Eight of these devices are interconnected to form a clock-less autonomous probabilistic computer to which we map two distinct problems **a**) an Invertible boolean gate **b**) a hardware optimizer which maps integer factorization as an optimization problem.

We then demonstrate in Chapter. 4 a much lower-level emulation of s-MTJ based p-bits which will allow us to study the role of device parameter variations and device characteristics on proper system operation.

Finally we present in Chapter. 5, a CMOS based implementation of p-computers which demonstrates a 32-bit invertible Ripple Carry Adder (RCA) using 450 digital p-bits operating in a clocked synchronous manner.

#### 1.3 Publications associated with Thesis

- 1. A. Z. Pervaiz, L. A. Ghantasala, K. Y. Camsari, & S. Datta (2017). Hardware emulation of stochastic p-bits for invertible logic. Scientific reports, 7(1), 10994.

- A. Z. Pervaiz, B. M. Sutton, L. A. Ghantasala & K. Y. Camsari (2018). Weighted p-bits for FPGA implementation of probabilistic circuits. IEEE transactions on neural networks and learning systems. vol. 30, no. 6, pp. 1920-1926, June 2019.

- A. Z. Pervaiz, K. Y. Camsari & S. Datta (2019). Probabilistic computing with Binary Stochastic Neurons. In press: BCICTS 2019

- W. A. Borders, A. Z. Pervaiz, S. Fukami, K. Y. Camsari, H. Ohno & S. Datta (2019). Integer Factorization using stochastic Magnetic Tunnel Junctions. Nature 573, no. 7774 (2019): 390-393.

Equal Contributing First author.

#### Other contributions

- K. Y. Camsari, R. Faria, O. Hassan, A. Z. Pervaiz, B. M. Sutton & S. Datta (2017). p-transistors and p-circuits for Boolean and non-Boolean logic. In Spintronics X (Vol. 10357, p. 103572K). International Society for Optics and Photonics.

- K. Y. Camsari, P. Debashis, V. Ostwal, A. Z. Pervaiz, T. Shen, Z. Chen, S. Datta and J. Appenzeller (2018). From charge to spin and spin to charge: Stochastic magnets for probabilistic switching. Under review: Proceedings of the IEEE

- A. Z. Pervaiz, K. Y. Camsari & S. Datta (2019). Asynchronous computing with p-bits. *Invited talk*. ASYNC 2019, Hirosaki Japan.

- K. Y. Camsari, A. Z. Pervaiz, R. Faria, E. E. Marinero & S. Datta (2016). Ultrafast spin-transfer-torque switching of synthetic ferrimagnets. IEEE Magnetics Letters, 7, 1-5.

## 2. HARDWARE EMULATION OF STOCHASTIC P-BITS FOR INVERTIBLE LOGIC

Materials in this chapter have been extracted verbatim from the paper: A. Z. Pervaiz, L. A. Ghantasala, K. Y. Camsari, & S. Datta (2017). Hardware emulation of stochastic p-bits for invertible logic. Scientific reports, 7(1), 10994.

#### 2.1 Introduction

This chapter presents the blue print of our autonomous p-computers. To begin our development of nano-device based p-computers we first emulate the idealized behavior of p-bit using off the shelf microcontrollers. The striking properties of p-circuits such as invertible logic are quite intriguing, but these were previously demonstrated using pure software implementations of Eqs. (1.1,1.2). In simulations of these p-circuits, it was well known that each p-bit needs to be updated in a serial manner. This process is enabled using control loop statements, however this represents a significant challenge towards scaling p-circuits to incorporate for example several millions of p-bits. A serial operation where each p-bit is updated one at a time seems rather difficult for scaled systems, and still says nothing of the dedicated hardware needed to implement such a large scale serial operation. Other questions addressing the effect of parameter variations among p-bits also need to be addressed.

In this chapter we demonstrate an *autonomous* p-computer where the serial updating of p-bits comes naturally without any peripheral control circuity. This fortuitous result comes due to the asynchronous operation of p-bits which result from natural time delays between p-bits in this case, while in later systems due to the statistics of the p-bit retention times. This paper presents a first pass in discovering and answering important questions that would arise in the hardware development of p-circuits. Our approach is similar to ref. [5] in the sense that we use microcontrollers to emulate both Eq. (1.1) and the interconnections between p-bits described by Eq. (1.2.

The hardware emulation presented in this chapter shares many of the essential feature of s-MTJ based p-computers; The output  $m_i(t)$  and the input  $I_i(t)$  appearing in Eqs. (1.1) and (1.2) are both actual voltages and both sub-systems are completely independent of each other. This allows us to later simply drop-in the s-MTJ based p-bits (chapter. 3) while using the same synapse. We also study the variability in retention times  $\tau_N$  of the p-bits and the role of interconnect delay  $\tau_{inter}$  on system operation. To summarize, the hardware emulation presented here helped establish important rules of operation for the autonomous p-circuits that are to follow in this thesis.

Next we describe our approach to emulate Eqs. (1.1) and (1.2). Fig. 2.1 shows a microcontroller based emulation of a p-bit. We then present a 3 p-bit circuit which implements an invertible AND gate (Figs. 2.2,2.3). We use this simple circuit to study the effects of  $\tau_N$  and  $\tau_{inter}$  (Figs. 2.4,2.5,2.6). This is followed by demonstrations of larger p-circuits; the 4-bit adder and the 4-bit multiplier, both working in the inverted mode.

#### 2.2 Methods

#### 2.2.1 Arduino pro mini as a p-bit

A version of Eq. (1.1) suitable for emulation of a p-bit by a microcontroller is given as

$$V_{OUT}(t) = sgn\left\{S(V_{IN}(t)) - rand(0,1)\right\}$$

(2.1)

where  $V_{OUT}$  is the digital output and  $V_{IN}$  is the analog input voltage of the p-bit. S(x) is a sigmoidal activation function which acts on an input x. Mathematically,

$$S(x) = \frac{1}{1 + e^{-2x}} \tag{2.2}$$

I/O characteristics: An Arduino pro-mini is a 24 pin microcontroller [6]. We program it to emulate the behavior of a p-bit using Eq. (2.1). A pseudo-code is given in Alg. 1. The microcontroller has 6 input pins which are connected to an internal 10bit analog-to-digital converter. The analog input pins have very high input resistances ( $\approx 100M\Omega$ ). The arduino pro-mini also has dedicated pins for PWM (Pulse-width modulation) outputs with low output resistances ( $\approx 100\Omega$ ) and the ability to source 40 mA of current.

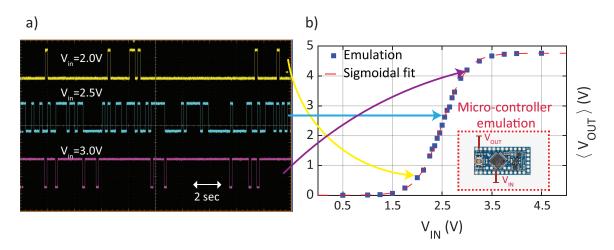

**p-bit operation:** Fig. 2.1(a) shows a time snapshot of the output voltage of a p-bit for a set of applied input voltages as captured on an oscilloscope (Tektronix DPO7104). For each applied input voltage  $V_{IN}$  the average output voltage is measured. At a  $V_{IN} = 2.5V$  the p-bit is fluctuating randomly between low and high states. When the input voltage is lowered or increased, the p-bit output gets biased towards more 0's or 1's. DC average measurements of the output voltage taken over 100 seconds are shown in Fig. 2.1(b). The shape of the average response of a p-bit follows the sigmoidal function given by Eq. 2.2.

Retention time  $\tau_N$ : Each p-bit is characterized by a retention time  $\tau_N$ ; a time period for which the output voltage maintains its state. Stochastic magnetic tunnel junctions (s-MTJs) have been proposed [7] as the building blocks for p-bits. These s-MTJs are two magnets, one stable (called a fixed layer) and the other (called a free layer), seperated by a thin insulating oxide. In s-MTJs the retention time is dependent on the energy barrier of the free layer whose energy barrier is lowered to make it stochastic. For example, MTJs meant to be used for digital memory are designed to have large energy barriers ( $\gg 40k_BT$ ), such that a bit of information stored remains intact for many years to come. For magnets the retention time is given by [8] :

$$\tau_N = \tau_0 \, \exp\left(\frac{\Delta}{k_B T}\right) \tag{2.3}$$

where  $\tau_0$  is a material dependent quantity ranging from a few ps to a ns [9],  $\Delta$  is the energy barrier of the free layer and  $k_B T$  is the Boltzmann energy. For stochastic MTJs with energy barriers of  $10 - 20 \ k_B T$ , the retention time is in the ms regime typically [10]. A user defined delay  $\tau_N$  shown in Alg. 1 is used to emulate the retention time of p-bits. This user defined delay is systematically changed to characterize its effects on system operation.

| Algorithm 1 Pseudocode for p-bit                 |                                                           |

|--------------------------------------------------|-----------------------------------------------------------|

| Parameters:                                      |                                                           |

| Digital output $V_{OUT}$ ;                       |                                                           |

| Analog input $V_{IN}$ ;                          |                                                           |

| Repeat:                                          |                                                           |

| $x \leftarrow \text{analogRead}(V_{\text{IN}});$ | $\triangleright V_{IN} \in (0, 5 \text{ V}), x \in (0.5)$ |

| $m \leftarrow 2x - 5;$                           | $\triangleright \mathbf{m} \in (-5,5)$                    |

| $Bias \leftarrow S(m);$                          | $\triangleright$ Bias $\in (0, 1)$ from Eq.(2.2)          |

| $W \leftarrow rand(0, 1);$                       | $\triangleright W \sim U(0,1)$                            |

| $\mathbf{If}(\mathrm{Bias} > \mathrm{W})$        |                                                           |

| $V_{OUT} \leftarrow 1;$                          |                                                           |

| Else                                             | $\triangleright V_{OUT} \in \{0, 5 V\}$                   |

| $V_{OUT} \leftarrow 0;$                          |                                                           |

| EndIf                                            |                                                           |

| Wait $\tau_{\rm N}$ ;                            |                                                           |

| EndRepeat                                        |                                                           |

#### 2.2.2 Synapse using a microcontroller and DAC

Fig. 2.2(a,b) shows the schematic and the block diagram of a 3 p-bit circuit. The p-bits are interconnected via a synapse which calculates the input voltage  $V_{IN}$  of the  $i^{th}$  p-bit using

$$V_{IN}(t) = I_0 \left\{ h_i + \sum_j J_{ij} V_{OUT}(t) \right\}$$

(2.4)

A pseudo-code for implementing the synapse is described in Alg. 2 where another user defined delay  $\tau_{inter}$  is added. This delay is meant to simulate the interconnect delay, which any real synapse would have in practice. Please note that Eq. (2.4) describes a liner synapse as described by Eq. (1.2), but the synapse can also implement non-linear interconnections as shown in later chapters.

Synapse using microcontroller: Our synapse is implemented using an Arduino Mega2560 microcontroller along with a MAXIM 5825 8 channel 12 bit digital-toanalog converter [11] (DAC). The Arduino Mega2560 reads the output voltage of each p-bit and calculates the inputs voltage for each p-bit accordingly. This calculation is turned into an analog voltage using DACs; a process which requires the Arduino Mega2560 to use one of its peripheral interfaces. We use a serial interconnect protocol known as  $I_2C$ , which limits the interconnect delay  $\tau_{inter}$  to  $\approx ms$ . The synapse can set a maximum voltage of 5 V, which requires the synapse to threshold the input voltages  $V_{IN}$ . The Arduino Mega2560 also provides a serial port which allows communication over the USB port. This is particularly useful for observing the state of p-circuits on a computer. Another possible method of observing the p-circuits is to create an artificial node (an analog voltage). An example of this is shown in Fig. 2.2(c), where an analog voltage  $4 \times A + 2 \times B + C$  is set via the DAC and observed on the oscilloscope.

| Parameters:                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog outputs $V_{IN}$ ;                                    | $\triangleright$ The input voltages of p-bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Digital inputs V <sub>OUT</sub> ;                            | $\triangleright$ The output voltages of p-bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Parameters $[J], \{h\}$ and $I_0$ ;                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $n \leftarrow \text{Number of p-bits};$                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $k \leftarrow \text{DAC}$ terminal for word;                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Repeat:                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| For $i \in \{1 \cdots, n\}$                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |