# HIGH TEMPERATURE SEMICONUCTING POLYMERS AND POLYMER BLENDS

by

Aristide Gumyusenge

#### **A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

Department of Chemistry West Lafayette, Indiana December 2019

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

### Dr. Jianguo Mei

Department of Chemistry

# Dr. Bryan Boudouris

Department of Chemistry

### Dr. Libai Huang

Department of Chemistry

### **Dr.** Corey Thompson

Department of Chemistry

#### Approved by:

Dr. Christine Hrycyna

To my family.

#### ACKNOWLEDGMENTS

First, I want to thank my advisor, Dr. Jianguo Mei for his unceasing mentorship; he made this learning chapter possible not only through his advice, but also by setting the example in terms of hard work, leadership, and problem solving. I also want to thank my labmates who through collaborative efforts helped me carry out my research. Special thanks go to Dr. Yan Zhao who mentored me at the very beginning of my research and continues to be an exemplary mentor. I thank the research collaborators especially Prof. Ying Diao's group, Prof. Alexander Ayzner's group, and Prof. Brett Savoie. Not only did they directly help carrying out the characterizations towards the completion of the research, but they also provided invaluable feedback and discussion that helped me tackle the scientific questions throughout my research. I would also like to appreciate the financial support for the research from the National Science Foundation (NSF CAREER Award, no. 1653909), the Office of Naval Research (Nos. N00014-16-1-2551 and N00014-19-1-2027), and Purdue University.

# TABLE OF CONTENTS

| LIST | OF T | ABLES                                                                     | 8   |

|------|------|---------------------------------------------------------------------------|-----|

| LIST | OF F | IGURES                                                                    | 9   |

| ABST | RAC  | Т                                                                         | 15  |

| CHAI | PTER | 1. GENERAL INTRODUCTION                                                   | 16  |

| 1.1  | Cha  | rge transport in organic semiconductors                                   | 16  |

| 1.2  | Infl | uence of temperature on charge transport in organic semiconductors        | 18  |

| 1.3  | Infl | uence of temperature on charge transport in conjugated polymer thin films | 22  |

| 1.4  | Obj  | ectives of this dissertation                                              | 24  |

| CHA  | PTER | 2. HIGH TEMPERATURE OPERATION IN SEMICONDUCTING POLYM                     | 1ER |

| BLEN | IDS  |                                                                           | 26  |

| 2.1  | Intr | oduction                                                                  | 26  |

| 2.2  | Exp  | perimental                                                                | 28  |

| 2.   | .2.1 | Materials                                                                 | 28  |

| 2.   | .2.2 | Thermal transition measurements                                           | 30  |

| 2    | .2.3 | OFET devices fabrication and characterization                             | 30  |

| 2.   | .2.4 | Morphology analysis                                                       | 31  |

| 2    | .2.5 | In-situ temperature-dependent Grazing Incidence X-ray Diffraction (GIXD)  | 32  |

| 2.   | .2.6 | UV-Vis spectroscopy                                                       | 32  |

| 2.   | .2.7 | Molecular dynamics (MD) simulations                                       | 33  |

| 2.3  | The  | rmal stabilization of conjugated polymer thin films by blending           | 35  |

| 2.4  | Rat  | ionalizing high temperature operation stability in polymer blends         | 40  |

| 2    | .4.1 | Impact of blending on morphology                                          | 40  |

| 2    | .4.2 | Impact of blending on ordering and packing                                | 43  |

| 2.5  | Mo   | lecular dynamics simulations                                              | 49  |

| 2.6  | Ger  | neralization of the blending approach                                     | 57  |

| 2    | .6.1 | Host matrix generality and scope                                          | 58  |

| 2.   | .6.2 | Semiconductor generality and scope                                        | 62  |

| 2.7  | Cor  | nclusions                                                                 | 69  |

| CHAF | PTER | 3. ALL-PLASTIC THERMALLY STABLE ELECTRONICS                               | 70  |

| 3.1 Intr | roduction                                                                     |         |

|----------|-------------------------------------------------------------------------------|---------|

| 3.2 Exp  | perimental                                                                    | 71      |

| 3.2.1    | Materials                                                                     | 71      |

| 3.2.2    | OFETs fabrication and characterization:                                       |         |

| 3.2.3    | Capacitance measurement:                                                      | 73      |

| 3.2.4    | In-situ temperature-dependent measurements:                                   |         |

| 3.2.5    | Morphology analysis                                                           |         |

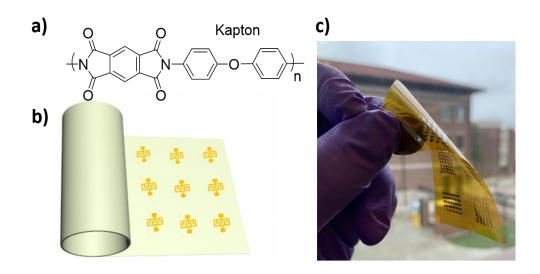

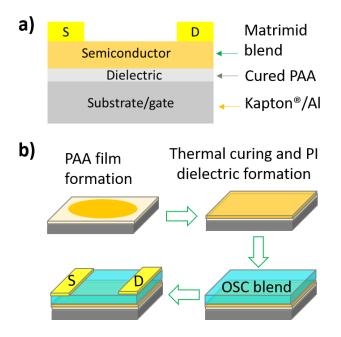

| 3.3 The  | ermally stable plastic transistors fabrication                                | 74      |

| 3.3.1    | Thermally stable plastic substrates                                           | 74      |

| 3.3.2    | Thermally stable dielectrics                                                  | 76      |

| 3.3.3    | Sequential layering approach                                                  | 80      |

| 3.4 Tei  | mperature resistant plastic transistors                                       |         |

| 3.5 Bal  | king of plastic electronics                                                   |         |

| 3.6 Co   | nclusions                                                                     |         |

| CHAPTER  | R 4. INFLUENCE OF MOLECULAR WEIGHT ON THERMAL STABI                           | LITY OF |

| SEMICON  | NDUCTING POLYMER BLENDS                                                       |         |

| 4.1 Intr | roduction                                                                     |         |

| 4.2 Exp  | perimental                                                                    |         |

| 4.2.1    | Materials                                                                     |         |

| 4.2.2    | UV-Vis absorption characterization                                            |         |

| 4.2.3    | Morphology analysis                                                           | 100     |

| 4.2.4    | OFETs fabrication and characterization                                        | 100     |

| 4.2.5    | In-situ temperature-dependent measurements                                    | 101     |

| 4.3 Dis  | scovering the influence of molecular weight on high temperature blend perform | mance   |

|          |                                                                               | 102     |

| 4.3.1    | Materials selection                                                           | 102     |

| 4.3.2    | Transistor performance demonstration                                          | 103     |

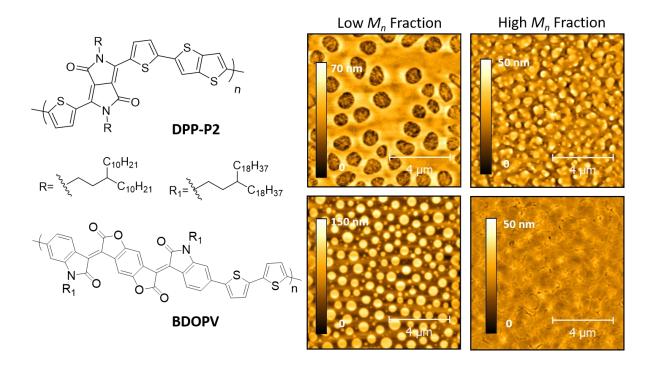

| 4.4 Inf  | luence of molecular weight on blend morphology engineering                    | 107     |

| 4.4.1    | Impact of molecular weight on miscibility                                     | 107     |

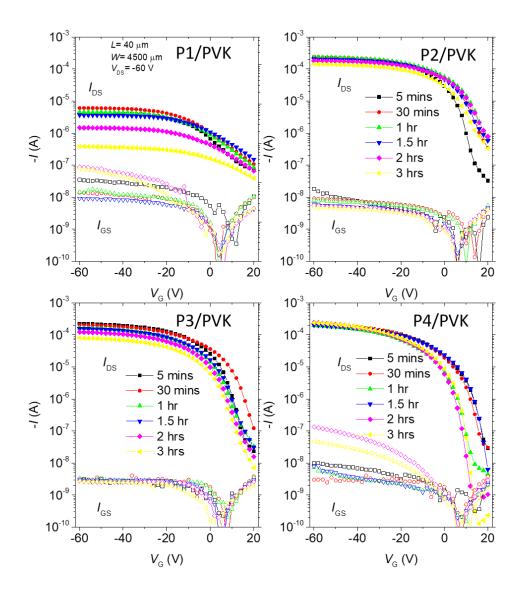

| 4.4.2    | Impact of miscibility on thermal stability                                    | 116     |

| 4.5 Mo   | blecular weight guided thermal stability in transistors                       | 118     |

| 4.6 C  | Conclusio | ons                |                |               |             |     |         |

|--------|-----------|--------------------|----------------|---------------|-------------|-----|---------|

| CHAPTI | ER 5.     | POLY(LADDEI        | R-IMIDES):     | MATRIX        | ENGINEERING | FOR | EXTREME |

| TEMPE  | RATURI    | E POLYMER BL       | ENDS           |               |             |     |         |

| 5.1 Ir | ntroducti | on                 |                |               |             |     |         |

| 5.2 E  | Experime  | ntal               |                |               |             |     |         |

| 5.2.1  | 1 Mate    | rials              |                |               |             |     |         |

| 5.2.2  | 2 Morp    | hology character   | ization        |               |             |     |         |

| 5.2.3  | 3 UV-V    | is absorption      | •••••          |               |             |     |         |

| 5.2.4  | 4 Capa    | citance measuren   | nents          |               |             |     |         |

| 5.2.5  | 5 OFET    | Is devices fabrica | ation and char | racterization |             |     |         |

| 5.2.6  | 6 In-sit  | u temperature de   | pendent meas   | surements     |             |     |         |

| 5.3 P  | oly(ladd  | er-imides) as higl | n temperature  | e matrices    |             |     |         |

| 5.3.1  | 1 Tune    | d blend compatib   | ilization and  | morphology    | ,           |     |         |

| 5.3.2  | 2 Impro   | oved dielectrics p | roperties      |               |             |     |         |

| 5.3.3  | 3 Impro   | oved transistor pe | rformance      |               |             |     |         |

| 5.3.4  | 4 Therr   | nally stable high- | performance    | transistors . |             |     |         |

| 5.4 C  | Conclusio | ons                | •••••          |               |             |     |         |

| CHAPTI | ER 6. C   | CLOSING REMA       | RKS AND C      | OUTLOOK.      |             |     |         |

| REFERE | ENCES     |                    |                |               |             |     |         |

| VITA   |           |                    |                |               |             |     |         |

| PUBLIC | CATIONS   | 5                  |                |               |             |     |         |

### LIST OF TABLES

Table 2.2. Summarized glass transition temperatures  $(T_g)$  of the studied host matrices and the corresponding molecular weights. <sup>b</sup>Dynamic scanning calorimetry (DSC) scans were taken at 10 °C/min heating/cooling rates. <sup>c</sup>Tetrahydrofuran was used as the eluent at room temperature. 29

| Table 2.3. Summarized partial charges of each atom type parameterized based on wE | 397X-D/def2- |

|-----------------------------------------------------------------------------------|--------------|

| TVZP calculations of the minimized geometry.                                      |              |

|                                                                                   |              |

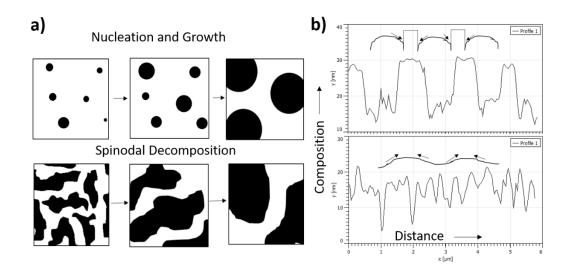

Table 4.1. Comparison between nucleation and growth and spinodal decomposition morphologicalbehaviors in binary polymer blends.117

## LIST OF FIGURES

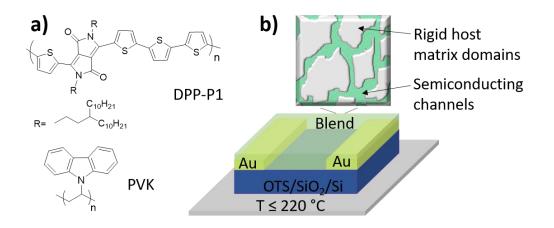

| Figure 2.1 Blending strategy to beating the heat. a) Molecular structures of both the semiconducting polymer and the high-Tg insulating host used in the study of high temperature semiconducting polymer blends. b) Design rigid blend morphology where the rigid host domains are mixed with semiconducting crystalline channels to form a thermally robust blend composite. Also show is the transistor device architecture used for temperature dependent electronic measurements |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

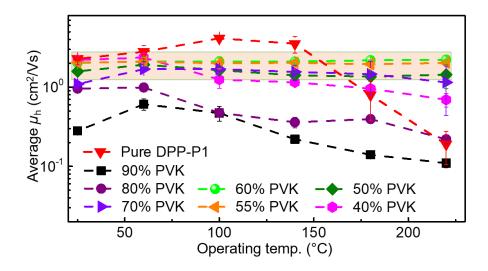

| Figure 2.2. Temperature dependent hole mobility extracted from FETs with varying blend composition                                                                                                                                                                                                                                                                                                                                                                                    |

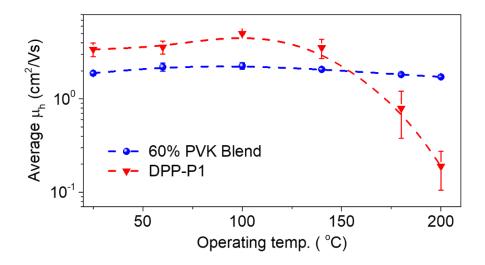

| Figure 2.3. Temperature dependent hole mobility from representative transistor devices measured under a nitrogen-filled environment                                                                                                                                                                                                                                                                                                                                                   |

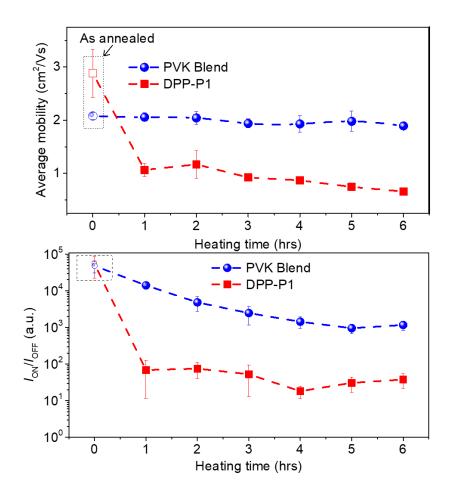

| Figure 2.4. Transistor behavior under constant thermal stress. After six hours of thermal stress, stable transistor performance is retained in the blend films                                                                                                                                                                                                                                                                                                                        |

| Figure 2.5. Characteristic transistor curve after 1 hour of thermal stress at 150°C comparing the thermal stability of the studied blend film to the pristine film                                                                                                                                                                                                                                                                                                                    |

| Figure 2.6. Morphology evolution with varying content of the insulating matrix. With optimal blending ratio, interpenetrating network of the crystalline conjugated polymer domains is formed surrounded by the host matrix                                                                                                                                                                                                                                                           |

| Figure 2.7. Morphology of the bottom interface revealing interconnected domains of the conjugated polymer analogous the top face morphology                                                                                                                                                                                                                                                                                                                                           |

| Figure 2.8. Effect of thermal stressing on thin film morphology. The blend film as well as the pristine matrix film show no changes after heating while the pristine conjugated polymer film reveals slight changes in the domain sizes                                                                                                                                                                                                                                               |

| Figure 2.9. Effect of blending on ordering. Normalized absorption spectra from DPP-p1 films when blended with different contents of PVK                                                                                                                                                                                                                                                                                                                                               |

| Figure 2.10. Temperature dependent absorption spectra of the pristine DPP-P1 film compared to the blend film containing 60 % of PVK                                                                                                                                                                                                                                                                                                                                                   |

| Figure 2.11. Diffraction patterns of DPP-P1 and corresponding PVK blend. The blend shows to inherit the $\pi$ - $\pi$ stacking nature of the conjugated polymer while retaining the amorphous domains of the insulator                                                                                                                                                                                                                                                                |

| Figure 2.12. In-situ temperature dependent diffraction analysis. a) In-plane line profile obtained from the 2-D diffraction patterns of DPP-P1 and its PVK blend at different temperatures. b) Extracted $\pi$ - $\pi$ stacking distances as well as the lamellar d-spacing of the films studied with increasing temperature. 48                                                                                                                                                      |

| Figure 2.13. Illustration of the impact of close packing of conjugated polymers chains on their degree of torsional disordering                                                                                                                                                                                                                                                                                                                                                       |

Figure 2.21. Blending generality in DPP-P1 films. Temperature dependent hole mobilities extracted from transistor devices of DPP-P1 when blended with different high Tg matrices...... 60

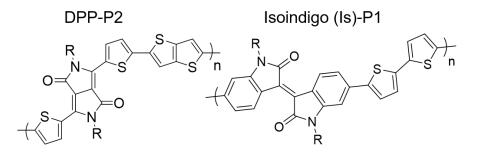

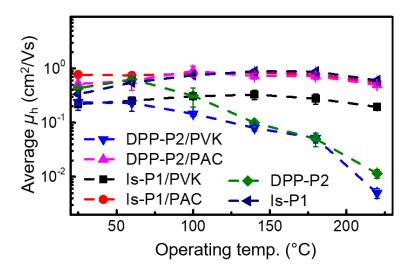

| Figure 2.26. Normalized absorption spe | ectra of DPP-P2 and it | ts blends with the | studied matrices. |

|----------------------------------------|------------------------|--------------------|-------------------|

|                                        |                        |                    |                   |

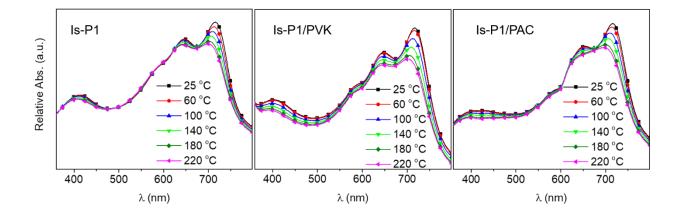

Figure 2.27. Normalized absorption spectra of Is-P1 and its blends with the studied matrices... 65

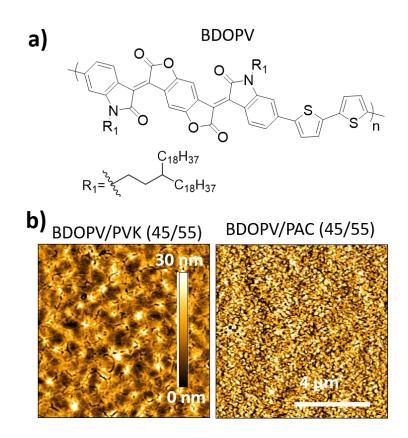

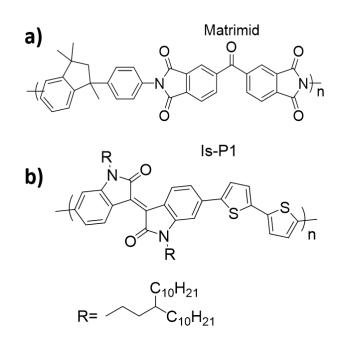

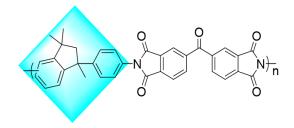

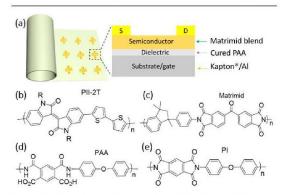

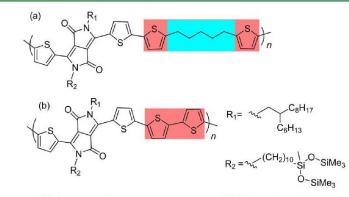

Figure 3.5. Semiconducting layer design for thermally stable all-plastic transistors. a) Molecular structure of Matrimid used as the polyimide host in the semiconducting layer. b) Molecular structure of the isoindigo-based semiconducting polymer used in the semiconducting blend..... 81

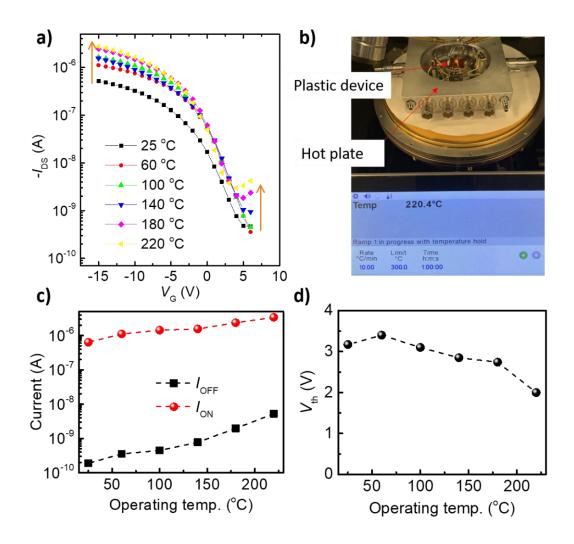

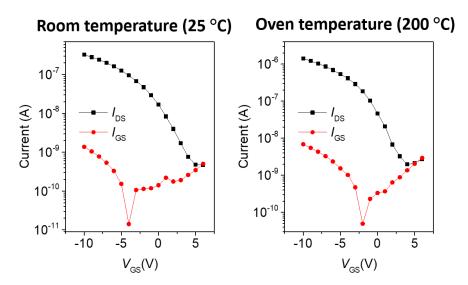

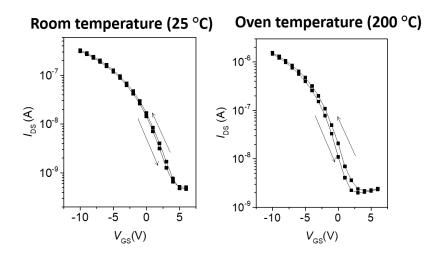

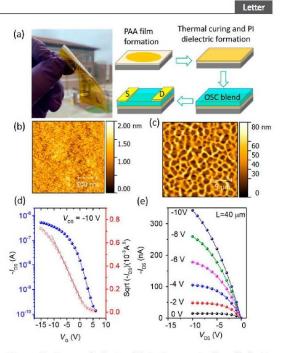

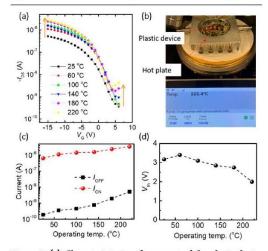

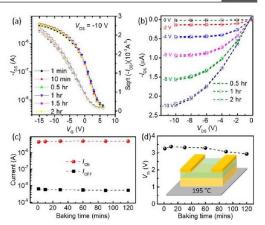

Figure 3.11. Temperature dependent characterization of the plastic devices. a) Thermal response of the transfer current showing increasing ON currents due to thermal activation. b) Experimental setup for the in-situ temperature dependent measurement of the plastic devices. c) Temperature dependent ON and OFF currents obtain from the representative average transistor device. d) The extracted threshold voltage with increasing temperature showing minimal variation upon heating.

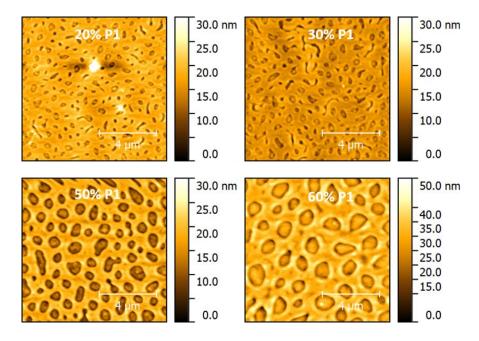

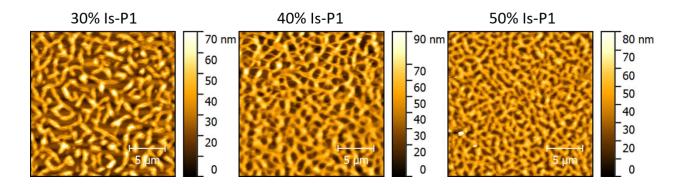

Figure 4.6. Nucleation and growth behavior in low molecular weight polymer blends. Morphology evolution of in P1 blends with varying blend ratio indicating the nucleation and growth behavior. 109

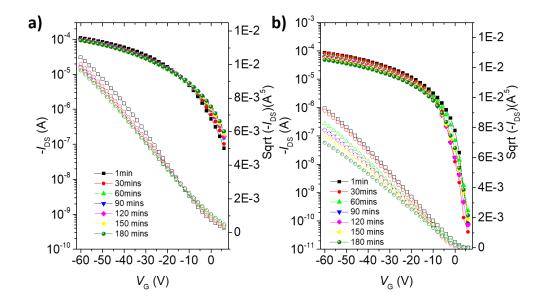

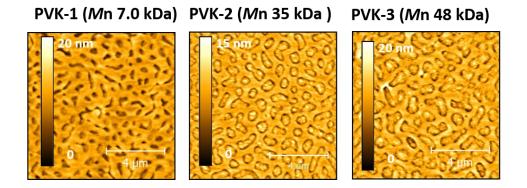

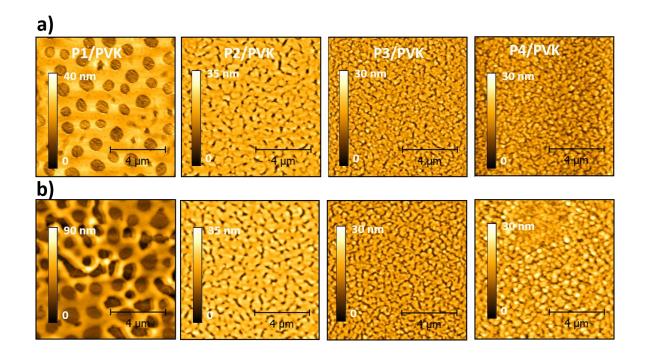

Figure 4.7. a) Illustration of nucleation and growth morphology compared to spinodal decomposition. b) Representative line profiles extracted from the AFM height images of P1/PVK and P2/PVK blend films. P1 films exhibit isolated cylindrical micelles across the hole film indicative of a nucleation and growth composition distribution. The insets represent the classical representative of the blend composition distribution across the film in comparison to the profiles.

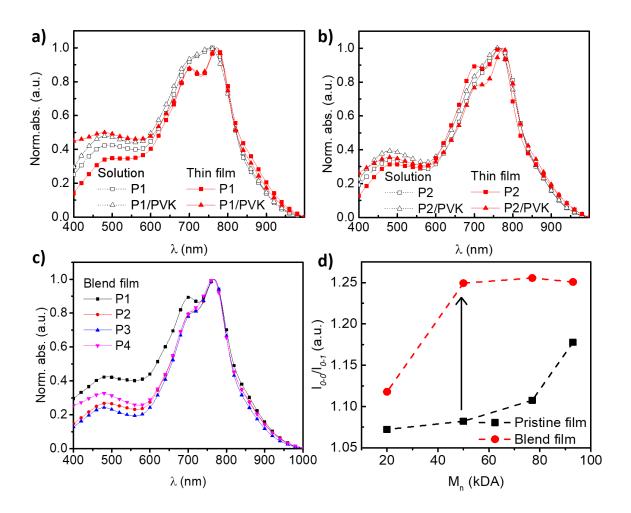

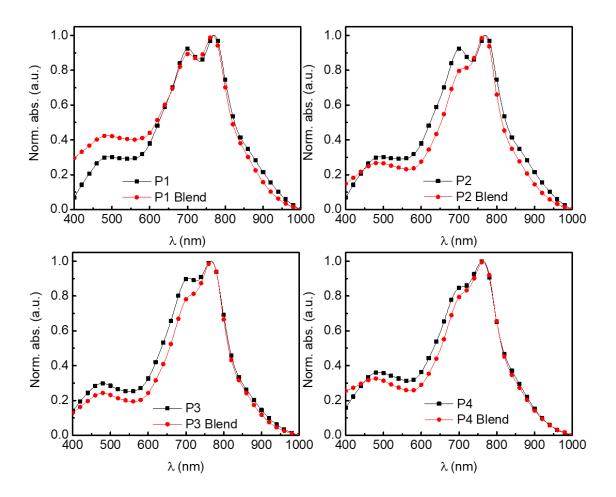

Figure 4.8. UV-Vis absorption comparison with varying molecular in the blends. a) b) Normalized absorptions P1 and P2 solutions and films compared to corresponding PVK blends. c) UV-Vis absorption spectra comparing the PVK blend films with different molecular weights of the semiconducting component. d) Extracted *0-0/0-1* vibronic peaks ratio from normalized absorption spectra.

Figure 4.12. AFM height images of blend films a) before and b) after baking near the Tg of the host matrix for 12 hours. An obvious expansion accompanied by a de-mixing is observable in the case of P1 while no significant morphological changes could be observed in the higher Mn based blends.

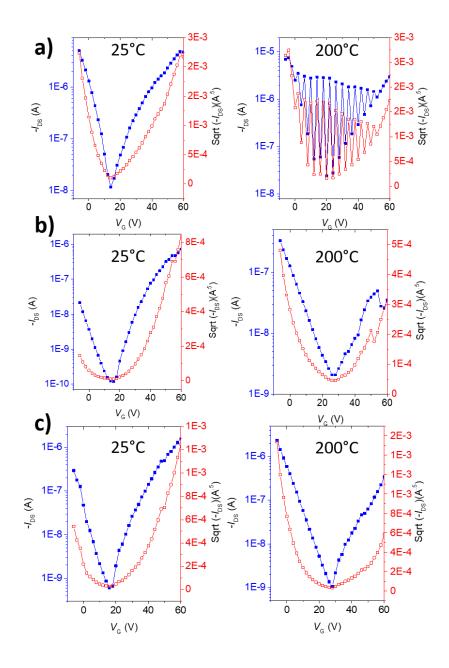

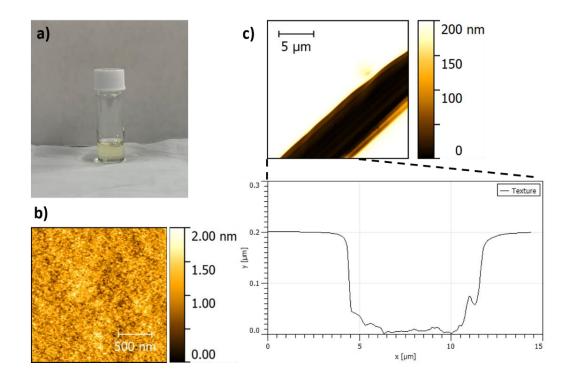

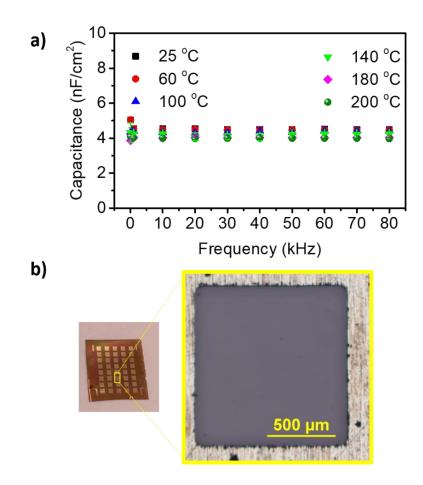

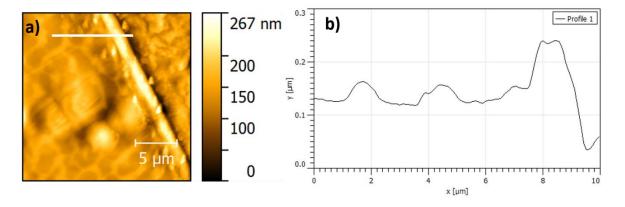

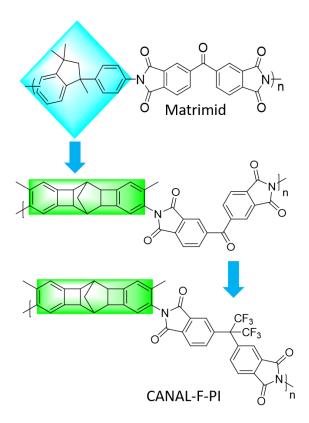

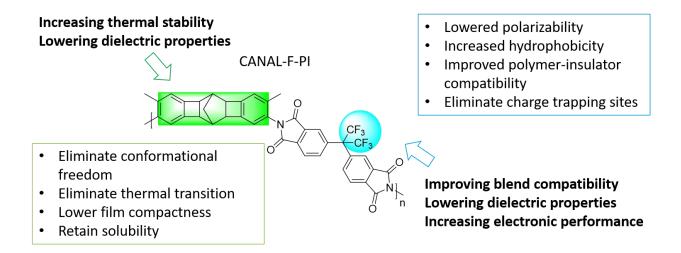

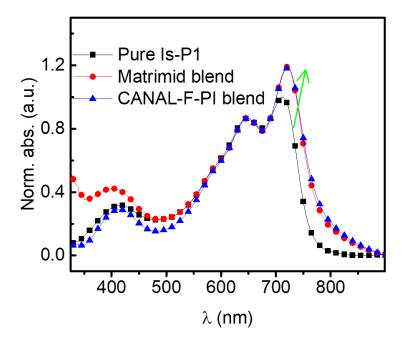

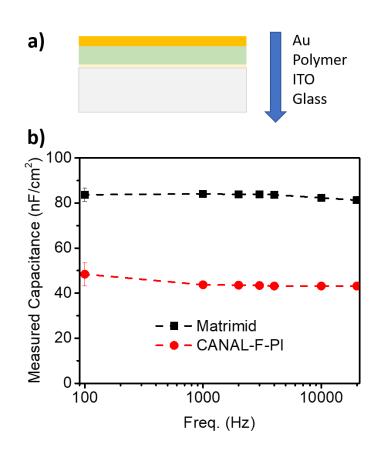

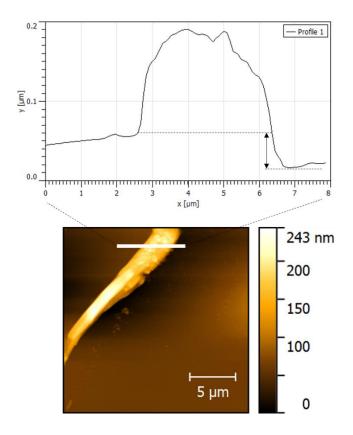

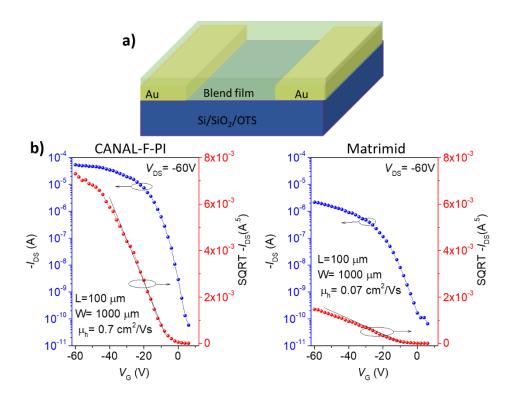

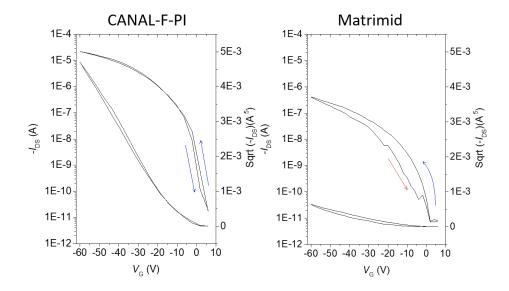

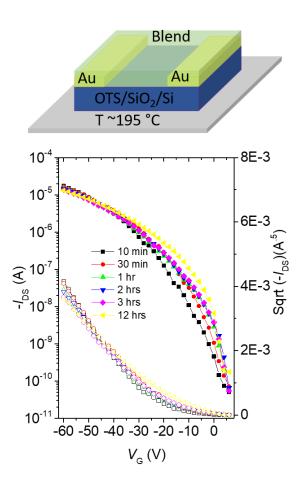

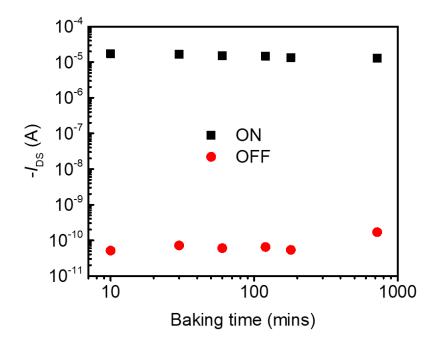

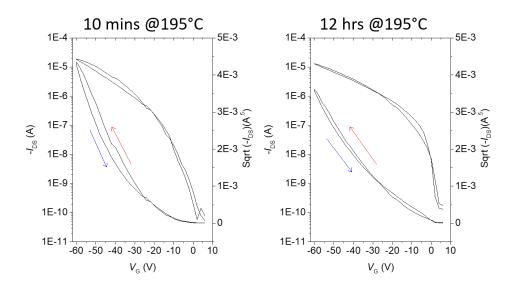

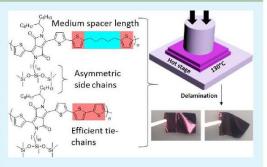

Figure 5.4. Normalized absorption spectra of Is-P1 in its pristine form compared to its Matrimid and CANAL-F-PI blends. A significant redshift accompanied with increased peak intensity in the Figure 5.5. Morphology characterization of blend films of CANAL-F-PI and Is-P1. A uniformly Figure 5.6. Capacitance comparison between polyimide-based matrices. a) The illustration of the sandwich structure used for the capacitance measurement. b) Measured capacitances for Matrimid Figure 5.7. Thickness extraction for matrix polymer films for the capacitance evaluation. The thin Figure 5.8. Electronic properties of CANAL-F-PI based blends compared to Matrimid based blends. a) Illustration of the transistor devices used for electronic performance comparison. b) Figure 5.9. Hysteresis characterization of the transistor devices based on blend films of Matrimid Figure 5.10. Baking characterization of transistor devices based on CANAL-F-PI blends. Overlapping current curves are observed when the devices are subjected to constant thermal stress Figure 5.11. Baking analysis of the transistor devices based on Is-P1/CANAL-F-PI blends. The extracted ON/OFF currents exhibit excellent stability even after baking for 12 hours under N<sub>2</sub>. Figure 5.12. Hysteresis characterization of transistor devices based on CANAL-F-PI blends under

#### ABSTRACT

Organic semiconductors have witnessed a prolific boom for their potential in the manufacturing of lightweight, flexible, and even biocompatible electronics. One of the fields of research that has yet to benefit from organic semiconductors is high temperature electronics. The lightweight nature and robust processability is attractive for applications such as aerospace engineering, which require high temperature stability, but little has been reported on taking such a leap because charge transport is temperature dependent and commonly unstable at elevated temperatures in organics. Historically, mechanistic studies have been bound to low temperature regimes where structural disorders are minimal in most materials. Discussed here is a blending approach to render semiconducting polymer thin films thermally stable in unprecedented operation temperature ranges for organic materials. We found that by utilizing highly rigid host materials, semiconducting polymer domains could be confined, thus improving their molecular and microstructural ordering, and a thermally stable charge transport could be realized up to 220°C. With this blending approach, all-plastic high temperature electronics that are extremely stable could also be demonstrated. In efforts to establish a universal route towards forming thermally stable semiconducting blends, we found that the molecular weight of conjugated polymer plays a crucial role on the miscibility of the blends. Finally, we found that the choice of the host matrix ought to consider the charge trapping nature of the insulator.

#### CHAPTER 1. GENERAL INTRODUCTION

#### 1.1 Charge transport in organic semiconductors

Since the demonstration of semiconducting and conducting properties in organic materials by Prof. Alan Heeger and colleagues,<sup>1-3</sup> this class of materials has gained tremendous attention for a multitude of applications.<sup>4-6</sup> Though these materials were not necessarily destined to rival the inorganics such as crystalline silicon, they offered other features that remain challenging to realize in inorganic systems including solution processability into thin films, flexibility, as well as biocompatibility.<sup>7-15</sup> Experimentally, the electronic performances of organic materials are commonly characterized in terms of their charge carrier mobility either in a diode configuration, a field-effect transistor, or using other setups such as time of flight and pulse radiolysis. Organic field-effect transistors (OFETs) became one of the most widely studied electronic configurations.<sup>16-21</sup> A FET is a three terminal electronic device consisting of a semiconducting layer deposited between two ohmic contacts (source and drain), separated by a thin dielectric layer from a third contact, the gate.<sup>22-25</sup> The gate can be positioned either on the top (top gate) or at the bottom (bottom gate). In some cases, the gate can also serve as the substrate, otherwise, the assembly can be patterned on a substrate (glass, plastic, or silicon).<sup>26-30</sup> A FET provides amplifying and/or switching of electronic signals passing through the semiconducting layer as a response to a certain voltage applied to the gate contact (V<sub>G</sub>).<sup>30, 31</sup> The amount of current that is able to flow between the source and drain—through the active layer—subsequently marks the device's performance in terms of its ability to transport charge carriers. In a such simplistic device architecture, OFETs have then been used as one of the robust ways to extract and benchmark the semiconducting properties of organic materials. These electronic devices have thus been widely

studied to the extent of improving the primitive charge carrier mobilities from  $\sim 10^{-5}$  to higher than tens of cm<sup>2</sup>/Vs.<sup>32-34</sup>

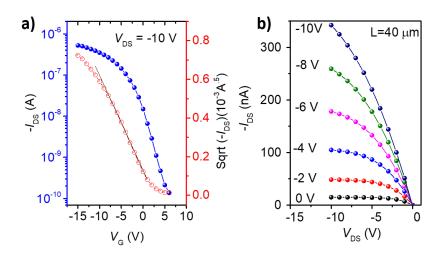

Ordinarily, the transistor performance is tested by analyzing the channel layer's transductance as a response to an applied bias at the gate ( $V_G$ ). By applying another voltage ( $V_{DS}$ ) between source and drain contacts, the performance of the channel layer can be monitored from the current flow through the organic material. Extrapolating transfer and output curves, a few key parameters are usually reported to characterize OFET performance. First, charge carrier mobility ( $\mu$ ), ON/OFF current ratio, as well as the threshold voltage (V<sub>TH</sub>) are to be evaluated. Charge carrier mobility tells how fast the charge carriers can move from one contact to the other, while the ON/OFF ratio shows the difference between currents before the device could be turned "ON" and when the device is switched on. The threshold voltage is an indication of the minimum voltage V<sub>DS</sub> that must be applied before the device can be "turned on". V<sub>TH</sub> is oftentimes reported with its subthreshold slope (SS) which is the voltage difference required to increase the current between source and drain by a factor of ten. Notice the dependence of the threshold voltage on any fabrication defects, since any pinholes or leakages-contact resistance-would have to be energetically filled before the device can turn on. Also note that the organic-based systems borrow these parameters from the inorganic semiconductors that are used as model systems to derive the parameters.<sup>24</sup> The devices architectures, charge transport mechanisms, the intrinsic structure-toproperty dependence have been widely reported and are beyond the scope of this discussion. In the current discussion, we focus on the influence of temperature on electronic performance, more specifically dedicate more effort on high-temperature stability.

#### 1.2 Influence of temperature on charge transport in organic semiconductors

Fundamentally, charge transport in semiconductors is a combination of temperature dependent processes: i) the temperature dependence of the concentration of charge carriers; ii) the activation energy required to excite carriers into higher energy level; iii) temperature-dependent delocalization of carriers; and the iv) temperature-induced lattice expansion and charge scattering.<sup>35</sup> Regardless of the doping level, the intrinsic carrier concentration will increase with increasing temperature. In terms of stability, this increase of carrier concentration is not necessarily detrimental with moderate temperatures. In fact, most semiconductors perform optimally between room temperature and 80°C. In highly crystalline materials, as it is the case for inorganic semiconductors, carrier scattering becomes problematic once the concentrations become too high and charge carrier mobility becomes slower. Charge carrier mobility gradually decreases as the temperature increases due to excessive carrier concentration increases that lead to carriers scattering and ineffective delocalization. This behavior is quasi linear in high performance materials (mostly inorganics) where band transport is the main carrier pathway. As the lattice expands and scattering arises, the performance drops. For lower performance materials, mainly lower crystallinity and "impure" materials, temperature is initially beneficial. This is because in these lightly doped and lower mobility materials, charge transport mechanism typically involves hoping behavior.<sup>36-41</sup> That is, carriers need activation energy to hop between domains. However, this thermally-promoted behavior is only observed with moderate heating. Beyond the optimal range, lattice scattering takes over again, and charge mobilities begin to decline once more.

This behavior becomes of interest not only for fundamental research but also because in real device applications, the increase in temperature typically translates to i) increasing intrinsic carrier density (doping becomes ineffective); ii) exponentially increasing junction leakage current (degrades performance, increases power consumption); iii) increased electromigration in

conductors (lower reliability, shorter lifetime); iv) decreased dielectric breakdown strengths; v) mechanical stress due to coefficient of thermal expansion (CTE) mismatch; and vi) variation in device parameters. These changes are mirrored by the changing transfer characteristics where the transistor device's amplifying abilities begin to decline.<sup>42</sup> Consequently, a lot of efforts are put into insulating and cooling the functional component in integrated circuits to ensure the surrounding temperatures do not elevate beyond optimal ranges. This cooling requirement in most electronics imposes not only a weight burden but also increased manufacturing and maintenance cost. The ideal case to obviate the need for insulation and cooling would be the use of semiconducting materials that are intrinsically thermally resistant. Wide band gap (WBG) materials have been proposed and studied for their thermal stability. With more energy levels to be populated upon temperature increase, materials such as silicon carbides (Si-C) show to maintain much lower carrier concentrations than the ubiquitous silicon.<sup>42-44</sup> In fact, the starting (i.e. room temperature) intrinsic carrier concentration of Si is nearly equivalent to that of 6H-SiC when the latter is studied at 225°C. This thermal tolerance of WBGs has kindled the exploration of carbides and nitrides for high temperature applications.<sup>42</sup> At elevated temperatures, as high as 500°C, doping remains relatively effective in WBGs and signal modulation can still be realized in thermal regimes where the traditional silicon begins to malfunction. However, these materials are still rare, and their crystal growth remains challenging to realize. In addition, these materials tend to be expensive, not to mention heavy. This heavy and brittleness nature makes WBG materials less attractive candidates for technologies such as aerospace engineering. Besides, the use of these highly crystalline would not overcome the bottleneck that is the lattice expansion which leads to decrease in charge carrier mobilities due to scattering.

Organic semiconductors present a special case in the design of high temperature operating electronics. Most organic semiconductors are not highly crystalline in nature which renders charge mobility in these systems thermally favored mostly through the hoping mechanism.<sup>20</sup> In organic transistors, charge carrier mobility, the most common figure of merit for transistor performance evaluation has been shown both theoretically and experimentally to be temperature dependent.<sup>20</sup> Charge transport is mostly affected by structural defects within the organic layer at the interface, the surface topology and polarity of the dielectric, and/or the presence of traps at the interface (that depends on the chemical structure of the gate dielectric surface). Additionally, contact resistance at the source and drain metal/organic interfaces plays an important role. The contact resistance becomes increasingly important when the length of the channel is reduced, and the transistor operates at low fields. In this scenario, any barriers to the injection of carriers from the metal to the channel will easily reflect in the transistor device's performance. Within the device channel, the key parameter that dictates the thermal dependence of transistor performance is the thermally induced disorder which is directly related to the channel resistance. Disorder is commonly described in two different types:<sup>20</sup> i) diagonal disorder which refers to the fluctuations in energy levels of individual molecules witch the materials. This disorder is commonly found in single crystal semiconductors. In less ordered materials such as semiconducting polymers, the ii) offdiagonal disorder is typically observed. It describes the variations in the coupling strengths between adjacent molecules or chain segments in the case of polymers. This type of disordering is commonly contributed by conformational freedom that leads to torsional fluctuations between segments.<sup>20</sup>

Though charge transport in organics shows to benefit from the thermal activation energy, the realization of high temperature operation stability remains challenging in these systems.<sup>45</sup> This

is mainly because with increasing temperature, though the hoping is favored, other factors including lattice expansion and unstable morphology which contribute to the disordering discussed above begin to impede charge carrier transport. For instance, this behavior was found in early studies on thermally sterilizable medical devices by Sekitani et. al.<sup>46</sup>. The authors carried out temperature dependent characterization on pentacene based transistors and showed that the charge transport increases with increasing annealing temperature up to 140°C then declines with further temperature increases. It was found that the morphological changes in the film were the major contributors to the declining performance. The disorder within the crystal-based film lead to ineffective charges delocalization and therefore poor transistor performances. To improve the thermal stability window, the authors further utilized the conjugation extension strategy and made dinaphtho-thiophene (DNTT) as pentacene derivative.<sup>47</sup> They found that DNTT exhibits a much better packing in comparison to pentacene and that this improved ordering could help maintain ordering even after high temperature pasteurization. DNTT based transistor devices thus offered improved thermal stability as well as improved mobilities. To further induce efficient stacking between the DNTT molecules the group introduced phenyl groups to extend the conjugation, improve processability, and thus synthesize DPh-DNTT.<sup>48</sup> With this molecular design, transistor devices that can remain functional after annealing at 250°C could be realized owing to the improved stacking within the crystalline films. In this approach, the use of phenyl pendant groups was found more beneficial than using long alkyl chains. The latter were found to be more prone to disordering at high annealing temperatures as the films packing behavior could be altered by annealing effects. This thermal stabilization approach by inducing better packing was further adopted by other research groups either by introducing "V-shaped" cores<sup>49</sup> and by extending the conjugation using conjugated pendants groups.<sup>50</sup> With these strategies, organic small-molecule

based transistors for medical devices that could survive sterilization temperatures up to 300°C could be fabricated From these series of studies, the following could be learned in quest for high temperature operation: <sup>46, 50-54</sup> i) the thermally promoted transport in organic materials is mainly hampered by unstable morphologies and defects formation at elevated temperature. ii) Improved ordering achievable through molecular design strategies, leading to retain close packing at elevated temperature leads to improved thermally-stability. And iii) large pendant groups which help prohibit molecular rearrangement upon heating can improve the semiconductor's thermal stability. Though the use of these small molecule semiconductors has promised relatively excellent stability at high temperatures, their difficult processability into thin films, complicated device architectures, and limited scope have limited the emergence of these materials as potential candidates for applications. Besides, most of the studies on such devices have merely focused on the effects of annealing and unstable performances remain an issue when in-situ thermal stressing is in effect.<sup>51,</sup> <sup>55</sup> The pursuit of thermally stable and even thermally insensitive material systems remains of great interest to the field as recent theoretical predictions show that by marrying the degree of charge delocalization with the available density of states, a temperature independent charge transport regime is attainable.<sup>36</sup> Though such a behavior has yet to be demonstrated in practice where disorder is more challenging to foresee than in theory, the fundamental understanding and the need for high temperature electronics are still important drivers for this field both towards the design of new semiconductors and the devices demonstrations.

#### 1.3 Influence of temperature on charge transport in conjugated polymer thin films

Semiconducting polymers, commonly in their thin film form exhibit a rather more complex charge transport behavior.<sup>38, 39, 56</sup> Since the mobility extraction involves channels that are several micrometers long and up to a millimeter wide, for the charge carrier to reach the drain contact from

the source, the carriers will not only hop between neighboring polymer chains but will also have to overcome the energy barrier in less ordered domains. It is also to be noted that given the bundlelike nature of polymers, it is nearly inevitable to hit dead-ends for the hopping carriers. In polymer thin films, charge mobility has thus been defined as thermally-activated process due to the inherent required activation energy for charge hopping. At elevated temperatures, similarly to small molecule based thin films, polymer thin films will undergo disordering. As mentioned in sections above, torsional fluctuations in polymer chains are the main source of disordering. This distorting nature is accentuated when enough thermal energy is added into the material systems. The disordering is most likely promoted when the lattice thermally expands, giving the chains enough degree of freedom to disentangle, unfold, and unpack.<sup>57-59</sup> For instance, through in-situ temperature dependent analyses of diketopyrrolopyrrole (DPP)-based donor acceptor polymer thin films, Zhao et al. found that with increasing temperature, the thermal expansion within the  $\pi$ - $\pi$ stacks leads to worsened interchain packing in the polymer films.<sup>57</sup> The crystallographic peak corresponding to the  $\pi$ - $\pi$  stacks showed to decline in intensity concomitant to the thermal expansion. The corresponding transistor devices further exhibited a thermally dependent behavior with increased mobilities up to near 140°C and a decline with further increase in temperature.

This poor morphological and electronic stability in polymers has thus limited the investigation on thermal stress effects on the operation of polymer-based devices. A few strategies including tuning the HOMO energy levels, high temperature pre-annealing, and sidechain engineering have been proposed to enable stability towards annealing temperatures,<sup>45</sup> but no demonstration on high temperature stable operation has been reported despite recent growing interest in polymer-based electronics. Despite the fact polymers are classified amongst the most thermally resistant materials known to date, semiconducting properties have yet to benefit from

such robust nature. We believe this is mainly because most fundamental studies on electronic performance in organics have focused on low temperature regimes. Consequently, both materials design fundamentals as well as organic electronics characterizations have seldomly explored the other end of the spectrum. Though the field of "high temperature electronics" has existed for many years, organic materials have barely taken part in such a discussion in terms of charge transport.

In retrospect, organic materials are mostly understood to be soft in nature. The higher the temperature, typically the softer the polymeric materials, for example, will get. As we mentioned above, this softening has been believed to be detrimental to the electronic performance. However, given the structural tunability offered by polymers, we don't believe that the discussion should be halted simply because the semiconductor softens. We believe there exist several tools to tune such properties either through sidechains and backbone engineering or composites formation without sacrificing the electronic properties of the semiconducting polymers. Since, such approaches have been used to attain ultra-soft and even stretchable semiconductors,<sup>60-65</sup> the same could be said about realizing ultra-rigid counterparts. This dissertation will thus focus on the rigidification approaches for high temperature semiconducting polymers and polymer blends.

#### 1.4 Objectives of this dissertation

In the following chapters, we aim to fully understand the governing factors towards unstable electronic performances in semiconducting polymers and how to mitigate such factors to realize high temperature operation stability. Inspired by the reports on small semiconductors, we will focus on minimizing disorder in polymers as a venue towards high temperature electronic tolerance. To attain the rigidification concept in polymer films, we will explore the use of blend composites. We will discuss the design strategy towards high temperature semiconducting polymer blends through an original approach that utilizes high glass transition temperature host materials. Through a systematic materials selection, we aim to demonstrate that this approach is a simple and generalizable route towards the fabrication of thermally stable organic transistors. We will then demonstrate the ability of our blending design to enable all-plastic transistors devices that are extremely thermally stable. From both the materials design approach and device manufacturing viewpoint, we will highlight how to fabricate transistors that are functional even under baking oven conditions. We will then discuss factors to be considered when designing thermally stable blends including the size of polymers, i.e. the molecular weight, the processing conditions, as well as the selection of the chemical nature of the blending components. After demonstrating the generality of the blending strategy, we will also discuss principles to optimize the electronic performance of the blend films especially by selecting low dielectric rigid materials. We will close our discussion with an outlook on the potential found in polymer-based high temperature electronics both for applications and for fundamental investigation on temperature dependence of charge transport.

### CHAPTER 2. HIGH TEMPERATURE OPERATION IN SEMICONDUCTING POLYMER BLENDS

#### 2.1 Introduction

Although high temperature electronic operation (i.e., beyond 150°C) is of great interest for many applications, it is fundamentally challenging to achieve stable carrier mobilities for semiconductors at elevated temperatures. Applications requiring electronics that can withstand harsh temperatures range from daily appliances (ovens, cellphones, computers, etc), to vehicles, space shuttles, and oil drilling devices. Despite the growing demand for high temperature electronics, both inorganic and organic semiconducting materials have yet to deliver the needed stability. For inorganic semiconductors the performance is typically optimized for operation at ambient temperatures and degrades at elevated temperatures. In these highly crystalline materials, when the operating temperature increase, a lattice expansion accompanied with increased charge carriers concentration results. Charge carriers will be thermally promoted across the band gap, which leads to increased carrier densities, ineffective doping, and junction leakages; the expanding lattice also leads to scattering and reduced charge carrier mobility <sup>42, 66, 67</sup>. To improve the device performance and lifetime in these harsh thermal conditions, wide-band gap materials as well as the use of increased amounts of insulating components have been utilized <sup>43, 44</sup>. For wide band-gap materials (e.g. carbides and nitrides), more energy levels become available which enables the semiconductors to remain functional at much higher temperatures. However, these materials are rare, challenging to process, and their heavy nature limits the scope of their application. Commonly, active or passive cooling, as well as thermally-engineered packaging are needed to maintain the optimal electronic performance <sup>68</sup>, but these approaches impose cost and weight and are thus inefficient for the applications mentioned above.

In contrast, organic semiconductors commonly display thermally-activated charge transport features <sup>69, 70</sup>. Most organic semiconducting materials are not highly crystalline in nature as it is the case for inorganics. This implies that charge transport is facilitated with moderate temperature increases, leading to improved performance <sup>20</sup>. This thermally-promoted behavior is a result of the hoping of charge carriers between ordered domains. With increasing temperature, the charge carrier mobility along with other electronic parameters typically improve. However, this thermally-activated charge transport becomes counteracted by unstable morphologies and disrupted molecular packing at higher temperatures, especially in polymer thin films <sup>52, 57</sup>. For example, it was shown in organic small molecules that, the electronic performance could increase up to 150°C but then the morphology began to vary, the molecular packing started to become weaker, and the electronic performance started to decline. In most reports on small molecule semiconductors, high-temperature annealing effects have been the main focus and a few studies explored the effect of in-situ thermal stress,<sup>46, 51, 53, 55</sup> but in all reports, charge-carrier mobilities have been temperature-dependent and start to decline beyond 150°C. A similar behavior was also observed in conjugated polymer thin films. In-situ temperature dependent crystallography analyses could reveal that the excess thermal expansion results into a complete dissolution of the  $\pi$ - $\pi$  stacks which could be mirrored in decline charge transporting ability.<sup>57</sup> Since organic electronics have shown attractive features such as their low cost processability, flexibility, and in many cases biocompatibility, <sup>71</sup> it is important to explore their potential in the manufacturing of thermal stable electronics.

In this chapter, we will introduce a general strategy to make thermally-stable hightemperature semiconducting polymer blends, composed of interpenetrating semicrystalline conjugated polymers and high glass-transition temperature insulating matrices. We first demonstrate that by physically rigidifying polymer thin films by adding a high Tg matrix, the thermally activated charge transport can be rendered stable at higher temperatures in comparison to the pristine conjugated polymer film. To explain the observed thermal stability, we will look at the effect of blending of film morphology, chain packing and ordering, and utilize computational tools as a guideline. We will also discuss the generality of the blending method by, first utilizing several high Tg matrices to demonstrate high temperature operation, then expanding this design onto other conjugated building blocks, even n-type polymers. We will close the chapter by laying out important aspects towards achieving high temperature operation in semiconducting blends, and by outlining current challenges as well as the potential that is found in these composites.

#### 2.2 Experimental

#### 2.2.1 Materials

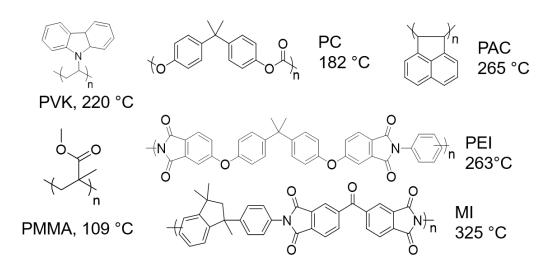

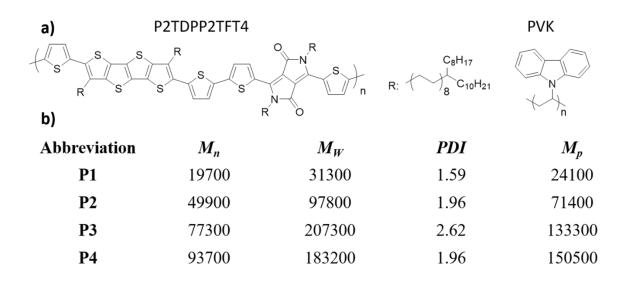

P1, P2, P3 were synthesized and the corresponding molecular weights were evaluated by gel permeation chromatography (GPC) as previously reported.<sup>72-74</sup> Poly(9-vinylcarbazole) (PVK, average Mw 25,000-50,000), polyacenaphthylene (PAC, average Mw 5,000-10,000), and polymethyl methacrylate (PMMA, average Mw 15,000) were purchased from Sigma Aldrich and used as received. Polycarbonate (PC), polyetherimide (PEI), and Matrimid® 5218 (MI) were purchased from PolyK Technologies and purified by precipitation and filtration in methanol before use. All polymer solutions for thin film formation were obtained in chloroform (10 mg/ml) and allowed to stir for 10 hours. The blends were obtained by mixing the appropriate volume percentages for at least 1 hour. Poly(dimethylsiloxane) (PDMS, Sylgard 184, Dow Corning) was prepared at ratio of 10:1 (base/cross-linker, w/w) and cured at 80 °C for 4 hours and used for film delamination. Octadecyltrichlorosilane <sup>75</sup> used for surface modification was purchased from Sigma

Aldrich and used as received. The molecular weight distributions of the studied semiconducting polymers are summarized in Table 2.1 and the glass transition temperatures of the studied matrices are shown in Table 2.2.

Table 2.1 Summarized molecular weight values of the studied semiconducting polymer materials. Low molecular weight extracts were used in this study as they could be easily solution processed into thin films from the blend solutions with the matrices. <sup>a</sup>Trichlorobenzene was used as the eluent at 150 °C.

| Semiconducting<br>Polymer | $M_{\rm n}({\rm kDa})^{\rm a}$ | Ð   |

|---------------------------|--------------------------------|-----|

| DPP-P1                    | 30.7                           | 3.6 |

| DPP-P2                    | 26.5                           | 1.7 |

| Isondigo-P1               | 28.0                           | 4.0 |

Table 2.2. Summarized glass transition temperatures  $(T_g)$  of the studied host matrices and the corresponding molecular weights. <sup>b</sup>Dynamic scanning calorimetry (DSC) scans were taken at 10 °C/min heating/cooling rates. <sup>c</sup>Tetrahydrofuran was used as the eluent at room temperature.

| Matrix Polymer | T <sub>g</sub> (°C) <sup>b</sup> | $M_{\rm n}({\rm kDa})^{ m c}$ |

|----------------|----------------------------------|-------------------------------|

| PVK            | 210                              | 23.7                          |

| PAC            | 265                              | 67.0                          |

| PC             | 182                              | 23.4                          |

| PMMA           | 109                              | 15.0                          |

| PEI            | 263                              | 37.8                          |

| MI             | 325                              | 7.2                           |

#### 2.2.2 Thermal transition measurements

The glass transitions of the studied matrix polymers were verified by dynamic scanning calorimetry (DSC). The DSC thermograms were measured using a TA Q5000 calorimeter. The polymer sample was sealed in a hermetic aluminum pan and measured under nitrogen purge (50 mL / min). The sample was heated and cooled in two cycles between -30 to 400°C (or otherwise as indicated), with the first cycle removing any thermal history of the sample. The heating and cooling rates for all measurements were 10°C / min.

#### 2.2.3 OFET devices fabrication and characterization

A heavily n-doped Si wafer with a 300 nm SiO<sub>2</sub> surface layer (capacitance of 11 nF/cm<sup>2</sup>) was employed as the substrate with Si wafer serving as the gate electrode and SiO<sub>2</sub> as the dielectric. The gold source/drain electrodes were sputtered and patterned by photolithography technique. The device channel width was 1400  $\mu$ m and the channel length was 50  $\mu$ m. For the octadecyltrichlorosilane surface modification, the silicon wafer (with Au bottom contact) was first cleaned with hot piranha solution (H<sub>2</sub>SO<sub>4</sub> (98%):H<sub>2</sub>O<sub>2</sub> (30% water solution) = 7:3) followed by a copious rinsing with water. It was then further subjected to sonication sequentially in water and acetone for 5 minutes each. After drying at 80°C inside an oven, the silicon wafer was then put in a clean and dried Petri dish with a small drop of OTS in the center. The dish was then covered and heated in a vacuum oven at 120°C for 3 hours, resulting in the formation of an OTS self-assembled monolayer on the surface. The OTS-modified substrates were rinsed with hexane, ethanol, and chloroform and blow-dried by nitrogen. During the temperature-dependent analyses, the contribution from the thermal expansion of the substrate was assumed to be negligible for the studied temperature range. The semiconductor layer was deposited on the OTS-treated Si/SiO<sub>2</sub>

substrates by spin-coating with speed of 2000 rpm for 30 seconds. The solvent used is chloroform. The concentrations of the solutions used for spin coating were 10 mg/mL. The devices were annealed in a  $N_2$  glovebox up to 200°C then slowly cooled to 25°C prior to electrical measurements.

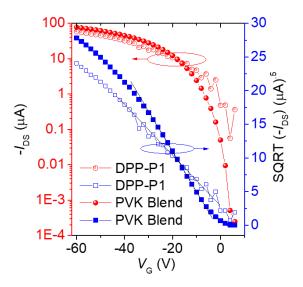

OFET devices characterizations were carried out using a Keithley 4200 both in ambient and under N<sub>2</sub> environment. The field-effect mobility was calculated in the saturation regime by using the equation  $I_{DS} = (WC_i / 2L)\mu(V_G - V_T)^2$ , where  $I_{DS}$  is the drain-source current,  $\mu$  is the fieldeffect mobility, *W* is the channel width, *L* is the channel length, *C*<sub>i</sub> is the capacitance per unit area of the gate dielectric layer,  $V_G$  is the gate voltage, and  $V_T$  is the threshold voltage. OFET performances were obtained by applying a gate bias from -60 V to 6 V, with the potential gradient between the source and drain contacts kept at -60 V. To control the thermal conditions, the HFS600E-PB4 Linkam stage was used, and for the measurement carried under inert environment, the stage chamber was first purged for 10 minutes and hermetically filled with N<sub>2</sub> gas prior to measurement. The heating and cooling rates were maintained at 10°C/ min and OFET devices were allowed to reach thermal equilibrium for 30 minutes at each temperature before measuring.

#### 2.2.4 Morphology analysis

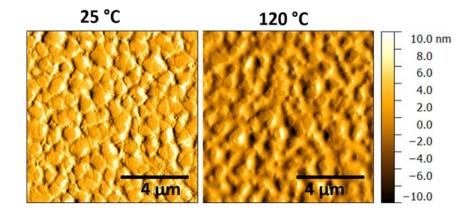

Polymer thin films were spin cast on cleaned and OTS-modified Si/SiO<sub>2</sub> substrates. The film thickness was measured to be around 170 nm when chloroform was used as a solvent. AFM images were taken using Cypher Asylum AFM and processed through Gwyddion Software. For the in-situ temperature dependent morphology study, the films annealed at 50°C for solvent removal were first imaged with the temperature on the sample stage maintained to 25°C. The sample stage temperature was then increased to 120°C (the instrument limitation), and the films were re-imaged for comparison. The same samples were further heated to 220°C in open air and re-imaged.

2.2.5 In-situ temperature-dependent Grazing Incidence X-ray Diffraction (GIXD)

GIXD measurements were performed at the Stanford Synchrotron Radiation Lightsource (SSRL), generated with a 24-pole, 2-Tesla wiggler insertion device. Beamline 11-3 utilizes a beam of energy of 12.7 keV with a 2 x 10<sup>12</sup> photons/s flux. The beam grazed the sample at an incidence angle of 0.12 for 180 seconds, and the resulting diffraction pattern was collected onto a 2D area detector 315 mm away. Lanthanum hexaborate; a polycrystalline material, was used to calibrate the sample-to- detector distance as well as the scattering vector. The beam footprint is 3.0 x 0.15 mm and was shaped with adjustable slit widths. TIFF files were generated at beamline 11-3 and were processed in WxDiff. Prior to collecting any GIXD measurements, the film on Si/SiO<sub>2</sub> substrates was annealed thermally at 200°C in a He atmosphere. The sample was allowed to "equilibrate" at a given temperature for 5 minutes prior to collecting the respective diffraction pattern.

#### 2.2.6 UV-Vis spectroscopy

Samples were prepared by spin casting the chloroform polymer solutions onto cleaned glass substrates. All absorption spectra were collected using a UV/Visible/NIR Cary 3000i spectrophotometer. To compare aggregation behavior between films of pure P1 and its PVK blends, and to probe the effect of temperature on the formed aggregates, all films were annealed to 200°C and slowly cooled down to room temperature inside a N<sub>2</sub> glovebox before each measurement. Insitu absorption spectra were recorded at different temperatures using the HFS600E-PB4 Linkam stage. Each sample was first carefully mounted inside the stage and hermetically encapsulated in the N<sub>2</sub>-purged chamber. The stage was then brought into the light path of the UV/Visible/NIR Cary 3000i spectrophotometer. Prior to each measurement, each sample was allowed to reach

thermal equilibrium for 30 minutes. The HFS600E-PB4 Linkam stage with a clean glass slide hermetically mounted in the chamber was used as the baseline and the background spectra were obtained after heating the blank sample for 10 minutes for each temperature. Temperaturedependent spectra were then obtained with corresponding baseline correction.

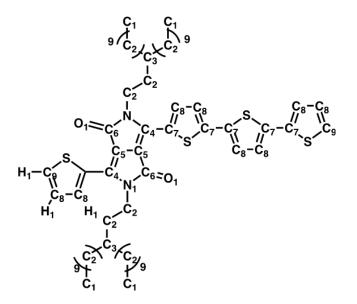

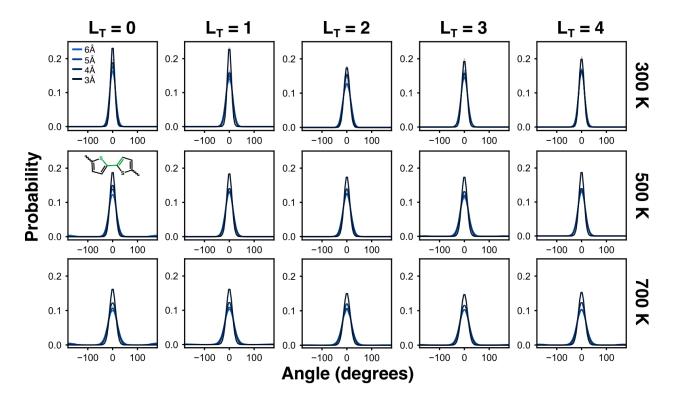

#### 2.2.7 Molecular dynamics (MD) simulations

All simulations were performed on atomistic models of the P1 polymer, using the GAFF force-field to describe bond, angle, dihedral, and Lennard-Jones terms<sup>76</sup>. The partial charges were parameterized based on density function theory (DFT) calculations of the monomer unit with ethyl substituted side-chains. The monomer was geometry optimized at the ωB97X-D/def2-TVZP level of theory<sup>77, 78</sup> and the electrostatic potential was calculated using the CHELPG methodology as implemented in Orca <sup>79</sup>. The partial charges were fit using a least-squares optimization to minimize the deviation between the monopole-based and quantum-chemically calculated electrostatic potential on the surface of the molecule. During the fit, the point charges of identical atom types were constrained to be identical. The partial charges of the side chain carbons were set to achieve charge neutrality based on the number of bonded hydrogens. Improper dihedral terms were added to all three-coordinate atoms to promote planarity using harmonic potentials centered at 0° with a force constant of 100 kcal/mol.

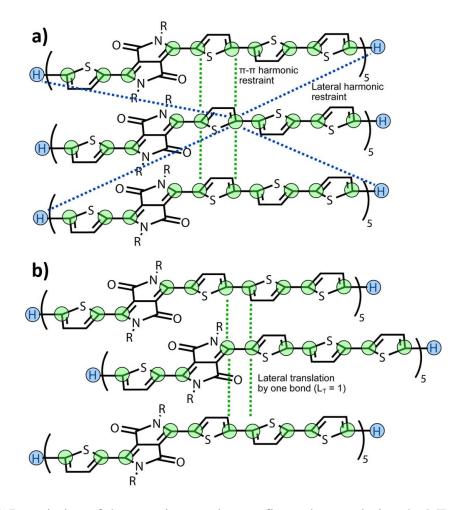

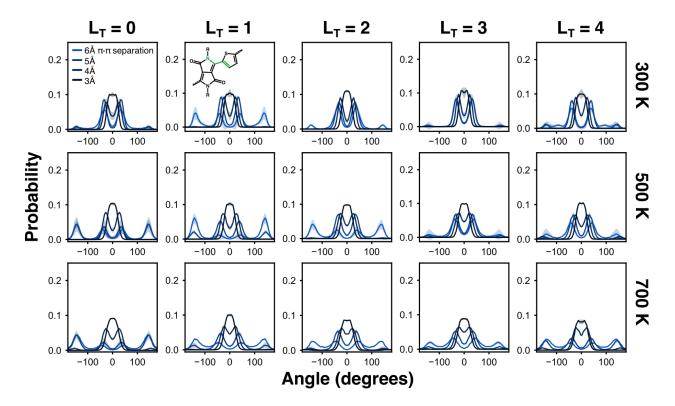

LAMMPS was used to perform the MD simulations <sup>80</sup>. All simulations used a one fs integration timestep and shrink-wrapped conditions. Electrostatics and LJ interactions were truncated at 14 Å. The initial polymer geometry was generated in an extended all-trans configuration for the backbone and side-chains. The dynamics were integrated using the Velocity-Verlet algorithm and temperature was fixed using a Langevin thermostat with 100 fs damping coefficient. The simulations were first relaxed in the NVE ensemble with restrained atomic displacements of 0.01 Å per timestep for 10 ps, followed by 100 ps of further equilibration with the Langevin thermostat and 3 ns of production simulations. To avoid chain-folding and mimic the condensed-phase packing, a harmonic restraint was applied between the terminal hydrogen atoms on each polymer backbone with a 10 kcal/mol force constant and minima corresponding to the displacement of the terminal hydrogen atoms in the initial all-trans structure. All results and errors are reported as the average and standard deviation, respectively, of the reported quantities over five independent trajectories.

The "unconfined" simulations consisted of a pentamer of DPP-P1 (MW of ~5kD) with a single harmonic restraint on the terminal hydrogens as described above. The "confined" simulations consisted of three pentamers of P1 with individual harmonic restraints on the terminal hydrogens as described above. These simulations were initialized to avoid overlaps by aligning a single extended chain so that its long axis and  $\pi$ -system were maximally aligned in the x-y plane, making two replicas of this geometry, then displacing the replicas +/- 10 Å along the z-axis from the original structure. To systematically investigate  $\pi$ - $\pi$  confinement, additional harmonic potentials were applied between subsets of the flexible dihedral atoms in each chain to restrain the chain separations and lateral registration. These restraints were grown during the equilibration phase of the simulations (from a force constant of 0 kcal/mol to 10 kcal/mol) to avoid forming kinetically-trapped structures. The confinement lengthscale in the reported results corresponds to the harmonic minima in the applied restraints. The effect of lateral registry, or slip, between the  $\pi$ stacked chains was also investigated by performing simulations with restraints between subsequent pairs of flexible dihedrals. In all confined simulations the dihedral statistics of the central (confined) chain were calculated and reported. In the main text, the confined simulations correspond to restraints of 3 Å in the  $\pi$ - $\pi$  separation with full lateral registry between the chains. We observe qualitatively identical behavior for the slipped simulations.

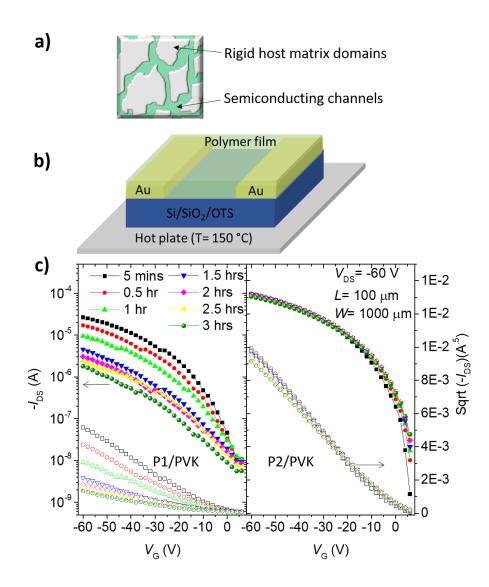

#### 2.3 Thermal stabilization of conjugated polymer thin films by blending

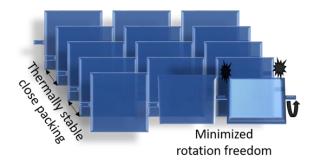

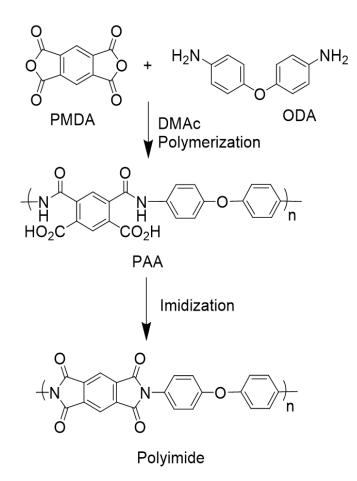

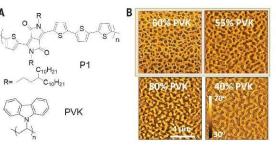

Figure 2.1 Blending strategy to beating the heat. a) Molecular structures of both the semiconducting polymer and the high-Tg insulating host used in the study of high temperature semiconducting polymer blends. b) Design rigid blend morphology where the rigid host domains are mixed with semiconducting crystalline channels to form a thermally robust blend composite. Also show is the transistor device architecture used for temperature dependent electronic measurements.

Blending semiconducting polymers with insulating hosts has been used as a general strategy to improve electronic performance, processability, mechanical and environmental stability in electronic devices. <sup>81-83</sup> Commodity insulating polymers such as poly-styrene (PS), poly-methyl methacrylate (PMMA) are the most commonly used for these purposes. Typically, the blending leads to the accumulation of the conjugated polymer at the interface, a strategy that has been used to improve performance as well as the environmental stability.<sup>84-87</sup> Given the relatively soft nature of these insulator however, these films are still subject to morphological changes. To attain high temperature stability in polymer thin films, preserving close intermolecular

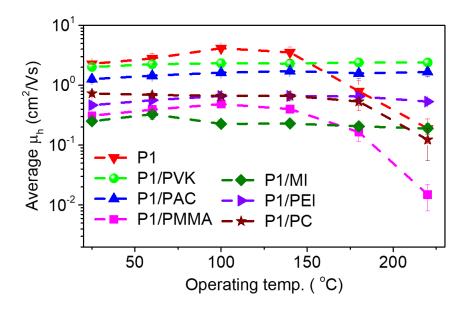

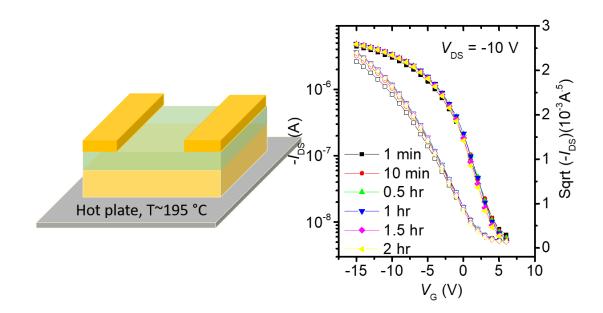

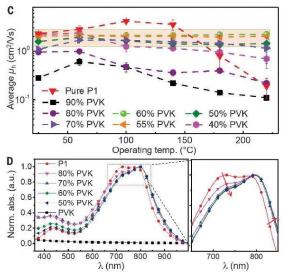

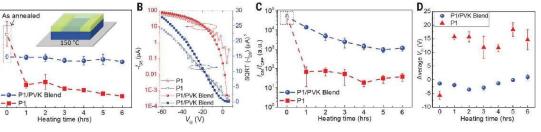

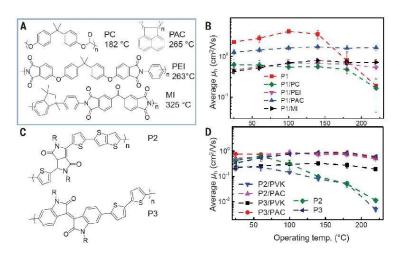

interactions and packing motifs with increasing temperatures is the key challenge.45, 57 In this chapter, we hypothesized that instead of utilizing the common low glass transition temperature matrices, for interpenetrating networks between semicrystalline conjugated polymers and high glass-transition  $(T_g)$  insulating polymer can confine conformational changes of semiconducting polymer chains at elevated temperatures. To test this concept, we first fabricated transistor devices using diketopyrrolopyrrole-thiophene (DPP-P1), a high-performance conjugated polymer, and compared its thermal stability in comparison to its blends with poly(vinyl carbazole) (PVK,  $T_g$ ~220°C) as the high-Tg host (Figure 2.1). We studied blends from 40 to 90 weight percentage (wt%) of PVK in spin-cast films. In situ temperature dependent measurements on fabricated fieldeffect transistors (FETs) under ambient air (Figure 2.2.) and inert conditions (Figure 2.3), revealed that the blends can out-perform the pristine films especially at high temperatures up to 220°C. Figure 2.2 shows the extracted temperature dependent hole mobilities revealing high performance in the blends containing as high as 40 % of the high Tg matrix in elevated temperatures ranges. As expected, the pristine film of DPP-P1 exhibit a thermally favored behavior up to 150°C, but a noticeable gradual decline takes over with increasing temperature. The mobility of the pristine DPP-P1 decreases to 8 % at 220°C. Hole mobilities as high as 2.5 cm<sup>2</sup>/Vs at the blend ratios of 55 to 65 wt % PVK could be attained and remain stable even under extreme temperatures.

Figure 2.2. Temperature dependent hole mobility extracted from FETs with varying blend composition.

Figure 2.3. Temperature dependent hole mobility from representative transistor devices measured under a nitrogen-filled environment.

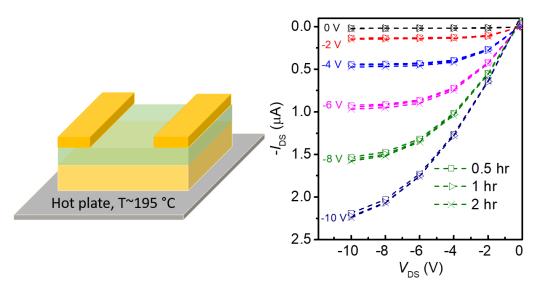

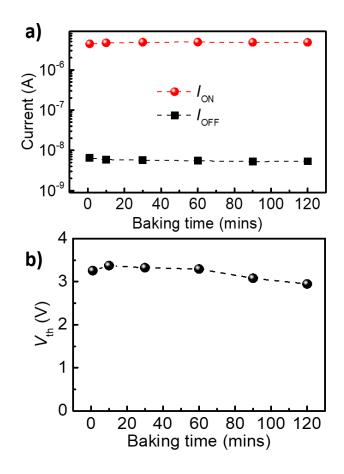

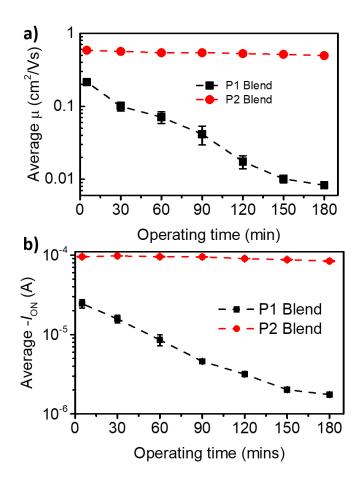

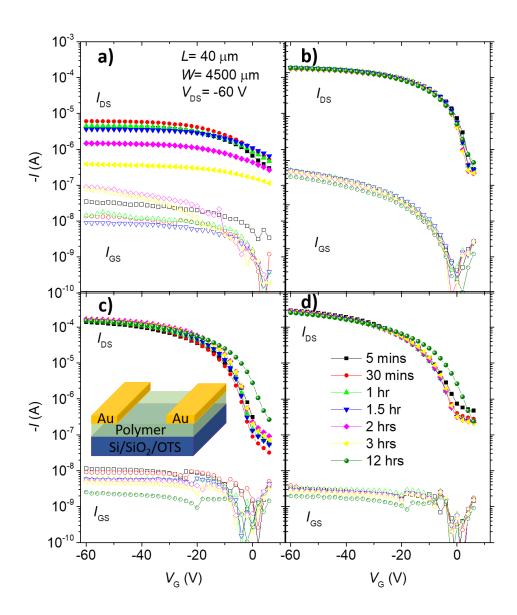

We further subjected the polymer films to constant thermal stress and test their tolerance to heat. We placed the transistor devices on a 150°C hot plate in the opened air and measured the device performance over time. In real life applications, electronic devices for high temperature applications would have to tolerate high temperature stress for prolonged period of times either for data collection or for signal transmission. When the devices based on pristine films of DPP-P1 were brought to contact with the hot surface, the original performance dropped immediately. In contrast, the PVK blend film showed to retain the original performance even after several minutes of baking. As shown in Figure 2.4, the blend films showed to maintain nearly 100 % of the original charge mobility even after 6 hours of constant heating. Other parameters including the ON to OFF current ratio which are typically sensitive to heat could also be maintained stable in the case of the blend. This ability to retain high ON to OFF ratio would determine the lifetime of the electronic devices based on these transistors. As shown in Figure 2.5, stable transfer characteristics are observed in the blend film while the current stability begins to worsen after 1 hour of heating in the pristine film. These unstable currents are typically the main cause of junction leakages, loss of amplification, and increased power consumption in high temperature electronics.<sup>42</sup> The blend films showed excellent thermal tolerance and proved to be excellent candidates for the manufacturing of high temperature organic electronics.

Figure 2.4. Transistor behavior under constant thermal stress. After six hours of thermal stress, stable transistor performance is retained in the blend films.

Figure 2.5. Characteristic transistor curve after 1 hour of thermal stress at 150°C comparing the thermal stability of the studied blend film to the pristine film.

- 2.4 Rationalizing high temperature operation stability in polymer blends

- 2.4.1 Impact of blending on morphology

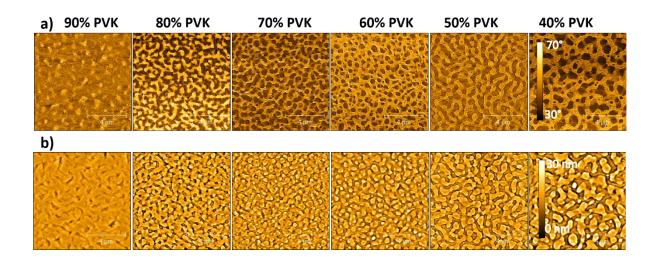

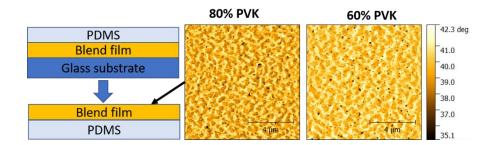

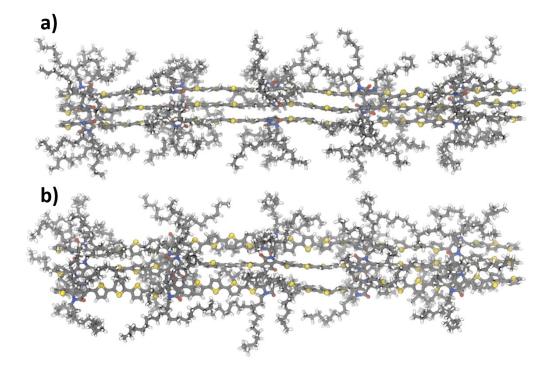

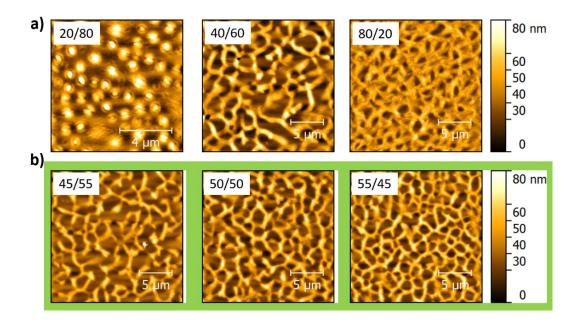

The miscibility between the two blending composites was envisioned to be important for the observed thermal stability. Without the interaction between the components the following would occur: i) either the blend films phase separates vertically or ii) the two polymers form large domains laterally separated. In the first scenario, the transistor performance would be achievable on one interface, but the blend would behave similarly to the pristine film. The latter scenario would lead to poor charge transfer since the domain isolation would prevent efficient hoping of the carrier in the transistor devices. We then characterized the blend morphology to not only visualize the degree on miscibility in our films, but to also understand why only a narrow blending percentage shows excellent stability in comparison to others. The AFM height images revealed that the conjugated polymer formed nanoscale domains that showed to increase in connectivity with increase semiconductor amount, and plateau around 55% of the semiconductor added (Figure 2.6). We then delaminated the film and imaged the bottom interface to find that interconnectivity nature persists on both sides of the thin film as shown in the AFM images in Figure 2.7. We could thus conclude that in our blends, we do not have a complete vertical nor a large lateral phase in accordance to the efficient electronic performance observed in the transistor devices. The two components form an interpenetrating network of the semiconducting domains surrounded by the insulating matrix. This close housing of the semiconducting domains by the rigid insulator could thus explain the observed thermal stability.

Figure 2.6. Morphology evolution with varying content of the insulating matrix. With optimal blending ratio, interpenetrating network of the crystalline conjugated polymer domains is formed surrounded by the host matrix.

Figure 2.7. Morphology of the bottom interface revealing interconnected domains of the conjugated polymer analogous the top face morphology.

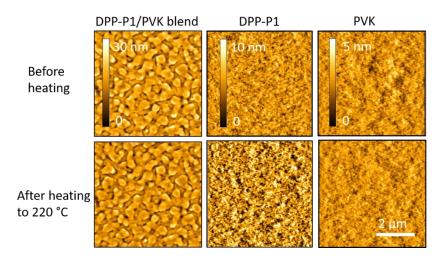

To probe the impact of temperature on the formed morphology, we subjected the blend films to extreme heat (220°C) and monitored any morphological changes in comparison to the pristine DPP-P1 film. The AFM height images revealed that the blend film morphology remains unchanged even after thermal treatment near the Tg of the matrix for 1 hour (Figure 2.8). The pristine conjugated polymer film treated in the same conditions exhibited detectable variations in the domains' sizes. This thermal robustness of the blend morphology could thus support the stable performance observed in transistor devices. This robustness was observed for the pristine PVK film. When heated 220°C, the matrix itself also revealed a stable morphology indicative of an excellent candidate as a rigid host in the blend film. Up to this point, it was understood that the matrix polymer brings the overall rigidity to the film while the semiconductor provides the electronic properties. The embrace of the two features in a mixed manner yields thermally stable electronic performance in transistor devices.

Figure 2.8. Effect of thermal stressing on thin film morphology. The blend film as well as the pristine matrix film show no changes after heating while the pristine conjugated polymer film reveals slight changes in the domain sizes.

## 2.4.2 Impact of blending on ordering and packing

To further understand the origin of the blending-induced thermal stability, we also carried out a series of studies on parameters that would impact the charge transport besides the microscale morphology. We wanted to probe the effect of blending on the semiconducting polymer especially in terms of ordering, a key feature towards improved electronic behavior. As suggested from the morphology analysis, the blending induces the aggregation of the conjugated polymer domains into a network of crystalline domains that are confined by the matrix polymer. At this stage we understand that the interconnectivity is key to reaching efficient charge delocalization within the blend films and that the confinement by the rigid host is the contributor to the stable morphology at high temperature, hence the stable charge transport in harsh thermal environments. We are however interested in probing the thermal stabilization much deeper especially within the conjugated polymer domains. We predicted that the absorption profiles as well as the crystallographic features of the DPP polymer chains would reveal the impact of blending on their ordering behavior both with and without the thermal stress.

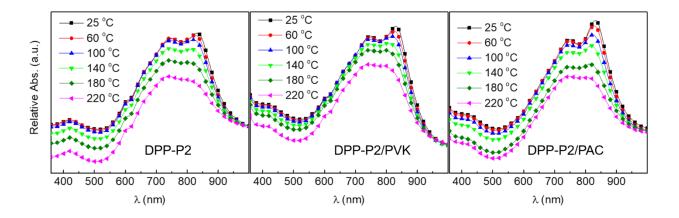

## 2.4.2.1 UV-Vis spectroscopy

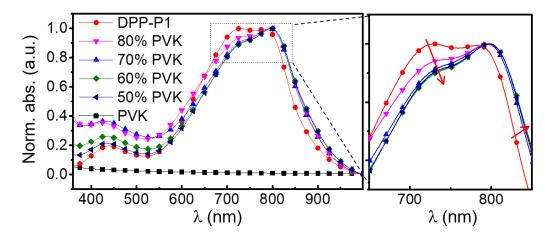

Since the blend formation showed to yield films morphologies drastically different from that of the pristine conjugated polymer films, we examined the UV-Vis absorption spectra and their relevant signatures on the observed thermal stability for the blend films. Figure 2.9 shows normalized absorption spectra of the blend films with varying blend content. In the presence of PVK we observe the following: 1) a slight red-shift in the absorption spectrum indicative of induced aggregation as revealed by the AFM images. 2) An increase in the 0-0 vibronic peak intensities signature of improved chain planarization and interchain stacking. Both features showed to not benefit significantly from further increase in the amount of the semiconductor beyond 40 % which suggested that there exists a threshold blend ratio at which the morphology is optimized. The first feature was not surprising since from the AFM images we observe the formation of DPP-P1 aggregates into a network which would explain the observed red-shifting in the spectra. This behavior is also common in other blending systems that use insulating matrices.<sup>84-</sup> <sup>87</sup> Furthermore, the red-shift showed to plateau, just as the domain connectivity showed to begin to disrupt beyond 50 % of the fully conjugated polymer present. The second feature was less obvious from the morphology results. From the aggregation behavior, we would expect that the semiconducting polymer chains would form bundle inside the aggregates. Instead, we observe that the presence of PVK leads to a disentanglement of the DPP-P1 chains and improves their ordering. According to previous works on signature absorption spectra in polymer films, the increase in the 0-0/0-1 vibronic peak ratio is indicative of chain planarization and improved stacking.<sup>88</sup> This feature will greatly benefit the efficient charge transport in our blends especially since we have a minority percentage of the semiconductor.<sup>85, 88, 89</sup> Coincidently to the electronic measurement results, both these features showed to be optimal for the blend ratios that revealed both high performance as well as excellent thermal stability.

Figure 2.9. Effect of blending on ordering. Normalized absorption spectra from DPP-p1 films when blended with different contents of PVK.

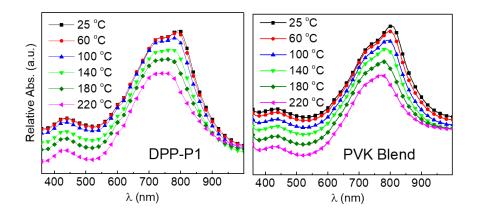

Given the hinted blending-induced ordering, we further carried out in-situ temperature dependent UV-Vis measurements to probe the blend stability. The annealed films on glass substrates were subjected to temperature increase and monitored were the changes in the signature vibronic peaks comparing the blend film (60 % PVK as a representative) to the pristine DPP-P1 film. For DPP-P1 films, the vibronic peaks showed to both blue-shift and decrease in intensity with increasing temperature (Figure 2.10). At 220°C, the maximum absorption peak that is associated to the inter-chain stacking was no longer detectable. This indicates that the ordering was nearly lost in the pristine film at such high temperature in accordance to previous reports.<sup>57</sup> In contrast, the blend film which began with much improved ordering between polymer chains, relatively higher ordering could be retained at all temperatures. At 220°C the strong 0-0 vibronic peak could still be observed as evidence of persistent ordering in the blends. This observation came to support the stable morphology as well as the stable electronic performance that we discussed in sections above. From these in-situ studies we could thus gain a better understanding on the role played by the blending approach: the insulator induces molecular ordering in the aggregated domains, rigidifies the microscale morphology, and thus minimizes disordering with increasing temperatures. UV-Vis absorptions which captures a large sample scale while accounting for both the crystalline and amorphous domains within the film was a great indicator of this thermal stabilization. To compliment these results, we further probed the crystalline domains of the conjugated polymer using x-ray crystallography.

Figure 2.10. Temperature dependent absorption spectra of the pristine DPP-P1 film compared to the blend film containing 60 % of PVK.

### 2.4.2.2 X-ray crystallography

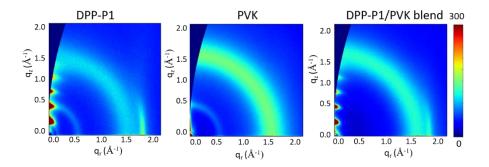

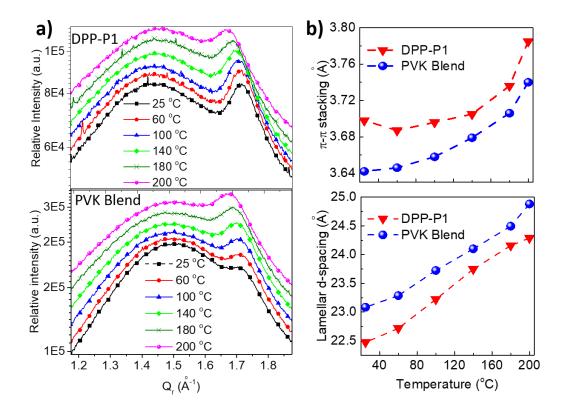

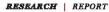

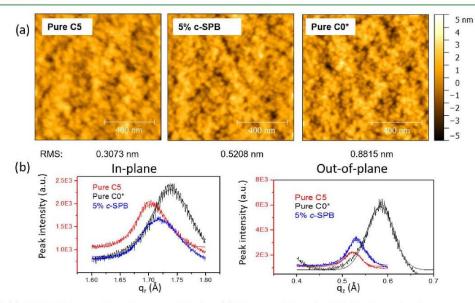

Since charge transfer processes in polymer films are understood to occur both along the polymer backbone and between the crystalline domains, we wanted to gain further insights on the influence of blending on crystallization of our conjugated polymer and the resulting thermal tolerance. We thus performed in-situ temperature-dependent x-ray diffraction studies on the pristine polymer and compared the DPP-P1 behavior to that of the corresponding PVK blend (Figure 2.11 and 2.12). As hinted by the UV-Vis absorption spectra and morphology results, we observed that the blending induced an improved packing for the DPP-P1 domains leading to closer  $\pi$ - $\pi$  stacking distances (Figure 2.12). Upon blending the  $\pi$ - $\pi$  packing distance shortened from 3.70 Å to 3.63 Å. This shortening could be explained by the observed ordering, planarization, and aggregation discussed above. The temperature-dependent results revealed that this improved

packing also persists when the diffraction patterns are collected up to 200°C. In agreement with the induced ordering observed from the absorption spectra, the crystalline domains of the blend films show to remain ordered at all studied temperatures. With the increase in heat, the lattice shows to expand, but in the blend films the expansion proved to be much slower than that of the pristine DPP-P1 film. At 200°C, the blend film could retain the inter-chain  $\pi$ - $\pi$  stacking distances of around 3.73 Å while the pristine DPP-P1 film showed to expand up to 3.8 Å (Figure 2.12). This efficient stacking at elevated temperatures could thus support the observed high performance in the transistor devices and supports why the blend films showed to outperform the pristine ones at elevated temperatures.

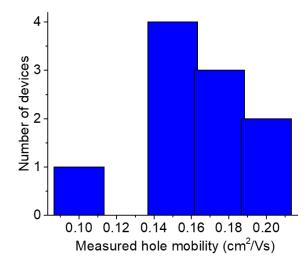

Figure 2.11. Diffraction patterns of DPP-P1 and corresponding PVK blend. The blend shows to inherit the  $\pi$ - $\pi$  stacking nature of the conjugated polymer while retaining the amorphous domains of the insulator.