## ACCELERATING PARALLEL TASKS BY OPTIMIZING GPU HARDWARE RESOURCE UTILIZATION

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Tsung Tai Yeh

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Timony R. Rogers, Chair School of Computer and Engineering

Dr. Rudolf Eigenmann School of School of Computer and Engineering

Dr. Samuel P. Midkiff School of School of Computer and Engineering

Dr. T. N. Vijaykumar

School of School of Computer and Engineering

## Approved by:

Dr. Timony R. Rogers

Head of the School Graduate Program

#### ACKNOWLEDGMENTS

I feel so grateful that I have had such a great opportunity over the past eight years to conduct my research work and turn it into my Ph.D. dissertation. I have to admit the path to the Ph.D. was full of challenges. Without the help of many people including my advisor, colleagues, friends, and family, this dream would never come true.

First, I want to appreciate each member of my dissertation committee that continuously cultivate me research skills and courage as I begin my graduate student life. Timothy G. Rogers, my Ph.D. advisor, demonstrates the value of seeking the root-cause of research problems and focusing intensely on pursuing solutions. Rudolf Eigenmann embodies professional effectiveness that inspires me to convey the research work succinctly and effectively. Samuel Midkiff and T. N. Vijaykumar are my role model for how to be a wonderful mentor to young graduate students.

I would also like to thank the colleagues who directly helped me on my research projects and life. They are all talented, hardworking and generous to share their ideas and thoughts. Their kindly sharing always scatters me the light when I was trapped by some difficulties. Here is everyone listed in alphabetical order: Roland Green, Akshay Jain, Mahmoud Khairy, Amit Sabne, Putt Sakdhnagool, and Mengchi Zhang.

I am also deeply appreciative of my internship supervisors at AMD research, Bradford M. Beckmann and Matt Sinclair. I feel so fortunate to have such wonderful mentors to give me guidance on designing practical micro-architectures. Their great jobs enrich my internship life and broaden my knowledge on the GPU architecture design. Larry Bihel was my supervisor at research computing center, Purdue University. I cherish his patience to direct me to understand insights of remote-sensing image analysis. My work would not nearly be meaningful without unwavering supports from my friends and family. Thank for their accompany to help me go through this adventure.

## TABLE OF CONTENTS

|    |                                                                  |        | Page                                                                                                              |  |  |

|----|------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------|--|--|

| LI | ST O                                                             | F TAB  | LES                                                                                                               |  |  |

| LI | ST O                                                             | F FIGU | JRES $\ldots \ldots x$ |  |  |

| AI | BSTR                                                             | ACT    |                                                                                                                   |  |  |

| 1  | INT                                                              | RODU   | CTION 1                                                                                                           |  |  |

|    | 1.1                                                              | GPU    | Underutilization on Latency-sensitive Applications                                                                |  |  |

|    |                                                                  | 1.1.1  | Narrow Task                                                                                                       |  |  |

|    |                                                                  | 1.1.2  | Prior Work to Overcome GPU Underutilization 3                                                                     |  |  |

|    |                                                                  | 1.1.3  | Challenges in Designing a GPU Runtime System for Narrow Tasks $4$                                                 |  |  |

|    |                                                                  | 1.1.4  | Pagoda GPU Runtime System for Narrow Tasks                                                                        |  |  |

|    | 1.2 Latency-sensitive GPU Applications with Deadline Constraints |        |                                                                                                                   |  |  |

|    |                                                                  | 1.2.1  | Constraints of GPUs on Latency-sensitive Applications 6                                                           |  |  |

|    |                                                                  | 1.2.2  | Prior Work to Improve QoS of Latency-sensitive GPU Applications $8$                                               |  |  |

|    |                                                                  | 1.2.3  | LAX: Laxity-aware GPU Job Scheduler                                                                               |  |  |

|    | 1.3                                                              | Redun  | adancy on GPU SIMT Instructions                                                                                   |  |  |

|    |                                                                  | 1.3.1  | Threadblock-wide Redundancy on GPU SIMT Instructions 14                                                           |  |  |

|    |                                                                  | 1.3.2  | Previous Work on Removing GPU SIMT Redundant Instructions 15                                                      |  |  |

|    |                                                                  | 1.3.3  | Challenges on Eliminating GPU SIMT Redundant Instructions . $16$                                                  |  |  |

|    |                                                                  | 1.3.4  | DARSIE GPU SIMT Redundant Instruction Skipper $\ . \ . \ . \ . \ 16$                                              |  |  |

|    | 1.4                                                              | Contri | butions of This Thesis                                                                                            |  |  |

|    | 1.5                                                              | Thesis | Overview                                                                                                          |  |  |

| 2  | BAC                                                              | CKGRO  | UND and RELATED WORK                                                                                              |  |  |

|    | 2.1                                                              | GPU .  | Architecture and Programming                                                                                      |  |  |

|    | 2.2                                                              | GPU I  | Micro-architectural Model                                                                                         |  |  |

|    | 2.3                                                              | Proces | ssing Narrow Tasks on Domain-specific Accelerators                                                                |  |  |

## Page

|   |     | 2.3.1   | Static Software Approaches                              | 23 |

|---|-----|---------|---------------------------------------------------------|----|

|   |     | 2.3.2   | Dynamic Runtime Solutions                               | 24 |

|   |     | 2.3.3   | Preemptive Hardware Scheduler and Virtualization        | 25 |

|   | 2.4 | Impro   | ving Application Latency on Accelerators                | 25 |

|   |     | 2.4.1   | QoS-Aware Scheduling Policies                           | 26 |

|   |     | 2.4.2   | Real-Time Scheduling                                    | 26 |

|   | 2.5 | Solutio | ons on the GPU Redundancy Removal                       | 27 |

|   |     | 2.5.1   | Hardware Redundant Instruction Skipper                  | 27 |

|   |     | 2.5.2   | Compiler-Assisted Approaches                            | 28 |

| 3 | LAT | ENCY-   | SENSITIVE GPU APPLICATIONS                              | 29 |

|   | 3.1 | Applic  | eations                                                 | 29 |

|   |     | 3.1.1   | Recurrent Neural Networks                               | 29 |

|   |     | 3.1.2   | Network Packet Processing                               | 30 |

|   |     | 3.1.3   | Intelligent Personal Assistants                         | 30 |

|   | 3.2 | Small   | Data-Parallel Kernels on Latency-sensitive Applications | 30 |

|   | 3.3 | Impac   | t of Job Arrival Rate                                   | 31 |

|   | 3.4 | Proble  | ems of Mixed Task and Data Parallel Applications        | 33 |

| 4 | ΑT  | AXONO   | OMY OF GPU REDUNDANCY                                   | 35 |

| 5 |     |         | FINE-GRAINED GPU RESOURCE VIRTUALIZATION FOR TASKS      | 30 |

|   | 5.1 |         | a Programming APIs                                      |    |

|   | 5.2 |         | a Runtime System                                        |    |

|   | 0.2 | 5.2.1   | GPU Resource Virtualization                             |    |

|   |     | 5.2.2   | Continuous Task Spawning                                |    |

|   |     | 5.2.3   | Concurrent Task Scheduling                              |    |

|   | 5.3 |         | rting Native CUDA Functionality                         |    |

|   | 0.0 | 5.3.1   | Shared Memory Management                                |    |

|   |     | 5.3.1   | Sub-Thread Block Synchronization                        |    |

|   |     | 0.0.2   |                                                         | 94 |

|                 |     |         |                                                      | Page |

|-----------------|-----|---------|------------------------------------------------------|------|

|                 | 5.4 | Evalua  | ation                                                | . 54 |

|                 |     | 5.4.1   | Experimental Setup                                   | . 54 |

|                 |     | 5.4.2   | Runtime Performance                                  | . 55 |

|                 |     | 5.4.3   | Pagoda Performance Scalability                       | . 58 |

|                 |     | 5.4.4   | Sensivity Analysis for Task Load Imbalance           | . 59 |

|                 |     | 5.4.5   | Task Latency Analysis                                | . 61 |

|                 |     | 5.4.6   | Lock Step Communication Overhead                     | . 61 |

|                 |     | 5.4.7   | Pagoda Task Scheduling Overlead Analysis             | . 62 |

|                 |     | 5.4.8   | Pagoda Shared Memory Analysis                        | . 64 |

|                 | 5.5 | Summ    | ary                                                  | . 65 |

| 6               | LAX | C: DEA  | DLINE-AWARE JOB SCHEDULING ON THE GPU                | . 66 |

|                 | 6.1 | LAX     | System Overview                                      | . 66 |

|                 | 6.2 | Job R   | emaining and Laxity Time Estimates                   | . 67 |

|                 | 6.3 | Preve   | nting Oversubscription with Queuing Delay Estimation | . 70 |

|                 | 6.4 | Laxity  | -Aware Job Scheduling Algorithm                      | . 70 |

| 6.5 Methodology |     | odology | . 71                                                 |      |

|                 |     | 6.5.1   | Evaluated Compute Queue Scheduling Policies          | . 72 |

|                 |     | 6.5.2   | Benchmarks                                           | . 74 |

|                 |     | 6.5.3   | Job Arrival Rate                                     | . 75 |

|                 | 6.6 | Exper   | imental Results                                      | . 75 |

|                 |     | 6.6.1   | Completing Jobs by Their Deadlines                   | . 76 |

|                 |     | 6.6.2   | Scheduling Effectiveness                             | . 82 |

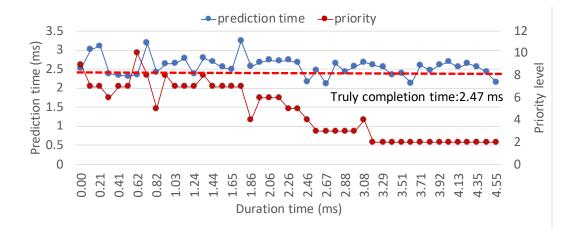

|                 |     | 6.6.3   | Execution Time Prediction and Priority Over Time     | . 83 |

|                 |     | 6.6.4   | Energy Consumption                                   | . 85 |

|                 |     | 6.6.5   | Throughput and 99-percentile Tail Latency            | . 85 |

|                 | 6.7 | Summ    | ary                                                  | . 86 |

| 7               |     |         | IMENSIONALITY-AWARE REDUNDANT SIMT INSTRUC-          | . 87 |

viii

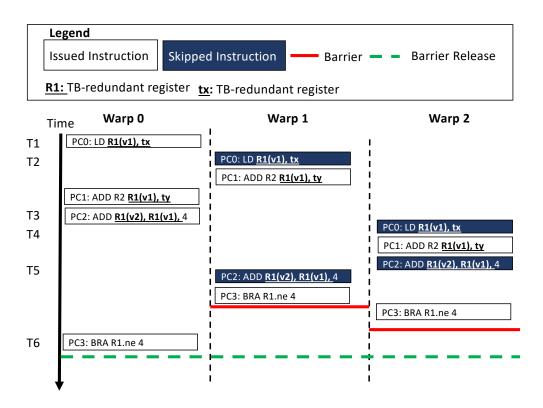

|    | 7.1  | High I | Level Operation                              |

|----|------|--------|----------------------------------------------|

|    | 7.2  | Comp   | iler Annotations                             |

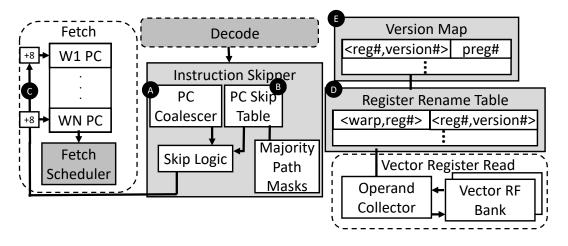

|    | 7.3  | DARS   | IE microarchitecture                         |

|    |      | 7.3.1  | Remapping Registers                          |

|    |      | 7.3.2  | PC Skip Table                                |

|    |      | 7.3.3  | Achieving the Illusion of Lockstep Execution |

|    |      | 7.3.4  | PC Coalescer                                 |

|    |      | 7.3.5  | Instruction Skipping Flow                    |

|    | 7.4  | Skippi | ng Load Instructions                         |

|    | 7.5  | Handl  | ing SIMD Divergence                          |

|    | 7.6  | Metho  | odology                                      |

|    | 7.7  | Exper  | imental Results                              |

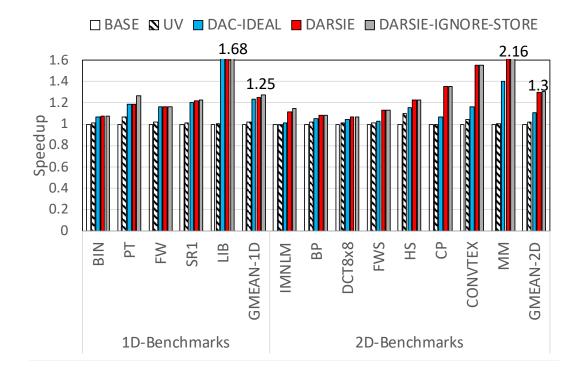

|    |      | 7.7.1  | Performance and Energy 101                   |

|    |      | 7.7.2  | Saving Memory Bandwidth 105                  |

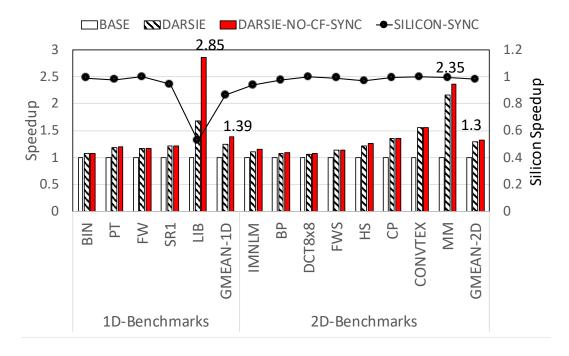

|    |      | 7.7.3  | Effect of Synchronization                    |

|    |      | 7.7.4  | Area Estimation                              |

|    | 7.8  | Summ   | ary                                          |

| 8  | CON  | ICLUSI | ION AND FUTURE WORK 110                      |

|    | 8.1  | GPU '  | Virtualization on the Cloud                  |

|    | 8.2  | Memo   | ry Model for GPU Concurrency                 |

| RI | EFER | ENCES  | S                                            |

## LIST OF TABLES

| Tab | le                                                                                                                                                                                                                                                                                        | Page |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1 | Summary of kernels in latency-sensitive benchmarks                                                                                                                                                                                                                                        | . 31 |

| 5.1 | Pagoda Programming API                                                                                                                                                                                                                                                                    | . 40 |

| 5.2 | WarpTable entry fields                                                                                                                                                                                                                                                                    | . 47 |

| 5.3 | Benchmark Description                                                                                                                                                                                                                                                                     | . 56 |

| 5.4 | Benchmark Characteristics                                                                                                                                                                                                                                                                 | . 57 |

| 5.5 | Compute performance comparison of tasks run in Pagoda with and with-<br>out shared memory allocation: Each version runs 32K tasks. DCT tasks<br>have 64 threads, MM tasks contain 256 threads. Only the compute time<br>is compared. The shared memory usage offers considerable benefits | . 64 |

| 6.1 | Key simulated system parameters                                                                                                                                                                                                                                                           | . 71 |

| 6.2 | Scheduling Policies                                                                                                                                                                                                                                                                       | . 73 |

| 6.3 | LAX Benchmarks                                                                                                                                                                                                                                                                            | . 74 |

| 6.4 | Energy rate (consumed energy over the number of successful jobs) (mJ))                                                                                                                                                                                                                    | . 84 |

| 6.5 | The Successful Job Throughput (the number of successful jobs per second                                                                                                                                                                                                                   | ) 85 |

| 6.6 | 99-percentile job latency(millisecond))                                                                                                                                                                                                                                                   | . 86 |

| 7.1 | Applications studied                                                                                                                                                                                                                                                                      | . 99 |

| 7.2 | Baseline GPU                                                                                                                                                                                                                                                                              | 100  |

## LIST OF FIGURES

| Figu | Ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Pa | ıge |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

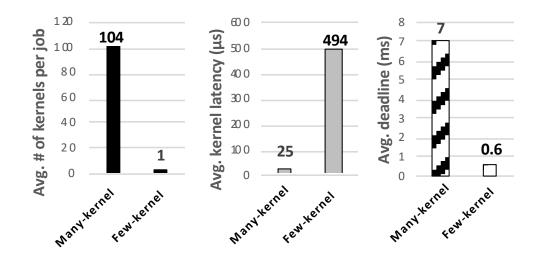

| 1.1  | Characteristics of many-kernel latency-sensitive jobs versus few-kernel latency-sensitive jobs, listed in Table 6.3                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6   |

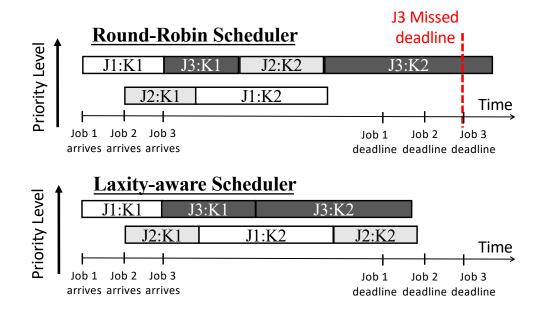

| 1.2  | Comparison of Round Robin and Laxity-aware Schedulers for a GPU that can simultaneously execute 2 jobs                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 9   |

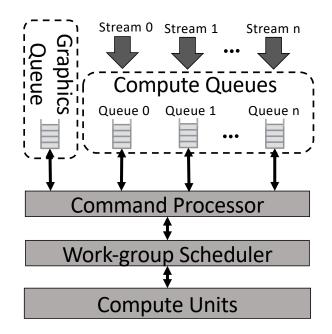

| 1.3  | GPU Queue Scheduler Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •  | 10  |

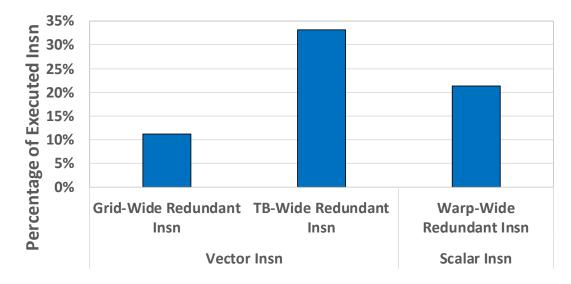

| 1.4  | Redundant instructions in each GPU thread grouping level across different applications                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 13  |

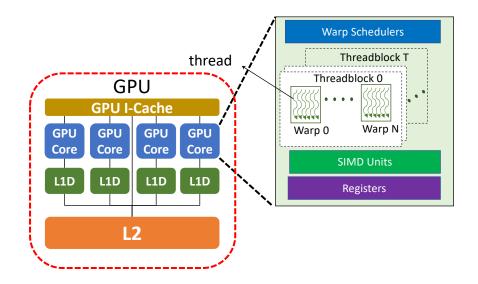

| 2.1  | GPU Architecture: The number of GPU cores is dependant with different GPU generations and the scratchpad cache is shared with L1D cache                                                                                                                                                                                                                                                                                                                                                                                  |    | 20  |

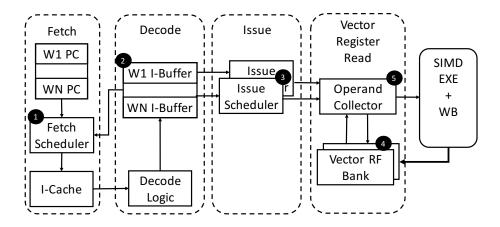

| 2.2  | GPU micro-architectural model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 22  |

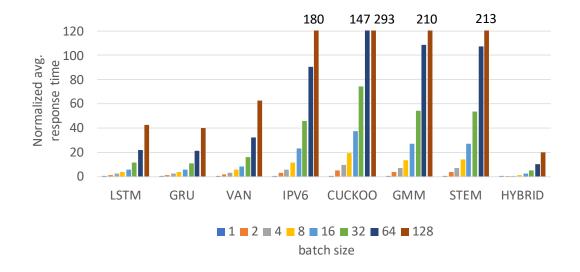

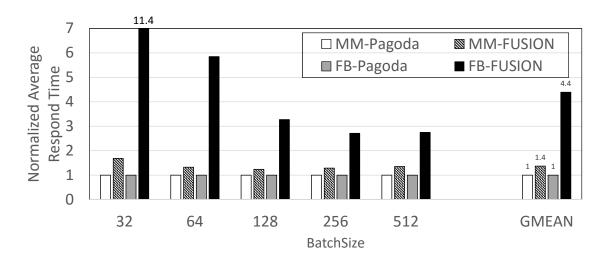

| 3.1  | Comparing response times with varying job arrival rates, normalized to batch size 1                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 32  |

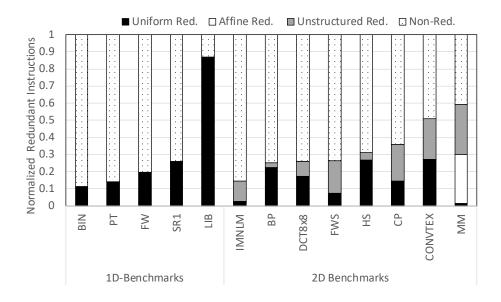

| 4.1  | Fraction of dynamically executed TB-redundant instructions. Instructions executed in diverged control flow are considered non-redundant                                                                                                                                                                                                                                                                                                                                                                                  |    | 36  |

| 4.2  | Pseudo-assembly code to read from an integer array with a base address<br>of 10 using tid.x as the index with 1D and 2D TBs. Values in output<br>registers for each instruction are classified based on the pattern they make<br>across the TB. 1D TBs create affine values that are not redundant, while<br>2D TBs create both affine and unstructured redundant values                                                                                                                                                 |    | 37  |

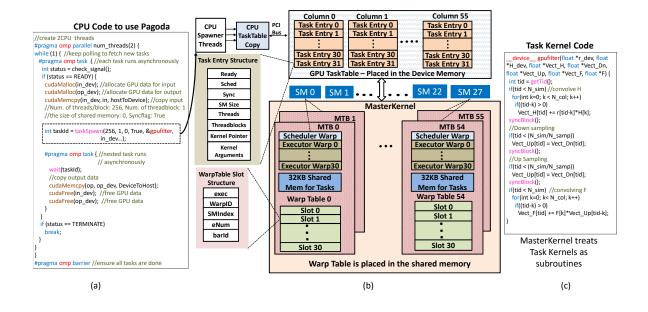

| 5.1  | Pagoda runtime system overview: The source task kernel and CPU code re-<br>quire few changes to an equivalent CUDA code. The MasterKernel design<br>is shown for Nvidia Pascal Titan X GPU. The 56 MasterKernel thread-<br>blocks (MTBs) have 1024 threads each. TaskTable is mirrored on both the<br>CPU and GPU. The CPU threads spawn tasks into the CPU TaskTable,<br>which are then sent to the GPU counterpart. Scheduler warps inside each<br>MTB find free executor warps to launch tasks on. The WarpTable per- |    |     |

|      | forms bookkeeping for each executor warp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 42  |

| XI |  |

|----|--|

|    |  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

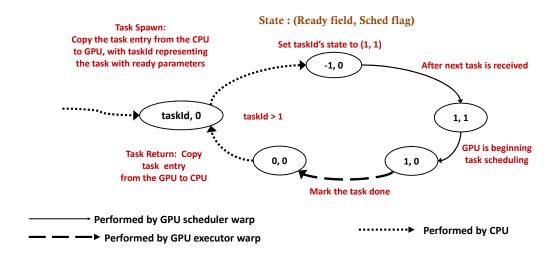

| 5.2  | TaskTable State Diagram : The CPU only touches TaskTable entries with reset <i>ready</i> fields, when a task gets scheduled to warps. and the GPU only touches TaskTable entries with non-zero <i>ready</i> fields, allowing for simultaneous TaskTable updates from the CPU and GPU. The <i>sched</i> flag determines when the task gets scheduled on GPU warps                                                                                                       | . 44 |

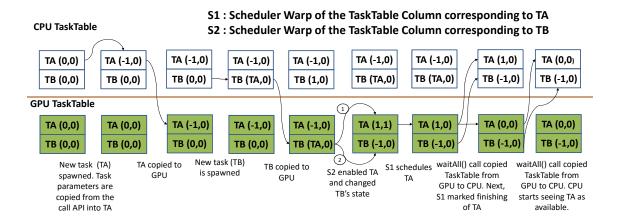

| 5.3  | Example execution of task TA : TA gets scheduled only after TB is spawned. Our design allows for the CPU and GPU TaskTable entries to contain mis-matching values                                                                                                                                                                                                                                                                                                      | . 45 |

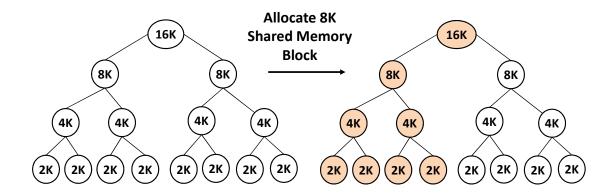

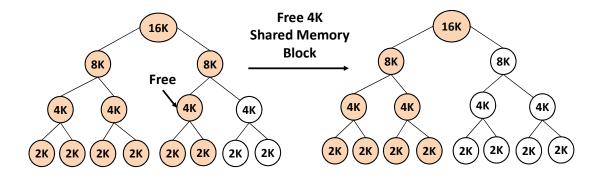

| 5.4  | Allocating 8K of shared memory in Pagoda: The value in each node represents the size of the shared memory block. Note that not all levels of the tree are shown here. The white nodes are free blocks and the shaded nodes are allocated blocks.                                                                                                                                                                                                                       | . 52 |

| 5.5  | Deallocating 4K of shared memory in Pagoda: Ancestors of the current node are marked free only if the sibling is free                                                                                                                                                                                                                                                                                                                                                  | . 53 |

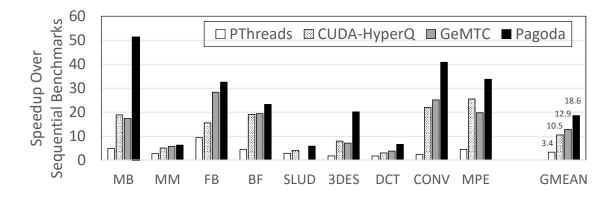

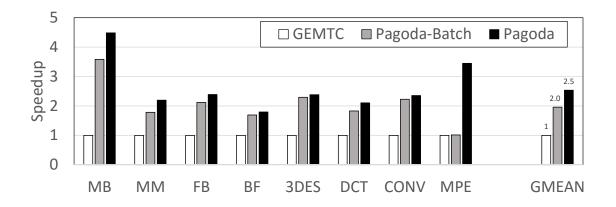

| 5.6  | Overall Performance Comparison: All applications of this experiment<br>were run on Nvidia Pascal GPU. The number of tasks in each benchmark<br>is constant (32K), except SLUD, which contains 273K tasks. Each GPU<br>task uses 128 threads. The measurement of execution time contains both<br>data copy and compute times. Pagoda significantly outperforms CUDA-<br>HyperQ(1.76x), 20-core PThreads(5.52x), and GeMTC(1.44x) because of<br>the high GPU utilization |      |

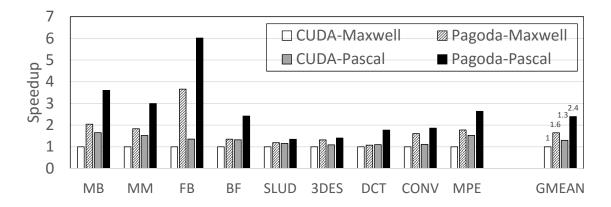

| 5.7  | Pagoda Performance Scalability: CUDA-Maxwell and CUDA-Pascal in-<br>dicates CUDA-HyperQ applications are run on Nvidia Maxwell and Pascal<br>Titan X GPU. Pagoda achieves 2.4X speedup compared to CUDA-Maxwell<br>by running benchmarks on Nvidia Pascal GPU                                                                                                                                                                                                          |      |

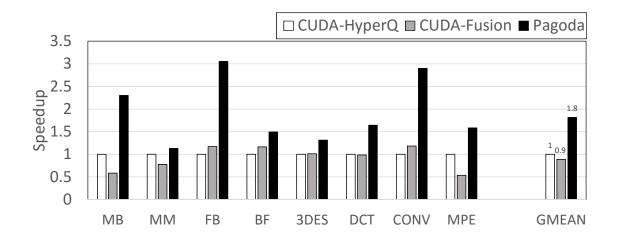

| 5.8  | Performance Comparison of Statis Fusion, CUDA-HyperQ and Pagoda with irregular tasks: Dynamic task spawning mechanism in Pagoda obtains high performance even with irregular workloads                                                                                                                                                                                                                                                                                 | . 60 |

| 5.9  | Average Latency of Tasks Pagoda achieves much lower latency compared<br>to static fusion                                                                                                                                                                                                                                                                                                                                                                               |      |

| 5.10 | Benefit of Pagoda Continuous Spawning and Concurrent, Pipelined Task<br>Processing Pagoda performs both continuous task spawning and concur-<br>rent, pipelined task processing. Pagoda-batching only performs task pro-<br>cessing. GeMTC performs neither. Pagoda outperms GeMTC in all cases                                                                                                                                                                        | . 63 |

Figu

| Figu | re                                                                                                                                                                                                                           | Pag | çe |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

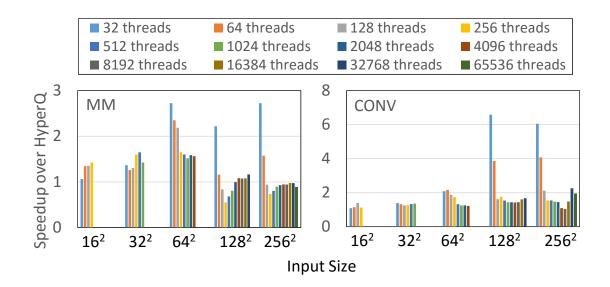

| 5.11 | Effects of varying threads per task for different input size For small threads, Pagoda outperms HyperQ in all input sizes. For large thread counts, Pagoda may still outperform HyerQ because its finer grain of scheduling. | . 6 | 54 |

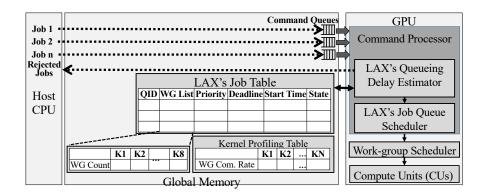

| 6.1  | LAX procedure and system overview                                                                                                                                                                                            | . 6 | 66 |

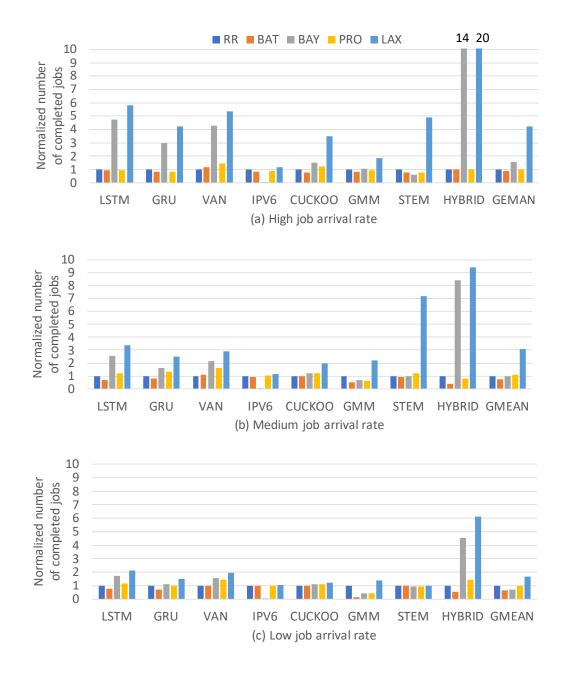

| 6.2  | Jobs completed by their deadlines for CPU-side schedulers, RR, and LAX, normalized to RR                                                                                                                                     | . 7 | 7  |

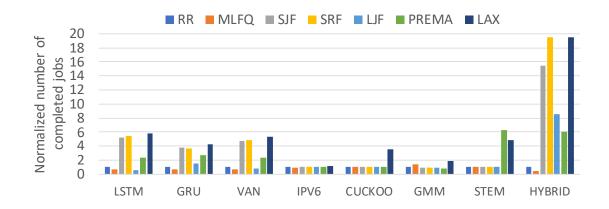

| 6.3  | Jobs completed by their deadlines at the high job arrival rate, for schedulers that extend the CP, normalized to RR                                                                                                          | . 7 | 78 |

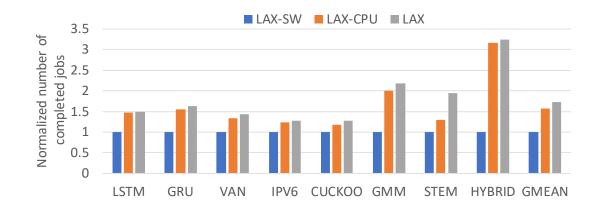

| 6.4  | Jobs completed by their deadlines over different laxity-aware implementations, normalized to LAX-SW                                                                                                                          | . 8 | 30 |

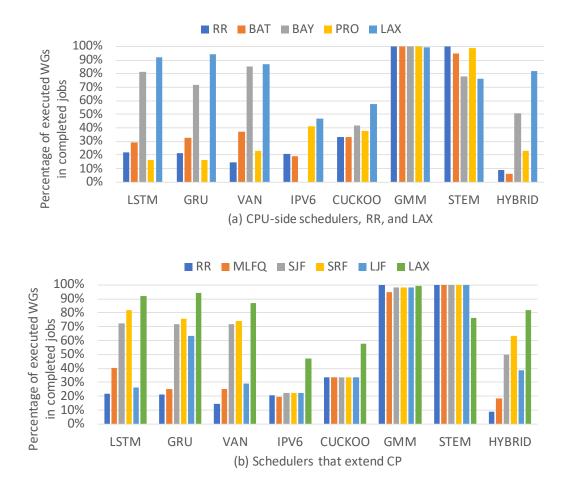

| 6.5  | Percentage of completed WGs from jobs that meet their dead-lines at the high job arrival rate.                                                                                                                               | . 8 | 33 |

| 6.6  | LAX's Job Time and Priority Prediction in LSTM. P0 is the highest pri-<br>ority.                                                                                                                                             | . 8 | 34 |

| 7.1  | DARSIE's Instruction Skipping Flow: Branch instructions always force a TB-wide barrier to determine what the majority-path is. In this example, TBs are three warps wide                                                     | . 8 | 38 |

| 7.2  | Example of compiler marking TB-redundant instructions for matrix multiply kernel. DR:Definitely Redundant, CR:Conditionally Redundant                                                                                        | . 9 | )1 |

| 7.3  | Detailed breakdown of DARSIE uarch operation.                                                                                                                                                                                | . 9 | )5 |

| 7.4  | Performance of DARSIE against prior work. Speedup is normalized to the baseline GPU                                                                                                                                          | 10  | )2 |

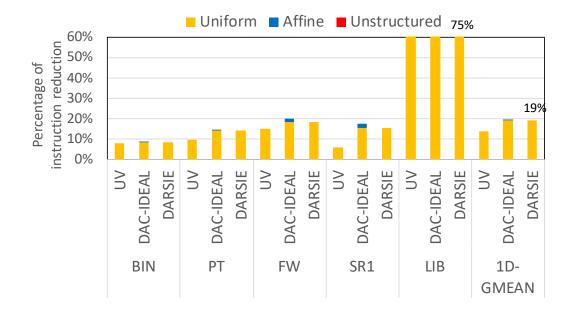

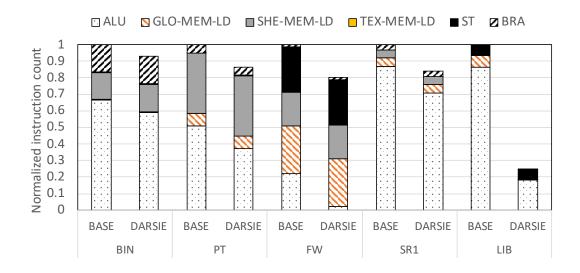

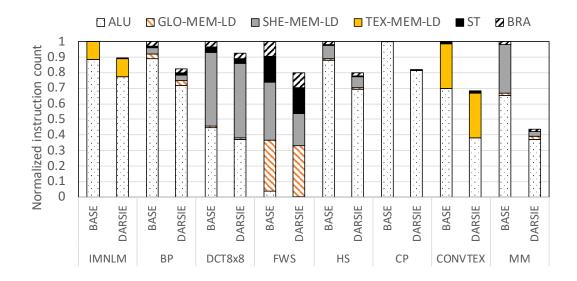

| 7.5  | Percent reduction in 1D benchmark instructions versus the baseline                                                                                                                                                           | 10  | )3 |

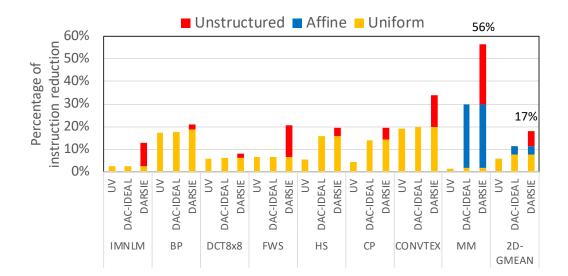

| 7.6  | Percent reduction in 2D benchamrk instructions versus the baseline                                                                                                                                                           | 10  | )3 |

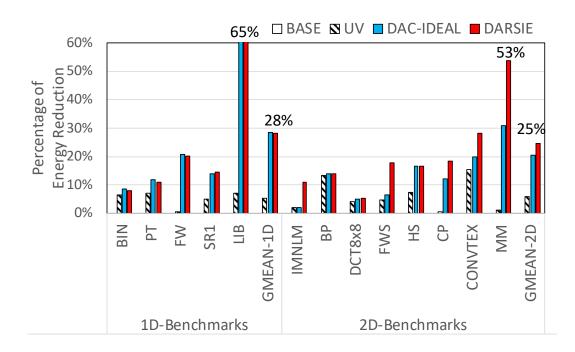

| 7.7  | Percent Energy Reduction versus the baseline                                                                                                                                                                                 | 10  | )4 |

| 7.8  | Effects of Synchronization.                                                                                                                                                                                                  | 10  | )6 |

| 7.9  | Instruction Reduction of 1D-benchmarks                                                                                                                                                                                       | 10  | )6 |

107

xii

#### ABSTRACT

Tsung Tai Yeh Ph.D., Purdue University, May 2020. Accelerating Parallel Tasks By Optimizing GPU Hardware Resource Utilization. Major Professor: Timothy G. Rogers.

Efficient GPU applications rely on programmers carefully structure their codes to fully utilize the GPU resources. In general, programmers spend a significant amount of time optimizing their applications to run efficiently on domain-specific architectures. To reduce the burden on programmers to utilize GPUs fully, I create several hardware and software solutions that improve the resource utilization on parallel processors without significant programmer intervention.

Recently, GPUs are increasingly being deployed in data centers to accelerate latency-driven applications, which exhibit a modest amount of data parallelism. The synchronous kernel execution on these applications cannot fully utilize the entire GPU. Thus, a GPU contains multiple hardware queues to improve its throughput by executing multiple kernels on a single device simultaneously when there are sufficient hardware resources. However, a GPU faces severe underutilization when the space in these queues has been exhausted, and the performance benefit vanishes with the decreased parallelism. As a result, I proposed a GPU runtime system – Pagoda, which virtualizes the GPU hardware resources by using an OS-like daemon kernel called MasterKernel. Tasks (kernels) are spawned from the CPU onto Pagoda as they become available, and are scheduled by the MasterKernel at the warp granularity to increase the GPU throughput for latency-driven applications. This work invents several programming APIs to handle task spawning and synchronization and includes parallel tasks and warp scheduling policies to reduce runtime overhead. Latency-driven applications have both high throughput demands and response time constraints. These applications may launch many kernels that do not fully utilize the GPU unless grouped with large batch sizes. However, batching forces jobs to wait, which increases their latency. This wait time can be unacceptable when considering real-world arrival times of jobs. However, the round-robin GPU kernel scheduler is oblivious to application deadlines. This deadline-blind scheduling policy makes it harder to ensure that kernels meet their QoS deadlines. To enhance the responsiveness of the GPU, I also proposed LAX, including an execution time estimate for jobs with one or many kernels. Moreover, LAX adjusts priorities of kernels dynamically based on their slack time to increase the number of jobs that complete by their real-time deadlines. LAX improves the responsiveness and throughput of GPUs.

It is well-known that grouping threads into warps can create redundancy across scalar values in GPU vector registers. However, I also found that the layout of thread indices in multi-dimensional threadblocks (TBs) creates redundancy in the registers storing thread IDs. This redundancy propagates into dependent instructions that can be traced and identified statically. To remove GPU redundant instructions, I proposed DARSIE that uses a per-kernel compiler finalization check that uses TB dimensions to determine which instructions are redundant. Once identified, DARSIE hardware skips TB-redundant instructions before they are fetched. DARSIE uses a new multithreaded register renaming and instruction synchronization technique to share the values from redundant instructions among warps in each TB. Altogether, DARSIE decreases the number of executed instructions to improve GPU performance and energy.

### 1. INTRODUCTION

Programmers spend a significant amount of time optimizing their applications to run efficiently on domain-specific architectures. However, variants of hardware components in these domain-specific accelerators increase the burden on programmers to utilize these accelerators fully. Graphic Processing Units (GPUs) consist of many computing units to enhance the throughput of parallel execution and provide programmable scratchpad cache memory and vector registers to reduce the data access latency. To increase the scope of GPU applications, GPUs also enable multi-tasking by executing multiple kernels simultaneously on a single device. However, these concurrent applications with difference resource usage and quality-of-service (QoS) constraints exhibit new challenges on GPU computing.

GPUs are increasingly being considered for latency-sensitive applications in data centers. Examples include deep learning inference, network packet, and natural language processing. These data parallel applications exhibit a modest amount of data parallelism with high throughput demands and real-time deadline constraints. Furthermore, these applications may launch many kernels that do not fully utilize the GPU unless grouped with large batch sizes. However, batching forces jobs to wait, which increases their latency.

To reduce the latency on large batch, contemporary GPUs support the execution of multiple kernels on a single device simultaneously when there are sufficient hardware resources. In general, a GPU contains multiple hardware queues to support this type of execution. Thus, programmers can use GPU streams to execute these latency-driven kernels concurrently. However, the GPU concurrent kernel execution exposes several problems on latency-sensitive applications. First, GPUs faces severe underutilization when the space in these queues has been exhausted, and the performance benefit vanishes with the decreased parallelism. Second, the round-robin GPU

2

kernel scheduler is oblivious to application deadlines. This deadline-blind scheduling policy makes it harder to ensure that kernels meet QoS deadlines. This thesis will present hardware and software solutions for problems when executing GPU kernels concurrently.

Additionally, GPUs achieve high throughput by grouping multiple threads into warps to hide long latency operations with fine-grained *Single Instruction Multiple Thread* (SIMT) execution. However, the layout of thread indices in multi-dimensional threadblocks creates redundancy in the registers storing thread IDs. For instance, each matrix can be chunked into multiple tiling blocks that are loaded in the GPU shared memory with 2D thread in matrix multiplication program. We can observe many repetitive memory load in each row and column of two matrices in a tiling block and present the redundancy across different warps in a threadblock. I run through multiple applications and found over 30% SIMT redundant instructions derived from their operand values. This thesis also focuses on removing these SIMT redundant instructions, Finally, this thesis will also present a hybrid software and hardware solution to reduce the waste of hardware resources on SIMT redundant instructions.

This chapter begins with the discussion of GPU underutilization problems in the presence of latency-sensitive applications. We follow with a close look at the kernel scheduling issues when executing latency-driven applications composed of multiple kernels simultaneously and the redundancy shown in the SIMT executions. At last, I will present several open challenges when increasing GPU resource utilization and reducing the number of redundant SIMT instructions.

#### 1.1 GPU Underutilization on Latency-sensitive Applications

This section addresses the GPU underutilization problem in the presence of latency-sensitive applications and challenges to overcome such an obstacle on contemporary GPUs.

#### 1.1.1 Narrow Task

GPGPU computing has demonstrated an ability to accelerate a substantial class of compute-intensive applications [1, 2]. These applications have a high degree of parallelism, where iterations of large parallel loops are executed on the GPU. The programs see significant performance benefits because they can fully utilize the GPU's hardware resources by launching enough concurrent threads.

The GPU's performance benefits start to diminish as the degree of parallelism lessens. Conventionally, large parallel loops are offloaded to the GPU, while retaining the execution of smaller ones on the CPU. Applications should benefit from using the GPU, provided that the involved task (or CUDA kernel) count is sufficiently high. Each such task, called a *narrow task*, has limited parallelism (< 500 data parallel threads in practice).

Narrow tasks emerge in a number of scenarios. One set of such applications comprises latency-driven, real-time workloads. For example, online sensors that generate small inputs, resulting in tasks with low parallelism. Online sensors can generate many tasks in quick succession and require immediate processing. These workloads have been characterized as having mixed task and data parallelism [3, 4]. Secondly, *irregular* applications can exhibit narrow tasks. These applications often contain varying amounts of computation among different threads, and/or among loop iterations. To reduce load imbalance, these applications are often represented using many tasks with low degrees of parallelism [5]. Irregular workloads may also arise in multiprogrammed environments. Different applications with low degrees of parallelism can be co-executed on a node to exploit all the computing resources.

#### 1.1.2 Prior Work to Overcome GPU Underutilization

Prior work has identified the issue of GPU underutilization [6–9]. One approach to solve this problem is to statically fuse multiple smaller tasks [6,7] to accumulate a large kernel. Advanced approaches [8,10] use a concurrent kernel mechanism, monitoring and time-slicing their execution at runtime to obtain fair sharing. These static approaches require the programmer to fuse tasks *manually* and none of them have been shown to work beyond ten concurrent tasks.

These mechanisms also require static knowledge of the kernels to be fused, which is not always possible in multi-programmed or real-time environments. Additionally, individual tasks in a fused tasks receive the same on-chip resource allocation, e.g., shared memory and registers, thereby limiting occupancy based on the resource requirements of the largest task.

Dynamic (runtime) solutions can mitigate the above issues of static fusion. NVIDIA's current-generation GPUs employ HyperQ [11], which allows 32 kernels (tasks) to concurrently execute on the GPU. However, I show that narrow tasks can still cause underutilization, as 32 such tasks may not occupy the entire GPU. I argue that software mechanisms are needed to achieve flexible kernel concurrency. Prior work, *GPU enabled Many-Task Computing* (GeMTC) [9], presents a runtime task scheduling mechanism, where a task executes as a single *threadblock. Threadblocks* are sets of threads constituting the GPU kernel. Because GPU architectures limit the concurrent threadblock count, executing narrow tasks in GeMTC may result in poor utilization. In addition, GeMTC uses batch-based task execution, which results in delayed task launching and load imbalance since the completion time of a batch is determined by its longest running task.

#### 1.1.3 Challenges in Designing a GPU Runtime System for Narrow Tasks

There are three key challenges that must be addressed when attempting to launch and run thousands of short-running tasks on a GPU.

First, CPU-GPU communication overhead must be minimized, while allowing the GPU to asynchronously schedule new tasks on each Streaming Multiprocessor (SM). Launching thousands of short-running tasks increases the importance of minimizing the time it takes for each task to begin execution on the GPU. Since the CPU and

GPU must coordinate task spawning and scheduling over the PCIe bus, which currently has no support for atomic operations, the handshaking required is expensive or impossible if a traditional data structure, such as a queue [12], is used. Previous work that required OS-like co-ordination over PCIe [13, 14] solved consistency issues using a producer-consumer model but did not have to optimize the system for many, short running tasks. The second challenge is to keep the overheads involved in task spawning and scheduling low. Minimizing both the copying of task parameters and the search for free GPU resources is important when task execution times are short. The third issue is supporting native CUDA functionality such as shared memory usage and efficient threadblock synchronization.

#### 1.1.4 Pagoda GPU Runtime System for Narrow Tasks

I proposed Pagoda – a GPU runtime system and is designed to increase the number of concurrent tasks (kernels) on a single GPU. The programmer replaces certain CUDA API calls with equivalent Pagoda calls in the host and device codes, retaining the functionality of the CUDA programming model. Unlike static solutions, the programmer does not have to tediously fuse the available tasks. Pagoda achieves high utilization by continually running a *MasterKernel*, which controls the execution of all GPU *warps* in software. In Pagoda, tasks are spawned by the CPU as soon as they become available, without batching. On the GPU side, the MasterKernel virtualizes the GPU's resource allocation and threadblock scheduling mechanism to allow individual warps to make progress as soon as resources are available.

#### 1.2 Latency-sensitive GPU Applications with Deadline Constraints

This section addresses problems when executing latency-sensitive applications with real-time deadline constraints simultaneously on a single GPU and previous work that improve QoS of GPU latency-sensitive applications.

Fig. 1.1.: Characteristics of many-kernel latency-sensitive jobs versus few-kernel latency-sensitive jobs, listed in Table 6.3

#### 1.2.1 Constraints of GPUs on Latency-sensitive Applications

GPUs are the programmable accelerator of choice for massively data-parallel applications that do not have strict latency requirements. However, there is a growing class of latency-sensitive, data-parallel workloads that can benefit from the GPU's throughput. Examples include machine learning (ML) inference for RNNs [15–20], network packet processing [21–23], and natural language processing (NLP) in Intelligent Personal Assistants (IPAs) [24]. These latency-sensitive applications have become a staple of contemporary datacenters and have response time constraints. For instance, Google TPU [25] paper raises RNN inference applications have become a staple of contemporary data centers, which increasing include GPUs and other high-throughput accelerators. Given the availability of GPUs in the data center, and the data-parallel nature of the applications, there is significant potential to offload work from overburdened CPUs to an accelerator. However, contemporary GPUs are

deadline-blind and have no mechanism to predict which work can be offloaded and completed in time.

Many deadline-driven applications exhibit a middling amount of data-parallelism [26]. Enough to justify GPU acceleration, but not enough to fully utilize the GPU's resources [24,27]. As a result, executing one job on the GPU at a time causes severe underutilization. To alleviate this issue, programmers batch similar jobs together [19], greatly improving throughput and utilization at the expense of additional latency. This increase in latency is usually unacceptable for tasks with tight deadlines [25], especially when realistic job arrival rates are considered. GPU programs can avoid batching, while still executing multiple jobs at once with streams. Streams allow kernels from independent jobs to be scheduled concurrently on multiple command queues located between the CPU and GPU [11, 28]. However, software cannot efficiently manage the relative priority of these queues at short time scales, which makes it difficult to efficiently re-prioritize jobs with different deadlines as contention in the GPU changes.

State-of-the-art GPU solutions for managing latency-sensitive tasks are restricted to varying priorities at a coarse granularity on the host CPU [29–31], and thus do not fully utilize the GPU's integrated queue scheduling logic. Consequently, the precision of information available to these CPU-side mechanisms is limited. Dynamic, microsecond-scale information about GPU-side contention, which some latency-sensitive applications require, is difficult to track from host-side software. As a result, these software-only techniques are less effective when scheduling many latency-sensitive jobs and primarily focus on mixing latency-insensitive and latencysensitive work. In contrast, we target a common situation in many data centers where many homogeneous, latency-sensitive jobs are executing in parallel [32].

Figure 1.1 demonstrates how quickly scheduling decisions must be made when executing concurrent latency-sensitive jobs. To better understand their demands, we subdivide our latency-sensitive applications into two categories: many-kernel and few-kernel. The many-kernel applications we study, which come from ML inference, are composed of a number of relatively small, short kernels and typically have deadlines on the order of milliseconds. The few-kernel applications, which come from network packet processing and IPAs, execute a single, much longer kernel, but have more aggressive deadlines (usually < 1 ms). To efficiently manage both many-kernel and few-kernel applications, per-kernel scheduling decisions must be made at the microsecond timescale.

We argue that dynamic, integrated stream scheduling is necessary to meet the low-latency scheduling demands of these workloads. An analogy can be made to the memory hierarchy in modern CPUs. At the lower-levels of the CPU memory hierarchy, the operating system is responsible for managing the replacement of relatively large pages in physical memory from the relatively high-latency disk. However, smaller cache blocks, which require nanosecond-scale response times, are managed by hardware. In throughput-oriented GPUs, scheduling relatively few, millisecondor second-scale kernels in soft-ware is acceptable. However, managing many shortrunning kernels competing for GPU resources to meet sub-millisecond or millisecondscale deadlines requires hardware support.

#### 1.2.2 Prior Work to Improve QoS of Latency-sensitive GPU Applications

Contemporary GPUs [11, 28, 33] contain multiple queues to manage independent work submitted asynchronously with streams. This parallel work can be executed concurrently on a GPU when resources are available. In this section, we describe the work to schedule multiple kernels on a GPU.

#### Preemptive GPUs

Prior work on GPU kernel preemption or re-execution [34–37] are alternative mechanisms that can be used in combination with better stream scheduling. However, for latency-sensitive workloads, the overheads associated with preempting GPU kernel contexts, whose aggregate registers and scratchpad size can be 100s of KBs

Fig. 1.2.: Comparison of Round Robin and Laxity-aware Schedulers for a GPU that can simultaneously execute 2 jobs

Table 3.1, may be prohibitive. Additionally, the benefits of preemption are muted for short running kernels that finish long before the cost of preemption and rescheduling can be amortized. Specifically, Table 3.1 indicates that the vast majority of kernels in our evaluated latency-sensitive workloads complete within 10 us. Recently proposed preemption-based techniques, such as PREMA, are effective at intelligently preempting and scheduling relatively coarse-grained tasks [38].

#### **GPU Stream Scheduling**

The Command Processor (CP) is an integrated microprocessor within a GPU, which parses the kernel contexts and schedules streams. In Figure 1.3, each stream is mapped to a queue and each queue can hold multiple kernels from a single stream. Inter-kernel dependencies between kernels in the same stream are maintained, but GPUs can execute kernels from different streams simultaneously. Each queue entry

Fig. 1.3.: GPU Queue Scheduler Architecture

describes a separate kernel and includes details such as the kernel's thread dimensions, register usage, and local data store (LDS) size. We assume the CP can parse four different streams in parallel every 2 microseconds in this work. Afterward, a work-group (WG) scheduler reads these fields to dispatch work groups to compute units (CUs). Generally, GPU work group schedulers issue all work groups from one kernel before switching to issuing work groups from a different kernel. Despite this restriction, work groups from kernels in different queues often interleave execution.

Normally, the CP schedules kernels within these queues in a Round Robin (RR) manner [48]. This deadline-blind scheduling policy makes it harder to complete jobs by their real-time deadlines. The top half of Figure 1.2 illustrates the problem with RR. In this example, the GPU is running three jobs with varying arrival times such that the deadline of each job varies. Each job contains two kernels with different execution times. For simplicity, assume that at most two kernels can be concurrently executed. RR will schedule kernel 1 from job 1 (J1:K1) and kernel 1 from job 2

(J2:K1) first because they arrive before job 3. When job 3 arrives, its first kernel is scheduled after J1:K1, and then J3 is not scheduled again until both J1:K2 and J2:K2 have executed. Since J3 is the longest job, if it had been prioritized over J1 and J2, all the jobs could have made their deadlines. However, since RR is unaware of this, J3 misses its deadline.

#### Priority-based GPU Programming

At the application level, programmers can specify the priority value of streams. However, the limited number of priority levels (e.g., high and low) in GPU programming languages [39] is insufficient. First, the priority level submitted by programmers does not give any information about when the kernel must be completed, only the kernel's relative importance. Second, priorities assigned to individual streams do not provide the GPU a global view of when to complete a chain of dependent kernels. As a result, programmers conservatively set a job's priority to ensure that its deadline is met. Finally, jobs can have different amounts of work despite potentially having the same static priority level.

#### Laxity-based Scheduling on GPUs

Laxity-based scheduling [40] leverages the laxity which tells us how close to the deadline of a job is predicted to finish. The dynamic laxity value is a job priority in the laxity-based scheduling. Jobs with less laxity have higher priority. Laxity-based scheduling was used in the real-time applications to ensure jobs to be completed by their deadlines. Also, laxity-based scheduling relies on accurate job execution time prediction to adjust jobs' priorities dynamically. However, GPU occupancy and job arrival rates cause the completion time of each job and their associated kernel(s) to vary. These dynamically varying parameters make static predictions of job completion time extremely difficult.

I propose to dynamically adjust the priorities of each job (and its associated queue) based on the estimated execution time of each job's kernels. By adjusting the priorities, kernel launches are re-ordered to increase the number of jobs completed by their deadlines. The bottom half of Figure 1.2 demonstrates that with reasonably accurate execution time estimates, a deadline-aware scheduler can optimize the scheduling of deadline-sensitive jobs (similar to prior work for CPUs [74][75]). The bottom example begins like the top example, with the GPU scheduling job 1 and job 2 first, because they arrive earlier than job 3. However, the LAX scheduler is aware of the deadlines and durations of all 3 jobs, so it prioritizes J3 when it arrives since it will miss its deadline if not immediately scheduled (i.e., it has a zero laxity). As a result, all three jobs completed by the deadlines.

#### 1.2.3 LAX: Laxity-aware GPU Job Scheduler

An effective deadline-aware scheduler must: (1) be aware of each job's deadline, (2) estimate the remaining execution time for each job, and (3) frequently adjust job priority as time progresses and the level of contention in the GPU changes. We propose an integrated laxity-aware stream scheduler (LAX) that achieves all three of these requirements.

LAX leverages the idea that stream-based GPU applications enqueue all their kernels in quick succession. In the many-kernel jobs, although each kernel launch is dependent on the data output by the previous kernel, all the kernels associated with a particular job are known before the GPU begins execution. As a result, LAX uses the GPU's queue scheduler (or command processor (CP)), to perform a novel stream inspection technique that reads the contents of parallel hardware streams and generates an estimate of how much work exists in each job. LAX's scheduling algorithm then combines this information with the job's deadline and fine-grain information about the current per-kernel work completion-rate to generate an accurate estimate of how much laxity the job has. A job's laxity is an estimate of how much earlier than its deadline it will finish, given current conditions [40]. Based on each job's estimated laxity, our scheduler re-prioritizes jobs to complete as many as possible by their respective deadlines. With the rich, fine-grained information available to GPU stream schedulers, LAX also prevents job oversubscription by using a Little's Law-based queuing delay estimate [41,42] to reject work that is predicted to miss its deadline. My proposed stream inspection, per-kernel work completion monitoring, and job rejection mechanisms make real-time scheduling possible and practical in GPUs

#### 1.3 Redundancy on GPU SIMT Instructions

This section illustrates the redundancy embedded in GPU SIMT instructions, previous work, and challenges to improve the performance and energy of GPUs through the elimination of SIMT redundant instructions.

Fig. 1.4.: Redundant instructions in each GPU thread grouping level across different applications

#### 1.3.1 Threadblock-wide Redundancy on GPU SIMT Instructions

Graphics Processing Units (GPUs) run thousands of concurrent scalar threads based on programmer-defined parallelism. Programmers define a three dimensional grid of threadblocks (TBs) for each kernel. TBs are three-dimensional arrangements of scalar threads, grouped into warps behind the scenes for Single Instruction Multiple Thread (SIMT) execution. Although the programming model for GPUs is SIMT, the underlying datapath is Single Instruction Multiple Data (SIMD). Each warp has a set of private vector registers from a vector register file storing per-thread scalar values in each vector lane. For example, each lane in every warp of the TB contains the same scalar value such as the shared constants and TB dimensions [43-45]. Furthermore, affine redundancy occurs when vector registers in different warps have the same value, which can be represented as (base, strand) pair. This redundancy occurs naturally in multi-dimensional TBs where consecutive lanes have consecutive threadId values, replicated in the private register space of each warp in the TB. Unstructured redundancy occurs when registers have the same vector values in each warp of the TB, but those values have no discernible pattern. However, little work exists on statically identifying and removing all three types of redundancy that can exist on GPU programming model.

To help understand this redundancy, Figure 1.4 shows the results of a limit-study measuring the fraction of redundantly executed instructions at the grid, TB, and warp level.Instructions are classified as redundant at the grid-level when all the grid's warp instructions operate on the same vector operands, implying it need only be executed once for the entire grid. Similarly, Figure 1.4 plots redundant instructions for TBs if all warp instructions within a TB use the same vector operands. Warp-wide redundancy occurs if all scalar threads in a warp operate on the same scalar value. We find that the greatest opportunity for redundancy elimination exists at the TB level, where on average 33% of instructions need only be executed once per TB.

GPU languages like CUDA and OpenCL express parallelism defined along multiple (x, y and z) axes, which helps programmers naturally map multi-dimensional data to multi-dimensional thread grids. However, this dimensionality can have a significant impact on redundancy. While opportunities exist for redundancy elimination at the warp granularity (through scalar instructions), eliminating vector instructions at the TB and grid levels improves both performance and energy efficiency without the addition of functional units or register files. Unlike warp-wide redundant operations that are local to one vector instruction, TB- and grid-wide redundant instructions occur across different vector instruction, each of which occupies space in the instruction pipeline. Elimination of these vector instructions frees space in the pipeline, and reduces pressure on the memory system if the instruction is a memory operation. In practice, grid-wide redundancy is both difficult to eliminate and less common than TB-wide redundancy. I therefore focus this thesis on the elimination of TB-wide redundant instructions to improve both performance and energy efficiency.

#### 1.3.2 Previous Work on Removing GPU SIMT Redundant Instructions

Contemporary GPUs from NVIDIA and AMD use a scalar functional unit and register file to perform operations on warp-wide redundant data identified by the compiler [46, 47]. Research has also sought to address warp-level redundancy by masking off lanes in the vector pipeline and skipping partial warp instructions when the SIMD width is less than the warp size [43–45]. Other work has proposed adding expensive value comparison hardware to the pipeline to remove redundancy at the issue stage, or reduce register file space via compression [48,49]. I use insights gained from creating a redundancy taxonomy for TBs to identify both new opportunities for instruction skipping that are unexplored in these works, and ways to offload redundancy identification to the compiler. This allows my proposed work to both avoid expensive value comparisons in hardware, and improve performance by skipping entire vector instructions before they are fetched in the frontend of the pipeline.

#### **1.3.3** Challenges on Eliminating GPU SIMT Redundant Instructions

Value sharing and instruction elimination is difficult to solve solely in the compiler or hardware. Alone, the compiler is not able to efficiently coordinate value sharing and instruction skipping between parallel warps. Likewise, it is difficult for a solely hardware implementation to detect redundancy in warp-wide vector registers, and a reactive mechanism to detect redundancy in register file accesses and forward PC values marked as redundant to the frontend of the pipeline is complex. My proposed work therefore uses a combined compiler and hardware approach to avoid these problems.

#### 1.3.4 DARSIE GPU SIMT Redundant Instruction Skipper

In this thesis, I examine the root-causes of TB-wide redundancy, and find that many conditionally redundant instructions at the TB level that can be identified during static compilation. We observe that the layout of thread indices in multidimensional TBs creates redundancy in the registers storing thread IDs. This redundancy propagates into dependent instructions that can also be traced and identified statically. A per-kernel runtime check of a TB's dimensions can be used to determine if conditionally redundant instructions are actually redundant. This avoids performing expensive vector register comparisons at runtime. Based on these observations, I propose Dimensionality-Aware Redundant SIMT Instruction Elimination (DARSIE), a TB-centric instruction skipping mechanism that statically identifies TB-redundant instructions using a combination of compiler markings and runtime TB-sizing information. Once identified, TB-redundant instructions are skipped by the hardware before they are fetched. DARSIE uses a novel multithreaded register renaming and instruction synchronization technique to share the values from redundant instructions among warps in each TB. This differs from CPU register renaming that is used to remove false dependencies in single-threaded pipelines.

Contemporary GPUs are designed to perform well when executing regular kernels with limited control-flow divergence. As a result, these regular applications are the most commonly run in the field today [50]. Although these applications can be computationally-dense, we demonstrate that they also operate a significant number of redundant operations. In contrast to the body of orthogonal work on improving GPUs in the presence of irregular, cache- and scheduling-sensitive workloads [51– 55], DARSIE is designed to target common contemporary workloads which prior work has demonstrated are insensitive to locality-optimizing techniques that focus on scheduling [51].

To demonstrate how common multi-dimensional redundancy is, we conducted a survey of 133 applications [56–67] running on a commodity NVIDIA Volta GPU. Over 33% of the applications surveyed demonstrated the multi-dimensional TB characteristics that create implicit redundancy. Interestingly, we find that this characteristic is more pervasive in applications that make use of optimized libraries (CUDNN, CUBLAS, etc.), where 60% met DARSIE's conditional redundancy requirements. Furthermore, in the apps that had at least one kernel that met the sizing requirements, an average of 71% of the application's execution time is spent in those kernels.

#### 1.4 Contributions of This Thesis

In this thesis, I demonstrate the hardware and software designs to improve the GPU utilization and response time on latency-sensitive applications. The main contributions are as follows:

• A GPU runtime system virtualizing the hardware resources. To increase GPU throughput in the presence of narrow tasks, I present a software mechanism – Pagoda to schedule multiple tasks on the GPU in parallel, and describes a pipelining scheme to overlap several task processing stages. Pagoda includes new APIs to handle the operation of task processing and software solutions for dynamic shared memory management and sub-threadblock synchro-

nization. Furthermore, Pagoda introduces a continuous task spawning mechanism to reduce CPU-GPU synchronizations to obtain a high task spawn rate.

- A deadline-aware GPU kernel scheduler for real-time applications with deadline constraints. Contemporary GPUs supports the concurrent kernel execution, but its round-robin kernel scheduling policy does not satisfy QoS requirements in latency-driven applications. Thus, I propose a laxity-aware algorithm (LAX), which is used in combination with a dynamic, per-kernel work completion rate to generate an accurate estimate of work and time remaining. LAX dynamically varies job priorities to improve throughput while attempting to meet real-time latency requirements.

- The elimination of GPU redundant SIMT instructions . I introduce a new taxonomy of redundancy for GPUs, focusing on the TB granularity. I show that the composition of TB-wide redundancy is highly dependent on the dimensions of the TB, and that thread index layouts in multi-dimensional TBs create ample implicit redundancy. Therefore, I propose DARSIE, which combines our redundancy identification software with novel instruction skipping hardware to ensure that redundant instructions are fetched an executed only once per-TB. DARSIE leverages multithreaded register renaming and selective warp synchronization to share vector registers between warps in a TB, allowing TB-redundant instructions to be skipped in the fetch stage of the pipeline.

#### 1.5 Thesis Overview

The following sections present the work that improves 1) the GPU resource utilization in the presence of narrow tasks. 2) the number of concurrent latency-sensitive jobs completed by their real-time deadlines. 3) the waste of GPU hardware resource caused by redundant SIMT instructions. Chapter 2 illustrates background and related work. Chapter 5 presents Pagoda GPU runtime system. Chapter 4 illustrates a taxonomy of GPU redundancy. Chapter 6 describes the work of deadline-aware LAX job scheduler. Chapter 7 demonstrates DARSIE that eliminates redundant GPU SIMT redundant instructions. The conclusion and future work are placed on Chapter 8.

### 2. BACKGROUND AND RELATED WORK

In this chapter, I describe the GPU architecture, constructions of GPU programming languages, and GPU microarchitectural model. Then, I examine the prior solutions to helping the GPU utilization and QoS requirements on domain-specific architectures. At last, I also discuss the taxonomy of GPU redundancy and the previous work in removing GPU redundant SIMT instructions.

Fig. 2.1.: GPU Architecture: The number of GPU cores is dependent with different GPU generations and the scratchpad cache is shared with L1D cache.

#### 2.1 GPU Architecture and Programming

The GPU hardware typically consists of multiple GPU cores within Streaming Multiprocessors (SMs) on NVIDIA GPUs [67] and Compute Units (CUs) on AMD GPUs [68]. Each GPU core has its private L1 data cache and one on-chip programmer managed cache, known as shared memory and a number of 32-bit registers. L2 cache and I-cache are shared across different GPU cores. GPU scalar threads typically share register files and the shared memory space in each SM and CU. Within a SM and CU, the SIMD unit contains hundreds of SIMD lanes for parallel thread arithmetic-logic unit (ALU) executions. In NVIDIA GPUs, the *War*p is the basic Single Instruction, Multiple Thread (SIMT) work unit, which comprises 32 threads that march in lockstep, executing the same instruction. In AMD GPUs, a *wavefront* is like the warp and composed of 64 threads. Each SM has multiple warp slots and warp schedulers. The warp scheduler can concurrently schedule up to 64 warps and issues ready warps to SIMD unit for the execution.

In the CUDA programming model, the programmer organizes parallel work in *kernels*. Threads of a kernel are grouped into *threadblocks*. Multiple threadblocks can reside on each SM, the maximum number being 32. The threadblock size is limited to 1024 threads, or 32 warps. Each SM can hold up to 2048 concurrent threads [67]. Both the shared memory and registers of an SM are partitioned among the executing threadblocks. There is no CUDA primitive for global, kernel-wide synchronization; however, threads in a threadblock can use the *\_\_syncthreads()* function as a barrier.

A way of measuring the GPU utilization is *occupancy*. Occupancy is the ratio of the total number of resident GPU warps divided by the maximum number of warps that can co-exist in the GPU (i.e.  $64 \times$  the number of SMs in the GPU). The kernel occupancy is affected by three factors, namely, i) size of threadblocks, ii) kernel's register count, and iii) size of the requested shared memory. Balancing these three factors requires programmer expertise, making high occupancy often difficult to achieve. For example, NVIDIA Volta V100 GPU [69] has 80 SMs. Consider a scenario of narrow tasks, where one task has 256 threads, or 8 warps. If only one task is executed at a time, the occupancy would be  $(8/(64\times80))\times100\% = 0.156\%$ . With HyperQ [11], 32 kernels may co-execute, meaning that 32 narrow tasks can run simultaneously. The achieved occupancy then would still be low, i.e.  $(8\times32/(64\times80))\times100\% = 5\%$ .

Fig. 2.2.: GPU micro-architectural model

#### 2.2 GPU Micro-architectural Model

Figure 2.2 presents the GPU microarchitectural model. Each cycle, a fetch scheduler (1) in Figure 2.2) in the frontend of the pipeline initiates a fetch for one of the warps assigned to the core. This scheduler uses loose-round-robin (LRR) prioritization, and initiates instruction cache (I-cache) fetches based on which warps have empty instruction buffer (I-Buffer 2) entries. Each warp has a two-entry I-buffer that is used to decouple the SIMT frontend (which fetches one PC for an entire 32-thread warp) from the SIMD backend. Each cycle, multiple issue schedulers select at most two instructions from one warp each for execution. Warps are statically partitioned among these issue schedulers.

Once selected to issue, instructions must read their source operands (32-element vector registers with 32-bit elements) from a highly banked register file (0). To avoid excessive bank conflicts and facilitate high bandwidth, an operand collector [70] schedules register file reads in a way that limits stalls. These operand collectors are the inputs to the execution stage of the pipeline. The mapping between <named vector register, warp ID> pairs and physical vector register contents is programmable, and based on a mapping table initialized when a Threadblock (TB) is launched on an SM.

This is necessary since each warp can be assigned a different number of registers at compile time.

There is little documentation on how this register mapping is achieved, so we make the assumption that blocks of registers are assigned to warps using a simple base register + length mapping table. This avoids storing a unique <named vector register, warp> pair for each physical vector register. We also assume this mapping is done in the operand collection phase. Contemporary GPUs (like the Pascal card we model) do not have scoreboard logic embedded in the core, but rather encode dependencies in their instruction stream. Variable-cycle memory instructions are controlled via *depbar* instructions that ensure source registers read by instructions have received responses to their memory requests before a dependent instruction is issued.

### 2.3 Processing Narrow Tasks on Domain-specific Accelerators