# ENERGY EFFICIENT NEUROMORPHIC COMPUTING: CIRCUITS, INTERCONNECTS AND ARCHITECTURE

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Minsuk Koo

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

May 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Kaushik Roy, Chair

School of Electrical and Computer Engineering

Dr. Anand Raghunathan School of Electrical and Computer Engineering Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

Dr. Shreyas Sen

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

To my family and friends.

#### ACKNOWLEDGMENTS

First of all, I would like to thank my advisor, Prof. Kaushik Roy for his encouragement and guidance. My research at Purdue has been guided with his warm-hearted and enthusiastic mentoring. I am truly fortunate to have him as my advisor. I am greatly indebted to him for guiding me not only in research but also in other facets of life at Purdue.

I am also highly thankful to my Ph.D. committee: Prof. Anand Raghunathan, Prof. Vijay Raghunathan and Prof. Shreyas Sen for kindly serving on the advisory committee and for their excellent advice and feedbacks.

I would like to thank all alumni of NRL who paved the way for current NRL members including me. I especially thank Dr. Woo-Shul Cho, Dr. Deliang Fan, Dr. Yusung Kim, Dr. Kon-woo Kwon, Dr. Parami Wijesinghe, Dr. Abhronil Sengupta, Dr. Yeongkyo Seo, Dr. Yong Shim, Dr. Gopalakrishnan Srinivasan, and Dr. Karthik Yogendra for helping me with many aspects.

I also want to thank all current NRL members with whom I had great time during my Ph.D. I especially thank to Amogh Agrawal, Mustafa Ali, Aayush Ankit, Indranil Chakraborty, Mei-Chin Chen, Chankyu Lee, and Chamika Liyanagedera for helpful discussions. I am also would like to thank Rwitti Roy for providing welcoming home, where we hung out playing games, having food, and etc.

Finally and most importantly, I would like to express my greatest thanks to family for their love and support, in particular, my mother Taihee Kim and fater Yunchon Koo who have shown endless love, devoted support and sacrifices. I would also like to recognize my aunt and uncle Yong-Bin and aunt Yong-sun.

This thesis has been possible due to the help and support of numerous people and I want to apologize for not being able to list everyone here.

## TABLE OF CONTENTS

|    |      |        | Pa                                                            | ge  |

|----|------|--------|---------------------------------------------------------------|-----|

| LI | ST O | F TAB  | LES                                                           | iii |

| LI | ST O | F FIGU | URES                                                          | ix  |

| A] | BSTR | ACT    |                                                               | xii |

| 1  | INT  | RODU   | CTION                                                         | 1   |

| 2  |      |        | NE COMMUNICATION FOR ENHANCED CONNECTIVITY<br>MORPHIC SYSTEMS | 5   |

|    | 2.1  | Introd | luction                                                       | 6   |

|    | 2.2  | Backg  | round                                                         | 9   |

|    |      | 2.2.1  | Spiking Neural Network                                        | 9   |

|    |      | 2.2.2  | Memristive Crossbar and Past Work                             | 10  |

|    | 2.3  | Power  | Line Communication                                            | 11  |

|    |      | 2.3.1  | Motivation                                                    | 11  |

|    |      | 2.3.2  | Challenges                                                    | 12  |

|    |      | 2.3.3  | PLC based neuromorphic system design                          | 12  |

|    | 2.4  | Hybri  | d PLC-NOC based Architecture                                  | 15  |

|    | 2.5  | Exper  | imental Methodology                                           | 18  |

|    |      | 2.5.1  | Neuromorphic architecture                                     | 18  |

|    |      | 2.5.2  | PLC channel quality                                           | 19  |

|    |      | 2.5.3  | Benchmarks                                                    | 20  |

|    | 2.6  | Result | 55                                                            | 20  |

|    |      | 2.6.1  | Tx power requirements                                         | 22  |

|    |      | 2.6.2  | Impact on classification accuracy                             | 22  |

|    |      | 2.6.3  | Overall power consumption                                     | 23  |

|    |      | 2.6.4  | Inference energy                                              | 24  |

vi

|   |     | 2.6.5  | Inference latency                                                                                                           | 25 |

|---|-----|--------|-----------------------------------------------------------------------------------------------------------------------------|----|

|   | 2.7 | Conclu | asions                                                                                                                      | 25 |

| 3 | NET | WORK   | OCHASTIC-BITS ENABLED BINARY SPIKING NEURAL<br>K WITH ON-CHIP LEARNING FOR ENERGY EFFICIENT<br>ORPHIC COMPUTING AT THE EDGE | 27 |

|   | 3.1 | Introd | uction                                                                                                                      | 27 |

|   | 3.2 | Backg  | round                                                                                                                       | 30 |

|   |     | 3.2.1  | Stochastic Binary Spiking Neural Network (sBSNN)                                                                            | 30 |

|   |     | 3.2.2  | Stochastic-STDP (sSTDP)                                                                                                     | 32 |

|   | 3.3 | sBSNN  | N Design and Implementation                                                                                                 | 33 |

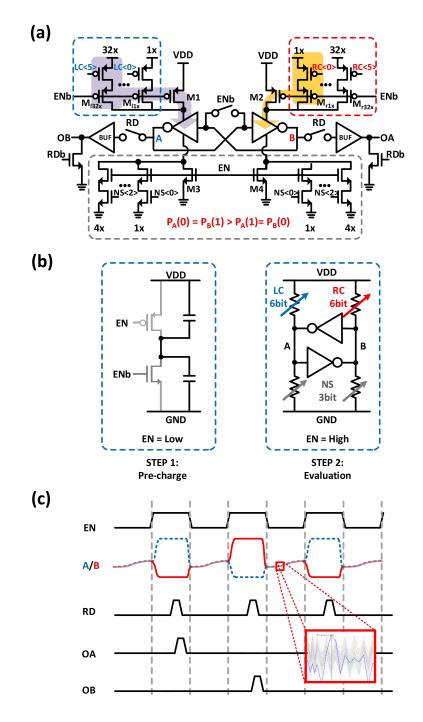

|   |     | 3.3.1  | CMOS 'Stochastic bit' Design                                                                                                | 35 |

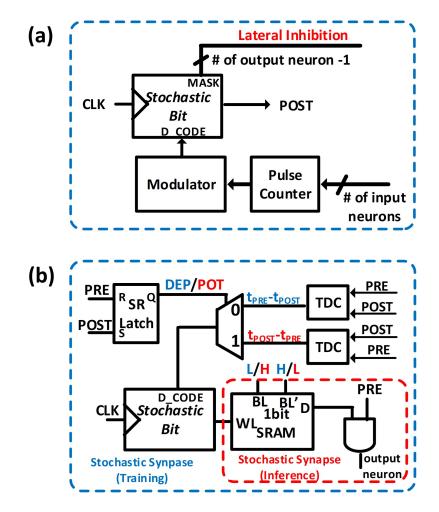

|   |     | 3.3.2  | Stochastic Neuron (sNeuron)                                                                                                 | 36 |

|   |     | 3.3.3  | Stochastic Binary Synapse                                                                                                   | 37 |

|   |     | 3.3.4  | sBSNN System-level Implementation                                                                                           | 38 |

|   | 3.4 | Result | 8                                                                                                                           | 42 |

|   |     | 3.4.1  | 'Stochastic bit' Characterization                                                                                           | 42 |

|   |     | 3.4.2  | Stochastic Binary Synapse                                                                                                   | 44 |

|   |     | 3.4.3  | sBSNN for MNIST Digit Recognition                                                                                           | 45 |

|   |     | 3.4.4  | Energy efficiency                                                                                                           | 47 |

|   |     | 3.4.5  | Process and temperature variation                                                                                           | 49 |

|   | 3.5 | Conclu | sions                                                                                                                       | 51 |

| 4 |     |        | SPIN-TORQUE-OSCILLATOR BASED DISTANCE COMPU-<br>PPLICATION TO IMAGE PROCESSING                                              |    |

|   | 4.1 | Introd | uction                                                                                                                      | 52 |

|   | 4.2 | Couple | ed Spin Torque Oscillator array                                                                                             | 54 |

|   | 4.3 | Couple | ed Oscillator-based Distance Computation System                                                                             | 57 |

|   | 4.4 | Impler | nentation and results                                                                                                       | 65 |

|   | 4.5 | Applic | eations using an STO-based $L2^2$ norm $\ldots \ldots \ldots \ldots \ldots \ldots$                                          | 69 |

|   | 4.6 | Mater  | ials and Methods                                                                                                            | 74 |

## Page

|    |      | 4.6.1  | STO Fabrication.                                                | 74 |

|----|------|--------|-----------------------------------------------------------------|----|

|    |      | 4.6.2  | RF conditioning board                                           | 75 |

|    |      | 4.6.3  | Distribution analysis                                           | 76 |

|    | 4.7  | Supple | ementary Information                                            | 76 |

|    |      | 4.7.1  | Distribution detrending                                         | 76 |

|    |      | 4.7.2  | Signal conditioning board                                       | 78 |

|    |      | 4.7.3  | Addition of sinusoids at the same frequency but different phase | 79 |

|    | 4.8  | Summ   | ary                                                             | 80 |

| 5  | CON  | ICLUSI | IONS                                                            | 82 |

| Rl | EFER | ENCES  | 5                                                               | 84 |

| V] | ITA  |        |                                                                 | 94 |

## LIST OF TABLES

| Tabl | le                                                 | Pa | age |

|------|----------------------------------------------------|----|-----|

| 2.1  | SNN benchmarks                                     |    | 21  |

| 3.1  | Comparison with related works                      | •  | 46  |

| 4.1  | Comparison with CMOS distance computation circuits |    | 73  |

### LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                           | Pε | age |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 1.1  | Categories of emerging computing architectures (2016 IRDS) [1] $\ . \ . \ .$                                                                                                                                                 |    | 1   |

| 2.1  | <ul><li>(a) Multi layer perceptron SNN (b) Convolutional neural network SNN</li><li>(c) Integrate-and-Fire neuron</li></ul>                                                                                                  |    | 9   |

| 2.2  | (a) Typical spiking neural network (b) Mapping a spiking neural network on memristive crossbar                                                                                                                               |    | 10  |

| 2.3  | Block diagram of PLC transceiver                                                                                                                                                                                             |    | 13  |

| 2.4  | Distributed RLC PDN model                                                                                                                                                                                                    |    | 14  |

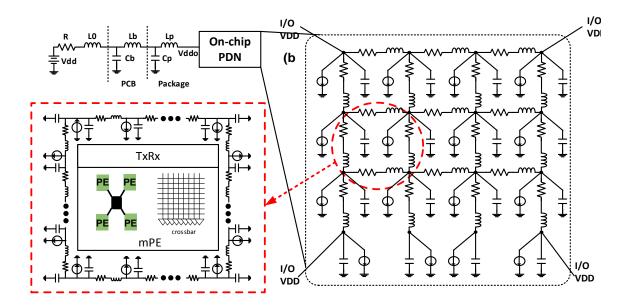

| 2.5  | (a) Processing Engine (PE) (b) Memrsitive crossbar architecture comprised of multiple PEs connected through hybrid PLC-NOC                                                                                                   |    | 16  |

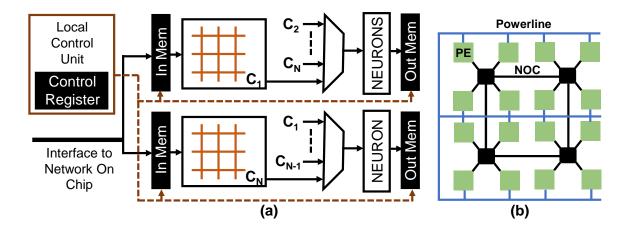

| 2.6  | SNN execution on multiple PEs showing intra-layer and inter-layer data transfers. Each PE can implement a $4 \times 4$ size layer                                                                                            |    | 17  |

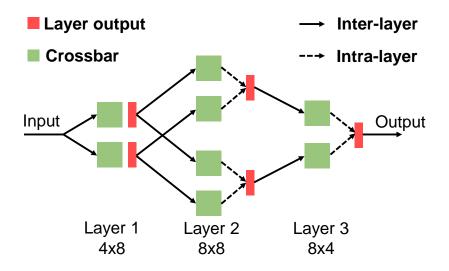

| 2.7  | (a) Channel loss, and (b) phase of the PDN channel for the longest path in 13x13 array of PEs using different metal layers                                                                                                   |    | 20  |

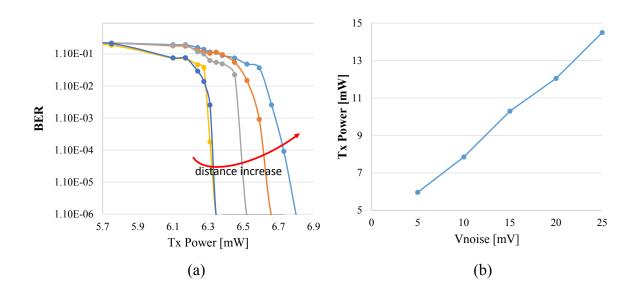

| 2.8  | (a) BER vs. Tx power $@V_{noise} = 5mV$ (b) The required Tx power vs. noise amplitude $\ldots \ldots \ldots$ |    | 21  |

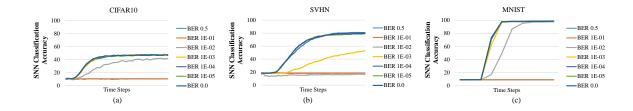

| 2.9  | Impact of BER incurred due to PLC on SNN classification accuracy for (a) CIFAR10 dataset (b) SVHN dataset and (c) MNIST dataset                                                                                              |    | 22  |

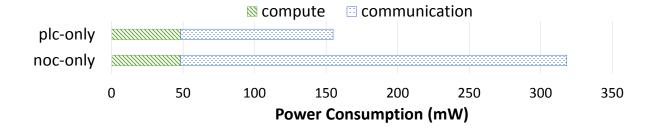

| 2.10 | Power consumption of chip                                                                                                                                                                                                    |    | 23  |

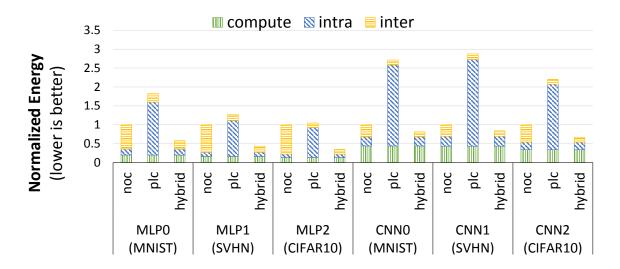

| 2.11 | Inference energy (batchsize = 1) $\ldots$                                                                                                                                                                                    |    | 24  |

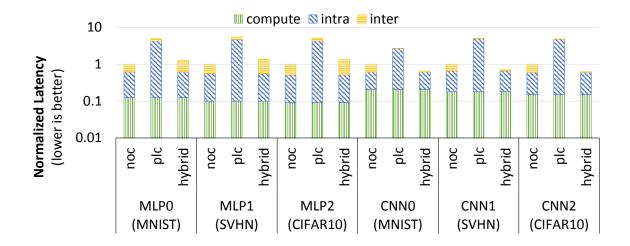

| 2.12 | Inference latency (batchsize = 1) $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                         |    | 26  |

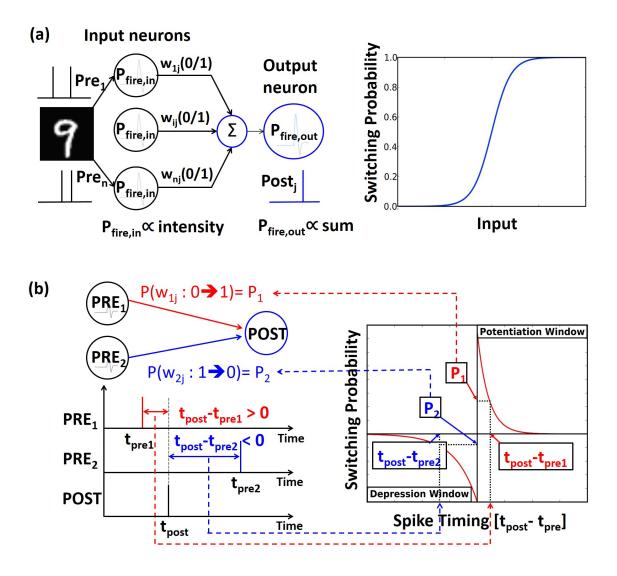

| 3.1  | (a) SNN composed of stochastic input and output neurons interconnected via binary synaptic weights. (b) Stochastic-STDP learning rule for binary synaptic weights                                                            |    | 31  |

| 3.2  | (a) Schematic of 6-bit 'stochastic bit' core. (b) Illustration of the pre-<br>charge and evaluation modes of operation of the 'stochastic bit'. (c) Timing<br>diagram illustrating the operation of the 'stochastic bit'     |    | 34  |

| 3.3  | Design of 'Stochastic bit' enabled (a) spiking neuron, and (b) binary synapse (stochastic during training and deterministic during inference).                                                                               |    | 37  |

## $\mathbf{Fi}$

| Figu | re                                                                                                                                                                                                                                                                                                                     | Pa | ge |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|

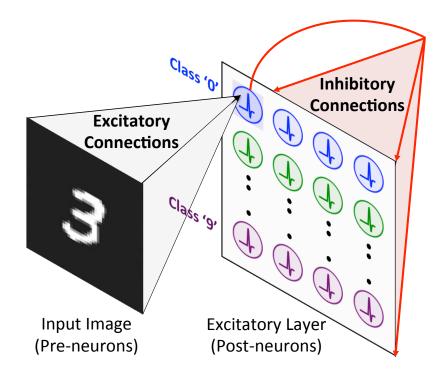

| 3.4  | Architecture of two-layer fully-connected sBSNN, with lateral inhibition, for object recognition.                                                                                                                                                                                                                      |    | 39 |

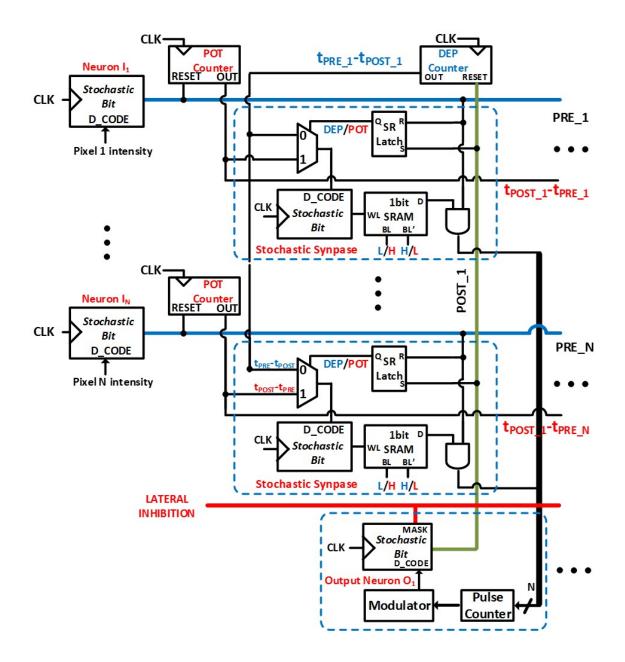

| 3.5  | System-level realization of two-layer fully-connected sBSNN with lateral inhibition.                                                                                                                                                                                                                                   |    | 40 |

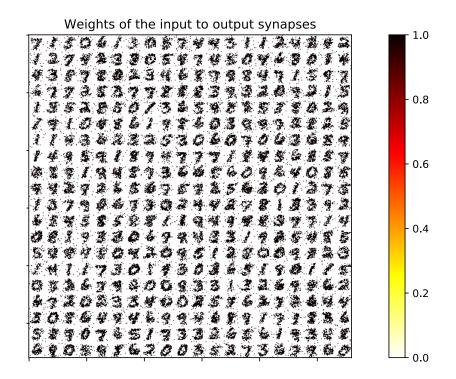

| 3.6  | MNIST digit representations $(28 \times 28 \text{ in dimension})$ learnt by a two-layer fully-connected sBSNN of 400 excitatory neurons (organized in $20 \times 20$ grid).                                                                                                                                            |    | 41 |

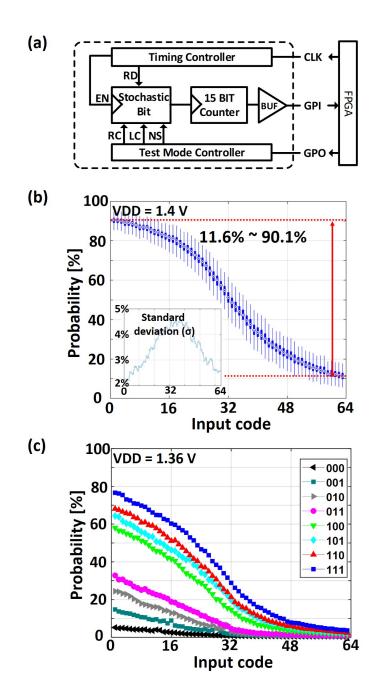

| 3.7  | (a) Measurement setup for the 'stochastic bit' design, which is interfaced with a FPGA board (b) The measured box plots of switching probability versus the input (PMOS) digital code, and its standard deviation, $\sigma$ (refer to the inset). (c) Switching probability dynamics for different 3-bit NMOS codes.   |    | 43 |

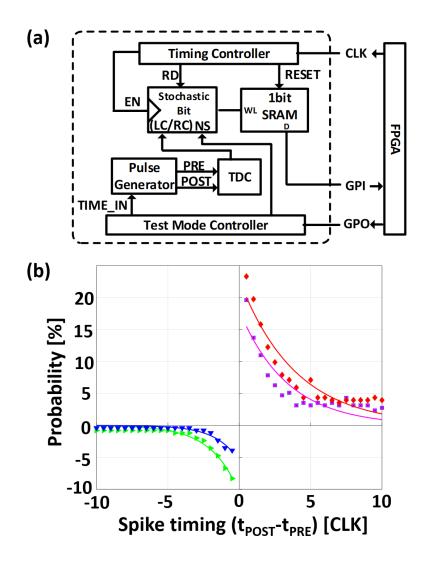

| 3.8  | (a) Measurement setup for the sSTDP dynamics needed to train a stochas-<br>tic binary synapse, which is interfaced with an FPGA board for generating<br>the clock and inputs (spike timing, TIME_IN), and monitoring the outputs<br>(state of SRAM cell). (b) The measured sSTDP curve for different NMOS<br>codes     |    | 44 |

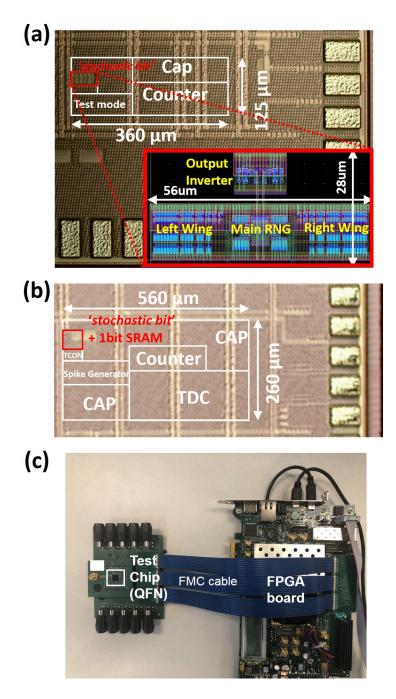

| 3.9  | (a) Die photo of the 'stochastic bit' and its layout (refer to the inset). (b) Die photo of the stochastic binary synapse composed of the 'stochastic bit' and 6T-SRAM bitcell. (c) Test chip measurement setup using FPGA                                                                                             |    | 48 |

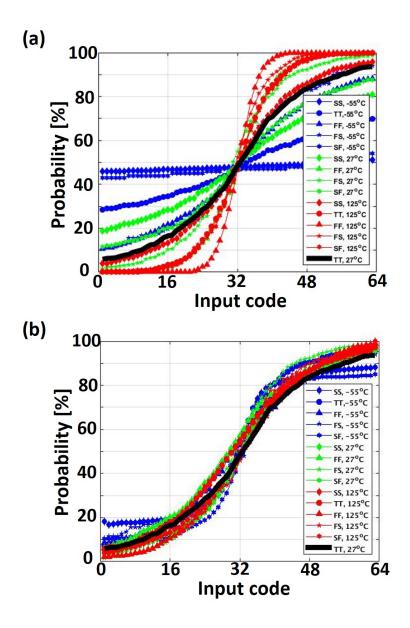

| 3.10 | (a) The switching probability curves with process (FF, TT, SS, FS, SF) and temperatures $(-55 \ ^{\circ}C, 27 \ ^{\circ}C, 125 \ ^{\circ}C)$ variations. (b) The compensated switching probability curves for all corners presented in (a).                                                                            |    | 50 |

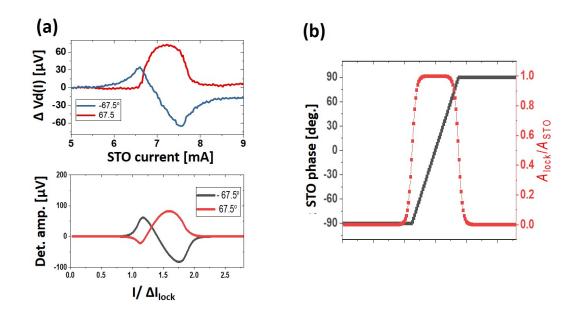

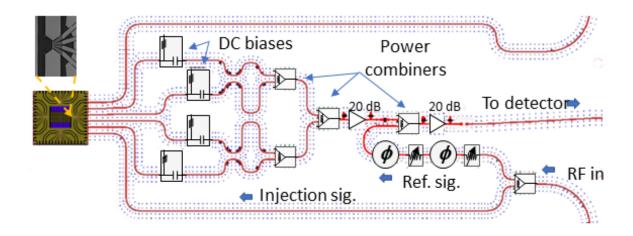

| 4.1  | (a) schematic of RF signal conditioning board for the spin torque oscillator<br>array. (b) Free-running response from single device. (c) Injection locking<br>response of similar device.                                                                                                                              |    | 55 |

| 4.2  | (a) Voltage from microwave diode across locking range for two different values of microwave phase reference. (b) <i>Top panel:</i> Inputs for amplitude and phase of STO signal for Phasor model below. <i>Bottom panel:</i> Phasor model of expect signal at $f = f_{inj}$ , for different values of reference phase. |    | 57 |

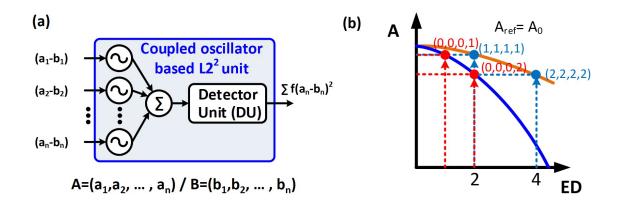

| 4.3  | (a) Block diagrams of coupled oscillator based $L2^2$ unit for a distance computing primitive (b) The cases showing the same A with different ED when the amplitude of reference signal is same as that of the STO signal.                                                                                             |    | 58 |

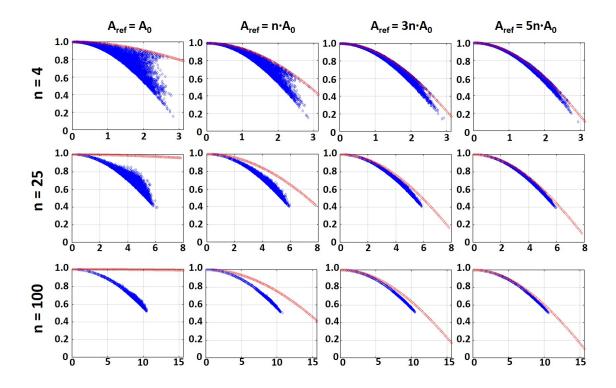

| 4.4  | The normalized amplitude, $A$ , versus ED for $n = 4$ , 25, and 100 with different $A_{ref} = A_0$ , $nA_0$ , $3nA_0$ , and $5nA_0$ .                                                                                                                                                                                  |    | 61 |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

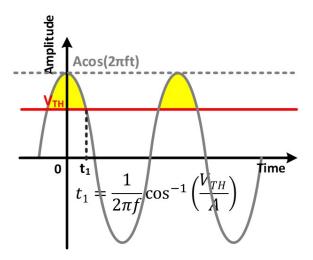

| 4.5  | The integration of a thresholded sinusoidal signal (The enclosed yellow area is proportional to the output voltage of the integrator)                                                                                                                                                                                                                                                                                                                                                                                                           | . 62 |

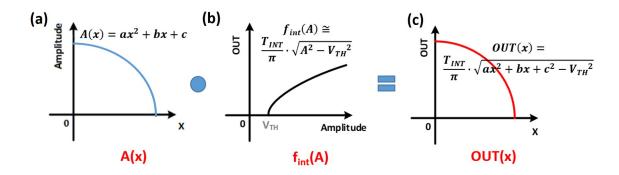

| 4.6  | The overall system equations. (a) The amplitude of the combined signal of the oscillator array, $A(x)$ . (b) The detector unit output voltage, $f_{int}$ . (c) The system output, $OUT(x)$ is the composition of the two functions $(A(x) \text{ and } f_{int})$ .                                                                                                                                                                                                                                                                              | . 63 |

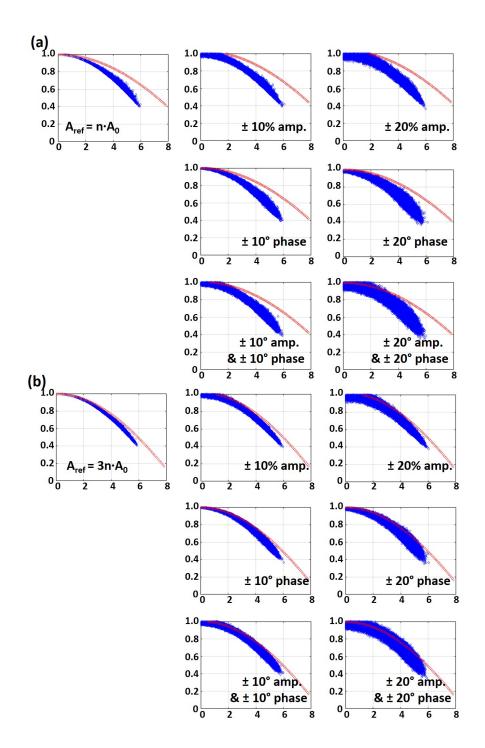

| 4.7  | The effect of phase $(10^{\circ}, 20^{\circ})$ and amplitude variations $(10\%, 20\%)$ . (a) $A_{ref} = nA_0$ , and (b) $A_{ref} = 3nA_0$ (n = 25)                                                                                                                                                                                                                                                                                                                                                                                              | . 64 |

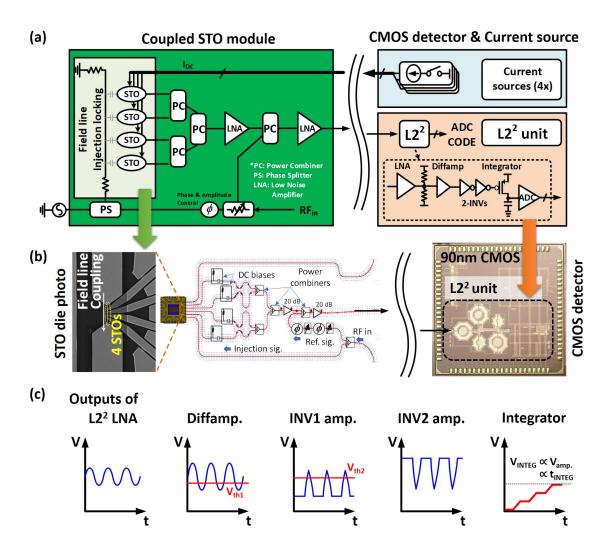

| 4.8  | The system implementation. (a) Block diagram for entire system, and (b) its implementation. (c) The expected signals at different nodes in the CMOS detector module                                                                                                                                                                                                                                                                                                                                                                             | . 66 |

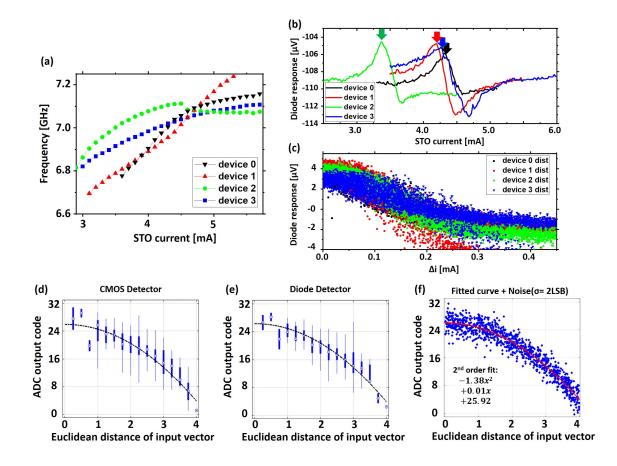

| 4.9  | (a) The fitted response of all devices, showing overlap at 7 GHz operating point. (b) Response curves for all devices. Arrows indicate the reference bias points. (c) Distribution of diode response for each device, 5000 test $\Delta$ I points. Box plots of response of 4 device array for test vectors within $\Delta I < 230 \ \mu A$ , (d) with CMOS detector and (e) with Diode detector plotted vs. ED (defined as mA/10 <sup>-4</sup> mA). (f) The fitted curve from (e) with normal distributed noise ( $\sigma$ of 2 LSB ADC code). | . 67 |

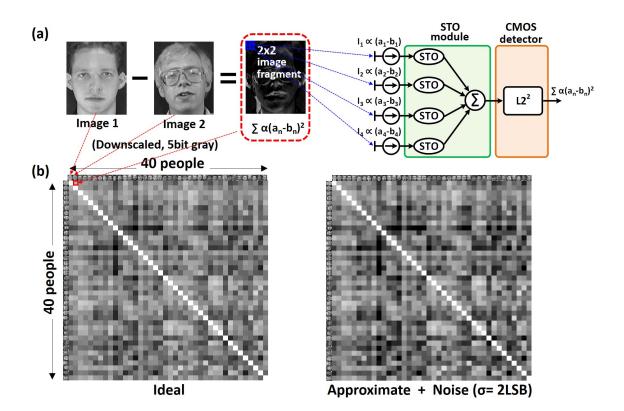

| 4.10 | (a) $L2^2$ distance computation with AT&T face database [112]. (b) The Ideal case (left) calculated mathematically and the approximate case (right) are shown using the fitting curve from the measured CMOS detector (Fig. 4.9(d)), with normal distributed noise ( $\sigma$ of 2 LSB ADC code) is shown.                                                                                                                                                                                                                                      | . 70 |

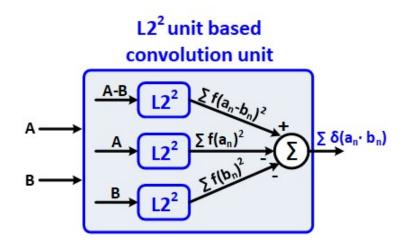

| 4.11 | Block diagrams for a convolution computing primitive based on ref. [105, 114].                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 71 |

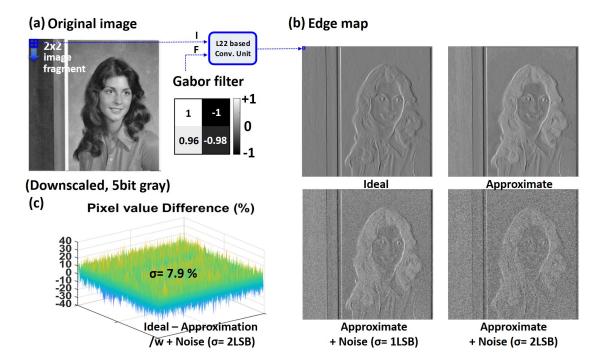

| 4.12 | (a) Edge detection on image (4.1.04 from SIPI database [115]) with the proposed computing primitive. (b) The edge map results from simulation (Ideal), experiment with the fitting curve (Approximate), and experiment with the fitting curve in addition to $\sigma$ of 1 and 2 LSB noise. (c) The difference of the edge map between the ideal case and the approximation in addition to $\sigma$ of 2 LSB noise.                                                                                                                             | . 72 |

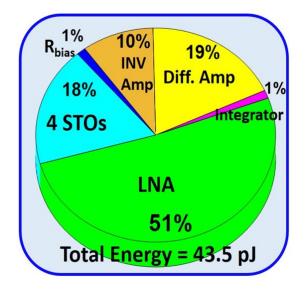

| 4.13 | The power breakdown of hybrid system for 4-dimensional case                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 73 |

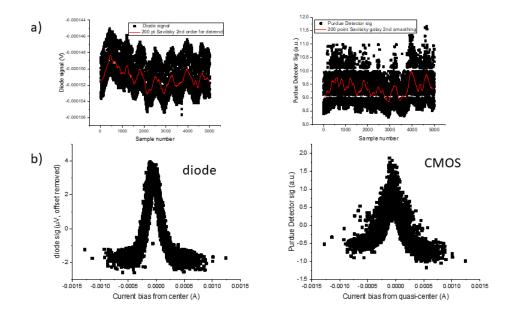

|      | Response of detectors to phase locking of a single STO device for both diode and CMOS detectors.(a) shows response as a function of time, for which random offsets are applied to the device. (b) shows the resultant response vs. current.                                                                                                                                                                                                                                                                                                     | . 77 |

| 4.15 | Layout of microwave signal conditioning board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 78 |

#### ABSTRACT

Koo, Minsuk Ph.D., Purdue University, May 2020. Energy Efficient Neuromorphic Computing: Circuits, Interconnects and Architecture. Major Professor: Roy K. Professor.

Neuromorphic computing has gained tremendous interest because of its ability to overcome the limitations of traditional signal processing algorithms in data intensive applications such as image recognition, video analytics, or language translation. The new computing paradigm is built with the goal of achieving high energy efficiency, comparable to biological systems. To achieve such energy efficiency, there is a need to explore new neuro-mimetic devices, circuits, and architecture, along with new learning algorithms. To that effect, we propose two main approaches:

First, we explore an energy-efficient hardware implementation of a bio-plausible Spiking Neural Network (SNN). The key highlights of our proposed system for SNNs are 1) addressing connectivity issues arising from Network On Chip (NOC)-based SNNs, and 2) proposing stochastic CMOS binary SNNs using biased random number generator (BRNG). On-chip Power Line Communication (PLC) is proposed to address the connectivity issues in NOC-based SNNs. PLC can use the on-chip power lines augmented with low-overhead receiver and transmitter to communicate data between neurons that are spatially far apart. We also propose a CMOS 'stochastic-bit' with on-chip stochastic Spike Timing Dependent Plasticity (sSTDP) based learning for memory-compressed binary SNNs. A chip was fabricated in 90 nm CMOS process to demonstrate memory-efficient reconfigurable on-chip learning using sSTDP training.

Second, we explored coupled oscillatory systems for distance computation and convolution operation. Recent research on nano-oscillators has shown the possibility of using coupled oscillator networks as a core computing primitive for analog/nonBoolean computations. Spin-torque oscillator (STO) can be an attractive candidate for such oscillators because it is CMOS compatible, highly integratable, scalable, and frequency/phase tunable. Based on these promising features, we propose a new coupled-oscillator based architecture for hybrid spintronic/CMOS hardware that computes multi-dimensional norm. The hybrid system composed of an array of four injection-locked STOs and a CMOS detector is experimentally demonstrated. Energy and scaling analysis shows that the proposed STO-based coupled oscillatory system has higher energy efficiency compared to the CMOS-based system, and an order of magnitude faster computation speed in distance computation for high dimensional input vectors.

### 1. INTRODUCTION

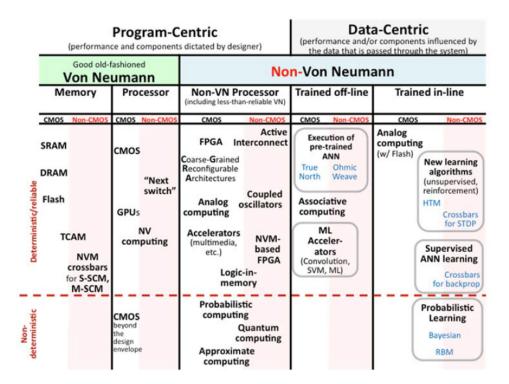

Even with unprecedented success driven by device scaling, solutions to optimization, recognition, and classification problems based on Von-Neumann architecture turn out to be very inefficient. Moreover, the scaling-down of CMOS technology is approaching its fundamental limit. Hence, researchers are exploring new possibilities from novel devices to non von-Neumann like architectures to achieve performance beyond CMOS scaling as shown in Fig. 1.1.

Fig. 1.1. Categories of emerging computing architectures (2016 IRDS) [1]

Neuromorphic computing that attempts to solve the problems in a "preferred way of nature" has acquired tremendous interest because of its ability to overcome the limitations of von-Neumann systems in data intensive applications. The key inspiration behind the development of such neuro-inspired computing systems comes from its high computing and energy efficiency to be comparable to biological systems. Hence, emerging devices that can mimic neurons and synapses, neuromorphic algorithms, and new architectures need to be explored individually and collectively to obtain such high energy efficiency.

Spiking Neural Networks (SNNs) offer a promising solution towards realizing energy-efficient neuromorphic systems. SNNs consider the presence and timing of spikes as the means of communication and neural computation. On account of spikebased event-driven computing capability and localized learning using Spike Timing Dependent Plasticity (STDP), SNNs are regarded as the third generation neural network [2]. However, the proper algorithm and architecture for SNNs still remain to be explored. This motivates us to investigate energy efficiency of the system for SNNs in terms of circuits, interconnects and architecture.

On the other hand, the paradigm of 'let physics do the computing' has also motivated researchers to look at alternative computing models that explore the use of emerging devices as functional units for better energy efficiency and speed. One such alternative model is based on the coupled oscillator network in which the oscillator array is used to compute (say) "similarity" between two multi-dimensional vectors. Such coupled oscillatory networks are widely found in nature such as pendulum clocks on a wall [3], flashing fireflies [4], animal flocking [5], coupled oscillations in the human heart and brain [6,7]. Spin-torque oscillator (STO) is an attractive candidate for such alternative computing models because it is CMOS compatible, highly integratable, scalable, and frequency/phase tunable. Based on these promising features, we are motivated to investigate a new coupled-oscillator based computing architecture that computes multi-dimensional norm.

The thesis also explores how emerging technologies like memristors [8–10] and memristive cross-bars (to do efficient dot-products, a core computing primitive for neuromorphic computing), and deeply scaled CMOS technologies can be used in novel computing architectures for efficient learning and inference. The rest of the dissertation is organized as follows. In chapter 2, we focused on connectivity issues arising from Network On Chip (NOC)-based SNNs. The brainlike connectivity requires modification to typical NoC architectures. While NOCs can provide very high throughput, they suffer from high power and area requirements and lacks the connectivity required for neural computing. We propose augmenting local connectivity of NoC computing units with Power Line Communication (PLC) to communicate data between computing units that are spatially further apart. The intrinsic broadcast based communication in PLC not only brings in higher connectivity but also enables energy efficient communication, where data sent over power line can be transmitted to multiple neurons in a single cycle.

In chapter 3, we propose stochastic bit enabled binary SNN with on-chip STDP learning for memory-compressed neuromorphic computing. The binary SNN composed of stochastic neurons and binary synapses are programmed stochastically during training. We present an energy-efficient realization of the binary SNN using Biased Random Number Generator (BRNG) based 'stochastic bits' fabricated in 90nm CMOS process for on-chip pattern recognition. The proposed BRNG enabled binary SNN, with high power efficiency of 89.49 TOPS/Watt for two-layer fully-connected SNN of 400 neurons, offers a potential solution for energy-efficient edge computing with on-chip intelligence.

In chapter 4, we experimentally demonstrated a distance computing primitive based on a STO-based coupled oscillator array. We have shown that the combination of injection locking scheme and its interference with a reference signal can realize the Euclidean distance computation unit. The performance of the system as an  $L2^2$  unit was measured by applying randomly generated test input vectors as bias current to the STOs. The characteristic curve from the experiment approximates an  $L2^2$  norm which, in turn, is used as input to simulations that demonstrate the hybrid system as both a distance metric and a convolution computational primitive for image processing applications. Energy and scaling analyses show that the STO-based coupled oscillatory system has higher efficiency than the CMOS-based system with an order of magnitude faster computation speed in distance computation for high dimensional input vectors. Modest improvements in STO critical currents and magneto-resistance (through the use of magnetic tunnel junctions) can make oscillator-based systems even more attractive.

Finally, chapter 5 summarizes the thesis and discusses the future work.

## 2. POWERLINE COMMUNICATION FOR ENHANCED CONNECTIVITY IN NEUROMORPHIC SYSTEMS

Neuromorphic Computing (NC) has acquired tremendous interest because of its ability to overcome the limitations of von-Neumann systems in data intensive applications. NC systems are inspired from the human brain, which combines storage (synapse) and compute (neuron) to circumvent the memory bottlenecks in von-Neumann computing. Note, human brain consists of densely connected neurons, where each neuron can connect to 1000s of synapses [11]. Such dense connectivity is the key to obtaining high classification accuracies in NC systems such as the Spiking Neural Networks (SNNs), as connectivity enables hierarchical learning with large number of features in each hierarchy.

Past research has focused on many-core architectures which implement synapses with memristive crossbars to overcome the memory bottlenecks and enable efficient compute. However, mimicking brain-like connectivity poses significant challenges. This is because typical computation cores in a many-core architecture are connected with a Network On Chip (NOC). While NOCs can provide very high throughput, they suffer from high power and area requirements which decimates the benefits of efficient synapse implementation with memristive crossbars. In this chapter, we propose a Power Line Communication (PLC) based architecture built with memristive crossbars for SNNs.

PLC can use the on-chip power lines augmented with low-overhead receiver and transmitter to communicate data between neurons. This removes the high area overhead due to channels and routers present in an NOC. Further, the intrinsic broadcast based communication in PLC enables energy efficient communication, where data sent over power line can be transmitted to multiple neurons in a single cycle. Hence, PLC can enable dense connectivity required in SNNs, while preserving the efficiency of memristive crossbars. We perform evaluations of SNNs ranging in scale from 1M - 10M synapses to demonstrate the efficiency of PLC based system. Also, we propose a hybrid PLC - NOC based design which can achieve high throughput along with area and energy efficiency.

#### 2.1 Introduction

Deep Neural Networks (DNN) are a class of machine learning algorithms and are extensively deployed in several learning tasks such as computer vision [12], speech and language processing [13], medical imaging [14], robotics [15] and gameplay [16]. DNNs are motivated from human brain and consist of densely connected neurons and synapses organized in a hierarchical fashion. This hierarchical nature and dense connectivity enable feature extraction from an input and its subsequent classification. The key feature that has enabled DNNs to achieve unprecedented performance in complex tasks is the ability to design and train large scale (in terms of neurons, synapses and layers) models. For example, in 1998, LeCun et al. used a model with less than ~1M synapses for simple digit recognition tasks [17]. In 2012, Krizhevsky et al. proposed AlexNet with ~60M synapses to recognize complex natural images [18]. Recently, Karpathy et al. proposed a DNN to convert image to natural language using ~230M synapses [19].

Despite the success of DNN, their execution on von-Neumann systems suffer from extremely high energy consumption. This has motivated research in energy-efficient design of DNNs using various algorithmic and hardware techniques [20–22]. One of the promising pathways is design of biologically plausible algorithms namely Spiking Neural Networks (SNN) [2, 11, 23]. Unlike artificial neural networks (ANNs) which use real-valued inputs, SNNs communicate data in the from of spikes (0/1). The spike based inputs simplify the computations to simple add and accumulation instead of multiply-add and accumulate in ANN. Further, the resulting input sparsity in data enables event-driven computations which alleviate unnecessary memory accesses and computations to bolster the energy benefits.

To this end, past work have looked into deep SNN designs in different application domains and achieved near DNN classification accuracies [24–27]. However, their acceleration on von-Neumann machines built with CMOS technology suffers from memory bottlenecks. This is because SNNs are data-intensive applications with simpler compute requirements. Consequently, the frequent movement of data between memory and compute units on von-Neumann systems results in high data access energy and latency. Also, the ever growing model size increases the memory demands for storing the synapses. As a result, researchers have focused on designing applicationspecific accelerators based on CMOS technology to enable energy-efficient execution of SNNs [11, 23]. However, the inherent mismatch between CMOS technology and compute primitives required in SNNs (neurons and synapses) limits their benefits. For instance, a CMOS implementation of synapse requires more than a dozen of transistors [20].

To this effect, researchers have focused on post-CMOS technology based neuromorphic computing. Consequently, memristive crossbars have been proposed which can store synapses and perform dot-product computations in a single time step. A memristive crossbar is comprised of memristors at each cross-point that can encode a multi-bit value using one device. Upon applying an input voltage on the crossbar's row, the resulting output current on a column is equal to the weighted summation of input and synapse on the column. Subsequently, several past works [20, 28–32] have utilized the intrinsic suitability of memristive crossbars to design DNN accelerators.

Typical memristive crossbars based accelerators use array of Processing Engines (PE) connected together with a Network On Chip (NOC). The PEs are built with crossbars to enable synaptic storage and weighted summation computations. An NOC connects these PEs to realize the connectivity structure in DNNs. However, typical NOCs have significantly higher area and power consumption, thereby reducing the storage and compute benefits that can be harnessed from memristive crossbars.

Further, data transfer in typical NOC requires several hops between routers which increases the latency and energy consumption. Consequently, this either restricts the algorithm designers to use under-performing SNNs, or incur high energy-latency costs.

To address these limitations, we propose a Power Line Communication (PLC) based approach to enable efficient data transfer between PEs in a spatial architecture. PLC uses the on-chip power lines augmented with low overhead receiver and transmitter to enable communication between PEs. The minimal hardware overhead incurred, preserves the benefits from memristive crossbars. Further, the inherent broadcast based nature of PLC, where a data on power line is received by all PEs on the chip maximizes the input reuse pattern common to DNNs. However, the data transfer throughput obtained from PLC is lower than typical NOCs. Hence, we also propose a hybrid PLC-NOC based memristive crossbar architecture to maximize throughput and boost connectivity. A high throughput NOC enables fast communication between a cluster of PEs located over short-distance. On the other hand, the PLC network enables long-distance communication to boost the overall connectivity between PEs.

In summary, we make the following contributions:

- **powerline based communication** approach to enhance the connectivity for achieving higher classification accuracy in neuromorphic systems.

- hybrid PLC-NOC based memristive architecture for obtaining high throughput and energy efficient acceleration of SNNs.

- evaluate the design over a wide range of image recognition applications to study the energy and performance benefits.

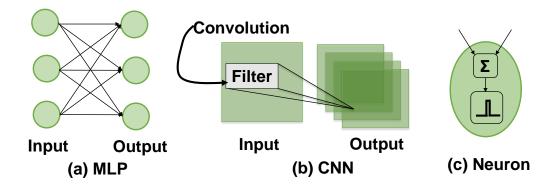

Fig. 2.1. (a) Multi layer perceptron SNN (b) Convolutional neural network SNN (c) Integrate-and-Fire neuron

#### 2.2 Background

#### 2.2.1 Spiking Neural Network

SNN is regarded as the third generation neural network [2]. It is a more bioplausible version of classical neural networks and involves spike based communication between neurons. Each input to an SNN is encoded as a Poisson spike train, where the spike frequency represents pixel intensity. At a particular instant, each spike is propagated through the layers of the network while the neurons accumulate the spikes over time as its membrane potential. A neuron spikes when the membrane potential exceeds a threshold. Subsequently, the output spike is sent to the neurons in the next layer of SNN. The deep SNN topologies used in this work are Multi Layer Perceptrons (MLP) and Convolutional Neural Networks (CNN). An MLP, shown in Fig. 2.1(a), is a multi-layered SNN in which all neurons in a layer are connected to all neurons in the previous layer. A CNN, shown in Fig. 2.1(b), is also a multilayered SNN composed of alternating convolution and sub-sampling layers. As shown in Fig. 2.1(c), a typical spiking neuron does an accumulation operation followed by thresholding operation. The spiking neuron model used in this work is the Integrateand-Fire (IF) model. Note that, our work focuses on the testing/computation of the SNN and assumes that the memristive crossbars have already been programmed with

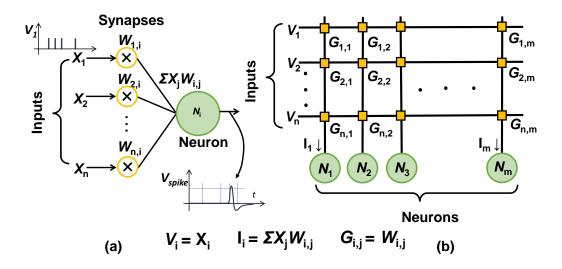

Fig. 2.2. (a) Typical spiking neural network (b) Mapping a spiking neural network on memristive crossbar

the trained weights. Hence, we do not consider energy or latency associated with writing the memristors.

#### 2.2.2 Memristive Crossbar and Past Work

Fig. 2.2(a) shows a 2-layer fully connected SNN. Fig. 2.2(b) shows the connectivity structure/matrix (from Fig. 2(a)) mapped onto a memristive crossbar. The memristive devices at its cross-points encode the synaptic weights of the SNN. A memristive crossbar receives voltage inputs at its rows and the resulting current output at any column is the weighted summation of the encoded weights at that column and the input voltage. This is a direct consequence of the Kirchhoff's law as the current output into a column from any cross-point will be the product of the conductance at that cross-point and the voltage across it. Thus, a memristive crossbar is an analog "dot-product" computation unit. Further, each crossbar is interfaced with neurons that receive the input current and accumulate membrane voltage over time.

Several previous works have explored memristive crossbar based architectures for accelerating DNNs. ISAAC [29] designs digital computation units with ReRAM crossbars for accelerating CNNs. PRIME [30] proposes a crossbar based design for CNNs, where a crossbar is logically partitioned to be used for regular memory storage and computations. RESPARC [20] proposes a hierarchical architecture built with crossbars for executing SNNs. Further, TIME [31] and PipeLayer [32] focus on training DNNs using memristive crossbars. This chapter complements the previous works by enabling efficient communication between processing units to enhance the utility and efficiency of crossbar based architectures.

#### 2.3 Power Line Communication

#### 2.3.1 Motivation

Spatial many-core architectures built with emerging post-CMOS technologies have been extensively explored for DNNs, owing to their ability to exploit data parallel nature of multi-layered neural networks [20, 29–32]. However, the NOC size scales linearly with the number of cores, which leads to high energy consumption in communication between distantly located cores. As a result, researchers have explored techniques for efficient multi-hop communication to optimize the high latency and power consumption involved in moving data between two far apart cores in a manycore architecture.

For conventional NOCs, different ways to improve channel utilization such as virtual channels, bypass routers, and the novel topologies have been studied [33], [34]. On the other hand, using new materials rather than metal wires have been studied, such as three-dimensional integration, nanophotonic communication and on-chip wireless links [35–37]. We propose PLC as a new channel that uses metal wires not only for delivering power but also for carrying data to different nodes in a chip. Further, PLC enables single hop links, thanks to the inherent broadcast nature of on-chip powerlines. PLC has lower data rate compared to typical interconnects such as, conventional NOCs and wireless links. However, the low latency and low power consumption for long distance communication along with with small area penalty make PLC an attractive solution especially in many-core neuromorphic systems. Recent works have shown the use of PLC at integrated-circuit level for the purpose of design for testability (DFT) on CMOS microprocessors [38, 39].

#### 2.3.2 Challenges

PLC mainly draws advantages from 1) dual usage, and 2) ubiquitous accessibility of Power Distribution Network (PDN). Since PLC uses the existing power supply line, it does not cost extra to obtain an additional channel for communication. Further, every circuit at any node connects to the power line and can receive data from it, thereby enabling data broadcast. Despite the apparent advantages of PLC, there are challenges that limit its applicability. First, loading data on top of power line, which works like a noise to PDN, is conflicting to the goal of a robust PDN design. Second, PLC channel suffers from simultaneous switching noise (SSN) resulting from the large current drawn by the switching devices. Third, ubiquitous accessibility to any internal nodes based on wide area network costs large power consumption to load data on top of the huge PDN.

#### 2.3.3 PLC based neuromorphic system design

Neuromorphic algorithm such as SNNs are inherently error resilient and can harness the advantages from PLC with little or no accuracy loss [40]. Recall, typical neural network accuracy increases with network size, thereby increasing the connectivity requirements for their on-chip deployment [22]. Additionally, typical SNNs have high data sparsity and input sharing which enable low data rates and enhance the benefits of broadcast based interconnects. Thus, PLC based neuromorphic system design can enable the needed connectivity to enable large scale SNN acceleration in an efficient way. Next we discuss the two components of our PLC design namely 1) transceiver, and 2) PDN.

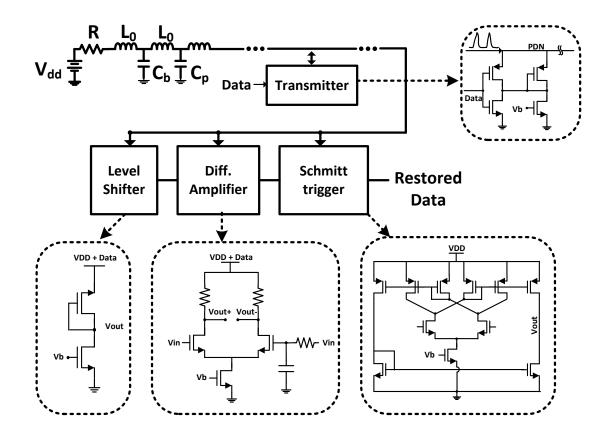

Fig. 2.3. Block diagram of PLC transceiver

#### Transceiver

Transceiver facilitates the send and receive of data between different processing engines (PEs) in a neuromorphic architecture (discussed in Section 2.4). Depending on the data to be sent, the transmitter (Tx) induces small glitches on the powerline by drawing current. This mechanism of loading data is similar to the way SSN gets added to a powerline. To distinguish the data from noise at the receiver side, glitches caused by data should be larger than the ones caused by SSN. In other words, a more noisy powerline would require larger amount of current (and power) for data transmission. Hence, keeping the powerline quiet is beneficial for PLC to achieve lowpower communication. We achieve this by separating the powerline for noisy/clocked

Fig. 2.4. Distributed RLC PDN model

blocks, for example, control unit, peripherals etc. from the non-noisy blocks like neurons and crossbars. In other words, the powerline used in communication connects to SSN free asynchronous components.

At the receiver side, a level shifter lowers the dc level of the signal to around half of the supply voltage (shown in Fig. 2.3). The circuit is a common source amplifier with a diode-connected load. In contrast to a typical amplifier, the power supply rejection ratio (PSRR) of level shifter is set to be small, in order to acquire the data from the signal on powerline [39]. Next, the level shifted signal is applied to a differential amplifier, in which one of the inputs is connected to an RC low pass filter for alleviating the dc offset voltage. Finally, the amplified signal goes into a differential Schmitt trigger for restoring the original data.

#### Power distribution network

We design a PDN comprised of power supply source, Printed Circuit Board (PCB), and on-chip power grid that accurately models the channel for PLC. The PCB and package parasitics are considered as a lumped model. However, a lumped model for on-chip power grid is not sufficient to estimate the desired characteristics of delay and attenuation at different locations of the PDN. Therefore, a distributed RLC model for on-chip power grid has been designed (shown in Fig. 2.4). Here,  $V_{DD}$ , R and  $L_0$  are power supply source, the resistive impedance, and the inductance of Voltage Regulator Module (VRM) respectively. The parasitics of R,L and C are modeled for on chip power grid using Equations 2.1, 2.2, and 2.3 [41]. Rs,  $\mu$ , and  $\epsilon$  are sheet resistance, permeability, and permittivity respectively, where l, w, t, and h are length, width, thickness, and height from substrate.

$$R = R_s(\frac{l}{w}) \tag{2.1}$$

$$L = \frac{\mu}{2\pi} \ln\left(\frac{8h}{w} + \frac{w}{4h}\right) \tag{2.2}$$

$$C = \epsilon \left[ \left(\frac{w}{h}\right) + 0.77 + 1.06 \left(\frac{w}{h}\right)^{0.25} + 1.06 \left(\frac{t}{h}\right)^{0.5} \right]$$

(2.3)

#### 2.4 Hybrid PLC-NOC based Architecture

We implement a hierarchical architecture using memristive crossbars as shown in Fig. 2.5. As shown in past works, a hierarchical architecture can efficiently exploit the available data-parallelism in SNNs [20]. Our novelty lies in proposing a hybrid PLC-NOC based technique to enable efficient communication between PEs in a tile.

Fig. 2.5(a) shows the organization of a Processing Engine (PE). A PE consists of multiple memristive crossbars, each interfaced with an input memory (InMem), neuron block (Neuron) and output memory (OutMem). Data received by a PE can

Fig. 2.5. (a) Processing Engine (PE) (b) Memrsitive crossbar architecture comprised of multiple PEs connected through hybrid PLC-NOC

be stored in one or multiple InMem depending on the input sharing between crossbars in a PE. For instance, crossbars on a PE mapped to different output neurons within an SNN layer will share inputs. Additionally, multiple crossbars in a PE can accumulate their outputs on different neuron blocks in a PE to produce final outputs. Lastly, outputs are sent to PEs mapped to the next layer of SNN.

Fig. 2.5(b) shows the architecture with multiple PEs connected through hybrid PLC-NOC. An SNN is partitioned to map the weights in different layers on different PEs. Further, within an SNN layer, weights are mapped across multiple crossbars on one or more PEs. This is because, typical crossbar sizes are an order of magnitude smaller than SNN layer sizes. Crossbar sizes can be limited by parasitic effects, sneak paths and peripheral overheads [20, 42]. Consequently, an SNN execution on memristive crossbar architecture can be subdivided into three operations 1) crossbar computation, 2) *intra-layer data transfer*, and 3) *inter-layer data transfer* (illustrated in Fig. 2.6).

We propose a hybrid PLC-NOC based architecture that leverages PLC and NOC for inter-layer and intra-layer communication, respectively. An NOC-only design consumes significant energy consumption ( $\geq \sim 60\%$  of the total energy) due to inter-layer

Fig. 2.6. SNN execution on multiple PEs showing intra-layer and inter-layer data transfers. Each PE can implement a  $4 \times 4$  size layer.

transfers (shown in Sec. 2.6.4). To overcome this limitation of NOC-only design, PLC enables efficient inter-layer communication. PLC based broadcast provides a natural fit for one-to-many nature of *inter-layer data transfers*. Further, NOC provides a high throughput communication medium for *intra-layer data transfers*. Thus, the hybrid approach preserves inference latency while reducing the energy consumption.

Inter-layer data transfers implement SNN execution by propagating input through multiple layers to compute the classification output. Such transfers are one-to-many in nature where a PE mapped to previous layer sends its output data to multiple PEs mapping the next layer (shown in Fig. 2.6, Layer 2). This is because typical SNNs have input sharing where, neurons in the next layer share the outputs produced by the previous layer. PLC enables harnessing this input reuse in SNNs by broadcasting output data over power lines, which is received by next layer PEs in a single time step. On the contrary, an NOC based inter-layer data transfer will require multiple data transfers of same input data, where each transfer sends data to one PE in the next layer. This leads to increased energy consumption. Further, data transfer over NOC typically incurs multiple hops, owing to the large number of PEs (typically 100s) required to map any given layer. This leads to increased latency and energy consumption.

Intra-layer data transfers occur when neuron fan-in exceeds the crossbar size. Crossbars in multiple PEs compute partial products, which are aggregated through intra-layer data transfers to compute final outputs. These transfers are one-to-one, and occur between closely located PEs (typically 4-8). Further, multiple intra-layer transfers occur in parallel to compute multiple output neurons concurrently. Hence, PLC is not suitable for intra-layer communication as only one data can be transmitted over powerline at any given time. However, NOC based intra-layer transfers enable parallel communication (one-to-one) and are energy efficient owing to the closely located PEs.

#### 2.5 Experimental Methodology

#### 2.5.1 Neuromorphic architecture

The RLC parameters for modelling the on-chip PDN are taken from IBM 45nm process, which uses some fitting parameters in addition to the Equations 2.1, 2.2 and 2.3 in Section 2.3. A set of typical values for the PCB board and package parasitics is provided in [43]. A  $1960\mu m \times 1960\mu m$  power grid is estimated to cover a  $13\times13$  array of PEs.

We modeled PDNs using different metal layers and analyzed the channel loss and the phase response, which are represented by the magnitude and the phase of S21, respectively (Fig. 2.7). Higher metal layers have higher metal thickness and less parasitic resistance. Thus, powerline is typically designed with the highest metal layer in order to minimize the voltage drop between power nodes. It can be observed that PDN modeling using 9<sup>th</sup> and 10<sup>th</sup> metal layers (out of 11 layers) shows the lowest channel loss. However, the 9<sup>th</sup> metal layer is 10× thicker than the 1<sup>st</sup> metal layer, which makes it unsuitable for low-power requirements. Therefore, in this work, we use the 6<sup>th</sup> and the 7<sup>th</sup> metal layers, which are 2× thicker than the 1<sup>st</sup> metal layer. The PDN model is designed as rectangular power grid meshes, and it surrounds a PE (in the PE-array) of size 0.34  $mm^2$ . Further, each PE has a transceiver (area  $\leq 0.001$   $mm^2$ ) located at the center of its power grid mesh.

The overall PE design was adopted from RESPARC [20]. Cycle-level NOC simulations were performed with Booksim2 [44] and Orion2 [45] was used for power measurements.

#### 2.5.2 PLC channel quality

In contrast to digital data links in an NOC, PLC based communication is analog in nature. Therefore, channel's robustness needs to be guaranteed in terms of Bit Error Rate (BER), that depends on channel noise, signal attenuation between the communicating nodes, PDN modeling parameters, the size of decoupling capacitors etc. Effectively, the PLC channel should satisfy a level of BER ( $< 10^{-5}$ ), which does not degrade output quality (SNN classification accuracy), irrespective of the distance between any two PEs considered for communication. BER primarily depends on the level of power supply noise (primarily SSN). Hence, the required transmitter power is determined by the amplitude of the noise on the powerline. Recall, our proposed PLC channel provides power to non-synchronous (non-clocked) components only, namely crossbar arrays and neurons. Thus, PLC will get affected when the neurons produce an output spike. However, for the worst case analysis, we assumed that the SSN noise has same frequency as the data bandwidth, because in-band noise degrades the channel quality significantly. Subsequently, for estimating the signal power required for a given noise level, we add an ideal current source to every line segment, such that its switching frequency matches the PLC bandwidth.

Typically, decoupling capacitors are added to counter the effect of switching noise. However, in our design, we purposely generate the switching noise to use it in PLC. Thus, the channel bandwidth is also affected by the decoupling capacitance. Each PE consumes an average power of 3mA and 20pF of decoupling capacitance is assumed

Fig. 2.7. (a) Channel loss, and (b) phase of the PDN channel for the longest path in 13x13 array of PEs using different metal layers

at the center of every PE. Considering the aforementioned requirements, we use a 1Gbps data rate for PLC for our simulations.

#### 2.5.3 Benchmarks

We construct MLP and CNN based SNNs for three popular image recognition datasets - MNIST [46], CIFAR-10 [47] and SVHN [48]. The SNNs were trained using supervised learning approach proposed in [24], wherein an ANN is trained using error back-propagation followed by its conversion to SNN [24]. Table 2.1 details the evaluated SNN benchmarks. We use 4-bit precision for inputs and weights, which obtains high classification accuracy on the SNN benchmarks [20].

#### 2.6 Results

This section discusses the Tx power requirements for PLC. Further, the energy and latency of hybrid PLC-NOC based neuromorphic architecture is analyzed compared to PLC-only and NOC-only systems. Our analysis focuses on the inference or testing

| Application           | Dataset | Layers | Neurons | Synapses |

|-----------------------|---------|--------|---------|----------|

| Digit recognition     | MLP0    | 3      | 2378    | 1902400  |

|                       | CNN0    | 3      | 66778   | 1484288  |

| House recognition     | MLP1    | 3      | 2778    | 2778000  |

|                       | CNN1    | 3      | 124570  | 2941952  |

| Object classification | MLP2    | 4      | 3778    | 3778000  |

|                       | CNN2    | 3      | 231066  | 5524480  |

Table 2.1. SNN benchmarks

Fig. 2.8. (a) BER vs. Tx power  $@V_{noise} = 5mV$  (b) The required Tx power vs. noise amplitude

phase as edge devices are typically used for deployment of inference applications whereas, training is performed in the cloud [22].

Fig. 2.9. Impact of BER incurred due to PLC on SNN classification accuracy for (a) CIFAR10 dataset (b) SVHN dataset and (c) MNIST dataset

#### 2.6.1 Tx power requirements

Fig. 2.8(a) shows that the power required to maintain the same level of BER increases with increasing distance between the communicating PEs. The required BER level is decided based on the classification accuracy degradation for different BERs. Consequently, we use BER of  $\leq 10^{-5}$  which suffices for SNN applications. Since signal attenuation increases with increasing distance between PEs, the largest attenuation occurs when the center PE transmits and the outermost PE receive. This enables us to estimate the minimum Tx power required for robust communication between PEs located at any distance. Subsequently, we analyzed the BER versus Tx power dependence for varying noise levels (V<sub>noise</sub>) which is shown in Fig. 2.8(b). The Tx power thus obtained are used in system-level simulations and are discussed in the following subsections.

#### 2.6.2 Impact on classification accuracy

Fig.s 2.9(a), (b), and (c) show the impact of BER incurred in data transmission due to PLC on SNN classification accuracy. It is evident that BERs in range of  $\leq 10^{-5}$  can ensure accurate SNN inference, which also justifies the choice of BERs used in Section 2.6.1. The applicability of relatively higher BER than typical requirements of (10<sup>-10</sup>) is enabled by the error-resilient nature of neural network applications.

Fig. 2.10. Power consumption of chip

This error-resiliency comes from the use of non-linear functions (for instance sigmoid, clamped ReLU), which squash the output of matrix transformation layer to a small output range (typically 0 - 1) thereby suppressing errors resulting from small perturbations in input. It can also be seen that complex datasets such as CIFAR10 and SVHN have more constrained BER requirements than simpler datasets for achieving ideal classification accuracy (obtained for ideal PLC with no error i.e. BER 0.0).

#### 2.6.3 Overall power consumption

Fig. 2.10 compares the power consumption of the neuromorphic architecture (discussed in Section 2.4) with PLC-only interconnect to a NOC-only architecture (baseline). Compute (synapse and neuron operations within PEs) constitutes only  $\sim 15.17\%$  of power consumption in the NOC-only architecture. This is because of the simple computation nature of SNNs, which consists of accumulations only, compared to multiplication and accumulation in ANNs. Efficient dot-product operation in memristive crossbars further reduce the PE power consumption.

A PLC-only architecture uses low-power on-chip interconnection network enabled by power lines and low overhead receiver and transmitter per PE. Thus, PLC-only system enables overall power reductions of  $\sim 51.34\%$  compared to NOC-only system for SNN acceleration. Low power is extremely valuable in power-constrained edge devices and battery-powered systems. Note that, while a PLC-only system has sig-

Fig. 2.11. Inference energy (batchsize = 1)

nificantly higher latency cost (discussed in Section 2.6.5), the power benefits can be useful in latency insensitive (or latency tolerant) applications.

# 2.6.4 Inference energy

Fig. 2.11 shows the inference energy consumption of six SNN applications on neuromorphic architectures built with three different interconnection namely (1) NOConly, (2) PLC-only, and (3) hybrid PLC-NOC (discussed in Section 2.4). MLPs have inter-layer data transfers with high input sharing (within an inference) because of their fully-connected design. Recall, all outputs produced by the previous layer are used by all the next layer neurons. This results in large number of inter-layer communications for transferring input data to multiple PEs mapping the next layer, in an NOC-only system. Further, each data transfer requires multiple hops due to the large distance between PEs mapping the successive layers. A PLC-only system harnesses the high input-sharing in fully connected NNs (one-to-many) to reduce the energy consumed in inter-layer communication. However, intra-layer communication are more efficient in the NOC-only system compared to the PLC-only system. This is because of the one-to-one nature of intra-layer communication, wherein no input sharing exists between the data-transfers. Consequently, the hybrid PLC-NOC architecture enables efficient inter-layer communication (PLC) and intra-layer communication (NOC) to achieve  $\sim 42.75\% - \sim 65.04\%$  reductions in energy consumption for MLPs.

Typical CNNs have smaller receptive fields than MLPs, thereby reducing the number of receiver PEs per input data packet. Thus, CNNs have lesser input sharing compared to MLPs, which reduces the benefits obtained from PLC for inter-layer data transfer. Consequently, the hybrid PLC-NOC system achieves lower energy benefits for CNNs ( $\sim 15.76\% - \sim 33.74\%$ ).

# 2.6.5 Inference latency

Fig. 2.12 compares inference latency of the three architectures for SNN applications. PLC achieves comparable latency with respect to NOC for inter-layer communication due to the one-to-many communication nature. Here, PLC benefits from its broadcast nature, while NOC benefits from the parallel one-to-one data transfers. However, PLC incurs significant latency costs for intra-layer communication. This is because of the sequential nature of data transfer in PLC, where only one data can reside on the powerline at any given time. Consequently, while a hybrid PLC-NOC system can achieve comparable latency to an NOC-only based system, the latency of PLC-only system can be  $\sim 5.46 \times$  higher than NOC-only system.

# 2.7 Conclusions

Low power and energy-efficient inference has become extremely important as more and more machine learning applications are being deployed in the edge devices. Further, the number of edge devices used per person have continuously increased over the past decade with majority of the devices being battery powered. This has motivated the design of neuromorphic systems to enable data processing capabilities at the edge devices. Both low-power computation units and energy-efficient interconnect

Fig. 2.12. Inference latency (batchsize = 1)

are fundamental to efficient neuromorphic system design. In this chapter, we propose a hybrid PLC-NOC based neuromorphic architecture built with memristive crossbars to enable efficient ML inference. Our hybrid interconnect harnesses the different data-transfer patterns in typical many-core architecture to optimize energy expended in data communication. Additionally, memristive crossbar based PEs achieve low energy consumption for neuromorphic computations. Our experiments over a wide range of spiking neural network benchmarks show average energy improvements of  $\sim 39.32\%$  at comparable latency.

# 3. SBSNN: STOCHASTIC-BITS ENABLED BINARY SPIKING NEURAL NETWORK WITH ON-CHIP LEARNING FOR ENERGY EFFICIENT NEUROMORPHIC COMPUTING AT THE EDGE

In this section, we propose stochastic Binary Spiking Neural Network (sBSNN) composed of stochastic spiking neurons and binary synapses (stochastic only during training) that computes probabilistically with one-bit precision for power-efficient and memory-compressed neuromorphic computing. We present an energy-efficient implementation of the proposed sBSNN using 'stochastic bit' as the core computational primitive to realize the stochastic neurons and synapses, which are fabricated in 90nm CMOS process, to achieve efficient on-chip training and inference for image recognition tasks. The measured data shows that the 'stochastic bit' can be programmed to mimic spiking neurons, and stochastic Spike Timing Dependent Plasticity (or sSTDP) rule for training the binary synaptic weights without expensive random number generators. Our results indicate that the proposed sBSNN realization offers possibility of up to  $32 \times$  neuronal and synaptic memory compression compared to full precision (32-bit) SNN and energy efficiency of 89.49 TOPS/Watt for two-layer fully-connected SNN.

## 3.1 Introduction

In the current era of ubiquitous autonomous intelligence, there is a growing need for moving Artificial Intelligence (AI) to the edge to cope with the ever increasing demand for autonomous systems like drones, self-driving cars, and smart wearable devices. Energy-efficient neuromorphic systems are henceforth necessary to process the massive amount of data generated by the resource-constrained battery-powered edge devices. Furthermore, it is highly desirable to embed on-chip intelligence using low-complexity learning rules, which enable the edge devices to learn from real-time inputs. Real-time on-chip learning capability precludes the need for offline training in the cloud, which can otherwise lead to higher latency and security concerns for real-time applications.

Spiking Neural Networks (SNNs), on the account of event-driven computing capability and hardware-friendly local learning using Spike Timing Dependent Plasticity (STDP), offer a promising solution for realizing energy-efficient neuromorphic systems with on-chip intelligence. In fact, researchers in [49] demonstrated that SNN running on event-driven neuromorphic hardware like Intel Loihi [23] incurs the minimum energy per inference relative to similarly sized analog neural network executed on CPU/GPU while providing equivalent inference accuracy for a latency-critical keyword spotting task. Recent works on deep SNNs indicate that energy efficiency significantly increases with network depth due to exponential drop in the spiking activity across successive SNN layers [50, 51]. In this regard, prior works proposed energy-efficient implementations of SNN using CMOS [11,23,52] and emerging device technologies such as Resistive Random Access Memory (RRAM) [53,54], Conductive Bridge RAM (CBRAM) [55], and Magnetic Tunnel Junctions (MTJs) [56]. However, SNNs composed of deterministic neuronal and synaptic models require multi-bit precision to store the parameters governing their dynamics. As a result, the computational complexity and neuronal/synaptic memory requirements increase with network size, leading to reduction in the overall power- and area-efficiency.

We propose and implement 'stochastic bits' enabled binary SNN (sBSNN) that computes probabilistically with one-bit precision for energy- and memory-efficient neuromorphic computing at the edge. The core building block of the sBSNN is a 'stochastic bit', which switches between its logic low and high states with a probability that varies in a sigmoidal manner based on the input. We realize the stochastic neurons, referred to as sNeurons, and synapses (stochastic only during training) using the proposed 'stochastic bit' as explained below. The sNeuron receives the weighted sum of the input spikes with the synaptic weights, and spikes probabilistically depending on the weighted input sum. The firing probability of the sNeurons, similar to the switching dynamics of the 'stochastic bit', has sigmoidal relationship with the weighted input sum. The binary synapse interconnecting a pair of input (pre) and output (post) neurons is similarly emulated using the 'stochastic bit' during training. The binary synaptic weight is trained using the stochastic-STDP (sSTDP) algorithm presented in [57], where the synaptic weight is potentiated/depressed with a probability that depends on the degree of correlation between the spike times of the preand post-neurons. The trained binary synaptic weights are then used deterministically during inference to predict the class of a test input. The proposed sBSNN, with event-driven computing capability enabled by state-less sNeurons and memoryefficient on-chip learning capability enabled by the hardware-friendly localized sSTDP rule, offers a promising solution for building the next generation of autonomous intelligent systems.

To that effect, we propose an energy-efficient realization of sBSNN, fabricated in 90nm CMOS technology, to achieve on-chip training and inference for visual image recognition tasks. The proposed 'stochastic bit' is composed of a cross-coupled inverter with PMOS header and NMOS footer transistors for obtaining the sigmoidal switching probability characteristics. We interface the CMOS 'stochastic bit' with the appropriate peripheral circuitry to realize the sNeurons and synapses. The energy and memory efficiency of the proposed implementation stems from three key factors. First, the power consumed by the sNeuron for generating a spike is comparable to that consumed in a single transition of a cross-coupled inverter, which is typically in the order of few  $\mu W$ . In addition, the 'stochastic bit' design also leverages power gating technique [58] with header and footer transistors between the supply and ground rails for reducing the leakage power consumption. Second, the spiking dynamics of the sNeuron depend only on the current input and not on the integrated sum of the current and past inputs, which precludes the need for storing the neuron state (typically known as the membrane potential) as is common in deterministic spiking neurons like the leaky integrate-and-fire neuron. Further, the synapses need only one-bit storage to record the respective binary states. Last, the weighted sum of the inputs with the synaptic weights, which is typically a series of multiply and accumulate (MAC) operations in analog neural networks, is transformed to AND operations followed by pulse count in the proposed sBSNN, thereby reducing the computational energy significantly. Our analysis using a two-layer fully-connected SNN of 400 neurons indicates that the proposed realization offers high energy efficiency of 89.49 TOPS/Watt, which renders it a potential candidate for enabling the next generation of intelligent devices.

In summary, we make the following contributions:

- We proposed the 'stochastic bit' as the core computational primitive to realize the stochastic neurons and binary synapses, which are implemented in 90nm CMOS process.

- We proposed and evaluated the 'stochastic bit' enabled sBSNN that computes probabilistically with one-bit precision for power-efficient and memory-compressed neuromorphic computing.

- We proposed and demonstrated one of the first works on all-CMOS realization of stochastic SNNs. Our proposal provides reconfigurable on-chip learning that is suitable for the real-time and resource constrained edge devices.

## 3.2 Background

## 3.2.1 Stochastic Binary Spiking Neural Network (sBSNN)

The core building block of the proposed sBSNN is a set of input (pre) neurons connected to an output (post) neuron via binary weights. The input neurons, which represent the image pixels for a visual object recognition task, generate Poissondistributed spikes at a rate proportional to the corresponding pixel intensities. At

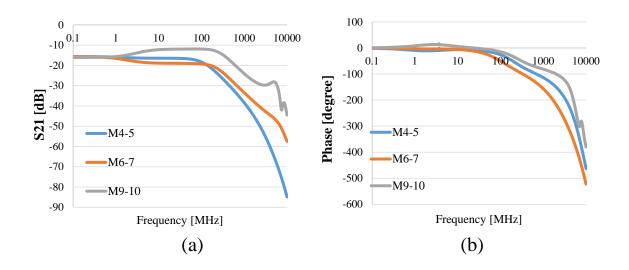

Fig. 3.1. (a) SNN composed of stochastic input and output neurons interconnected via binary synaptic weights. (b) Stochastic-STDP learning rule for binary synaptic weights

any given time, the input pre-spikes get modulated by the interconnecting synaptic weights to produce resultant current into the output neuron. Several previous works have explored the hardware implementations for these core building blocks of stochastic SNNs, using emerging technologies like CBRAMs and MTJs [57,59] and built-in blocks in FPGA board [60]. We proposed a *'stochastic bit'* as the core building block for neuron and synapse (training) to achieve on-chip learning with compressed memory. We model the output neuron using the 'stochastic bit', which spikes probabilistically based on the input current (or weighted input sum) during both training and inference. The spiking probability of the output sNeuron has sigmoidal dependence on the input current as illustrated in Fig. 3.1(a). It is important to note that the sNeuron is state-less since the stochastic spiking dynamics depend only on the instantaneous input current and not on the integrated sum of current and past input currents as is typical in deterministic neuron models, thereby eliminating the multi-bit precision requirement for the neuron state (or membrane potential). The stochastic synapses (stochastic only during training) are similarly emulated using the 'stochastic bit', where the synaptic switching probability depends on the time difference between the pre- and post-spikes as explained in the following section 3.2.2.

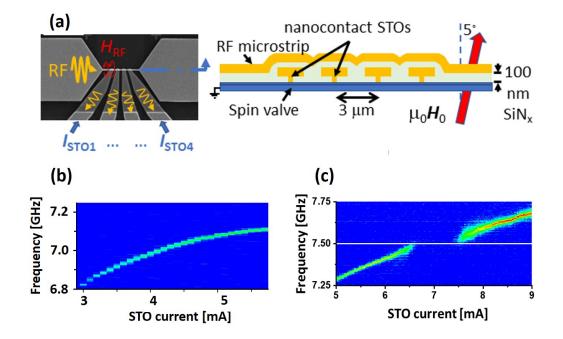

# 3.2.2 Stochastic-STDP (sSTDP)