# EFFICIENT AND ROBUST DEEP LEARNING THROUGH

## APPROXIMATE COMPUTING

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Sanchari Sen

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

August 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Anand Raghunathan, Chair School of Electrical and Computer Engineering Dr. Kaushik Roy

- School of Electrical and Computer Engineering

- Dr. Sumeet K. Gupta School of Electrical and Computer Engineering

- Dr. Vijay Raghunathan School of Electrical and Computer Engineering

# Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

### ACKNOWLEDGMENTS

First and foremost, I would like to express my deepest gratitude to my advisor, Prof. Anand Raghunathan, for his constant guidance and support throughout the last five years. Our regular discussions have helped me grow immensely not only as a researcher, but also as a person. He has constantly encouraged me to pursue new ideas and acquire new skills. His persistence on improving my writing and presentation skills has allowed me to conceptualize and communicate better. Throughout my graduate life, I have been trying to imbibe his impeccable research acumen, work ethic and thirst for knowledge, and will continue to do so in the next phase of my life.

I would like to thank the members of my advisory committee, Prof. Kaushik Roy, Prof. Vijay Raghunathan and Prof. Sumeet Gupta for their insightful comments and constructive feedback. Their thoughts and suggestions have helped to better shape my research. I am grateful for their time and effort on the same.

Next, I want to thank the past and current members of the Integrated Systems Laboratory (ISL) at Purdue, including Dr. Swagath Venkataramani, Dr. Ashish Ranjan, Dr. Shubham Jain, Younghoon Kim, Jacob Stevens, Sarada Krithivasan, Vinod Ganesan, Abinand Nallathambi, Manik Singhal, Sourjya Roy, Shrihari Sridharan, Reena Elangovan and Amrit Nagarajan. Their willingness to help and share their expertise have allowed me to overcome numerous obstacles encountered in my work. I have thoroughly enjoyed our conversations on a variety of academic and nonacademic topics, both inside and outside the confinements of the lab. I am grateful for having the opportunity to closely collaborate with some of the members, which has helped expand my research horizon. I also enjoyed my interactions with Viji Srinivasan, Kailash Gopalakrishnan, Derrick Aguren and Joseph Greathouse as part of my internships at IBM T. J. Watson Research Center and AMD Research. My stay at Purdue would have been incomplete without the amazing time I spent outside work. I am lucky to have been part of the Purdue University Tagore Society (PUTS) and attend their numerous events. I will greatly cherish the memorable moments spent with my friends here and would specially like to thank Sreya Sarkar, Esha Chatterjee, Indrani Biswas, Somrita Chatterjee, Srishti Chakravorty, Sayan Choudhury, Aritra Mitra, Arindam Nandi and Sayantan Bhattacharya for their invaluable friendships. I am deeply indebted to my boyfriend, Prabudhya Roy Chowdhury, for constantly supporting me and accompanying me throughout the past 8 years of my life.

Finally, I would like to thank my parents, Dr. Siddhartha Sen and Sreeparna Sen, for their unparalleled love, care and support; for always believing in me and encouraging me to pursue my dreams. I would like to thank my brother, Dr. Sambudhha Sen, for being someone I could always look up to, share my concerns and ask for advice. The following pages of the dissertation are dedicated to them.

## TABLE OF CONTENTS

| LI              | ST O         | F TAB  | LES                                                                                | х  |  |

|-----------------|--------------|--------|------------------------------------------------------------------------------------|----|--|

| LIST OF FIGURES |              |        |                                                                                    |    |  |

| ABSTRACT        |              |        |                                                                                    |    |  |

| 1               | INTRODUCTION |        |                                                                                    | 1  |  |

|                 | 1.1          | Comp   | utational Challenges of DNNs                                                       | 3  |  |

|                 | 1.2          | Robus  | stness of DNNs                                                                     | 5  |  |

|                 | 1.3          | Thesis | s contributions                                                                    | 6  |  |

|                 |              | 1.3.1  | Improving Efficiency of Feed-Forward Neural Networks                               | 7  |  |

|                 |              | 1.3.2  | Improving Efficiency of Recurrent Neural Networks                                  | 9  |  |

|                 |              | 1.3.3  | Improving Efficiency of Spiking Neural Networks                                    | 9  |  |

|                 |              | 1.3.4  | Exploring Opportunities for Combining Multiple Approximate<br>Computing Approaches | 11 |  |

|                 |              | 1.3.5  | Improving Robustness of DNNs                                                       | 12 |  |

|                 | 1.4          | Thesis | soutline                                                                           | 13 |  |

| 2               | RELATED WORK |        |                                                                                    |    |  |

|                 | 2.1          | Impro  | ving Efficiency of DNNs                                                            | 14 |  |

|                 |              | 2.1.1  | Software parallelization on multi-cores and GPUs                                   | 15 |  |

|                 |              | 2.1.2  | Specialized accelerators                                                           | 15 |  |

|                 |              | 2.1.3  | Model compression                                                                  | 16 |  |

|                 |              | 2.1.4  | Exploiting sparsity in DNNs                                                        | 16 |  |

|                 | 2.2          | Impro  | ving Robustness of DNNs                                                            | 17 |  |

|                 |              | 2.2.1  | Modified DNN training                                                              | 17 |  |

|                 |              | 2.2.2  | Input pre-processing                                                               | 17 |  |

2.2.3

Page

|   |     |        |                                                                                                             | Pa | ıge |

|---|-----|--------|-------------------------------------------------------------------------------------------------------------|----|-----|

|   | 2.3 | Appro  | eximate computing                                                                                           | •  | 18  |

|   | 2.4 | Thesis | s contributions                                                                                             | •  | 19  |

| 3 | BAC | CKGRO  | OUND                                                                                                        | •  | 22  |

|   | 3.1 | Feed-I | Forward Neural Networks                                                                                     | •  | 22  |

|   |     | 3.1.1  | Sources of Sparsity in FFNNs                                                                                | •  | 24  |

|   |     | 3.1.2  | Opportunity for Computational Savings                                                                       | •  | 26  |

|   | 3.2 | Long   | Short Term Memory Neural Networks                                                                           | •  | 27  |

|   |     | 3.2.1  | Long Short Term Memory networks (LSTMs)                                                                     | •  | 28  |

|   |     | 3.2.2  | Sequence-to-Sequence Learning                                                                               | •  | 29  |

|   | 3.3 | Spikin | g Neural Networks                                                                                           | •  | 31  |

|   | 3.4 | Prunii | ng in DNNs                                                                                                  | •  | 33  |

|   | 3.5 | Quant  | zization in DNNs                                                                                            | •  | 34  |

|   | 3.6 | Adver  | sarial Attacks on DNNs                                                                                      | •  | 35  |

|   | 3.7 | Test F | Pattern Compression                                                                                         | •  | 36  |

| 4 |     |        | <u>PAR</u> SITY AWARE GENERAL-PURPOSE <u>C</u> ORE <u>E</u> XTENSION<br>LERATE FEED-FORWARD NEURAL NETWORKS |    | 38  |

|   | 4.1 | Spar(  | CE: Sparsity Aware General Purpose Core Extensions                                                          |    | 41  |

|   |     | 4.1.1  | Challenges                                                                                                  |    | 42  |

|   |     | 4.1.2  | SparCE: Overview                                                                                            |    | 44  |

|   |     | 4.1.3  | In-order SparCE Processor Pipeline                                                                          | •  | 46  |

|   | 4.2 | Softwa | are for SparCE Processors                                                                                   | •  | 50  |

|   |     | 4.2.1  | Code Generation for SparCE                                                                                  | •  | 51  |

|   |     | 4.2.2  | Case Study: Executing GEMM Routine on SPARCE                                                                | •  | 54  |

|   | 4.3 | Exper  | imental Methodology                                                                                         | •  | 56  |

|   |     | 4.3.1  | Performance Evaluation                                                                                      | •  | 56  |

|   |     | 4.3.2  | Power and Area Evaluation                                                                                   | •  | 58  |

|   |     | 4.3.3  | Benchmarks                                                                                                  | •  | 59  |

|   | 4.4 | Result | 5S                                                                                                          |    | 59  |

# Page

|   |     | 4.4.1  | Performance and Energy Improvement                             | 59 |

|---|-----|--------|----------------------------------------------------------------|----|

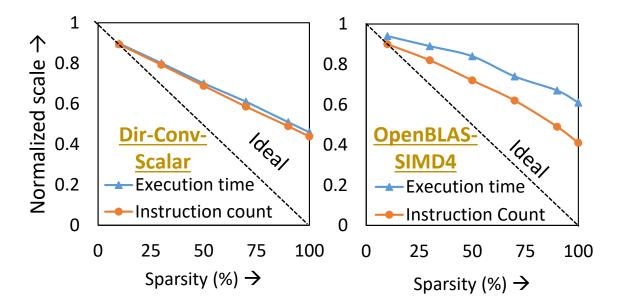

|   |     | 4.4.2  | Performance Scaling with Sparsity                              | 63 |

|   |     | 4.4.3  | Operand Ordering in SPARCE OpenBLAS-SIMD4 Implemen-<br>tations | 65 |

|   | 4.5 | Summ   | ary                                                            | 66 |

| 5 |     |        | MATE COMPUTING FOR LONG SHORT TERM MEMORY<br>EURAL NETWORKS    | 68 |

|   | 5.1 | AxLS   | ΓM: Design Approach and Methodology                            | 70 |

|   |     | 5.1.1  | AxLSTM: Overview                                               | 70 |

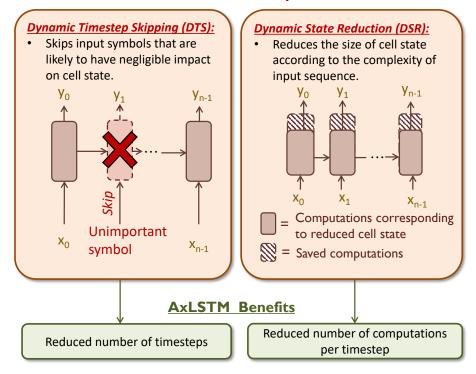

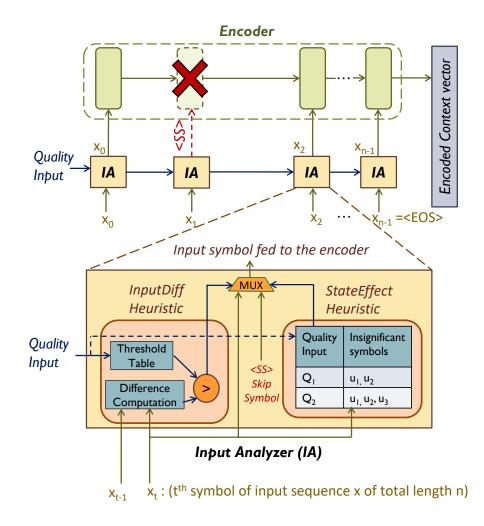

|   |     | 5.1.2  | Dynamic Timestep Skipping (DTS)                                | 72 |

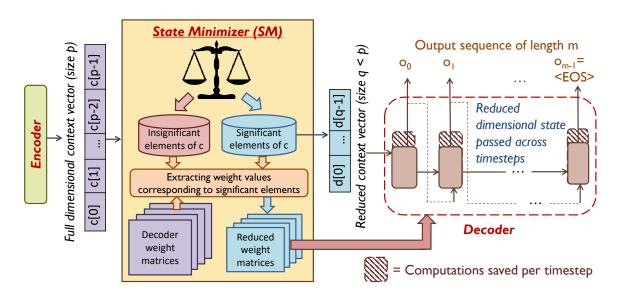

|   |     | 5.1.3  | Dynamic State Reduction (DSR)                                  | 74 |

|   |     | 5.1.4  | AxLSTM: Design Methodology                                     | 77 |

|   | 5.2 | Exper  | imental Methodology                                            | 79 |

|   |     | 5.2.1  | Performance Evaluation                                         | 79 |

|   |     | 5.2.2  | Application benchmarks                                         | 80 |

|   | 5.3 | Result | ïS                                                             | 80 |

|   |     | 5.3.1  | Performance Benefits Versus Accuracy                           | 80 |

|   |     | 5.3.2  | Benefits Breakdown and Overhead analysis                       | 83 |

|   |     | 5.3.3  | Input Adaptive Approximations in Action                        | 85 |

|   | 5.4 | Summ   | ary                                                            | 87 |

| 6 | APF | PROXIN | MATE COMPUTING FOR SPIKING NEURAL NETWORKS                     | 88 |

|   | 6.1 | AxSN   | N: Design Approach and Methodology                             | 91 |

|   |     | 6.1.1  | Approximating Spike-triggered Updates                          | 91 |

|   |     | 6.1.2  | AxSNN: Overview                                                | 92 |

|   |     | 6.1.3  | AxSNN: Design Methodology                                      | 95 |

|   | 6.2 | SNNA   | P: Architecture                                                | 96 |

|   | 6.3 | Exper  | imental Methodology                                            | 98 |

|   |     | 6.3.1  | Runtime and Energy Evaluation                                  | 98 |

|   |     | 6.3.2  | Application Benchmarks                                         | 99 |

| Page |

|------|

|------|

|   | 6.4 | .4 Results |                                                                                                                 |      |

|---|-----|------------|-----------------------------------------------------------------------------------------------------------------|------|

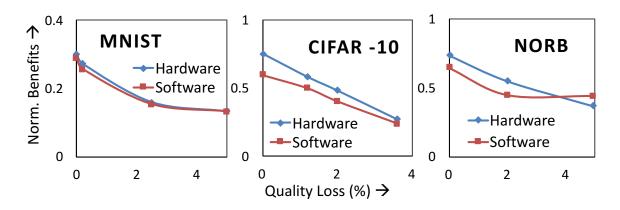

|   |     | 6.4.1      | Energy Benefits at Iso-Accuracy                                                                                 | . 99 |

|   |     | 6.4.2      | Energy vs. Accuracy Tradeoff                                                                                    | 100  |

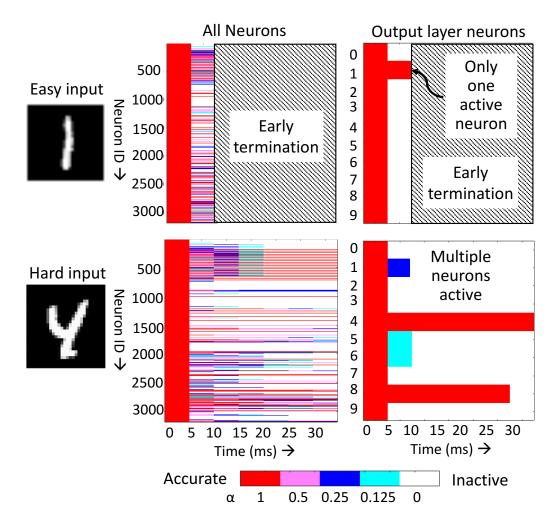

|   |     | 6.4.3      | Input Adaptive Approximations: Easy vs. Hard Inputs                                                             | 101  |

|   | 6.5 | Summ       | ary                                                                                                             | 103  |

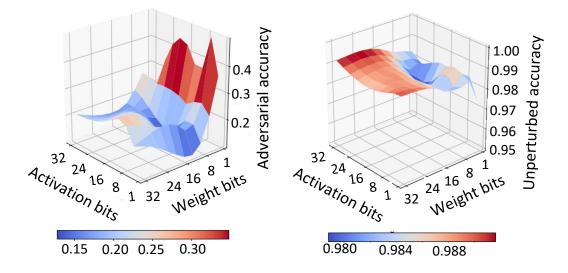

| 7 | EFF | ICACY      | OF PRUNING IN ULTRA-LOW PRECISION DNNS                                                                          | 104  |

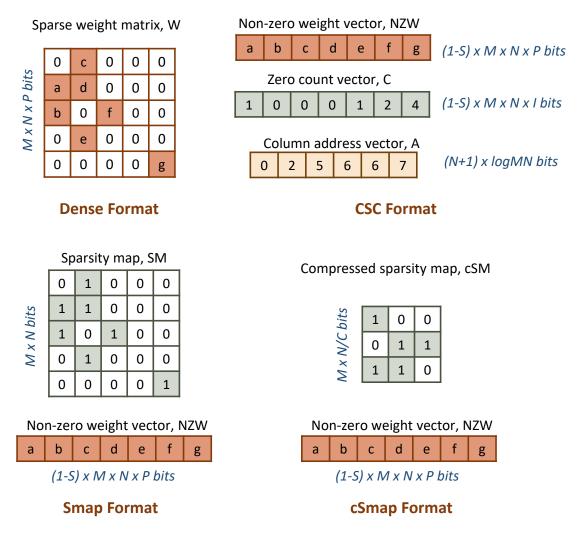

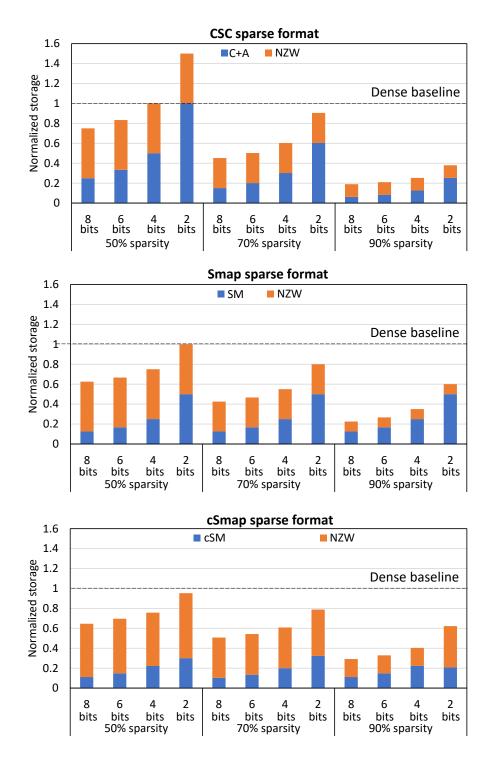

|   | 7.1 | Sparse     | Storage Formats for Pruned DNNs                                                                                 | 106  |

|   |     | 7.1.1      | Compression Ratios                                                                                              | 107  |

|   |     | 7.1.2      | Realizing the cSmap Format using Test Pattern Compression .                                                     | 110  |

|   | 7.2 | Exper      | imental Methodology                                                                                             | 112  |

|   |     | 7.2.1      | Benchmarks                                                                                                      | 112  |

|   |     | 7.2.2      | Compression Evaluation                                                                                          | 113  |

|   | 7.3 | Result     | s                                                                                                               | 113  |

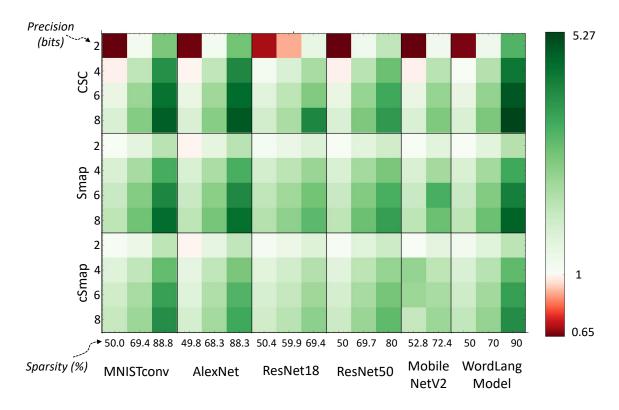

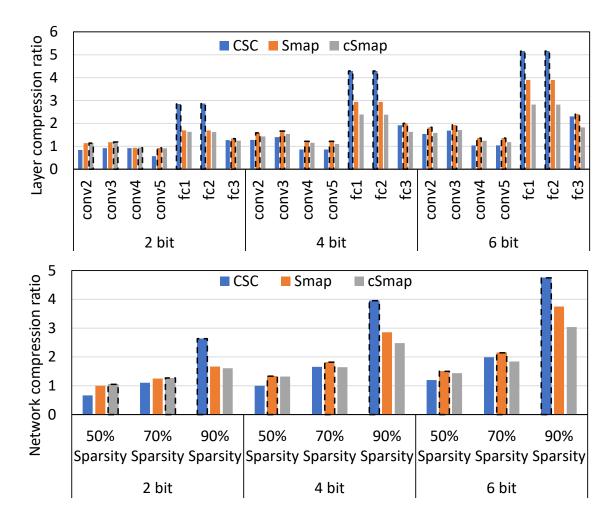

|   |     | 7.3.1      | Network-level Compression Ratios                                                                                | 113  |

|   |     | 7.3.2      | Storage Breakdown in Sparse Formats                                                                             | 114  |

|   |     | 7.3.3      | Benefits of a Hybrid Compression Scheme                                                                         | 116  |

|   | 7.4 | Summ       | ary                                                                                                             | 118  |

| 8 |     |            | SEMBLES OF <u>MIXED PRECISION DEEP NETWORKS FOR</u><br>D <u>R</u> OBUSTNESS AGAINST ADVERSARIAL ATTACKS $\dots$ | 119  |

|   | 8.1 |            | R: Ensembles of Mixed Precision Deep Networks for Increased<br>tness against Adversarial Attacks                | 121  |

|   |     | 8.1.1      | Adversarial Robustness of Low-Precision Networks                                                                | 121  |

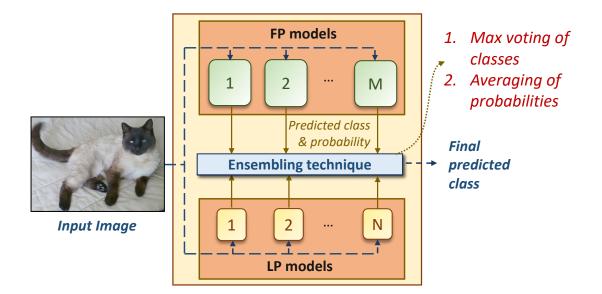

|   |     | 8.1.2      | EMPIR: Overview                                                                                                 | 123  |

|   |     | 8.1.3      | Computational and Memory Complexity of EMPIR                                                                    | 125  |

|   | 8.2 | Exper      | iments                                                                                                          | 126  |

|   |     | 8.2.1      | Benchmarks                                                                                                      | 126  |

|   |     | 8.2.2      | Evaluation of robustness                                                                                        | 126  |

|   | 8.3 | Result     | S                                                                                                               | 128  |

|   |     | 8.3.1      | Robustness of EMPIR models across all attacks                                                                   | 128  |

# Page

ix

|    |            | 8.3.2  | Comparison with individual models $\ldots \ldots \ldots \ldots \ldots$  | 131 |

|----|------------|--------|-------------------------------------------------------------------------|-----|

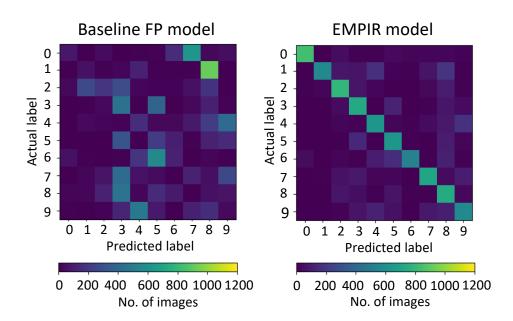

|    |            | 8.3.3  | Analysis of confusion matrices                                          | 132 |

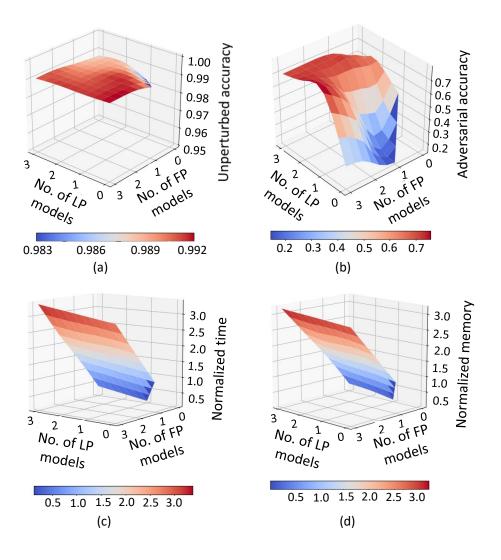

|    |            | 8.3.4  | Impact of varying the number of low-precision and full-precision models | 133 |

|    | 8.4        | Summ   | ary                                                                     | 135 |

| 9  | CON        | ICLUSI | ON                                                                      | 136 |

|    | 9.1        | Thesis | Summary                                                                 | 137 |

| RF | REFERENCES |        |                                                                         | 139 |

| VI | ТА         |        |                                                                         | 152 |

# LIST OF TABLES

| Tabl | e                                                                                                              | Page |

|------|----------------------------------------------------------------------------------------------------------------|------|

| 4.1  | (a) Gem5 simulation parameters (b) Application benchmarks                                                      | . 58 |

| 5.1  | Application benchmarks                                                                                         | . 79 |

| 6.1  | (a) SNNAP parameters (b) Application benchmarks                                                                | . 99 |

| 7.1  | Benchmarks                                                                                                     | 112  |

| 8.1  | Benchmarks                                                                                                     | 127  |

| 8.2  | Attack parameters                                                                                              | 128  |

| 8.3  | MNISTconv: Unperturbed and adversarial accuracies of the baseline and EMPIR models across different attacks    | 129  |

| 8.4  | CIFARconv: Unperturbed and adversarial accuracies of the baseline and EMPIR models across different attacks    | 130  |

| 8.5  | AlexNet: Unperturbed and adversarial accuracies of the baseline and EM-<br>PIR models across different attacks | 130  |

# LIST OF FIGURES

| Figu | Figure                                                                                                                                |   |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------|---|----|

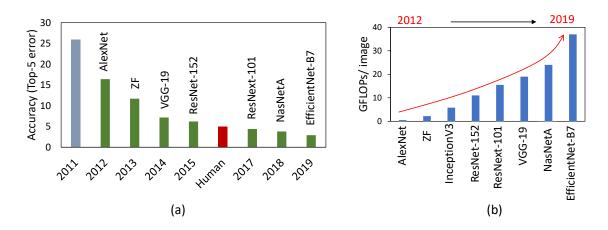

| 1.1  | (a) Results from the ImageNet challenge (b) Number of FLOPs required to evaluate different DNNs from the ImageNet challenge           |   | 4  |

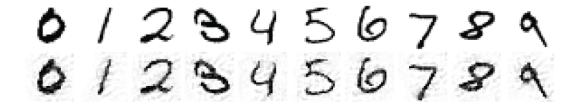

| 1.2  | Original and adversarial images from the MNIST dataset [53] $\ldots$ .                                                                | • | 6  |

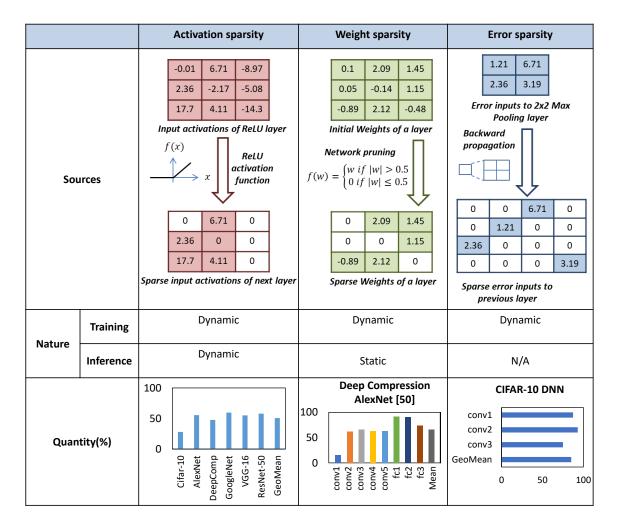

| 3.1  | Different forms of sparsity in FFNNs                                                                                                  | • | 23 |

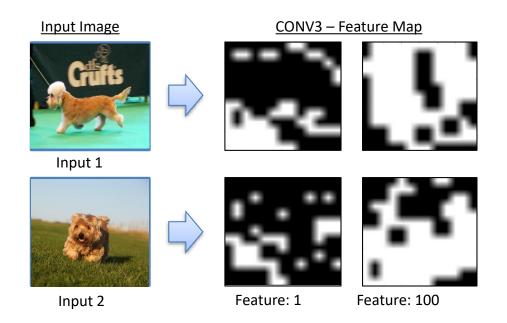

| 3.2  | Variation in activation sparsity of AlexNet CONV3 layer across two different input images                                             |   | 25 |

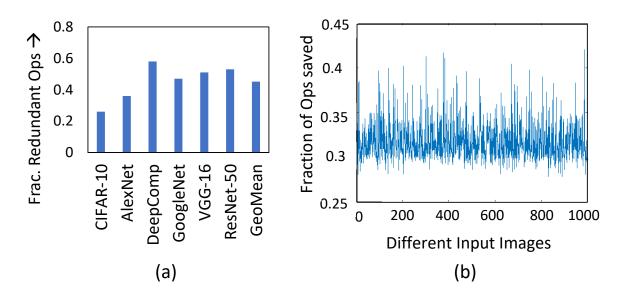

| 3.3  | (a) Average fraction of redundant ops across benchmarks (b) Variation in fraction of redundant ops across different inputs of AlexNet |   | 26 |

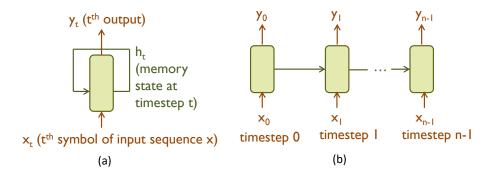

| 3.4  | (a) Basic RNN (b) Time unrolled RNN                                                                                                   | • | 27 |

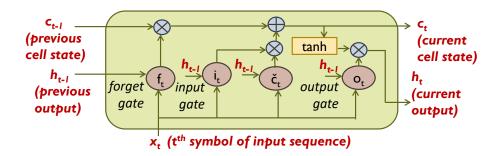

| 3.5  | Long Short Term Memory cell                                                                                                           | • | 28 |

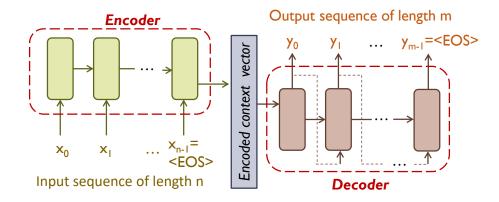

| 3.6  | Sequence-to-sequence model                                                                                                            | • | 30 |

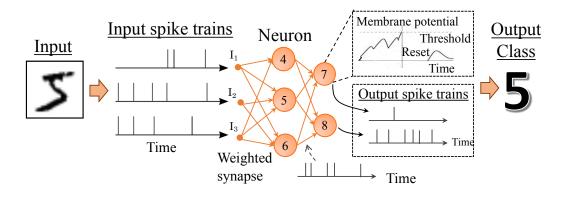

| 3.7  | Spiking neural network preliminaries                                                                                                  | • | 32 |

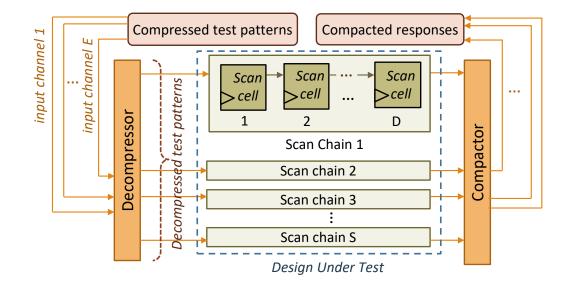

| 3.8  | Test pattern compression architecture                                                                                                 | • | 37 |

| 4.1  | Related work: Exploiting sparsity in FFNNs                                                                                            | • | 39 |

| 4.2  | Redundant instructions due to sparsity in vector dot-product evaluation                                                               | • | 42 |

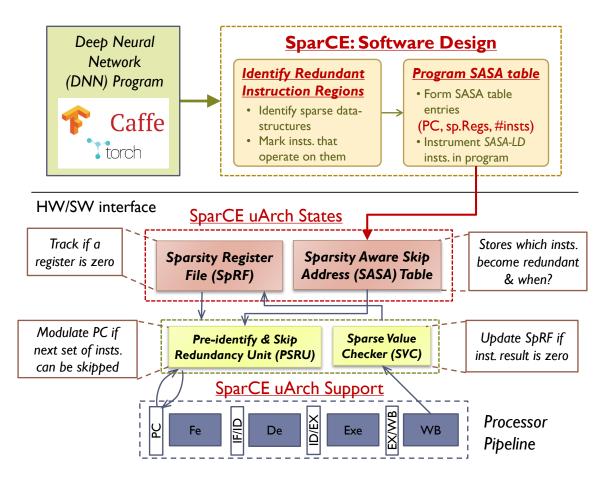

| 4.3  | SPARCE: Design Overview                                                                                                               | • | 44 |

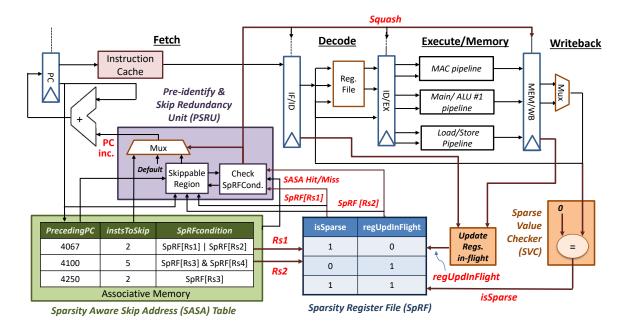

| 4.4  | Block diagram of SPARCE in-order processor architecture                                                                               | • | 47 |

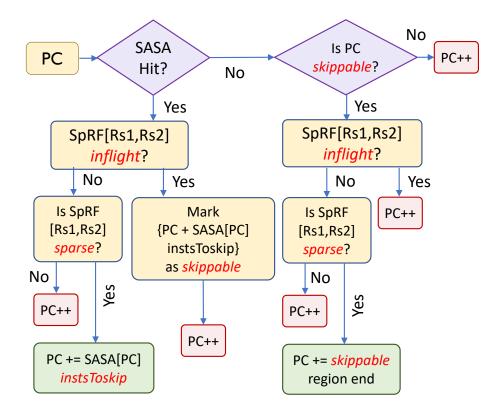

| 4.5  | Flowchart for pre-identifying and skipping redundancy $\ . \ . \ . \ .$ .                                                             | • | 48 |

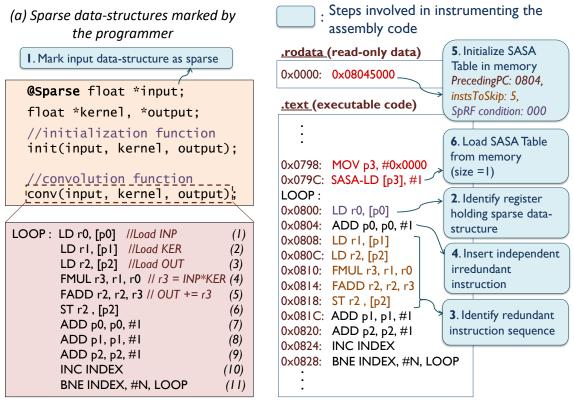

| 4.6  | Code generation for SPARCE                                                                                                            | • | 51 |

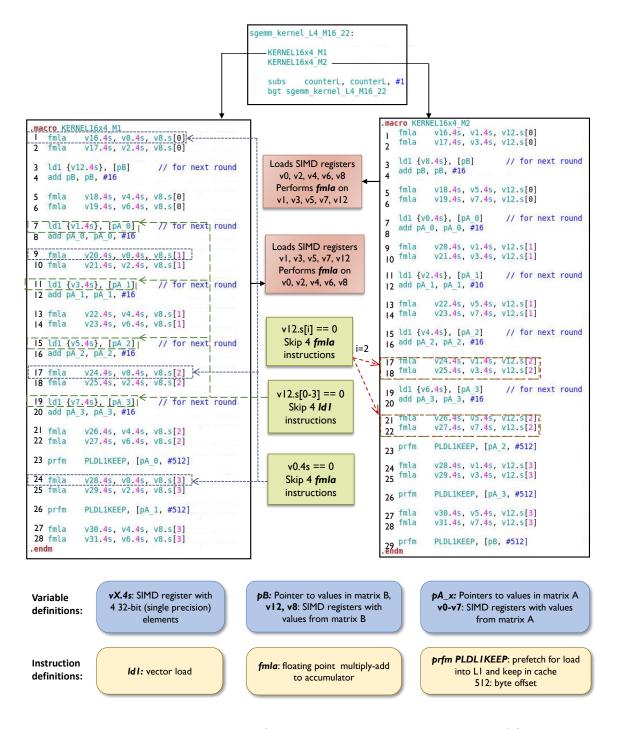

| 4.7  | Zero skipping for <i>sgemm_kernel</i> subroutine in BLAS                                                                              | • | 53 |

| 4.8  | SASA table entries for $kernel16x_4M1$ subroutine $\ldots \ldots \ldots \ldots$                                                       | • | 55 |

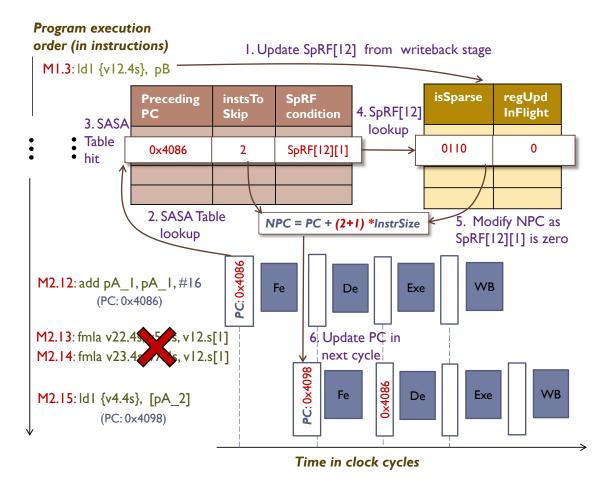

| 4.9  | SparCE in action for <i>sgemm</i> routine                                                                                             | • | 57 |

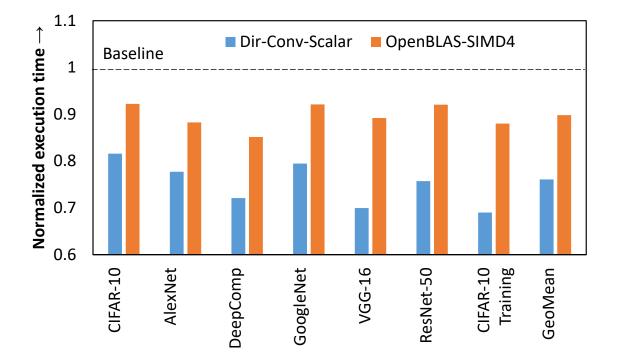

| 4.10 | Improvement in execution time at the application level $\ldots \ldots \ldots$                                                         | • | 60 |

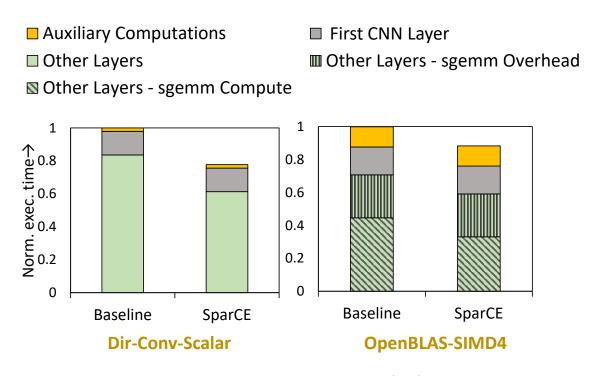

| 4.11 | Execution time breakdown for AlexNet                                                                                                  | • | 62 |

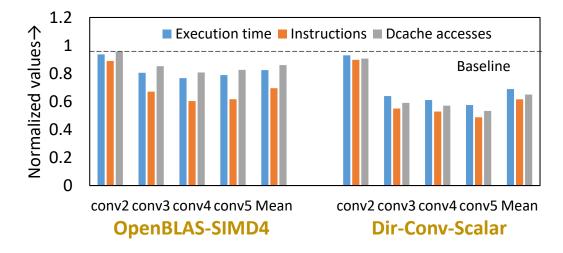

| 4.12 | Layer-wise benefits breakdown for AlexNet                                                                                             |   | 63 |

| Figu | re                                                                                                                                                               | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.13 | SPARCE performance scaling with sparsity                                                                                                                         | . 64 |

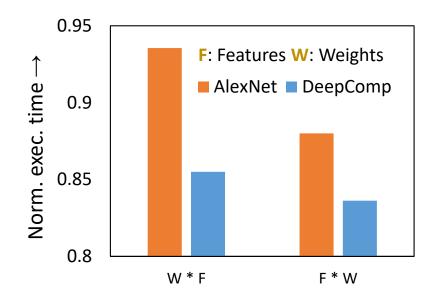

| 4.14 | Impact of operand ordering on performance                                                                                                                        | . 65 |

| 5.1  | Overview of AxLSTM approximation strategies                                                                                                                      | . 71 |

| 5.2  | Dynamic Timestep Skipping in sequence-to-sequence models                                                                                                         | . 73 |

| 5.3  | Dynamic State reduction in sequence-to-sequence models                                                                                                           | . 74 |

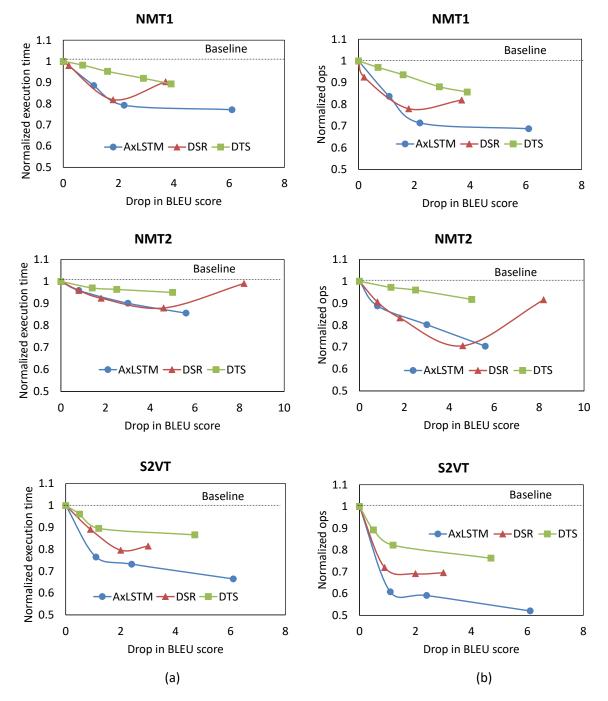

| 5.4  | (a) Normalized execution time and (b) Normalized compute operations versus drop in quality using AxLSTM for sequence-to-sequence models .                        | . 81 |

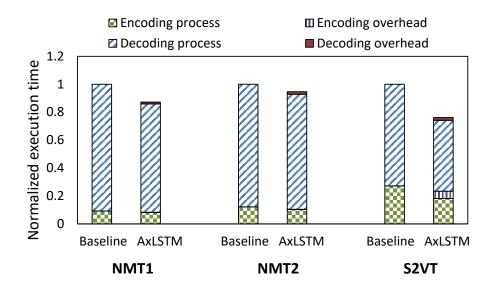

| 5.5  | Execution time benefits breakdown with AxLSTM                                                                                                                    | . 84 |

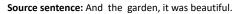

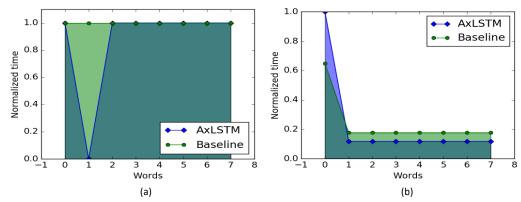

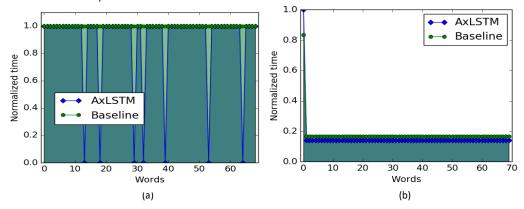

| 5.6  | (a) Normalized encoding time per input word and (b) Normalized decoding time per output word for a semantically simple sentence with and without AxLSTM          | . 85 |

| 5.7  | (a) Normalized encoding time per input word and (b) Normalized decod-<br>ing time per output word for a semantically complex sentence with and<br>without AxLSTM | . 85 |

| 6.1  | Neuron approximation mechanism                                                                                                                                   | . 92 |

| 6.2  | Overview of approximation strategy in AxSNN                                                                                                                      | . 93 |

| 6.3  | Block diagram of SNNAP                                                                                                                                           | . 97 |

| 6.4  | Normalized OPS and energy benefits for different applications                                                                                                    | 100  |

| 6.5  | Normalized energy $vs.$ accuracy trade-off for 3 SNN benchmarks                                                                                                  | 101  |

| 6.6  | Approximation levels of neurons at each time step                                                                                                                | 102  |

| 7.1  | Data-structures and memory requirements of different storage formats                                                                                             | 107  |

| 7.2  | Lossy SM compression                                                                                                                                             | 111  |

| 7.3  | Network-level compression                                                                                                                                        | 114  |

| 7.4  | Storage breakdown in different sparse formats                                                                                                                    | 115  |

| 7.5  | Layer-level and network-level variation in best performing sparse formats                                                                                        | 117  |

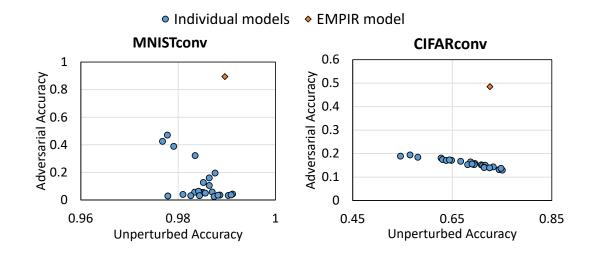

| 8.1  | Unperturbed accuracies and adversarial accuracies of low-precision models trained for the MNIST dataset                                                          | 122  |

| 8.2  | Overview of EMPIR                                                                                                                                                | 124  |

| 8.3  | Tradeoff between unperturbed and adversarial accuracies of the individual                                                                                        |      |

| Figu | re                                                                                                                                                                                  | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 8.4  | Confusion matrices of the baseline FP and EMPIR model for the MNIST-<br>conv benchmark.                                                                                             | 132  |

| 8.5  | Effects of varying the number of LP and FP models in EMPIR (a) Un-<br>perturbed accuracies, (b) Adversarial accuracies, (c) Execution time over-<br>heads and (d) Storage overheads | 134  |

### ABSTRACT

Sen, Sanchari PhD, Purdue University, August 2020. Efficient and Robust Deep Learning Through Approximate Computing. Major Professor: Anand Raghunathan.

Deep Neural Networks (DNNs) have greatly advanced the state-of-the-art in a wide range of machine learning tasks involving image, video, speech and text analytics, and are deployed in numerous widely-used products and services. Improvements in the capabilities of hardware platforms such as Graphics Processing Units (GPUs) and specialized accelerators have been instrumental in enabling these advances as they have allowed more complex and accurate networks to be trained and deployed. However, the enormous computational and memory demands of DNNs continue to increase with growing data size and network complexity, posing a continuing challenge to computing system designers. For instance, state-of-the-art image recognition DNNs require hundreds of millions of parameters and hundreds of billions of multiply-accumulate operations while state-of-the-art language models require hundreds of billions of parameters and several trillion operations to process a single input instance. Another major obstacle in the adoption of DNNs, despite their impressive accuracies on a range of datasets, has been their lack of robustness. Specifically, recent efforts have demonstrated that small, carefully-introduced input perturbations can force a DNN to behave in unexpected and erroneous ways, which can have to severe consequences in several safety-critical DNN applications like healthcare and autonomous vehicles. In this dissertation, we explore approximate computing as an avenue to improve the speed and energy efficiency of DNNs, as well as their robustness to input perturbations.

Approximate computing involves executing selected computations of an application in an approximate manner, while generating favorable trade-offs between computational efficiency and output quality. The intrinsic error resilience of machine learning applications makes them excellent candidates for approximate computing, allowing us to achieve execution time and energy reductions with minimal effect on the quality of outputs. This dissertation performs a comprehensive analysis of different approximate computing techniques for improving the execution efficiency of DNNs. Complementary to generic approximation techniques like quantization, it identifies approximation opportunities based on the specific characteristics of three popular classes of networks - Feed-forward Neural Networks (FFNNs), Recurrent Neural Networks (RNNs) and Spiking Neural Networks (SNNs), which vary considerably in their network structure and computational patterns.

First, in the context of feed-forward neural networks, we identify sparsity, or the presence of zero values in the data structures (activations, weights, gradients and errors), to be a major source of redundancy and therefore, an easy target for approximations. We develop lightweight micro-architectural and instruction set extensions to a general-purpose processor core that enable it to dynamically detect zero values when they are loaded and skip future instructions that are rendered redundant by them. Next, we explore LSTMs (the most widely used class of RNNs), which map sequences from an input space to an output space. We propose hardware-agnostic approximations that dynamically skip redundant symbols in the input sequence and discard redundant elements in the state vector to achieve execution time benefits. Following that, we consider SNNs, which are an emerging class of neural networks that represent and process information in the form of sequences of binary spikes. Observing that spike-triggered updates along synaptic connections are the dominant operation in SNNs, we propose hardware and software techniques to identify connections that can be minimally impact the output quality and deactivate them dynamically, skipping any associated updates.

The dissertation also delves into the efficacy of combining multiple approximate computing techniques to improve the execution efficiency of DNNs. In particular, we focus on the combination of quantization, which reduces the precision of DNN data-structures, and pruning, which introduces sparsity in them. We observe that the ability of pruning to reduce the memory demands of quantized DNNs decreases with precision as the overhead of storing non-zero locations alongside the values starts to dominate in different sparse encoding schemes. We analyze this overhead and the overall compression of three different sparse formats across a range of sparsity and precision values and propose a hybrid compression scheme that identifies that optimal sparse format for a pruned low-precision DNN.

Along with improved execution efficiency of DNNs, the dissertation explores an additional advantage of approximate computing in the form of improved robustness. We propose ensembles of quantized DNN models with different numerical precisions as a new approach to increase robustness against adversarial attacks. It is based on the observation that quantized neural networks often demonstrate much higher robustness to adversarial attacks than full precision networks, but at the cost of a substantial loss in accuracy on the original (unperturbed) inputs. We overcome this limitation to achieve the best of both worlds, i.e., the higher unperturbed accuracies of the full precision models combined with the higher robustness of the low precision models, by composing them in an ensemble.

In summary, this dissertation establishes approximate computing as a promising direction to improve the performance, energy efficiency and robustness of neural networks.

## 1. INTRODUCTION

Deep Neural Networks (DNNs) have transformed the field of machine learning by achieving state-of-the-art results on a wide range of tasks like image classification, speech recognition, object detection and machine translation [1-7]. Today, DNNs are deployed in a spectrum of real-world products and services including Google Translate [8], Google Maps [9], Apple's Siri [10], Google's voice and image search [11], Netflix and Amazon's recommendation engines [12]. Although neural networks have a rich history dating back to the 1950s, their phenomenal growth and expansion into nearly all fields of machine learning is relatively recent and can be attributed to a favorable confluence of various factors. A major factor on that front has been the improvement in the capabilities of hardware platforms like Graphics Processing Units (GPUs) and specialized accelerators. For instance, there was a  $65 \times$  increase in the performance of different GPUs proposed between 2013 and 2016 [13]. The evolution of these hardware platforms, along with the availability of larger datasets, has been instrumental in allowing the development of more accurate (and more complex) networks over the years. For example, AmoebaNet, a state-of-the-art image-recognition DNN demonstrates an impressive 83.9% accuracy on the ImageNet dataset but requires 469 million parameters and 104 billion multiply-accumulate operations to classify a single image [14]. Thus, in order to continue the development of increasingly complex DNNs with better accuracies, computing system designers need to pursue innovative ways of meeting their high computational demands.

Prior research efforts have explored a few key directions to address the computational challenges posed by DNNs. The first direction explores efficient parallelization techniques of DNNs on programmable platforms such as multi-cores and GPUs [15–21]. The second direction develops specialized accelerators to match the compute and data access patterns of different kinds of DNNs [22–30]. Complementary to these directions, we explore approximate computing as a promising approach to improve the execution efficiency of DNNs.

Along with their high computational and memory demands, recent efforts have highlighted another key limitation of DNNs, namely, their lack of robustness [31]. Specifically, DNN outputs have been observed to be severely affected by small, carefullyintroduced input perturbations, which can have drastic consequences in different safety-critical applications like autonomous driving and healthcare. These adversarial input perturbations can be systematically generated through a range of adversarial attack techniques, including Fast Gradient Sign Method [31], Projected Gradient Descent [32] and Basic Iterative Method [33]. Therefore, it is imperative to improve the robustness of DNNs for ushering in the next realm of deep learning applications, beyond the primitive tasks of image, speech and text analytics.

Realizing this need, previous efforts have looked into various means for boosting robustness, including training with adversarial or noisy inputs [31, 32, 34], defensive distillation [35] and regularizing input gradients [36]. We, on the other hand, focus on improving robustness through approximate computing.

Approximate computing is a computing paradigm that allows certain computations in an application to be performed in an inexact or approximate manner while preserving the output quality. It leverages the intrinsic error resilience of applications to introduce approximations that can achieve maximum benefits for a given quality constraint. In general, neural networks have been observed to be highly resilient to approximations in a significant fraction of their computations. For example, different quantized neural networks [37–39] utilizing low-precision data-structures have succeeded in achieving high accuracy levels, in spite of the errors introduced during the quantization process. This intrinsic error resilience makes DNNs attractive candidates for approximate computing.

A key challenge in approximate computing is to identify which computations to approximate and by how much. In order to achieve a favorable energy or execution time versus quality tradeoff, we primarily target our approximations on computations that do not affect the network numerically, as well as, computations that do affect the intermediate values of the network such that the effects don't propagate to the final output quality significantly. In this dissertation, we perform a comprehensive analysis of these computations in DNNs and propose efficient software and hardware techniques for introducing approximations in them. We specifically illustrate the benefits of approximations in three different types of neural networks, namely, Feed-Forward Neural Networks (FFNNs), Recurrent Neural Networks (RNNs) and Spiking Neural Networks (SNNs), which have widely varying computational characteristics and network structures. We further explore the challenges in combining multiple approximate computing techniques for improving the efficiency of these DNNs, specially in the context of FFNNs and RNNs.

While a majority of previous efforts in approximate computing focus on improvements in execution time and energy consumption, a few recent efforts have also highlighted a previously unexplored advantage of approximate computing, in the form of improving robustness of DNNs [40–42]. We explore this advantage even further to develop DNNs robust to a range of adversarial attacks, while maintaining their output quality on the original unperturbed inputs.

In the following sections, we first discuss the computational challenges of DNNs. Next, we discuss the robustness of DNNs. Following that, we present the contributions of this dissertation in terms of developing approximate computing techniques for improving the efficiency and robustness of DNNs. Finally, we outline the remaining chapters of this dissertation.

### 1.1 Computational Challenges of DNNs

The rise of DNNs in the last few years has allowed us to achieve major breakthroughs in several machine learning tasks. Their success can most readily be exemplified by their achievements in the ImageNet challenge. Figure 1.1(a) illustrates the classification accuracies of the top entrants in the challenge over different years. The accuracies are quantified in terms of the top-5 errors which represent the fraction of images for which the correct class did not appear in the top five categories determined by the algorithm. DNNs entered the challenge for the first time in 2012 and immediately caused the error rate to decrease by almost 10%. For the next few years, the development of other forms of DNNs allowed the error rate to quickly decrease to below 5% in 2017, which even exceeds human accuracy levels.

Fig. 1.1.: (a) Results from the ImageNet challenge (b) Number of FLOPs required to evaluate different DNNs from the ImageNet challenge

The dramatic accuracy improvements on the ImageNet dataset were mainly possible through the design of deeper and increasingly complex networks. Obviously, this came at the expense of increased computational and storage requirements of DNNs. Figure 1.1(b) quantifies the computational demands of different top DNN entries in the ImageNet challenge over the years. It shows that there was a  $10\times$  increase in the number of scalar floating point operations (FLOPs) required to evaluate different networks proposed between 2012 to 2019. A significant number of these DNNs relied on GPUs to meet their high computational demands in both training and inference. This was further facilitated by a  $65\times$  increase in GPU performance from 2013 to 2016 [13].

As DNNs get deployed in increasingly complex tasks on bigger datasets, their computational demands are expected to further increase in the future. In addition, this growth can potentially surpass the growth in performance of future GPUs, thereby ceasing any possibility of addressing the challenge by simply executing them on increasingly powerful GPUs. Realizing this, existing research efforts have mainly tried to improve the computational efficiency of DNNs by designing accelerators that can mimic the compute and data access patterns of DNNs [22–30].

Complementary to the above approaches, this dissertation focuses on the use of approximate computing for improving the computational efficiency of DNNs. Previous efforts in that context have explored the use of network pruning [43–45], quantized data-structures [39, 46, 47] and approximate arithmetic units [37, 48, 49]. However, these approaches are often restricted to feed-forward neural networks and can primarily provide benefits on only specialized hardware architectures. In contrast, we consider different classes of DNNs and identify approximations that exploit their unique computational characteristics. Further, we don't restrict these approximations to accelerator platforms and demonstrate savings on different general-purpose platforms as well.

### 1.2 Robustness of DNNs

The remarkable success of DNNs on different machine learning tasks, as illustrated in the previous section for the ImageNet challenge, has naturally led to a significant interest in deploying them in various real-world applications. A large number of these real-world applications, including autonomous driving, healthcare, financial risk management, *etc.*, are safety-critical in nature. Accordingly, robustness, *i.e.*, the ability to cope with erroneous or malicious inputs fed to an application, is emerging as an important requirement for DNNs, along with accuracy.

Recent studies on robustness of DNNs have in fact revealed that DNNs are susceptible to errors under the presence of small input perturbations, imperceptible to humans [31]. A range of adversarial attack techniques, proposed in previous works, provide systematic methodologies for generating perturbations that can cause a DNN to fail [31, 33, 50, 51]. These perturbations can even be targeted towards a particular output class [51] and transferred across different models [52], increasing their strength even further. Fig 1.2 presents some original and adversarial images from the MNIST dataset.

Fig. 1.2.: Original and adversarial images from the MNIST dataset [53]

To overcome this limitation, prior efforts have proposed a range of techniques for boosting robustness. These efforts can be grouped into two broad classes. The first class of efforts involve modifying the training process of DNNs to perform adversarial training [31, 32], noise-based training [34] or defensive distillation [35]. The second class of efforts focuses on different input pre-processing techniques to reduce the effect of perturbations [54, 55].

Complementary to these efforts, we focus on the use of approximate computing for boosting robustness. Earlier efforts in this respect have specifically studied the effect of quantization and observed that it can improve robustness [40–42], but at the cost of some loss in the original unperturbed accuracy. We, on the other hand, overcome this limitation by forming ensembles of both full-precision and low-precision DNNs, to increase the robustness of DNNs while maintaining their accuracy on the original unperturbed inputs.

### **1.3** Thesis contributions

In this dissertation, we explore approximate computing as an avenue to improve the speed, energy efficiency and robustness of both software and hardware implementations of DNNs.

The unique computational and data characteristics of different classes of DNNs give rise to distinct forms of computations that can be approximated. We first explore these approximations for improving the speed and energy efficiency of three different classes of DNNs, namely, Feed-forward Neural Networks (FFNNs), Recurrent Neural Networks (RNNs) and Spiking Neural Networks (SNNs). Next, we explore the opportunities for combining two different forms of approximations, namely, quantization and pruning, in DNNs. Finally, we explore approximations for improving the robustness of DNNs.

### **1.3.1** Improving Efficiency of Feed-Forward Neural Networks

Feed-Forward neural networks (FFNNs) are a class of DNNs characterized by the flow of information strictly in the forward direction from the input layer to the output layer. These include Convolutional Neural Networks (CNNs) and Multi-Layer Perceptrons (MLPs) deployed in tasks like image recognition and object detection. They lack any memory of previous inputs and are thus more suitable for tasks with fixed-length, temporally independent inputs and outputs. We identify sparsity, or the presence of zero values in different data-structures, as a significant source of redundancy in these CNNs. Specifically, multiply-accumulate (MAC) operations, which are the primitive unit of computations in these networks, become redundant when any of the input operands are zeros. Across 6 image-recognition feed-forward networks, we observe that sparsity results in  $\sim 45.1\%$  of the computations being rendered redundant, presenting a significant opportunity for improving performance. Therefore, we target our approximations on these redundant MAC computations.

Sparsity in the FFNN data-structures like activations, weights and backpropagated errors arises from the presence of ReLU (Rectified Linear Unit) layers as well as from the application of pruning techniques for model size reductions. This sparsity can be both static or dynamic, depending on whether the zero values remain constant or vary across different inputs to the network. Sparsity in weights, introduced by pruning connections in the network after training, is static in nature. In contrast, activation and error sparsities, caused by the thresholding nature of the ReLU activation functions, are dynamic in nature. In this dissertation, we propose lightweights extensions to general-purpose cores in the form of Sparsity-aware Core Extensions (SPARCE) for exploiting both static and dynamic sparsities by dynamically detecting whether an operand (e.g., the result of a load instruction) is zero and subsequently skipping a set of future instructions that use it. SPARCE consists of 2 key micro-architectural enhancements. First, a Sparsity Register File (SpRF) is utilized to track registers that are zero. Next, a Sparsity-Aware Skip Address (SASA) Table is used to indicate instruction sequences that can be skipped, and to specify conditions on SpRF registers that trigger instruction skipping. When an instruction is fetched, SPARCE dynamically pre-identifies whether the following instruction(s) can be skipped, and if so appropriately modifies the program counter, thereby skipping the redundant instructions and improving performance. We model SPARCE using the gem5 architectural simulator, and evaluate our approach on 6 state-of-the-art image-recognition CNNs (the most commonly used type of FFNNs) in the context of both training and inference using the Caffe deep learning framework. On a scalar microprocessor, SPARCE achieves  $1.11 \times 1.96 \times$  speedups across both convolutional and fully-connected layers that exhibit 10%-90% sparsity. These speedups translate to 19%-31% reduction in execution time at the overall application-level. We also

evaluate SPARCE on a 4-way SIMD ARMv8 processor using the OpenBLAS library, and demonstrate that SPARCE achieves 8%-15% reduction in the application-level execution time.

In addition to the feed-forward networks described above, there exists a different class of neural networks referred to as Recurrent Neural Networks (RNNs), which can handle variable-length inputs and outputs forming sequences. The following subsection will briefly discuss our proposed approximations in RNNs.

### 1.3.2 Improving Efficiency of Recurrent Neural Networks

Recurrent Neural Networks (RNNs) are a class of DNNs with applications in text and handwriting synthesis [56], speech recognition [57], neural machine translation [58] and image and video captioning [3]. These networks have a cyclic structure, allowing information to persist temporally in the form of memory (state) in the network. The computation of an RNN can be thought of as proceeding in timesteps with a new element of the input sequence being fed to the network at each timestep.

In this dissertation, we propose hardware-agnostic approximate computing techniques for accelerating RNNs. We specifically consider Long Short Term Memory networks (LSTMs), the most popular class of RNNs. The proposed AxLSTM consists of two techniques Dynamic Timestep Skipping (DTS) and Dynamic State Reduction (DSR). Dynamic Timestep Skipping identifies, at runtime, input symbols that are likely to have little or no impact on the cell state and skips evaluating the corresponding timesteps. In contrast, Dynamic State Reduction reduces the size of the cell state in accordance with the complexity of the input sequence, leading to a reduced number of computations per timestep. We describe how AxLSTM can be applied to the most common application of LSTMs, viz., sequence-to-sequence learning. We implement AxLSTM within the TensorFlow deep learning framework and evaluate it on 3 state-of-the-art sequence-to-sequence models. On a 2.7 GHz Intel Xeon server with 128 GB memory and 32 processor cores, AxLSTM achieves  $1.08 \times -1.31 \times$  speedups with minimal loss in quality, and  $1.12 \times -1.37 \times$  speedups when moderate reductions in quality are acceptable.

### **1.3.3** Improving Efficiency of Spiking Neural Networks

Apart from the conventional CNNs and RNNs discussed above, which consist of neurons communicating through continuous activation values, there also exists an emerging class of neural networks often referred to as the third generation of neural networks, namely, Spiking Neural Networks (SNNs). SNNs mimic the spiking behavior of biological neurons and accordingly, represent and process information in the form of binary valued spikes. They well-suited to applications that operate on temporal streams of data (e.g. outputs of event-driven cameras).

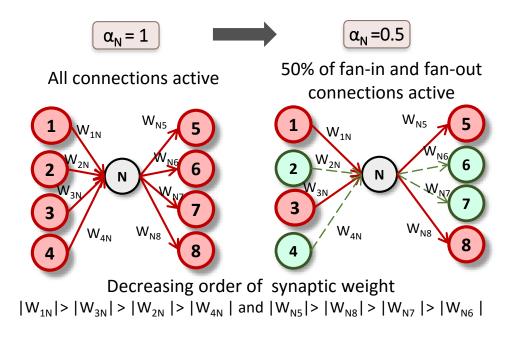

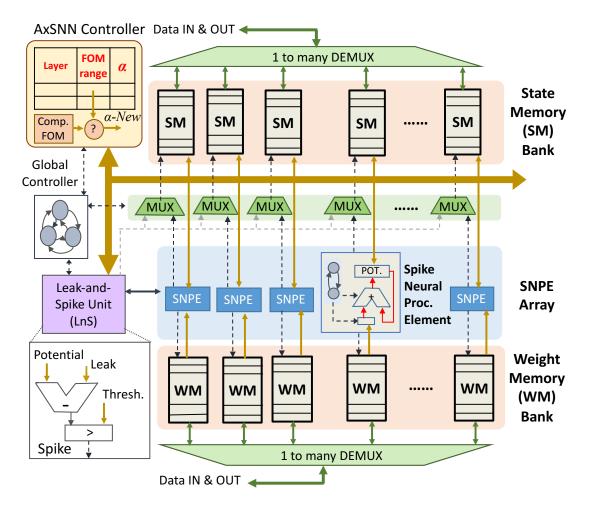

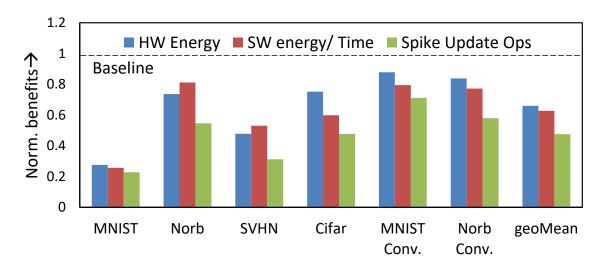

This dissertation proposes AxSNN, a set of approximate computing techniques exploiting the spiking behavior of SNNs to improve their computational efficiency. SNNs are composed of neurons associated with membrane potentials and these neurons generate spikes whenever the potential exceeds a threshold. The spikes generated by neurons can be viewed as events that trigger updates to the membrane potentials of all outgoing neurons. These spike-triggered updates thus form the fundamental compute primitives in SNNs. AxSNN determines spike-triggered neuron updates that can be skipped with little or no impact on output quality and selectively skips them to improve both compute and memory energy. Neurons that can be approximated are identified by utilizing various static and dynamic parameters such as the average spiking rates and current potentials of neurons, and the weights of synaptic connections. Such a neuron is placed into one of many approximation modes, wherein the neuron is sensitive only to a subset of its inputs and sends spikes only to a subset of its outputs. We apply AxSNN to both hardware and software implementations of SNNs. For hardware evaluation, we designed SNNAP, a Spiking Neural Network Approximate Processor that embodies the proposed approximation strategy, and synthesized it to 45nm technology. The software implementation of AxSNN was evaluated on a 2.7 GHz Intel Xeon server with 128 GB memory. Across a suite of 6 image recognition benchmarks, AxSNN achieves  $1.4-5.5 \times$  reduction in scalar operations for network evaluation, which translates to  $1.2-3.62 \times$  and  $1.26-3.9 \times$  improvements in hardware and software energies respectively, for no loss in application quality.

# 1.3.4 Exploring Opportunities for Combining Multiple Approximate Computing Approaches

Along with the above approaches, a wide spectrum of other approximate computing techniques have also been proposed over the years for improving the efficiency of DNNs. Pruning and quantization have emerged as two of the most popular approaches among them, specially for reducing the memory requirements of DNNs. Pruning zeros out different weight values by removing redundant connections in the network and allows weights to be stored compactly in memory using different sparse formats. Quantization, on the other hand, converts DNN weights to low-precision values, which can be represented and stored in memory using a smaller number of bits. Both pruning and quantization have primarily been explored as independent approaches with ongoing efforts focusing on advancing their individual limits even further. We investigate the opportunities for combining them, specially as we go into the regime of ultra-low precision DNNs (sub-8 bits of precision).

In this dissertation, we systematically evaluate the effectiveness of pruning ultralow precision DNNs, in terms of the memory reductions achieved by storing these pruned DNNs in different sparse formats. We consider two sparse formats widely used in compressing DNNs, *viz.*, Compressed Sparse Column (CSC) and Sparsity Map (Smap). We also propose a new format, namely, compressed Sparsity Map (cSmap), that improves upon the Smap format by replacing the sparsity map matrix with its compressed version. We realize the cSmap format in our implementation by re-purposing the test pattern compression tools widely used in manufacturing tests. We discover that the memory compression benefits of all three sparse formats reduce with decreasing precision because of the increasing overhead of storing the location of non-zero weights along with their values. Across several pruned and quantized versions of 6 state-of-the-art DNNs, we observe that the compression ratio achieved by each format is a strong function of both sparsity and precision, even leading to values <1 in certain cases. Based on this observation, we propose a new hybrid compression scheme that compresses different networks, and individual layers within them, in different sparse formats — identified to be best-suited for their precision and sparsity levels. We demonstrate that such a hybrid scheme can improve the average compression ratio of a 2-bit DNN by 18.3% - 34.7% over homogeneous compression schemes.

### 1.3.5 Improving Robustness of DNNs

In addition to reducing the computational and memory demands of DNNs, a few recent efforts have highlighted that quantization can also be used as an approach to improve robustness, as low-precision DNNs exhibit higher adversarial accuracies than full-precision DNNs [40–42]. However, the loss in information associated with the quantization process often makes these low-precision models perform significantly worse than their full-precision counterparts while classifying the original unperturbed inputs.

This dissertation proposes EMPIR, ensembles of mixed-precision DNNs, as a new approach for improving robustness. It combines the higher robustness of low-precision models with the higher unperturbed accuracy of full-precision models by composing them in an ensemble. In the general case, it is composed of M full-precision models and N low-precision models with the outputs of the individual models combined through ensembling techniques that count the number of predictions for each class or average the probabilities of the models. We study the effect of ensemble size and ensembling technique on the overall robustness of the model and observe that M = 1and N = 2 or 3 provides significant improvement in robustness with minimal compute and memory overheads. We implemented EMPIR within the TensorFlow framework and measured the adversarial accuracies under a range of adversarial attacks within the Cleverhans library. Our results indicate that EMPIR boosts the average adversarial accuracies by 42.6%, 15.2% and 10.5% for the DNN models trained on the MNIST, CIFAR-10 and ImageNet datasets respectively, when compared to single full-precision models, without sacrificing accuracy on the unperturbed inputs. Further, these EM-PIR models only incur modest compute and memory overheads compared to a single full-precision model (<25% in our evaluations).

### 1.4 Thesis outline

The rest of the thesis is organized as follows. Chapter 2 details the related research efforts in accelerating different types of DNNs and improving their robustness. Chapter 3 provides the necessary background on FFNNs, LSTMs and SNNs, along with the preliminaries of pruning, quantization and adversarial attacks on DNNs. Chapter 4 proposes techniques to accelerate FFNNs on general-purpose platforms by exploiting sparsity. Chapter 5 proposes hardware-agnostic approximate computing techniques for accelerating SNNs. Chapter 6 discusses another application of approximate computing for accelerating SNNs. Chapter 7 investigates the opportunities for combining two popular approximate computing techniques of pruning and quantization in DNNs. Chapter 8 proposes an approximate computing technique for boosting robustness of DNNs. Finally, Chapter 9 concludes this dissertation.

## 2. RELATED WORK

Deep neural networks have successfully achieved state-of-the-art results in a wide range of machine learning tasks like image, video, text and speech processing. However, the pursuit of larger networks with better accuracies has also led to increasing concerns about their high computational and memory demands, which far outstrips the capabilities of modern computing platforms. Multiple research efforts have accordingly tried to address the computational challenge posed by DNNs by proposing techniques to improve their computational efficiency on different platforms. In this chapter, we discuss some of these efforts, particularly in the context of convolutional neural networks, long short term memory neural networks and spiking neural networks, and highlight the unique aspects of our work.

In addition to their high computational and memory demands, recent efforts have also highlighted another notable limitation of DNNs, namely, their lack of robustness. Various forms of adversarial attacks have successfully fooled DNNs through small, carefully-introduced input perturbations that cause large misclassifications. To overcome this limitation, prior research efforts have proposed different techniques for increasing robustness of DNNs. We present the details of some of these efforts in this chapter and contrast them with our approach.

Finally, as this dissertation is built on the principles of approximate computing, we also present previous research efforts in applying approximate computing techniques to improve the computational efficiency of different applications.

### 2.1 Improving Efficiency of DNNs

Prior research efforts that target improving the computational efficiency of DNNs can be grouped into the four broad classes which are discussed below in more detail.

### 2.1.1 Software parallelization on multi-cores and GPUs

A large number of previous efforts have been directed towards developing techniques for efficient parallelization of DNNs on programmable platforms such as multi-core servers and GPUs [15–20, 59–63]. These techniques primarily exploit two different forms of parallelism, namely, model parallelism and data parallelism [15]. Model parallelism refers to the parallelization of different parts of the same model across different threads or cores. On the other hand, data parallelism refers to the parallelization of different inputs to the same model across different threads or cores. The efficiency of model or data parallelism largely depends on the characteristics of a particular DNN. Model parallelism is generally observed to be more efficient for scenarios with large amounts of compute operations per neuron while data parallelism is observed to be more efficient for DNNs with larger batch sizes of inputs. Some of the approaches also employ other optimizations on top of model and data parallelism, exploiting the computational pattens of specific classes of DNNs like LSTMs [21] or SNNs [63]. Overall, the scalability of the techniques is often limited by synchronization and communication bottlenecks. Specially the dynamic and event-driven nature of SNNs makes parallelization challenging, as it leads to irregular and unpredictable compute and memory access patterns.

### 2.1.2 Specialized accelerators

Developing specialized hardware architectures has been an attractive approach to improve the computational efficiency of DNNs. These accelerators utilize specialized processing cores, interconnect networks and other hardware-software co-design methodologies to leverage the different forms of compute and data reuse patterns in DNNs. They differ on the kind of parallelism exploited, the DNN operating phase targeted for acceleration — training or inference phase, as well as, the area, power and energy constraints considered in the designs. Some of the designed accelerators can support a range of neural networks [23, 24, 26] while others are more targeted towards a particular type of network [22, 29, 64–66].

### 2.1.3 Model compression

DNNs require high storage and memory bandwidths to efficiently store and transfer the large number of parameters involved in their computations. Existing efforts in pruning [43–45] and quantization [37,39,47,67] address this challenge by reducing the number of parameters and the number of bits used in representing them, respectively. This is specially advantageous in various resource-constrained embedded platforms which cannot support DNNs of large model sizes.

### 2.1.4 Exploiting sparsity in DNNs

Prior efforts that exploit sparsity to improve DNN efficiency can be grouped into two classes based on whether they exploit static sparsity or dynamic sparsity. Specialized sparse architectures that are capable of exploiting static or dynamic sparsity incorporate a variety of compression techniques and zero-skipping schemes to reduce storage requirements and avoid redundant multiplications in accelerators [26, 68–72].

On the other hand, software approaches that exploit static weight sparsity on GPPs take advantage of sparse matrix libraries. These sparse libraries usually yield performance improvements only under extreme levels of sparsity (>95%). Since DNNs naturally exhibit sparsity in the range of 40%-70%, a few research efforts force more weight sparsity into DNNs using sparse decomposition methods, *etc.* [73, 74] or customize the pruning to match the underlying hardware organization [75]. These invariably come at the cost of training overhead or loss of functional accuracy.

### 2.2 Improving Robustness of DNNs

Popular approaches for improving robustness of DNNs can be grouped into the following three classes.

### 2.2.1 Modified DNN training

The first class of efforts includes popular techniques like adversarial training and noisebased training which augment the training dataset with adversarial inputs [31,32] or noisy inputs [34] to increase robustness. Although they do improve the robustness of DNNs, the increase in training time can be prohibitively high. Another approach, defensive distillation [35], involves training networks on the output probabilities of classes instead of the conventional approach of training on hard output class labels. It is based on the technique of distillation that was originally proposed to efficiently transfer knowledge across different DNN models. Other approaches have also explored input gradient regularization [36] during the training process for enforcing smooth input gradients in the network.

### 2.2.2 Input pre-processing

The second class of efforts for increasing robustness performs input pre-processing for reducing the effect of perturbations. Popular pre-processing techniques include input discretization and quantization [54, 55]. However, modifying the attack generation process to include the discretization process is can break the defense mechanism [55].

### 2.2.3 Use of specialized DNN models

The third class of efforts focus on the use of specialized forms of DNN models for increasing robustness. Some efforts have advocated the use of ensembles of full precision models [53,76–78]. In addition to the above efforts, there have been a parallel set of efforts studying the robustness of low-precision or quantized DNNs. For example,

binary neural networks with single bit precisions for weights and activations have been shown to exhibit higher adversarial robustness than their full-precision counterparts on different white-box attacks [40,41]. Stochastic quantization of activations has also been proposed as an approach to make DNNs more robust [42]. However, the quantized models in these efforts are often in the sub-8 bit domain and thus demonstrate lower accuracies on unperturbed or clean examples due to the loss in information associated with the quantization process.

### 2.3 Approximate computing

Approximate computing refers to an emerging computing paradigm that improves the performance and energy efficiency of computing platforms by exploiting the intrinsic error resilience of different applications. Intrinsic error resilience is defined as the ability of certain applications to produce outputs of satisfactory quality even when some of the underlying computations are approximated. Prior research efforts have proposed a multitude of approximate computing techniques over the years, applicable to different levels of the hardware stack, from circuits to architecture and software [79]. These include voltage overscaling techniques at the circuit level [80, 81], precision scaling techniques at the architectural level [82, 83] as well as iteration skipping and dependency relaxation techniques at the software level [84, 85].

Various machine learning applications in domains like recognition, vision, search and data analytics have been observed to exhibit significant amounts of intrinsic error resiliency and thereby be amenable to approximate computing. Accordingly, in the context of NNs, approximate computing has been previously applied to feed-forward neural networks [37,48,49]. In addition, one of the prior approaches have also explored approximate computing for RNNs [86]. These approaches utilize backpropagation, one of the key steps involved in training NNs, to characterize the criticality of neurons in the network, and correspondingly subject them to varying levels of approximation. These approximations are subsequently realized by utilizing reduced precision and approximate arithmetic units.

### 2.4 Thesis contributions

The primary contributions of this dissertation are different or complementary to the prior efforts in the following aspects:

Sparsity aware general-purpose core extensions to accelerate FFNNs. Our work differs from specialized accelerator based approaches to accelerate FFNNs [22– 26] by focusing on different size and cost-constrained systems like wearables and sensors where the use of accelerators employing large numbers of processing elements and considerable on-chip memory is prohibitive. We specifically accelerate FFNNs on these systems by developing lightweight extensions to the general-purpose processors (GPPs) already present in them. The proposed extensions exploit a key attribute of FFNNs, i.e., sparsity of weights and activation values. Unlike software based approaches that can only exploit the static sparsity in weights [73–75], our proposed extensions, in the form of SPARCE (Sparsity-aware Core Extensions), can exploit both dynamic sparsity in activations and static sparsity in weights, while being effective even under intermediate levels. Further, these extensions account for just 1.04% area overhead over an ARM Cortex A35 core of  $0.4mm^2$  area, as opposed to area overheads of  $4 - 16mm^2$  of different accelerators [22, 25, 26].

Hardware-agnostic approximate computing for LSTMs and SNNs. Our work complements other efforts that accelerate SNNs or LSTMs through the use of parallel software [19–21, 59–63] or specialized hardwares [27–30, 64–66, 87, 88] by proposing the use of approximate computing to improve their computational efficiency. Prior efforts that apply approximate computing to neural networks [37, 48, 49, 86] utilize reduced precision and approximate arithmetic units. As a result, they often require specialized hardware implementations and do not benefit software implementations. In contrast, our work proposes new approximate computing techniques that are generic in nature and are applicable to both software and hardware implementations. These techniques also take advantage of the unique structure and computational characteristics of SNNs and LSTMs. For instance, our proposed AxSNN (Approximate computing for SNN) identifies spike-triggered neuron updates to be the primitive unit of computations in SNNs and determines updates with little or no impact on output quality to selectively skip them at runtime. On the other hand, the proposed AxLSTM (Approximate computing for LSTM) takes advantage of LSTM's computational pattern of updating its entire memory state vector after processing a new symbol in each timestep. It accordingly skips the evaluation of input symbols that are likely to have little or no impact on memory state and reduces the size of the cell state in accordance with the complexity of the input sequence.

Investigating opportunities for combining pruning and quantization techniques. Prior efforts have primarily explored pruning [43–45, 89] and quantization [39, 46, 47, 67] as independent approaches for compressing DNN models. In contrast, we focus on the intersection of the two techniques and identify the opportunities for combining both. We demonstrate that existing sparse storage formats, which store non-zero locations along with non-zero values in pruned DNNs, suffer from inefficiencies in the ultra-low precision (<8 bits) regime. Specifically, the overhead of storing non-zero locations starts to dominate in this regime and can even force the overall compression ratio to drop below 1 in the worst case, when the sparse format ends up consuming higher memory than the dense format. Our work is also complementary to a few previous efforts that propose training frameworks to perform pruning and quantization in parallel [90]. These efforts solely on simultaneously maximizing the achieved sparsity levels and minimizing the weight precisions without considering the implications of exploiting sparsity in the ultra-low precision regime.

**Ensembles of mixed-precision DNNs for increased robustness.** Our work differs from existing ensembling approaches for increasing robustness [53, 76–78] by considering both low-precision and full-precision DNNs in the constituent models. The presence of all full-precision models in the previously proposed ensembles in-

creases their compute and memory requirements significantly ( $10 \times$  for an ensemble with 10 models in [53]), which prevents the application of this approach to larger state-of-the art models. In contrast, as low precision DNN models have significantly lower computational and storage requirements than full precision models, the proposed EMPIR ensemble incurs only modest compute and memory overheads compared to a single full-precision model (<25% in our evaluations). Further, unlike the low unperturbed accuracies of the low-precision models proposed for increasing robustness [40–42], EMPIR maintains high unperturbed accuracy by combining higher robustness of the low-precision models with the higher unperturbed accuracies of the full-precision models in the ensemble.

# 3. BACKGROUND

In this chapter, we first provide a brief background on the network architectures and computational patterns of FFNNs, RNNs and SNNs. Next, we present the basics of pruning and quantizing DNNs. Following that, we present a brief background on adversarial attacks on DNNs. Finally, we discuss the basics of test pattern compression mechanisms.

#### 3.1 Feed-Forward Neural Networks

In this section, we first provide a brief background on Feed-Forward Neural Networks (FFNNs). We then explain the various static and dynamic sources of sparsity in the different data-structures of FFNNs and quantify the opportunity for performance improvement afforded by sparsity.

FFNNs are networks of primitive compute units called *neurons*, organized into layers like convolutional layer, pooling layer and fully-connected layer. Each layer is associated with a set of parameters called weights. Just like any other neural network, FFNNs operate in two phases *viz*. training and inference. During the training phase, a labeled training dataset is used to iteratively refine the weights of the FFNN. In the inference phase, the trained FFNN is used to classify new inputs.

Computationally, FFNN executions iteratively perform three key steps *viz*. Forward Propagation (FP), Backpropagation (BP), and Weight Gradient and Update (WG). These steps operate on four primary data-structures, *viz.*, activations, weights, errors and gradients. All three steps (FP, BP, WG) are performed during the training phase, while inference involves only the FP step. In FP, inputs to the FFNN are propagated through its layers to produce the FFNN outputs. In each layer, the input activations are operated on with its weights to produce its output activations, which are then fed to the next layer and so on. In BP, errors observed at the output of the FFNN are propagated backwards through each layer of the FFNN. In this case, the error at the output of a layer is operated on with its weights to compute the error at its inputs. In WG, the input activations and the output error of each layer are used to refine its weights.

Fig. 3.1.: Different forms of sparsity in FFNNs

#### 3.1.1 Sources of Sparsity in FFNNs

In practice, all major FFNN data-structures - activations, weights, errors and gradients - exhibit significant levels of sparsity, which can be exploited for computational savings. Three of the four data-structures (all except weight gradients) are used as inputs to multiply-and-accumulate operations in the different steps (FP/BP/WG), which become redundant when one of the input operands is zero. Among these three sparse multiply-and-accumulate operands, weights exhibit static sparsity that remains constant across different inputs while the remaining two data-structures (activations and errors) exhibit dynamic sparsity that varies dynamically across different inputs. Figure 3.1 summarizes the sparsity in the different FFNN data-structures, which we describe in the remainder of this subsection.

#### Static Sparsity

Weight Sparsity. Sparsity in weights occurs during the inference phase of the FFNN. As shown in Figure 3.1, after training, connections whose weights are close to zero are pruned to compress the model size [25, 43, 44]. The last row in Figure 3.1 shows the fraction of zero weights in the different layers of the AlexNet model trained using deep compression [43]. We find the sparsity to vary between 18%-85% across the different layers. Weight sparsity is static in nature because of the fact that zero weights are identified before the inference phase.

#### **Dynamic Sparsity**