# DATA TRANSFER PERFORMANCE ANALYSIS FROM PROGRAMMABLE LOGIC TO PROCESSING SYSTEM OF ZYNQ 7000

by

**Tilottoma Barua**

## A Thesis

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Masters of Science in Engineering

Department of Electrical and Computer Engineering Fort Wayne, Indiana August 2020

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Todor Cooklev, Chair

Harris Professor of Wireless Communications and Applied Research Director of the Center for Wireless Technology

## Dr. Chao Chen

Director of Engineering Graduate Program in ECE Department Associate Professor of Computer Engineering

## Dr. Yanfei Liu

Associate Professor of Electrical and Computer Engineering

# Approved by:

Dr. Chao Chen Head of the Graduate Program

## ACKNOWLEDGMENTS

At first, I would like to thank Dr. Todor Cooklev for allowing me to proceed with my MSc. thesis under his supervision. I found him supportive during the whole journey while working with him. I am grateful to him for being my supervisor because when I work under him I always felt motivated and happy. My special gratitude goes to the members of my MSc committee, Dr. Chao Chen and Dr. Yanfei Liu for accepting their role. They always helped me by reading my dissertation and providing useful feedback. I would like to thank the Electrical and Computer Engineering Department of Purdue Fort Wayne for giving me this wonderful opportunity to complete the thesis, and for providing the necessary support in the school. Finally, I would like to take the opportunity to thank my husband Anomadarshi Barua, for his continuous support and encouragement throughout my graduate studies at Purdue University Fort Wayne.

# TABLE OF CONTENTS

| LIST OF 7 | ΓABLES                                                         | 6  |

|-----------|----------------------------------------------------------------|----|

| LIST OF F | FIGURES                                                        | 7  |

| LIST OF A | ABBREVIATION                                                   | 9  |

| ABSTRAG   | CT                                                             |    |

| 1. INTR   | ODUCTION                                                       | 11 |

| 1.1 Mc    | otivation                                                      | 12 |

| 1.2 Wł    | ny Performance Analysis is Needed - Data Movement Challenges:  |    |

| 1.3 Ap    | plication Areas of ZYNQ-7000-"Data Flow":                      | 14 |

| 1.3.1     | Video Processing of Drones                                     | 14 |

| 1.3.2     | LiDAR in Autonomous Vehicle                                    | 15 |

| 1.4 The   | esis Outline                                                   | 16 |

| 2. BACk   | GROUND AND RELATED WORK                                        |    |

| 2.1 Ba    | ckground:                                                      |    |

| 2.1.1     | Hardware-Software co-design                                    |    |

| 2.2 Re    | lated Works with Hardware/Software Co-Design:                  | 19 |

| 2.3 Re    | lated Works with ZYNQ 7000:                                    |    |

| 2.4 Soi   | me More Work On A Different Platform                           |    |

| 2.4.1     | HW/SW Co-design for Exascale System                            |    |

| 2.4.2     | Coarse-Grained Reconfigurable Accelerators (CGRA Architecture) |    |

| 2.4.3     | Different Embedded System Platform for Co-Design Applications  |    |

| 2.4.4     | FPGA and other SoC Platforms                                   |    |

| 3. HARI   | DWARE-SOFTWARE PLATFORM AND METHODOLOGY                        |    |

| 3.1 ZY    | NQ-7000 Architecture                                           |    |

| 3.1.1     | Overview                                                       |    |

| 3.1.2     | ZYNQ-7000 Features                                             |    |

| 3.1.3     | ZYNQ-7000 Communication Interfaces                             |    |

| 3.1.4     | Processing System and Programmable Logic Interfaces            |    |

| 3.1.5     | Theoretical Data Transfer Throughput of PL-PS Interfaces       |    |

| 3.2 Sot   | ftware Platforms                                               |    |

| 3    | 3.2.1 | Vivado Design Suite                                               | 6          |

|------|-------|-------------------------------------------------------------------|------------|

| 3    | 3.2.2 | Software Development Kit (SDK)                                    | 7          |

| 3.3  | Met   | thodology                                                         | 8          |

| 4. I | DESIC | GN AND IMPLEMENTATION                                             | 9          |

| 4.1  | Har   | dware-Software Design Co-simulation process                       | 9          |

| 4.2  | Har   | dware Design                                                      | 1          |

| 4    | 1.2.1 | Designing "Sample Data Generator" using RTL Flow: 4               | 1          |

| 4    | 1.2.2 | AXI4-Stream interface signals 4                                   | -3         |

| 4    | 1.2.3 | Sample Data Generator- Testbench Logic Simulation 4               | 4          |

| 4    | 1.2.4 | Hardware Design with VIVADO Design Suite4                         | 6          |

| 4.3  | Sof   | tware Design                                                      | 1          |

| 5. E | EXPE  | RIMENTAL RESULTS AND PERFORMANCE ANALYSIS 5                       | <i>i</i> 4 |

| 5.1  | Exp   | perimental Setup                                                  | 4          |

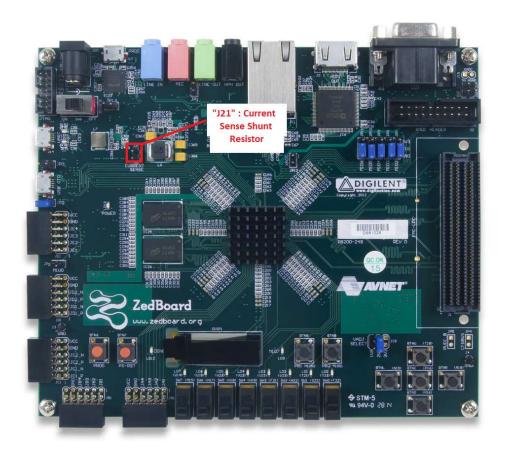

| 5    | 5.1.1 | Power Measurement in Zedboard                                     | 5          |

| 5.2  | Per   | formance Analysis For Different Data Length 5                     | 6          |

| 5.3  | Ene   | rgy Consumption                                                   | 8          |

| 5.4  | Per   | formance Analysis For Different Burst Size and PL Clock Frequency | ;9         |

| 5    | 5.4.1 | Analysis 6                                                        | <b>j</b> 4 |

| 6. 0 | CONC  | LUSION AND FUTURE WORK 6                                          | 5          |

| 6.1  | Cor   | nclusion 6                                                        | 5          |

| 6.2  | Fut   | ure Work 6                                                        | 6          |

| APPE | ENDE  | X A 6                                                             | 7          |

| APPE | ENDE  | X B                                                               | 0          |

| REFE | EREN  | CES                                                               | 2          |

# LIST OF TABLES

| Table 3.1: AXI4 Feature Availability and IP Replacement                                                          | 33 |

|------------------------------------------------------------------------------------------------------------------|----|

| Table 3.2: Theoretical Data Transfer Throughput of PL-PS Interfaces                                              | 36 |

| Table 4.1: ZYNQ Memory Map                                                                                       | 51 |

| Table 5.1: Data Transfer Performance Analysis for GP,1-HP and ACP ports                                          | 57 |

| Table 5.2: Power Consumption during data transfer                                                                | 58 |

| Table 5.3: Energy Consumption                                                                                    | 59 |

| Table 5.4: Performance Analysis of High-performance port(HP0) For Different Burst Size         Clock Frequency   |    |

| Table 5.5: Performance Analysis of Accelerator Coherency Port (ACP) For Different Bunand PL Clock Frequency.     |    |

| Table 5.6: Performance Analysis of General Purpose Port (S_GP0) For Different Burst S         PL Clock Frequency |    |

# LIST OF FIGURES

| Figure 1-1: A simplified model of Zynq 12                                                             |

|-------------------------------------------------------------------------------------------------------|

| Figure 1-2: LiDAR in Autonomous Vehicle[33]15                                                         |

| Figure 1-3: A flow graph of thesis outline                                                            |

| Figure 2-1: FPGA and CPU Integration[11]                                                              |

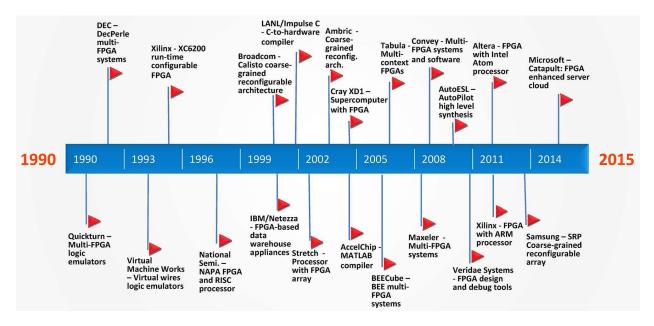

| Figure 2-2: A timeline of reconfigurable computing system evolution[31]25                             |

| Figure 3-1: Zynq Block Diagram[18]                                                                    |

| Figure 3-2: Zedboard                                                                                  |

| Figure 3-3: Zynq-7000 Architecture[18]                                                                |

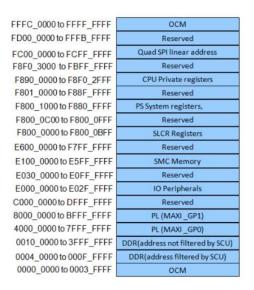

| Figure 3-4: System-Level Address map[17]                                                              |

| Figure 3-5: Read and Write Channels[17]                                                               |

| Figure 3-6: Two-way VALID/READY Handshake[17]                                                         |

| Figure 3-7: AXI4-Stream Transfer with Unidirectional Channel[17]                                      |

| Figure 3-8: Zynq Processing System Architecture[18]                                                   |

| Figure 3-9: Hardware-software design tools                                                            |

| Figure 4-1: Hw/Sw Co-design Flow 40                                                                   |

| Figure 4-2: The sample data generator AXI stream module                                               |

| Figure 4-3: Clock cycle and counter circuit for sample data generator                                 |

| Figure 4-4: Data Generation Circuit                                                                   |

| Figure 4-5: AXI4 stream signals                                                                       |

| Figure 4-6: The sample data generator test bench simulation showing the logic simulation wave diagram |

| Figure 4-7: Basic Hardware Block Diagram 46                                                           |

| Figure 4-8: VIVADO hardware design with high-performance interfacing port and AXI DMA 49              |

| Figure 4-9: ZYNQ memory mapping for the custom design interfaces (HP, ACP, and GP ports) in VIVADO    |

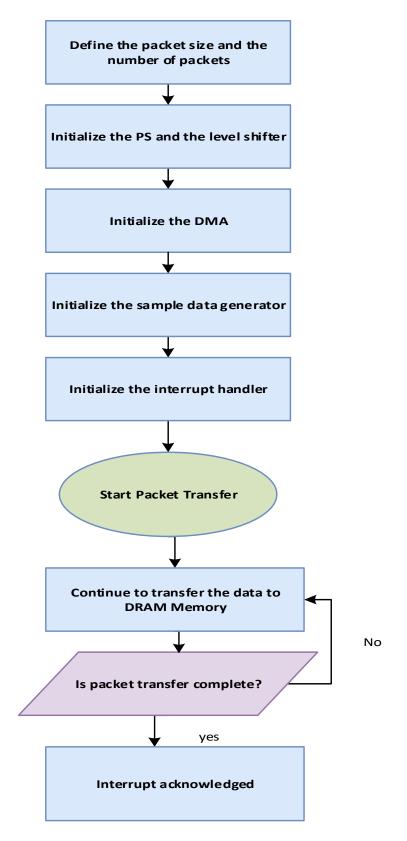

| Figure 4-10 : Flow chart for the data transfer from PL to DDR memory                                  |

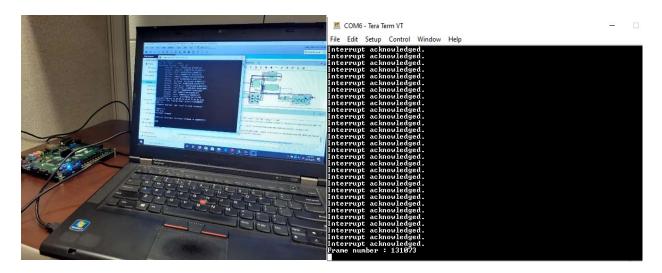

| Figure 5-1:Experiemntal Set up and the Tera Term Serial COM port                                      |

| Figure 5-2: Current sensor shunt resistor on Zedboard                                                 |

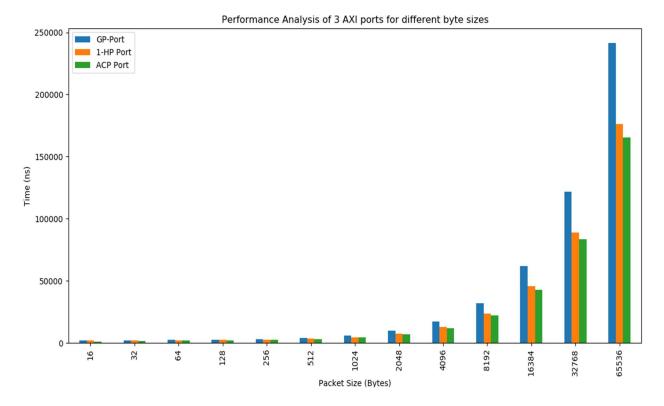

| Figure 5-3: Performance Analysis of three AXI ports in transferring data from PL to PS 57                 |

|-----------------------------------------------------------------------------------------------------------|

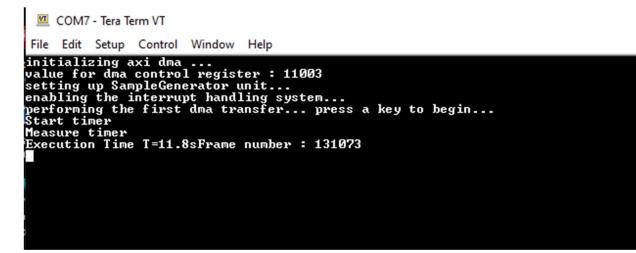

| Figure 5-4: Tera Term COM console 60                                                                      |

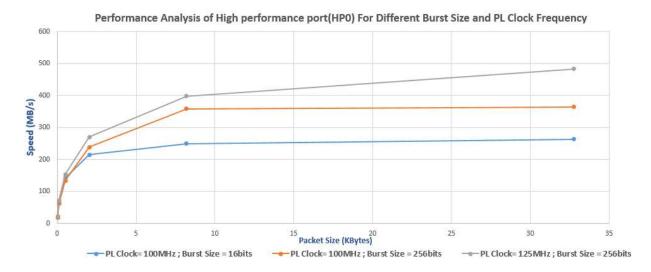

| Figure 5-5: Graphical analysis of HP0 interface port For Different Burst Size and PL Clock<br>Frequency   |

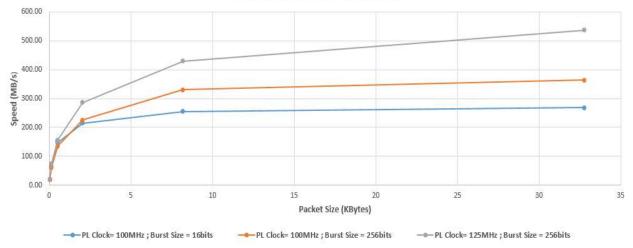

| Figure 5-6: Graphical analysis of ACP interface port For Different Burst Size and PL Clock<br>Frequency   |

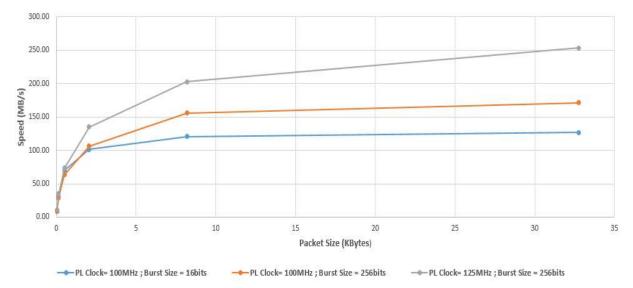

| Figure 5-7: Graphical analysis of S_GP0 interface port For Different Burst Size and PL Clock<br>Frequency |

| Figure 6-1: Proposed workflow of video processing                                                         |

# LIST OF ABBREVIATION

| ACP   | Accelerator Coherency Port                              |  |

|-------|---------------------------------------------------------|--|

| ARM   | Advanced RISC Machines                                  |  |

| ASIC  | Application Specific Integrated Circuit                 |  |

| AXI   | Advanced eXtensible Interface                           |  |

| CPU   | Central Processing Unit                                 |  |

| DDR3  | Double Data Rate Synchronous Dynamic RandomAcess Memory |  |

| DMA   | Direct Memory Access                                    |  |

| DRAM  | Dynamic RandomAccess Memory                             |  |

| FPGA  | Field Programmable Gate Array                           |  |

| HLS   | High Level Synthesis                                    |  |

| HP    | High Performance                                        |  |

| IP    | Intellectual Property                                   |  |

| LiDAR | Light Detection And Ranging                             |  |

| SoC   | System On Chip                                          |  |

| GP    | General Purpose                                         |  |

| SDK   | Software Development Kit                                |  |

| PL    | Programmable Logic                                      |  |

| PS    | Processing System                                       |  |

| LUT   | Look Up Table                                           |  |

| OCM   | On-Chip Memory                                          |  |

# ABSTRACT

Field-Programmable Gate Arrays (FPGAs) were invented in the 1980s. Since then the use of FPGAs in many fields has been growing rapidly. Due to the inherent reconfigurability and relatively low development cost FPGA technology has become one of the important components in data processing and communication systems.

The recent development of computing technology affects not only the software but also requires integrating and utilizing a custom logic design on a dedicated hardware platform.

In this context, this research work analyses and compares on-chip interfaces for hardware/software communications in the Zynq-7000 all programmable SoC-based platform. Several experiments were carried out to evaluate the performance of data communication between the processing system and the programmable logic through general-purpose (GP), high-performance ports (HP), and accelerator coherency port (ACP); the experiments were conducted for bare-metal standalone applications. The results identified the most effective interfaces for transferring data from the PL to PS and store the data to DRAM memory. The Xilinx Software Development Kit (SDK) and Vivado Design Suite together provide hardware/software development platform to evaluate their performance.

One conclusion of this work is that the selection of suitable ports depends on application requirements. For low-bandwidth applications the GP port is appropriate. For high-speed applications, the High Performance (HP) port and Accelerator Coherence Port (ACP) are suitable and work better. The results of this thesis are useful in high-performance embedded systems design.

## **1. INTRODUCTION**

FPGAs continue to have a remarkable impact on computing technology and various fields in engineering. The inherent reconfigurability of FPGAs and comparatively cheap development cost has made it an important tool for research. Nowadays the availability of field-configurable micro-chips that combine multi-core processors and reconfigurable logic incorporated with several DSP slices and block memories has made this path smoother. Such integration leads to the ease of communication system between two different types of processors allowing the systems-on-chip to reduce the complexity of computation and communication. The Zynq-7000 all programmable system-on-chip (APSoC) device from Xilinx integrates a dual-core processing unit running on different software and programmable logic which can be customized to develop different hardware-accelerated systems using different logic combinations and computations, and which further allows interfaces enabling interactions and data exchange between the dual-core processing system using software and hardware components. These cost-effective devices permit complete solutions for embedded systems to be integrated on a chip. To achieve the best and optimal performance of this type of platform, the fastest and best communication channel is required between two different processors. The interfaces between the Processing system (PS) and Programmable Logic (PL) are supported by different intellectual property (IP) cores and the AXI interface system bus. The combination of architectural and technological advances has enabled Zynq-7000 to open a new era in the development of highly optimized computational systems with enormous variations of practical applications. These applications not only include highperformance computing but also data, signal, and image processing with embedded systems. On this contrary, the potential methods need to be studied to decide which method is better for data communications. This type of comparison study has been shown in this thesis with different test cases for Zynq-7000 APSoC. The design flow includes the development of hardware-accelerated tools in the PL supported by available Xilinx IP cores and customized design of IP cores with available features in VIVADO and software development tools (SDK) in the PS for the applications on the bare metal operating system. Bare metal application can be defined as the operating system, which is operational directly on the hardware with no underlying specification. Bare metal application typically has a limited bootloader to start the processor, time, and memory spaces and switch into the main program.

#### 1.1 Motivation

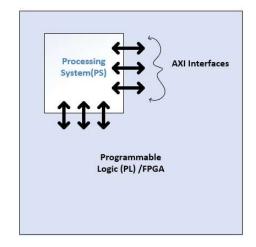

A system-on-chip (SoC) like the ZYNQ -7000 series consists of all the necessary parts and peripherals (e.g. processing units (PS & PL), peripheral interfaces (UART, JTAG, USB, Ethernet, etc.), memory systems, clocking circuit units, Interrupt systems and input/output). Xilinx Zynq-7000 family is the first All Programmable System-On-Chip - APSoC system which is a combination of the dual-core ARM CortexTM MPCoreTM-based processing system (PS) and programmable logic (PL) on the same microchip [1].

The processors were used to connect with a Field Programmable Gate Array (FPGA) via remote communication method which made communication between the Programmable Logic (PL) and Processing System (PS) more complicated before the development of the ZYNQ-7000. The Zynq all programmable (SoC) is the latest generation of Xilinx's all-programmable System-on-Chip (SoC) families which combines a dual-core ARM Cortex-A9 with programmable logic (FPGA). To establish communication between the different components, specifically between PS & PL, the Zynq architecture is based on the Advanced extensible Interface (AXI) standard, which provides high bandwidth and low latency connections [1].

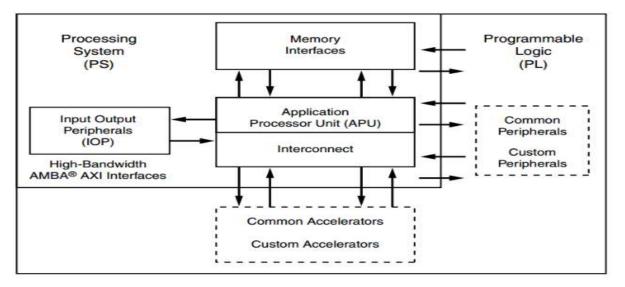

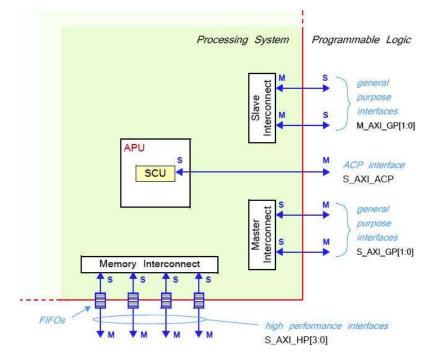

The PL(FPGA) part of Zynq is ideal for implementing high-speed logic, arithmetic, and data flow subsystems. On the other hand, the dual-core PS (Processing System) supports software routines and operating systems which ensures the overall functionality of the designed system. The PS-PL interface consists of all the signals available for the designer to integrate the PL-based functions and the PS [2]. A typical simplified model of Zynq is shown in Figure 1-1.

Figure 1-1: A simplified model of Zynq

#### 1.2 Why Performance Analysis is Needed - Data Movement Challenges:

Microelectronics has recently been exponentially progressed with the rapid growth of fieldprogrammable gate array technology (FPGA). This growth has contributed to a range of highly promising applications. Also, adding more transistors on the FPGA chip allows the vast amounts of parallel calculations. Secondly, recent developments in high-speed transceivers permit the transfer of data into and out of FPGAs in high bandwidths. Further, FPGA technology supports computerized algorithms, such as those with LiDAR(Light Detection and Ranging) systems or middleware communication systems that can be used with several FPGA components to accelerate hardware efficiently.

Using a standard interface like AXI, data movement in a System-on-a-Chip (SoC) like Zynq can be on-chip from one usable block to another or off-chip. However, Advanced eXtensible Interface (AXI) protocol, has been adopted by Xilinx as the IP cores. An AXI interface can be defined as an end-to-end linkage between master and slave clients inside the system for transmitting data, addresses, and handshaking signals. Nonetheless, data transfer between normal or memory interfaces are normally performed as on-chip communication. The big issue for a hardware engineer is to determine the appropriate data transfer method for a memory subsystem. Although small data transfer on the chip can be performed using the software instructions, it can be done more effectively with special data transfer tools when large data transfers are made.

The communication overheads have to be evaluated to assess the potential performance increase that can be accomplished with hardware accelerators. Data can be exchanged across a wide range of ports and the right approach for faster data transmission is preferred. The amount of data to be transmitted, the communication bus configuration, and the sharing of the memory of the ARM cache are a key factor in assessing the analysis. Multi-processor approaches to improve system performance are pursued by engineers. Moreover, the processors also need to compute several tasks in parallel. Hence, without an effective mechanism for communication, the purpose or the idea of the development of the multiple-processor system will be degraded.

The right bus protocol and data widths are required for each peripheral on the SoC to optimize the use of on-chip bus structures, that reduce silicone infrastructure or the resources by supporting high-performance on-chip low-power communication.

## 1.3 Application Areas of ZYNQ-7000-"Data Flow":

Many data streaming applications like video and multimedia processing or packet switching needs great performance, which can be achieved by mapping the multi-task parallel application on the System on Chip (SoC). A smooth transition of a task from software to hardware implementation demands a unified system for information exchange. Some applications that have relatively modest requirements for multi-processing, and that could be done within the available PL components and resources would be more cost-effectively implemented with the Zynq-7000 platform. Some sets of applications/examples will be demonstrated here which heavily requires data transfer performance analysis among the processors.

### 1.3.1 Video Processing of Drones

A common use of drones is aerial photography. In recent days, drones are used in individual filming, news, and sports broadcasting, monitoring, security inspection, and agricultural applications, etc. An HW/SW co-design can be used in video and image processing in this application.

However, to achieve professional-quality recording by using drones some parallel combinations of tasks are needed. Fast frame rates, integration of the 4K or higher resolution, and (HDR) video, may result in a huge quantity of the data to be stored.

Video streaming from drones brings new challenges, and current research areas usually involve some compression methods. These methods are appropriate for wide mobility cameras, and drone-based cameras for sports and other live broadcasts. Also, this type of advanced camera technology includes the system to monitor and detect an exact location of an object in the video. All of these tasks regarding video processing involves complicated processing. A software program running on the Zynq SoC-7000 application processing unit (APU), preferably with the advantage of hardware acceleration in the Programmable Logic(PL), would be an optimal solution in this application. For this reason, the data transfer needs to be faster and the suitable interface must be chosen as per the application [33].

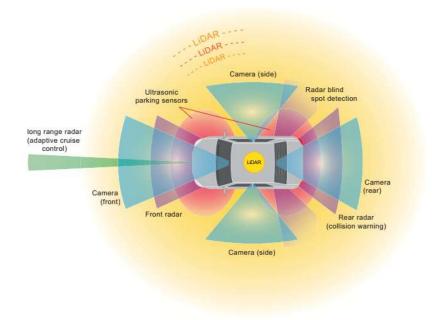

#### **1.3.2** LiDAR in Autonomous Vehicle

LiDAR (Light Detection And Ranging), which uses radar-like concepts of laser light, is fast to emerge as an impressive technology particularly for autonomous vehicles. Even though LiDAR systems are currently significantly large and costly, there is an increasing potential to develop lower-cost and relatively portable solutions that are suitable for mass-market vehicles.

Figure 1-2: LiDAR in Autonomous Vehicle[33]

Figure 1-2[33] shows a typical representation of an autonomous vehicle where different types of sensors are placed around the vehicle. For example, adaptive cruise control, blind-spot detection, etc. Front, rear, and sided cameras can be used to capture visuals data elements from the image to gather the sensor information. In this case, LiDAR is an important choice as it can deliver greater distance precision than radar at medium distances (10-100 meters), including complete 360-degree coverage, which is appropriate for autonomous vehicles.[33]

To determine the vehicle's condition, the significant amount of data produced in the sensor systems must be processed, merged, and evaluated. This implies enormous signal processing on sensor nodes input. Also, accurate syncing and further processing to incorporate the data helps to interpret hazards and take immediate measures accurately. All this process (including both PL and PS based components in Zynq-7000) should occur simultaneously as quickly as possible,

considering the high speed at which vehicles can drive and the reaction times required to prevent collisions.

### **1.4** Thesis Outline

For this thesis, the outline is divided into five chapters. Chapter 2 contains the background or related work on the mentioned topic. At first, a brief overview of the background work related to Hardware-Software Co-design is discussed. Later some related work with ZYNQ APSoC is provided. The present scenario of the available related platform is also discussed. Afterward, the applications of Zynq both in research and the present application has been discussed.

Chapter 3 discusses the Zynq platform, its architecture, and its specific features regarding communication between the processors and operating system descriptions. This section focuses on the PL & PS part interface types and how each port can be used to transfer data from PL to PS and the corresponding IP cores to establish the communication. This chapter also focuses on the software platform that can be used for designing the hardware and the software development tool for PS part considering the Standalone Bare-Metal operating system and describes how each of these interfaces is dependent on each other. This portion also describes the methodology to be followed to implement the design and the analysis.

Chapter 4 describes the design and implementation part using the Vivado software platform and software development kit (SDK). Vivado has been used for designing IP cores with Verilog RTL based designing system. This part also discussed the test bench of the designed IP core. Finally, at the end of this chapter, it discusses the different IP cores and the corresponding designing techniques and the implementation of hardware design to transfer the data from the custom based IP core located at the FPGA part and transferring a stream data to the DDR memory of the Zynq processing system using AXI interconnect. The implementation of the different portbased design is also explained in this chapter. It also discusses the software part implementation using the Software Development Kit (Xilinx SDK) tool. A complete flow diagram of the data/packet moving process is also described in this section. It also discusses the Standalone Bare metal operating system implementation of the processing system.

Chapter 5 describes the performance analysis of the interfaces after the hardware implementation of the design on the Zedboard using JTAG port. It also discusses the data collection of the time in different data transferring conditions for different slave port to transfer

the data from PL to PS. Graphical based performance analysis of the AXI interconnection ports is also presented for the different traffic conditions and the packet size.

Chapter six is the conclusion where the summary of the full thesis is discussed along with the future work scope and analysis plan. A complete flow graph of the thesis outline is presented in Figure 1-3.

Figure 1-3: A flow graph of thesis outline

## **2. BACKGROUND AND RELATED WORK**

A literature review on the latest cutting-edge method of data transfer for hardware/software Co-Design is the first approach of this work for achieving the goals defined in the previous chapter. There is also a need for a thorough understanding of the Advanced Extensible Interface (AXI) protocol bus and the software and hardware platform.

## 2.1 Background:

### 2.1.1 Hardware-Software co-design

The Hardware / Software co-design has been a popular field of research for developers. However, hardware/software (HW / SW) co-design can be defined as a simultaneous development of the system's both hardware and software sides. The HW parts should be run in FPGAs or ASICs on an all-inclusive processor while the SW parts are being translated into a low-level programming language.

### ASIC- Application-Specific Integrated Circuits

The integrated circuits ASICs are fully configured for a specific purpose. It can be configured in a specific application where high efficiency and lower energy consumption are the key issues. The optimization process can be controlled by the engineers due to its reconfigurability for a specific application. This implies that for a particular application it produces very high output and low power consumption. By completely configuring the ASICs, engineers can save on additional resources and reduce large-volume costs dramatically.

#### FPGA- Field Programmable Gate Arrays

As a configurable computing platform, the Field Programmable Gate Arrays (FPGA) has become especially important for high-performance computing applications. It can typically improve performance considerably over the conventional computing platforms while reducing energy consumption considerably. Hardware designs typically take a bit longer time equivalent to software designs. A wide variety of resources are available at FPGA such as the Flip-flop (FF), LUT, Optical Signal Processing and RAM Block (BRAM). FFs are small gate elements that can store a data bit between cycles. For each particular set of inputs, LUT has an N-bit Table of preset responses. However, DSPs are a block of interconnected computational units like the adder, subtractor, and multiplier. BRAM is a single-port or dual-port RAM block very similar to the fabric of the FPGA.

## Zynq-7000 SoC

The Xilinx Zynq-7000 SoC is a group of FPGA and CPU chips integrated into the same chip, which allows effective and quick interaction during software acceleration. Software Acceleration is the method of maximizing system function and delegating performance-critical functions for specialized external hardware so that it can reduce program execution time. The dual ARM Cortex-A9 CPU and two Neon co-processors are used on every 7000 chip array. Each of the dual processors has independently owned high speed, low-power cores, and L1 level and 32 KB data cache. Additionally, 512 KB of L2 cache is shared. This also allows FPGA and CPU to share external memory much greater than the usable internal memory by adopting the DDR3 storage interface. Zynq SoC has a Processing System (PS) and a Programmable Logic (PL) in its internal structure. In the PS part, the application processing unit (APU) is located.

### 2.2 Related Works with Hardware/Software Co-Design:

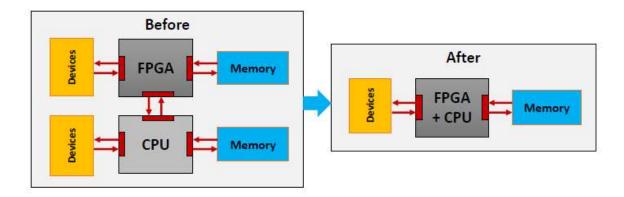

Co-designing the hardware/software refers to the simultaneous design of both software and hardware in a system. The software is executed in processing elements such as Central Processing Units (CPU), and Digital Signal Processors (DSP). Application-specific Integration Circuits (ASICs) or FPGAs typically implement hardware logic. Since software and hardware systems have different characteristics, there is potential for a hybrid system to utilize the best of both worlds. The publication [11] analyzes the key properties of co-designing hardware/software: teamwork, flexibility, precision, and complexity.

Hardware/software co-design has evolved considerably since it was first used in electrical systems. Co-design 's earliest use case appeared in the 1980s [12]. Partitioning was the key problem to be addressed during the first generation of co-design. Two approaches have been proposed: (a) starting with pure software and then migrating software functions to hardware; [13],

and (b) starting with a hardware-only system and ending with a codesigned system[14]. Multicore and multiprocessor were used in the second generation, and thus multi-threads were used instead of a single thread. Thread planning is one of the biggest challenges in this approach. Besides, the interface and communication between hardware /software are important because they have a drastic impact on device efficiency and design space [15]. According to [11], the co-design is now in its third generation, where it shortens the time-to-market cycles by optimizing the flow of hardware/software development. Also, different languages for the hardware /software co-design are needed. The language for both hardware and software development should be appropriate as per their platform. Neither Hardware Description Languages (HDLs) nor C/C++ seems to be able to replace the other.

The major difference in hardware/software codesign is described in [12] as compared to pure-software design. They are, 1) Allocation: there are plenty of options for SoC architecture design and designers need to pick suitable resources for their systems among different processors, ASICs, FPGAs, DSPs, etc. 2) Binding: Developers having different resources in SoC(s), have to link applications, tasks or variables to similar resources; partitioning, stated in the first generation, was one kind of binding. In [16] it was proved that the binding mechanism is an NP-complete problem, so finding an optimal solution is time-consuming. 3) Scheduling: several resources are shared (such as processors, memory, and communication bus, etc.) so, real-time analysis is required when complex co-design is being implemented.

Additional factors today influence the development of hardware/software co-design [11]. Heterogeneous SoCs is a new phenomenon where many more resources can be combined into a single chip, e.g. one multi-billion transistor chip includes multiprocessors, DSPs, FPGA, IP, memory, and peripherals. First, the complexity of SoC(s) systems is highly increasing, as many SoCs need to work together. Last but not least, as systems become more complex, it is very common for different subsystems to be introduced by different suppliers, so all entities must share shared standards.

Figure 2-1: FPGA and CPU Integration[11]

### 2.3 Related Works with ZYNQ 7000:

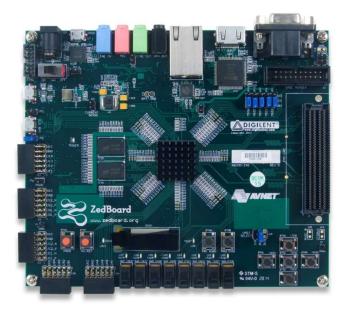

The Zynq architecture and its flexibility of communication have attracted may researchers to work on it. Particularly in this thesis, all the implementation is based on the Zedboard, which features an XC7Z020 Zynq device. Zedboard is a joint venture between Xilinx, Avnet (the distributor), and Digilent (the board manufacturer) [2]. The books [1] & [2] mainly focus on the Zynq platform and its architecture on different topics.

A paper for analyzing the impact of hardware accelerator data transfer granularity on the performance of a typical embedded system is presented in [3]. An insight into maintaining coherency between CPU caches and accelerator data in a multi-core embedded system is discussed in [4]. The same research paper emphasizes on possible hardware architectures and related software solutions to reduce the problem. The research [4] concludes that the optimal solution is more dependent on the type of application. It also discusses the solutions at the architecture level but it doesn't provide any performance comparisons on the mentioned topic. In [5] the author mainly explores the performance of the ACP and GP slave ports. There are several publications on the implementation of image processing. In [6] the author uses the ZYNQ architecture for image restoring contrast by defogging. This type of application is becoming more popular in automobile industries. Hence, application development using such SOCs is developing rapidly. Another research work discusses the driver awareness monitoring system [8]. A car simulator has been used to prove their method. A project of Microsoft's Catapult was explored in [9] which is mostly concentrated on the acceleration of the Bing Search Engine data center. The project combines the

server rack computers and FPGAs used in achieving a significant improvement in the ranking throughput of each server. This project did not use the Zynq technology.

In this research paper, a custom design is implemented for the data transfer from PL and PS DDR memory. AXI interface is used for the internal data transfer which is on-chip. On the contrary, data transfer between two devices with measurable distance has some critical challenges when the link operates at high frequency, and also the communication becomes hard to maintain. Hence, efficient on-chip communication between two different types of processors was an important topic to ensure the optimal data flow. The performance analysis between the available port to transfer the data from the PL to the PS portion of the Zynq was analyzed in different conditions and a graphical representation of the performance analysis is also discussed.

## 2.4 Some More Work On A Different Platform

Diverse research on the use of reconfigurable architectures in hardware-software co-design applications has been shown in the industry and academia over the last few years. Studies and experiments on different platforms were also performed. The following are some of these works.

#### 2.4.1 HW/SW Co-design for Exascale System

The study was conducted by the "Lawrence Berkeley National Laboratory" in a joint project involving three laboratories. The experiment was performed on Codesign for Exascale(CoDEx), a robust co-design platform for hardware-software, which provides applications and algorithm researchers with an unparalleled opportunity. This paper discussed the comparative analysis and the experimental results of the "Green Wave" co-design process and the conventional HPC system (Intel Nehalem and Nvidia) in a project to develop climate modeling and seismic imaging applications. The result shows a significant benefit in using co-design applications. The results indicate that the co-designed device provides 5 to 7.6 times higher performance compared to a traditional HPC design for similar constraints lithographic scale, on-chip region, and memory interface technology. [22]

#### 2.4.2 Coarse-Grained Reconfigurable Accelerators (CGRA Architecture)

Several studies were performed recently on the CGRA architecture. In one recent study, domain-specific accelerators (DSAs) has been implemented on a CGRA platform. A new approach for assembling and characterizing the reconfigurable accelerators, based on data flow was implemented in this report. The concepts of functional programming, which can resolve the challenges of the efficient design of CGRA, have been explored. The comparative resource utilization analysis with the other state-of-the-art high-level synthesis(HLSs) is the main advantage of the proposed approach.[23]

In another work [24], the implementation was in the same CGRA based platform. The work described the design and implementation of a "C-programmable hybrid coarse-grained array, single-instruction, multiple-data (CGA-SIMD)" based SDR accelerator. It also analyzes the performance of the design for the SDR based baseband signal processing and also in terms of power efficiency.

#### 2.4.3 Different Embedded System Platform for Co-Design Applications

There are a lot of works with embedded system Co-designing applications. One of the research papers [25] discusses the rapid prototyping in a real-time embedded system platform. A design cycle has been proposed for this framework. The main target of this research is to have an integrated framework Co-design and Rapid-Prototyping System for Applications with Real-Time Constraints. The design flow includes implementation, specification-synthesis, system-synthesis, and performance analysis.

Another work focuses on the unified designing approach for the HW/SW components in an embedded system [26]. However, the goal of this work is mainly to reduce the gap between hardware and the software in the design method. This was done by introducing the object-oriented and aspect-oriented programming, which provides a unified description for an embedded system. The purpose of this work is to explain how the components and element unified design weaving processes can only be applied using the standard interface and its metaprogramming. Hence, the separation of the hardware/software implementation in unified implementation takes place directly via changing at the language level, thus enabling integration with various -related HLS software and flow architecture. The status and evolution in the field of co-designing of an embedded system has been discussed in [27],[28]. These review papers discuss the major processes in the field of computeraided embedded systems. In the current system analysis, co-simulation of HW/SW is the main requirement.[27]

However, embedded systems face special problems for the evolution of systems. They are embedded in a dynamic environment and they have to interact with the evolving processes of different organizations. To address these problems the research and the industrial practices need to improve.[28]

### 2.4.4 FPGA and other SoC Platforms

For low power and distributed applications, FPGA and SoC platforms are widely used for the research and industry sectors. In one of recent the research works,[29] an algorithm has been proposed to determine and manage the problems of resource management/ allocation and task assignment. To assess the timing of all assignments and coordination events in the system, a priority task scheduling was also developed. Another research work represents[30] an experimental analysis and of an SoC platform. This "Dalton Project" shows that platform tuning(parameterization of the IP and IC) can increase the performance of an SoC-based embedded platform.

However, reconfigurable architecture and the computing system has brought immense performance increment in terms of power and resource-based efficiency[31]. Reconfigurable Computing has established groundbreaking accelerator architectures, hardware, and RTR models and support for the past 25 years. A timeline of that evolution can be illustrated in figure 2-2 [31].

Figure 2-2: A timeline of reconfigurable computing system evolution[31]

# **3. HARDWARE-SOFTWARE PLATFORM AND METHODOLOGY**

In this chapter, we introduce the hardware and software platforms that have been used in the course of this work. First, we describe the Xilinx Zynq-7000 device architecture and the AXI protocol, which manages its internal communication. Then, the software workflow is described that is used in this thesis. In the last section, the methodology for performance analysis is briefly described.

## 3.1 ZYNQ-7000 Architecture

The analysis assesses the implemented design on Z-7020, which belongs to the Xilinx ZYNQ-7000 SoC family. Detailed architecture and its features are provided in the following sections.

## 3.1.1 Overview

Xilinx ZYNQ-7000 SoC has a Processing System (PS) and Programmable Logic (PL), as shown in Figure 3-1[18]. The PS comprises of different working blocks like I / O peripherals, internal and interconnection memory interfaces. PS-PL communication is carried out via high-bandwidth AMBA AXI interfaces (define AMBA).

Figure 3-1: Zynq Block Diagram[18]

The ZYNQ framework integrates reconfigured functionality with a PS ASIC interface through this architectural scheme. This is necessary as the PL is capable of performing a parallel data-intensive task, while PS can handle the sequential process. This leads to increased performance overall. The AMBA AXI4 connects a high-bandwidth connection between the PS and PL as well as the connections within the PS. With the AMBA Standard AXI4 Interfaces, a high-bandwidth connection between PS and PL is established. This ensures effective communication with the functional units.

First, the PS is configured. Only after the PS configuration, the hardware design will be loaded into the PL fabric. Once the system starts, a hard-coded boot ROM is performed, which in turn allows PS to load a First Stage Boot Loader (FSBL) from OCM. On the second-stage, the bootloader can be used to load the kernel to DDR memory. A bitstream file can then be used to set up the PL fabric, if necessary.

Zynq-7000 family PL uses Xilinx 7 Series FPGAs such as Z-7020 (which is used in this thesis). The Zynq contains Xilinx-7 series FPGA. An external clock pin or a PS may be used to produce the clock to PL. Three PLLs (phase-locked loops) are used by PS and four input clocks are provided for the PL. Architecture manages clock synchronization between PS and PL. In a wide range of fields, such as industrial motor control, automotive and medical diagnostics, SoC devices Zynq-7000 are used. Figure 3-2 shows the target hardware platform for design and implementation.

Figure 3-2: Zedboard

### 3.1.2 ZYNQ-7000 Features

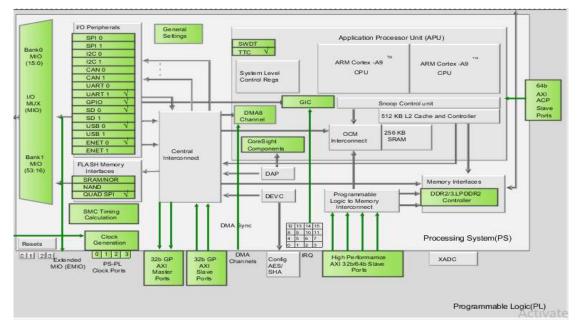

Figure 3-3[17] shows the functional blocks integrated into the ZYNQ-7000. The figure also displays the location of the Processing System (PS) and Programmable Logic (PL) within the same chip.

Figure 3-3: Zynq-7000 Architecture[18]

Application Processor Unit (APU) consists of a processing system that incorporates a dualcore ARM-Cortex A9 processor with a 32 kB level 1 cache memory. The Floating Point Unit (FPU) provides the necessary floating operation for applications such as DSP. To improve system functionality by employing data parallelism, the NEON Engine supports "Single Instruction Multiples Data" (SIMD). DMA Controller and Memory Management Unit (MMU) are also components in APU. The processor design implies automatic cache coherence between processor cores [17].

Central interconnection binds the APU to several peripherals. It uses a 64-bit AXI interface [18] based on ARMNIC301 (Network Interface Configuration). The Processing System (PS) has the "Core Sight controller" to debug and track the software design. PS usually communicates with the PL by using two General Purpose ports (GP ports) based on 32 bit of AXI interfaces. To communicate with the functional units in PS, different types of ports are provided in PL. Two 32-bit General Purpose ports are suitable for the transfer of a small amount of data, for example,

control signals. Two master ports and two slave ports are available as General Purpose ports. Four 64-bit high-performance ports provide high-performance memory access to OCM (On-Chip Memory) and DDR memory. In APU, the Snoop Control Unit (SCU) access is provided by the Accelerator Coherence Port (ACP). PL can use OCM and Level-2 cache memory. XADC (Xilinx Analog to Digital Converter) module is included in the PL for "Analog Mixed Signal" (AMS) processing It offers a dual 12-bit, 1 mega per second ADC, which allows 17 analog external input channels to access[19].

As Figure 3-3[18] shows, both PS and PL devices are mapped to system memory. Zynq has an EMIO (Extended multiplexed I/O) interface for unmapped peripherals in PS, which allows the PL pins in to use those peripherals.

## 3.1.3 ZYNQ-7000 Communication Interfaces

The Zynq-7000 family uses ARM AMBA4 AXI. An end-to-end protocol between an AXI master interface and an AXI slave interface is established by the AXI Interface. The AMBA4 consists of

three AXI interface types :

- AXI4 Memory-Mapped Interfaces

- AXI4-Lite Memory Mapped Interface

- AXI4-Full Memory Mapped Interface

- AXI4 Stream Interfaces

Figure 3-4: System-Level Address map[17]

In terms of performance and functionality, each AXI interface defines a protocol that differs from each other. The developer can choose an acceptable AXI protocol depending on the application. This enhances design flexibility.

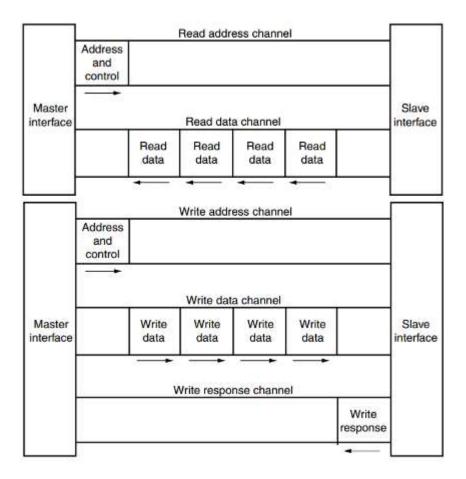

# **AXI4 Memory-Mapped Interfaces**

The AXI4 Memory-mapped interfaces have several channels to allow read/write communication through AXI interconnect from the master to the slave. These channels are distinct and include the data signal, address signal, and, control signals as shown in Figure 3-5[17].

Figure 3-5: Read and Write Channels[17]

Upon transmitting address/control or data signals, each channel employs a two-way VALID/ READY handshake process. As shown in figure 3-6[17], only when both VALID and READY signals are high, the information is transferred. There may be dependence between channel handshake signals that can result in a deadlock. AMBA AXI Protocol Specification thus specifies the dependence rules which must be complied with during the design implementation.

Figure 3-6: Two-way VALID/READY Handshake[17]

Data transmission can be concurrent and bidirectional due to different addresses and data channels to read/write. These channels are used in two kinds of interfaces with memory mapping.

#### AXI4-Full Interface

AXI4-Full interface applies a point to point burst-based protocol which offers several options for data transfer performance. By placing the first address on the address channel of the burst transfer, AXI Master initiates a data transfer. The slave needs to measure the following transaction addresses based on burst parameters (size and length). Burst size demonstrates the width of a data bit while burst length represents the number of bits in a burst. One of the most important characteristics is mentioned in [20] about the incremental burst size. For the incremental bursts and 1 to 16 bits of wrap bursts, a burst length of 1 to 256 bits is accepted. Support is given for variable data widths between 32 and 256 bits. If required, data can be upsized or downsized. There can be multiple pending addresses. Transactions like non-order transfers and unaligned transfers that provide greater overall throughput are acceptable. Safety features such as read and write access security are also included for the interface. It has an option for adding register slices during pipelines to improve performance.

## AXI4-Lite Interface

AXI4-Lite is almost the same as that of AXI4-Full interfaces but does not allow burst transfers. On a different note, it only supports a burst length of 1. The AXI Lite protocol is used by the Processing systems (PS) to set up an IP by mapping the system addresses. This can be used to transfer control signals because only some few clock cycles are needed. This requires the AXI Lite protocol. For example, if AXI Port0 uses, then port 0 address space of the General purpose (GP0) port will be used to interface the IP. This offers a fixed data width of 32-bit or 64-bit. Yet Xilinx IP only has a 32-bit big data bus[17].

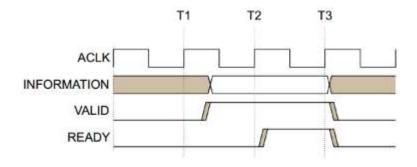

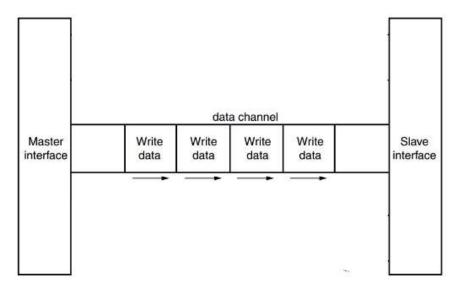

#### AXI4-Stream Interface

For applications that are usually focused on a data-centric and data-flow framework, the protocol of AXI-Stream (for high-speed streaming data) is used. However, the HLS interface has been used to transmit end to end data transmission without the need for an address. This means that data is transferred without addressing from a master node to a slave node. For each AXI4 stream, a one-way channel for handshaking the flow of data is used. This can be shown in figure 3-7[17]. For data flow applications AXI4 Stream IP may be optimized better for performance.

Figure 3-7: AXI4-Stream Transfer with Unidirectional Channel[17]

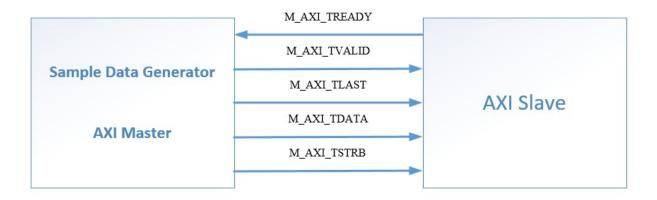

Our main emphasis for this thesis is the AXI4-stream that is used in our design for the communications system. AXI4-Stream is used in high-speed streaming data. TVALID, TDATA, TREADY, TLAST, and TUSER/TSTRB are standard AXI4 connectivity signals. The connection TUSER / TSTRB enables additional, fully user-definable information to be transferred. The detail about the AXI stream signals for designing any stream module is discussed in chapter 4.

Zynq-7000 has four high-performance (HP) AXI 32/64-bit ports, which are mostly used for reading/writing to the OCM and DDR memory through the AXI4 stream protocol. Certain features of the protocol are [17]:

- The Stream protocol has an unlimited burst length: It has different options for chosing the different burst lengths.

- It has sparse, continuous aligned & unaligned streams: A sparse stream is the combination of position and data bytes, but usually most of the bytes are data bytes. also continuous aligned stream is defined as the transfer of a number of data bytes that have no position or null bytes in each packet. On the other hand, an unaligned continuous stream may have a number of contiguous bytes at the beginning, end or at beginning and end of a packet.

- **Data transfer features:** It has different data transfer features, for example- interleave, merge, upsize or downsize. Interleaving transmission is the process to interleave transfers from various streams based on transfer types.

- Ordered transfer : The stream protocol only allows ordered transfers. The data stream should be ordered in such a way that, the low order bytes of the data stream bus will be the earlier bytes in the stream.

Table 3.1 summarizes the key features and differences of the AXI4 Interfaces.

| Interface   | Features                               | IP Replacements           |

|-------------|----------------------------------------|---------------------------|

| AXI4        | Memory-mapped address/data interface   | PLBv3.4/v4.6,OPB, NPI,XCL |

|             | Data burst support                     |                           |

| AXI4-Lite   | Memory-based address/data<br>interface | PLBv4.6,DCR,DRP           |

|             | Single data cycle only                 |                           |

| AXI4-Stream | Data-only burst                        | Local Link,DSP, TRN,FSL   |

Table 3.1: AXI4 Feature Availability and IP Replacement

### 3.1.4 Processing System and Programmable Logic Interfaces

The PS-PL interface includes all the signals to combine the PL and the PS functions. There are two types of PL-PS interfaces:

**Functional interfaces:** This interface includes AXI interconnect, extended MIO interfaces (EMIO) for most of the I/O peripherals, interrupts, DMA flow control, clocks, and debug interfaces. These signals can be used to connect the user-designed PL IP blocks.

**Configuration signal interfaces:** This includes the single event upset (SEU), Processor configuration access port (PCAP), configuration status, Program/Done/Init, etc. The configurations signals, which provide PS control, are connected to the fixed logic of the PL configuration block.

For primary data communication between the PS-PL, the following AMBA AXI interfaces are included. These interfaces are under the functional interface family :

• (M\_AXI\_GP): Two 32-bit AXI master interfaces

• (S AXI GP) : Two 32-bit AXI slave interfaces

• High-performance (HP) AXI ports (AXI\_HP): Four 64-bit/32-bit configurable buffered AXI slave interfaces. These ports have direct access to DDR memory and OCM.

• AXI slave interface (ACP port) : One 64-bit for coherent access to CPU memory

Figure 3-8: Zynq Processing System Architecture[18]

Figure 3-8[18] shows that all of the interfaces are specifically connected to AXI interconnects within the PS, with the only exception being the ACP interface, which is connected directly to the Snoop Control Unit inside the APU.

Inside the processing device, AXI interfaces are used both within the ARM APU (making connections between processing cores and SCU, cache memory, and OCM), and more broadly to link the various interconnections within the PS. These interconnect are internally connected to the central Interconnect as shown in figure 3-8.

To move data from the FPGA part to the Processing system part, the processing system part works as a slave port and the PL part works as a master port. The two GP AXI slave ports (S AXI GP) allow PL AXI master to access the PS memory on the PS subsystem or any of the PS peripherals.

The high-performance AXI ports (HP) and the ACP interface are the two highestperformance interfaces for PS and PL for data transference. The high-performance AXI (AXI\_HP) ports provide a high-bandwidth PL slave interface to the OCM and DDR3 memories of the PS. The AXI ACP interface offers a User IP topology similar to the HP ports (AXI HP). Because of its communication within the PS, the ACP varies from the HP output ports. The ACP connects to the L2 CPU cache, allowing ACP transactions to communicate with subsystems in the stack.

## 3.1.5 Theoretical Data Transfer Throughput of PL-PS Interfaces

Many other documents and descriptions are readily accessible about the use of interfaces as well as how the programmable logic can communicate with the processing system. However, most of the documents didn't fully addressed about the maximum throughput with an experimental analysis using different conditions. In this work a comparative analysis for the three interfaces was presented. However, Xilinx in their document[18] has presented about the maximum theoretical (without any overhead protocol) estimated data throughput for a single read/write operations for each of the PL-PS interfaces. Table 3.2 shows the details of that.

| PL-PS Interfaces | Data Bus width(bits) | Maximum Estimated<br>Bandwidth(MB/s) |

|------------------|----------------------|--------------------------------------|

| S_AXI_GP         | 32                   | 600                                  |

| S_AXI_HP         | 32/64                | 1200                                 |

| S_AXI_ACP        | 32/64                | 1200                                 |

| EMIO/GPIO        | 32/64                | <25                                  |

| M_AXI_GP         | 32                   | 600                                  |

Table 3.2: Theoretical Data Transfer Throughput of PL-PS Interfaces

## 3.2 Software Platforms

Designing for the Zynq system requires the use of several different software tools which together form an end-to-end work-flow which will produce a functioning Zynq system.

## 3.2.1 Vivado Design Suite

Vivado is the tool suite for Xilinx FPGA designs. Vivado is the overall project manager and is used for developing and designing the environment for the configuration of PS, and hardware design for PL. The platform also includes peripheral simulation and logic analyzer. The hardware portion will be primarily designed using Xilinx Vivado software. This program can be configured with the presets of the particular board one is using, which allows it to automatically generate a large number of circuit connections that would otherwise need to be specified manually. Is also contains an extensive catalog of hardware IP which can be integrated into one's design. Many of these IP blocks are targeted at signal processing applications such as the Fast Fourier Transform block.

Vivado also contains an extensive set of analysis tools. Hardware expressed using IP blocks or HDL can be simulated and its behavior analysed on the signal level. This can be vital in applications where a single clock cycle delay in a particular operation could cause the system to fail. Additionally Vivado allows for design validation which will quickly pick up any errors or critical warnings in the design before it is processed. This is especially useful as the full bitstream generation flow can take a very long time, over an hour depending on the extent of the design. Vivado also supports on-chip debugging which allows for a live analysis of the signal values while the system is powered on and operating. The most important functionality that Vivado provides is the ability to take a hardware bitstream that can be loaded onto the board. This is a multistage process that begins with a project specified at the register transfer level (RTL) and ends with a bitstream that describes the FPGA custom hardware. The first of these stages is called synthesis. Synthesis is essentially the process of taking the RTL description which may be a combination of IP blocks and HDL and convert this into a logic gate level representation. Figure 3-9 shows the VIVADO software starting window.

Once the design has been synthesized and a gate-level representation has been generated, it must be converted to be compatible with the FPGA. This stage which seeks to configure the FPGA resources to represent the gate-level logic expression is called implementation [21]. With the design implemented it must be converted to a format that can be loaded onto the board, this process is called bitstream generation.

#### **3.2.2** Software Development Kit (SDK)

SDK is an Eclipse-based Integrated Development Environment (IDE) that has been extensively used to meet the unique needs of the Zynq framework. Using the "Program FPGA "command, the hardware description that has been exported from Vivado will be loaded to the chip via SDK. This hardware description can also be used by the SDK to create a Board Support Package (BSP). The BSP contains drivers that are automatically generated for the hardware that was implemented in the design. This allows the user to communicate with the board in C/C++ code using driver calls.

The SDK's principal function is the development of the software part. When a new application is created, one can choose between a bare metal\standalone application or a Linux application. The bare metal application runs directly on the hardware, with no OS layer. That gives an outstanding performance. The Linux application option will create an application. When it builds, it will be cross-compiled using the GNU Linux compiler. This is appropriate for the ARM processor on the chip in use. The cross-compiled application can then be transferred via storage media to the board and executed from the OS running on the board.

Another important aspect of the SDK is its debugging capabilities. Applications can be started on the hardware remotely, and a connection can be maintained that allows SDK to handle the control of the program flow. Breakpoints and operation stepping function just like they would in a conventional IDE but the code is being executed remotely.

Figure 3-9: Hardware-software design tools

## 3.3 Methodology

The main target of this thesis is to design a hardware system in order to evaluate the performance of AXI interfaces (ACP, HP and GP). The design is implemented on Zedboard. The AXI Interfaces have to be evaluated under different criteria and conditions to determine the most appropriate interface as per the application. The approach is as follows:

- 1. Evaluation of three different AXI Interfaces:

- 1.1. Designing the Hardware in VIVADO for three different AXI4 Interfaces.

- 1.2. To analyze the performance of three AXI4 interfaces determine several Test cases.

- 2. Implement the Software algorithm on SDK.

- 3. Analyze the test result data, and determine the application-oriented usage of each AXI4 interface.

- 4. The test cases to evaluate the performance of AXI4 interfaces:

- Data transfer time of write operation DDR memory of PS.

- Data transfer time for different PL clock frequency.

- Data transfer time for different data widths and burst transfer.

- Energy consumption during data transfer.

## 4. DESIGN AND IMPLEMENTATION

The purpose of this chapter is to present the complete design flow in detail and tools used for implementing the sample data generator. Since the target device is a Xilinx Zynq platform, the Xilinx tool-chain is used. It is composed of Vivado HLS (RTL flow and the HLS), for designing the accelerator and the hardware part and the Xilinx Software Development Kit (SDK) for modifying the original software to work on the accelerated system. The design flow includes hardware design and software design using the tools described in the previous chapter. The hardware design process will be described at first, followed by the software implementation on SDK to run the application on the target board.

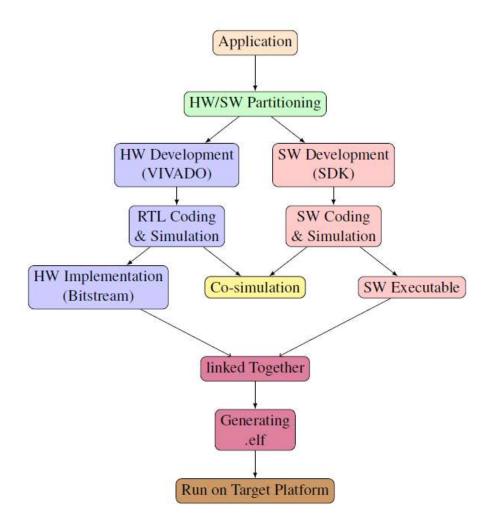

#### 4.1 Hardware-Software Design Co-simulation process

A description of the Harware / Software co-design to be used in this study is shown in figure 4-1. The first step in hw/sw co-design is the high-level specs of the system behavior which includes the behavioral simulation, power, functionality, and other constraints of the expected circuit or design.

The following move is to partition the functionality of device design between the software and hardware. The partitioning of the Hardware / Software is the mechanism that separates the functions into a part of the hardware and software. The partitioning phase gathers the information from the profiling task to make decisions about the instances to map the software and the hardware. Once the instance of hardware and software creation has been established, and the interfaces has been established between them, the next step is the coding & simulation. In this stage, specs are refined, where autonomous system specifications are translated into HW and SW specifications. When the coding & simulation action is over, the subsequent phase is authenticated by the design flow, which collectively simulates both the hardware/software. This is called the co-simulation process.

The co-simulation process verifies whether or not the design objective has been achieved. When the specification is appropriate, the co-simulation ends. The design cycle is repeated until the satisfactory design output is reached; if the design is not satisfactory, the design returns to the HW/SW partitioning step. If the results of co-simulation are acceptable, then the next task is the simulation-level implementation of both hardware and software parts.

Figure 4-1: Hw/Sw Co-design Flow

Once the partitioning task is finished, the executable program and the bitstream files are combined to create the elf file and to run it on the hardware platform. The performance of these parameters relies on the level of design constraints and the reduction in design costs. If the design parameters are not fulfilled, then to boost the performance some optimization techniques must be used to obtain the desired performance.

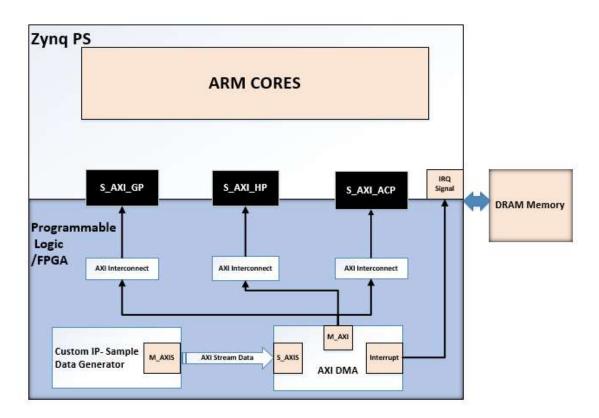

#### 4.2 Hardware Design

This portion describes the hardware design implementation using VIVADO Design Suite software. The main idea is to integrate custom stream IP (Sample Data generator) and through the AXI-Bus interface and DMA engine to establish the communication between the processing system and FPGA. Where, through the custom IP, the FPGA portion will send the data to the DDR memory which is accessible by the ARM processing system. This communication has been established using different AXI slave interfaces.

The hardware design implementation is described in three main sections. Firstly, to start with the proposed design, a custom IP "Sample Data Generator" is designed using the RTL flow. The designed IP is then modified with the Verilog code. Secondly, the designed IP is verified using a Vivado logic flow simulation to test the proper functionality. Thirdly, the "Sample Data generator" block IP will be integrated with the AXI DMA and AXI-Bus interfaces as illustrated above.

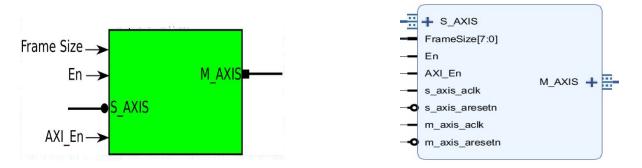

#### 4.2.1 Designing "Sample Data Generator" using RTL Flow:

The data generator is a customizable, programmable logic core designed in Verilog language, mostly known as "Hardware Description Language" (HDL). It produces a stream of sample data which the AXI DMA Core finally receives. The clock is created by the PS-configured FPGA common clock. The clock is produced by toggling on each nth edge of the common clock and N is a natural number greater than 1. Finally, the data generator introduces a standard FPGA clock-driven AXI 4-stream protocol. The new value is moved to the stream and to the AXI DMA core, when the counter register is updated.

There are two modules in the sample data generator: the slave port and the internal data generation counter. In Figure 4-2 one can see the a graphical representation of the inputs, outputs, and mutual connections of these modules. At the top level of sample data generator, the AXI4-Stream interface is implemented.. In the designed AXI4 stream module the "En- Enable Signal" is used to enable and disable the module. "AXI\_En – AXI Enable" plug is used as an input signal to switch between the S AXIS and the Frame Size.

Figure 4-2: The sample data generator AXI stream module

The clock is derived by measuring the rise edges of the general FPGA clock/ACLK as well as by restoring the output as per the user input value. In figure 4-3 and in the entire module in Appendix A, the reset circuit and counter implementation of the sample data generator can be illustrated.

```

// sample data generator

1

reg [C_M_AXIS_TDATA_WIDTH-1 :0] counterR ;

2

3

assign M AXIS TDATA = counterR ;

4

assign M AXIS TSTRB = {C M AXIS TDATA WIDTH/8 {1 'bl}};

5

6

7

// counteR circuit

always @(posedge M_AXIS_ACLK)

8

9

if ( ! M AXIS ARESETN ) begin

10

counterR <= 0 ;

11

end

12

else begin

if ( M_AXIS_TVALID && M AXIS TREADY )

13

14

counterR <= counterR +1;</pre>

15

end

16

17

18

// circuit to count number of clock cycles after reset

19

sampleGeneratorEnR;

reg

20

[7:0] afterResetCycleCounterR;

reg

21

22

always @(posedge M AXIS ACLK)

if ( ! M AXIS ARESETN ) begin

23

24

sampleGeneratorEnR<= 0;</pre>

25

afterResetCycleCounterR <= 0;

26

end

27

else begin

28

afterResetCycleCounterR <= afterResetCycleCounterR +1;

29

if (afterResetCycleCounterR == C M START COUNT)

30

31

sampleGeneratorEnR <= 1;</pre>

32

end

```

Figure 4-3: Clock cycle and counter circuit for sample data generator

The clock is being used in the counter data generator so that a counter register is increased each time the clock is changed from 0 to 1. As a result, for an ACLK clock time, the TVALID register is set to 1. The faster ACLK clock is used in the data generation circuit. Figure 4-4 presents the data generation circuit with the implementation of the TVALID and TLAST signal, while *Appendix A* displays the module program as a whole.

70 // M AXIS TVALID circuit 71 tValidR; rea 72 assign M AXIS TVALID = tValidR; 73 74 always @(posedge M AXIS ACLK) if ( ! M AXIS ARESETN ) begin 75 76 tValidR <= 0; 77 end 78 else begin 79 if (! En) 80 tValidR <= 0; 81 else if ( sampleGeneratorEnR) 82 tValidR <=1; 83 end // M AXIS TLAST circuit 84 85 reg [31:0] packetCounter; always @(posedge M AXIS ACLK) 86 if (! M AXIS ARESETN ) begin 87 packetCounter <= 32'hfffffff;</pre> 88 89 end 90 else begin if ( M AXIS TVALID && M AXIS TREADY ) begin 91 92 //if ( packetCounter == (FrameSize-1) ) // packetCounter <= 32'hfffffff;</pre> 93 if ( M AXIS TLAST ) 94 95 packetCounter <= 32'hfffffff;</pre> 96 else 97 packetCounter <= packetCounter + 1;</pre> 98 end 99 end 100 101 assign M AXIS TLAST = ( packetCounter == (FrameSize-2) ) ? 1 : 0;

Figure 4-4: Data Generation Circuit

#### 4.2.2 AXI4-Stream interface signals

The IP sample data generator is interfaced with 5 signals at AXI4 output.: M\_AXI\_TREADY, M\_AXI\_TVALID, M\_AXI\_TLAST, M\_AXI\_DATA, and M\_AXI\_TSTRB. Figure 4-5 illustrates the AXI4-Stream protocol using 5 signals.

Figure 4-5: AXI4 stream signals

A data transfer for a sample data generator which is an AXI stream module can be seen from figure 4-5. The slave (AXI Slave) must configure the TREADY signal, which indicates that the slave is prepared to accept the data transmission, before transmitting the data. The master will be able to write the stream of data through the TDATA bus after the signal is configured. The master must also configure the TVALID signal, that shows valid data in the stream. Otherwise, the slave will ignore it. After a transfer is complete the master sets the TLAST signal. The TSTRB signal is indicating the amount of valid data bytes in the data stream. For example, in a transfer, the data frame consists of 3 data bits. In this case, while implementing the sample data generator, the 4-bit constant "1111" can be safely written.

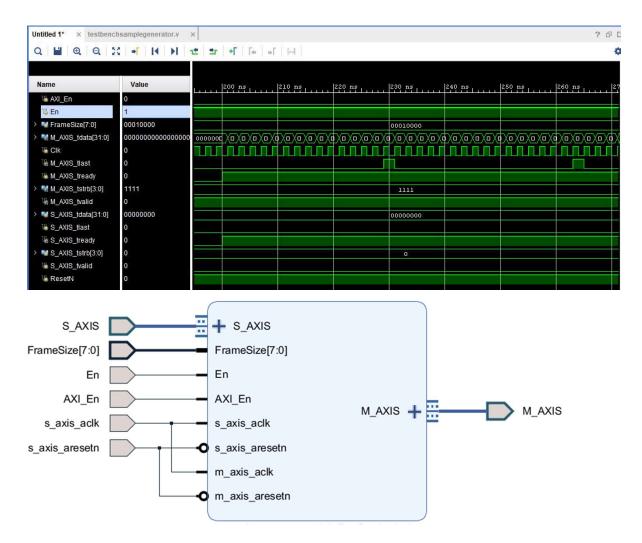

#### 4.2.3 Sample Data Generator- Testbench Logic Simulation

A test bench was developed to check proper functionality of the AXIS interface. The behavioral simulation was performed in the Vivado Design Suite, the default design development environment for Xilinx devices. The test bench produces an input of 100 MHz ACLK clock for the generation of a series of sample data frames. figure 4-6 shows the wave-diagram generated by the simulation environment. The testbench was written in Verilog code. The TDATA bus maintains the same frequency of the clock, as seen in the wave diagram created by the Vivado simulator. On the testbench design wrapper level, a customized behavior was written indicating the appearance of the TLAST signal after 16 cycles of the clock. In this wrapper level the block design is wraped into a vhdl or verilog file so it can be synthesized to generate the output products.

From the below figure it can be observed that, whenever the TLAST signal appears, it shows the end of the last frame of the data. The testbench also shows the proper functionality of the sample data generator. When the "En" signal falls to 0, there is no TDATA or TLAST signal. That means, no stream of data will pass when the "En" signal is not enabled which disables the stream module. These signals are reasonably straightforward. The top-level Verilog-code for the testbench of the sample data generator can be seen in Appendix B.This logic simulation ensures the proper functionality of the designed stream module.

Figure 4-6: The sample data generator test bench simulation showing the logic simulation wave diagram

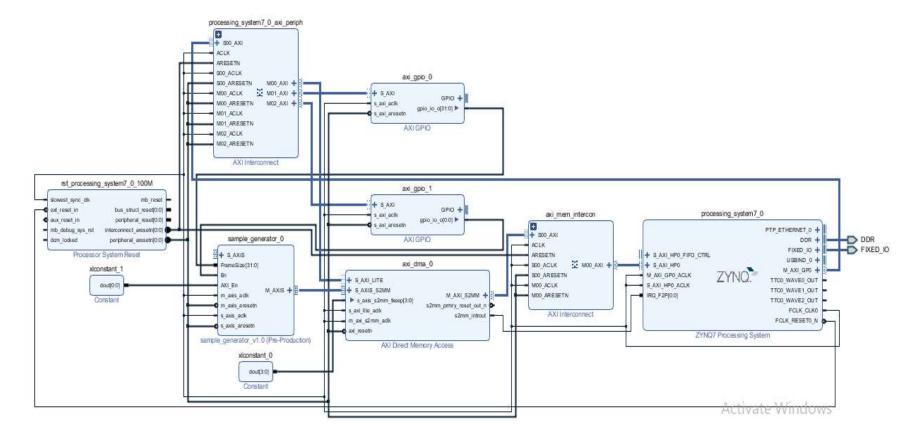

#### 4.2.4 Hardware Design with VIVADO Design Suite

The hardware design is done in the Vivado design suite. It is used to configure and connect the Zynq Processing System with the other Intellectual Property (IP) cores from the Xilinx Embedded IP library as well as with the custom-designed IP "Sample Data Generator".

Figure 4-7: Basic Hardware Block Diagram

Figure 4-7 shows the proposed hardware architecture. The custom-designed PL block which is named the "Sample Data Generator" is responsible for generating a series of data. The series of data is then passed to the PS using AXI DMA. AXI DMA has memory mapped interconnection between the PL and PS. The used memory is specified through mapping. DDR has different pre-allocated ranges of addresses that have to be properly chosen in hardware modules (in the Vivado design suite) and in software modules (in the Xilinx software development kit - SDK). As the data will be passing from the PL side to PS side, the AXI DMA is working as a master port and the available AXI stream interfaces e,g. S\_AXI\_GP, S\_AXI\_HP, S\_AXI\_ACP will be working as a slave port. After the transfer of each packet from the PL side to PS DRAM

memory and interrupt will be initiated from the PS side to start new data transfer. Data transfers between hardware and software are supported by Xilinx IP cores.

From the previous section, when the RTL is successfully verified by the logic simulation testbench verification, the "Sample Data Generator" can be exported in IP format, to be used in Vivado design. This is done by exporting the IP in the repository. The exported design should be copied into the project's local IP repository, so it appears in the list of available IPs. All the necessary components are added to the design and connected appropriately. The Processing System and the accelerator should share a memory space to store the source and destination grids, which is the DDR memory. The sample data generator can access the DDR through the DMA and AXI slave ports of the Processing System (PS).

Xilinx's programmable logic core, AXI DMA (Direct Memory Access), is implemented in VHDL. It is AXI4- compliant and can be accessed from AMBA bus from the Z-7020 SoC side of the PS (Processing System). It matches with the input and output AXI4 stream defined as stream to memory mapping (S2MM) and memory mapping to stream (MM2S) ports separately. These AXIS interfaces support TDATA buses which are 8, 16, 32, 64, 128, 265, 512, and 1024 bit long. The AXI DMA IP handled all memory transaction address generation, scheduling, and burst formatting. For the other analysis, the burst size was also varied to measure the performance. Most connections are generated automatically via Vivado after initializing the core to the graphical Vivado block design. The sample data generator can now be linked as an AXIS master data source in the design. Figure 4-8 displays the entire Vivado block design of the implemented system. Figure 4-9 shows the mapping of the address for all three interfaces.