# APPLICATIONS OF TWO-DIMENSIONAL LAYERED MATERIALS IN INTERCONNECT TECHNOLOGY

by

Chun-Li Lo

## **A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical & Computer Engineering West Lafayette, Indiana December 2020

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

School of Electrical & Computer Engineering

Dr. Sumeet Kumar Gupta

School of Electrical & Computer Engineering

Dr. Muhammad Ashraful Alam

School of Electrical & Computer Engineering

Dr. Dana Weinstein

School of Electrical & Computer Engineering

Dr. Wenzhuo Wu

School of Industrial Engineering

# Approved by:

Dr. Thomas I-P. Shih Head of the Graduate Program Dedicated to my family

# ACKNOWLEDGMENTS

First and foremost, I would like to express my most sincere gratitude to the two advisors/mentors in my career of research – Prof. Zhihong Chen at Purdue University and Prof. Tuo-Hung Hou at National Chiao Tung University, Taiwan. I thank my Ph.D. thesis advisor, Prof. Chen for giving me the opportunity to join her group back in the end of 2015, when I made a tough decision to leave my original position and pursued an unknow future. Prof. Chen provides me with guidance not only on research conducting but also on presentation skills, which I believe I will keep benefiting from throughout my lifetime. She sees every student different and unique, and hence tailors different advising tactics for different students. I cannot thank her more for making me one of the most outstanding researchers in this field. I also thank Prof. Hou, my Master degree thesis advisor, for introducing the world of research to me. He taught me how to write a technical paper and how to deliver a good presentation, which I benefit from even throughout my Ph.D. study. Moreover, I appreciate his advice on my career decisions even after I graduated from his group. Without the two advisors/mentors, I will never be a bit close to success.

I would like to thank current and former group members from Prof. Chen's and Prof. Appenzeller's groups. Without the greatest-known supports from them, my thesis would never be completed. I especially thank my two mentors, Ruchit Mehta and Sunny Chugh, and my partner, Shengjiao Zhang for all the guidance, discussions, and the great time working together. I also thank the staffs and members at Birck Nanotechnology Center for making conducting research possible. I especially thank Daniel Hosler for the greatest help with constructing the system my thesis highly depends upon.

I thank the company, whether in person or not, of all my friends – too many names to be included here. Without their encouragement, or even simply the joking around, I would have never come this far.

Last but not the least, I thank my family for giving me such a wonderful life and for making me who I am. I am particularly indebted to my mother, Shu-Min Huang, who gave up her decent job when I was young to dedicate all her life to me and my sister.

# TABLE OF CONTENTS

| LIST  | OF TABLES                                                            | 7    |

|-------|----------------------------------------------------------------------|------|

| LIST  | OF FIGURES                                                           | 8    |

| ABST  | RACT                                                                 | . 14 |

| 1. IN | NRODUCTION                                                           | . 16 |

| 1.1   | State-of-the-art Cu Interconnect Technology and its Challenges       | . 16 |

| 1.2   | Introduction to Two-dimensional Layered Materials                    | . 20 |

| 1.3   | Motivation of Integrating 2D Layered Materials with Cu Interconnects | . 21 |

| 1.4   | Synopsis of the Thesis                                               | . 23 |

| 2. T  | WO-DIMENSIONAL LAYERED MATERIALS BEYOND GRAPHENE AS CU               |      |

| DIFFU | JSION BARRIERS                                                       | . 26 |

| 2.1   | Introduction                                                         | . 26 |

| 2.2   | Simulation and Experimental Procedures                               | . 27 |

| 2.    | 2.1 Density Functional Theory (DFT) Calculations                     | . 27 |

| 2.    | 2.2 Preparation of 2D Materials                                      | . 28 |

| 2.    | 2.3 Fabrication of MOS Capacitor Structure                           | . 29 |

| 2.    | 2.4 TEM/EDS/EELS Analysis                                            | . 29 |

| 2.3   | Results of DFT Calculations                                          | . 30 |

| 2.4   | TDDB Measurements and Lifetime Prediction                            | . 32 |

| ,     | Transferred h-BN                                                     | . 39 |

| ,     | Transferred MoS <sub>2</sub>                                         | . 39 |

| ]     | Directly-grown MoS <sub>2</sub>                                      | . 39 |

| 2.5   | STEM/EDS/EELS Analysis                                               | . 39 |

| 2.6   | Conclusion                                                           | . 42 |

| 3. D  | EVELOPMENT AND EVALUATIONS OF BACK-END-OF-LINE COMPATIBLE            |      |

| TWO-  | DIMENSIONAL DIFFUSION BARRIERS                                       | . 43 |

| 3.1   | Introduction                                                         | . 43 |

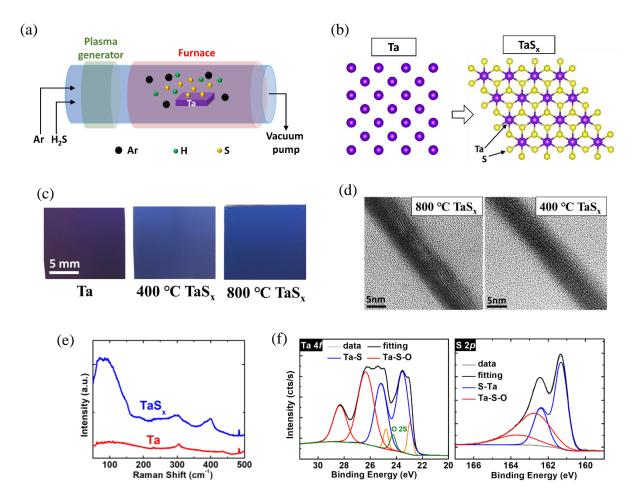

| 3.2   | Material Preparation and Characterizations                           | . 45 |

| 3.3   | Diffusion Barrier Property Tests                                     | . 45 |

| 3.4   | Comparison of MoS <sub>2</sub> Grown at Different Temperatures       | . 49 |

| 3.5                                                              | 5 Co              | nclusion                                                             | 51 |  |  |  |

|------------------------------------------------------------------|-------------------|----------------------------------------------------------------------|----|--|--|--|

| 4. TWO-DIMENSIONAL TANTALUM SULFIDE AS BEOL-COMPATIBLE DIFFUSION |                   |                                                                      |    |  |  |  |

| BAR                                                              | BARRIER AND LINER |                                                                      |    |  |  |  |

| 4.1                                                              | Int               | roduction                                                            | 52 |  |  |  |

| 4.2                                                              | Ma                | terial Preparation and Characterization                              | 53 |  |  |  |

| 4.3                                                              | Те                | sts of Liner and Diffusion Barrier Properties                        | 57 |  |  |  |

| 4                                                                | 4.3.1             | Liner Properties                                                     | 57 |  |  |  |

| 2                                                                | 4.3.2             | Diffusion Barrier Properties                                         | 61 |  |  |  |

| 4.4                                                              | Ot                | her Aspects of Using TaS <sub>x</sub> as Diffusion Barrier and Liner | 63 |  |  |  |

| 2                                                                | 4.4.1             | Electromigration                                                     | 63 |  |  |  |

| 2                                                                | 4.4.2             | Cu Corrosion during Sulfurization                                    | 64 |  |  |  |

| 4.5                                                              | Co                | nclusion                                                             | 67 |  |  |  |

| 5.                                                               | VERT              | TICAL CONDUCTION OF 2D LAYERED MATERIALS                             | 69 |  |  |  |

| 5.1                                                              | Int               | roduction                                                            | 69 |  |  |  |

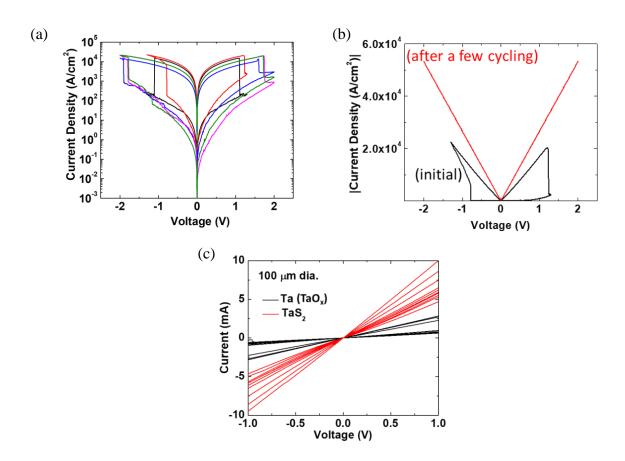

| 5.2                                                              | Im                | pact of Oxide on Vertical Conduction                                 | 70 |  |  |  |

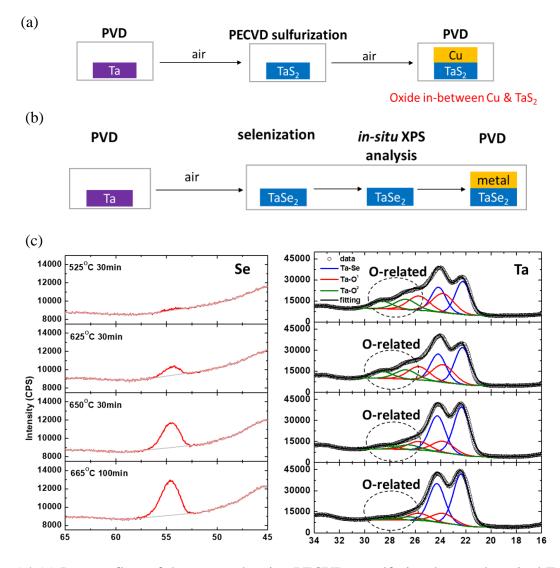

| 5.3                                                              | Re                | alization of Oxide-Free Interface                                    | 74 |  |  |  |

| 4                                                                | 5.3.1             | In-situ 2D Material Formation with Metal Deposition                  | 74 |  |  |  |

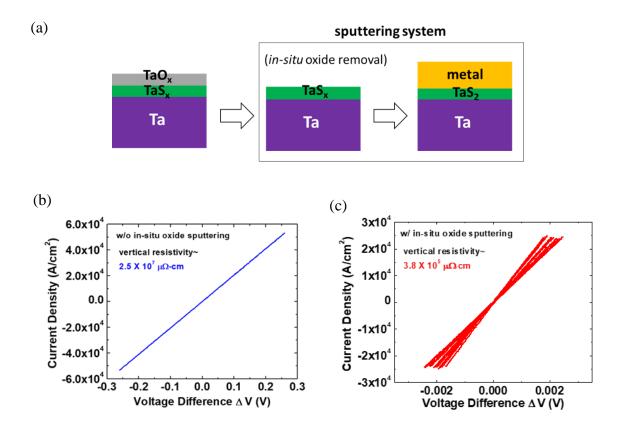

| 4                                                                | 5.3.2             | In-situ Oxide Sputtering before Metal Deposition                     | 77 |  |  |  |

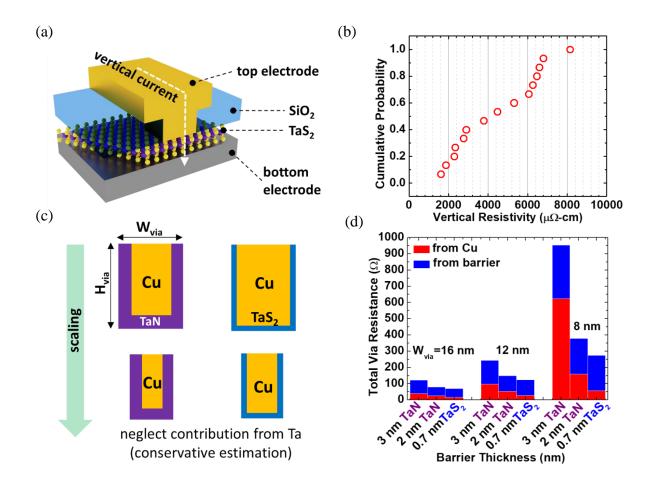

| 5.4                                                              | Int               | rinsic Vertical Conduction of TaS <sub>2</sub>                       | 79 |  |  |  |

| 5.5                                                              | Co                | nclusion                                                             | 81 |  |  |  |

| 6. (                                                             | OTHI              | ER APPLICATIONS AND FUTURE WORKS                                     | 82 |  |  |  |

| 6.1                                                              | Int               | roduction                                                            | 82 |  |  |  |

| 6.2                                                              | RF                | Transmission Line                                                    | 82 |  |  |  |

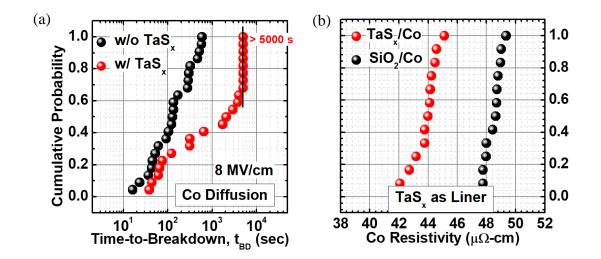

| 6.3                                                              | Co                | balt Interconnects with TaS <sub>x</sub> Barrier/Liner               | 86 |  |  |  |

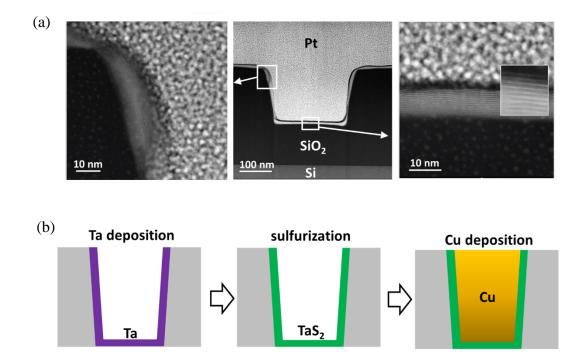

| 6.4                                                              | De                | position of 2D materials in Trench Structure                         | 87 |  |  |  |

| REFERENCES                                                       |                   |                                                                      |    |  |  |  |

| VITA                                                             | VITA              |                                                                      |    |  |  |  |

| PUBLICATIONS                                                     |                   |                                                                      |    |  |  |  |

# LIST OF TABLES

Table 2.1 Material information and lifetime improvement in samples with different barriers..... 39

Table 3.1 Comparison of different works using 2D layered materials as Cu diffusion barriers .. 44

Table 4.1 Summary of liner properties of various 2D layered materials in different aspects. The 2D materials used for the adhesion test are all CVD-grown since a large area is needed for the test. 60

# LIST OF FIGURES

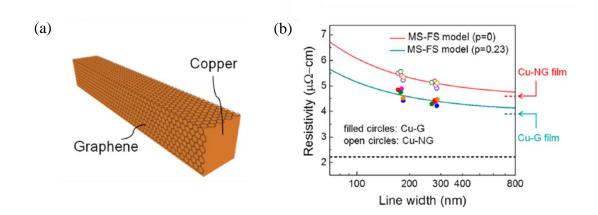

Fig. 1.6 (a) Cu nanowire encapsulated by graphene. (b) With the encapsulation of graphene, the resistivity of Cu nanowires decreases due to the suppression of surface scattering. Reprinted with permission from Mehta *et al.* Nano Lett. **15** (2015) Copyright @ 2015 American Chemical Society.

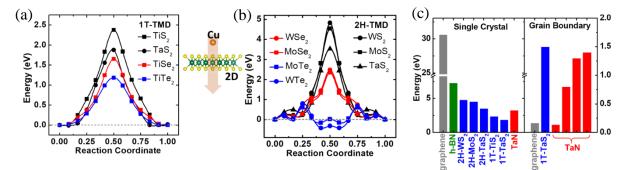

Fig. 2.1 (a) DFT-calculated barrier energy for Cu diffusion across various single-layer, perfect crystals of (a) 1T and (b) 2H TMDs. (c) Summary of barrier energies of various single crystal

materials and materials with grain boundaries, both from this work (h-BN and materials in (a) and (b)) and literature (graphene, grain boundary diffusion of 1T-TaS<sub>2</sub>, and TaN). It can be clearly observed that the energies for diffusion across single crystals are much higher than those across grain boundaries. Some 2D materials show comparable or superior performance than TaN...... 31

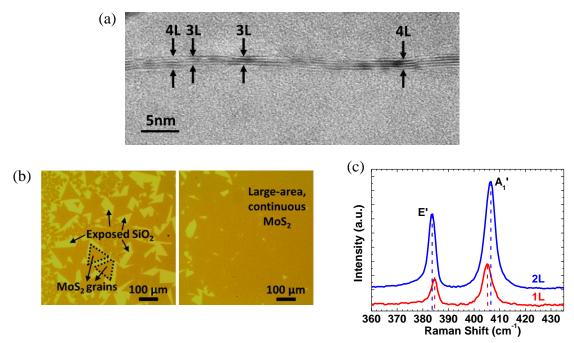

Fig. 2.2 (a) STEM cross-sectional image of transferred h-BN. (b) Optical images of directly-grown CVD MoS<sub>2</sub> films on SiO<sub>2</sub>. Large MoS<sub>2</sub> grains are triangular shapes. The film consists of mostly 1L MoS<sub>2</sub> with some 2L regions. The empty areas are exposed SiO<sub>2</sub>. (c) Raman spectra of MoS<sub>2</sub> on 30 nm SiO<sub>2</sub> on Si substrate. Characteristic peaks of 1L and 2L MoS<sub>2</sub> can both be identified, with 1L being dominant. The wavelength of the laser used for Raman measurements was 532 nm. All measurements on both h-BN and MoS<sub>2</sub> were conducted in regions with large-area (> 1 cm<sup>2</sup>), continuous film coverage.

Fig. 2.4 (a) Current evolution with time for multiple devices with and without h-BN under the stress condition of 7 MV/cm. Devices without barriers break down earlier in general. (b) TDDB results at various E-fields for devices with and without the h-BN barrier. Time-to-breakdown ( $t_{BD}$ ) of the h-BN devices is significantly increased. (c) Lifetime predictions based on three analytical models. With the presence of h-BN, device lifetime at low fields can be enhanced from  $10^5$  s to  $7.5 \times 10^6$  s, based on the E-model.

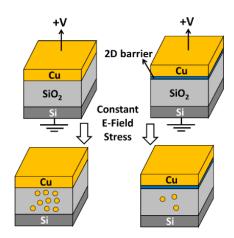

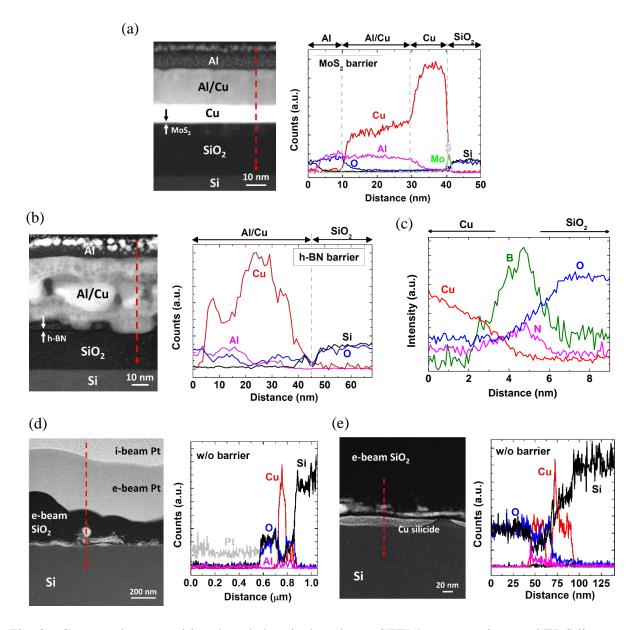

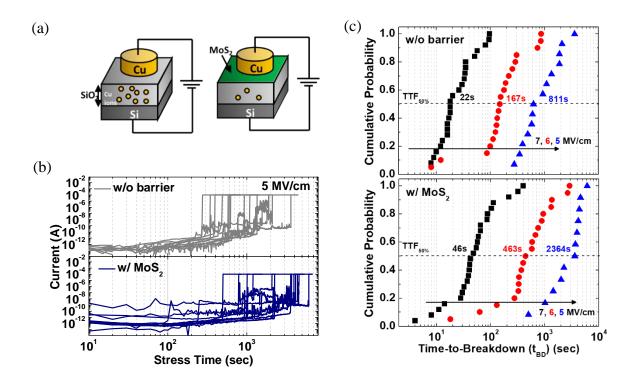

Fig. 3.2 (a) Capacitor structures used for TDDB measurements to evaluate Cu diffusion. If  $MoS_2$  barrier can mitigate Cu ion diffusion, time-to-breakdown (t<sub>BD</sub>) will increase due to the suppression of Cu induced breakdown (b) Current evolution with stress time of devices with and without a barrier at 5MV/cm. (c) Cumulative distribution of t<sub>BD</sub> under various electric field stress for devices with and without MoS<sub>2</sub> barrier. From (b) and (c), it is observed that t<sub>BD</sub> increases in general with the presence of MoS<sub>2</sub> barrier. 47

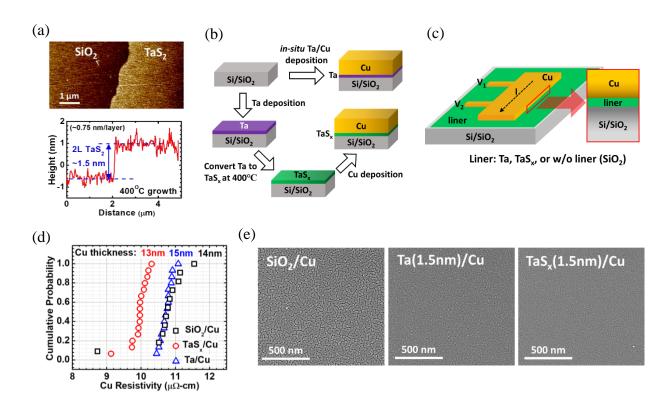

Fig. 4.2 Device structures and tests of liner properties of 400 °C TaS<sub>x</sub>. (a) AFM profile of 1.5 nm TaS<sub>x</sub> grown at 400 °C. This film is used for all the liner and barrier tests. (b) Sample fabrication procedure. Ta/Cu stack is deposited *in-situ*, while TaS<sub>x</sub> has been exposed to air before Cu deposition. An *in-situ* Cu deposition on TaS<sub>x</sub> could bring an even better performance. (c) Cu thin film patterned into Kelvin structure for resistance measurements. Ultra-thin Cu (~15 nm) film is adopted to enhance the contribution of the interface. (d) Cu resistivity on various surfaces. In general, thinner

Cu is expected to have a higher resistivity. Nevertheless, the thinnest Cu (13 nm) on TaS<sub>x</sub> has the lowest resistivity, indicating suppression of surface scattering at the TaS<sub>x</sub>/Cu interface. (e) Wetting properties of Cu tested by depositing ultra-thin Cu (~10 nm) on different surfaces. Numbers of cracks can be observed when Cu is on SiO<sub>2</sub>, while Cu on 1.5 nm Ta and on 1.5 nm TaS<sub>x</sub> have smooth morphologies. The results show that TaS<sub>x</sub> can provide a good wettibility as Ta does for Cu

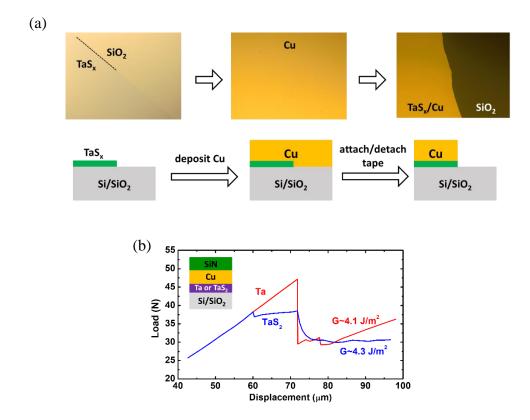

Fig. 4.3 (a) Adhesion tests using the tape method. ~80 nm Cu is deposited on both  $TaS_x$  and  $SiO_2$ regions. After detaching the tape, only Cu on  $TaS_x$  region remains, indicating that  $TaS_x$  is a good liner for Cu to survive CMP processes. (b) Adhesion tests using industrial-standard four-point bending method. The test structure is depicted in the inset.  $TaS_x$  has a slightly higher adhesion

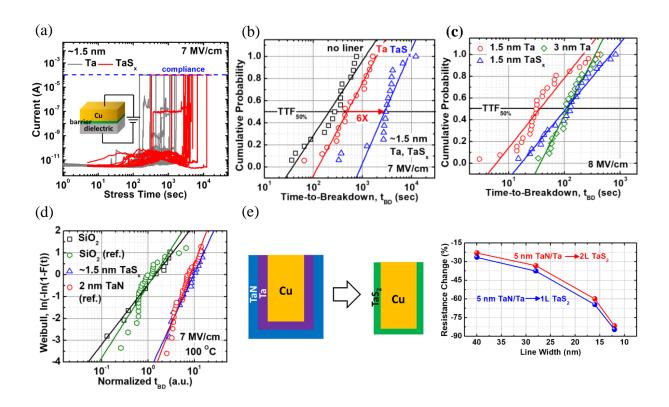

Fig. 4.4 (a) Current versus stress time of devices with Ta and TaS<sub>x</sub>. Devices with TaS<sub>x</sub> have longer lifetime in general. (b) Statistical distribution of devices with Ta and TaS<sub>x</sub> barriers. By converting Ta to TaS<sub>x</sub>, medium-time-to-failure (TTF<sub>50%</sub>) increases by 6 times. (c) 1.5 nm TaS<sub>x</sub> has similar diffusion barrier properties as a 3nm Ta. Since Ta also plays a (minor) role in blocking Cu diffusion, this result indicates the Ta liner thickness can be reduced by using a thinner TaS<sub>x</sub> and Cu volume can be increased. (d) Benchmarking diffusion barrier properties of ~1.5-nm TaS<sub>x</sub> against 2-nm TaN. Two materials have a comparable diffusion barrier property. Improvement of TaS<sub>x</sub> qualify can further reduce the required thickness. (e) Resistance reduction at various line widths with the thinner barrier/liner layer by using TaSx. The improvement in narrower interconnect is more significant. A method to have a single-layer/high-quality  $TaS_x$  can lower the resistance much more tremendously.

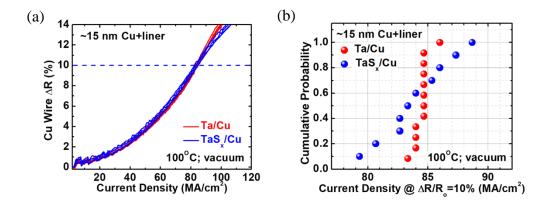

Fig. 4.5 (a) Resistance increase with the stress current density. Current density that reaches 10% of resistance change is defined as the  $J_{\text{max}}$ . (b) Distribution of  $J_{\text{max}}$  of Ta/Cu and TaS<sub>x</sub>/Cu. Two liners have the similar effect on  $J_{max}$ , while TaS<sub>x</sub> results in a larger variation. Improvement of TaS<sub>x</sub>

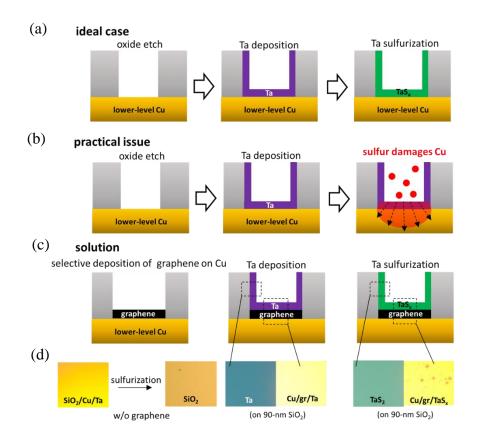

Fig. 4.6 (a) Ideal process flow to synthesize  $TaS_x$  in the trench. (b) Practical issue encountered during the sulfurization. The sulfur species can corrode the lower-level Cu from the bottom of via. This issue could also happen during the growth for other types of TMD. (c) Proposed solution adopting a selective-deposited corrosion barrier on Cu. Both SAM and graphene can be used. Graphene is adopted here. (d) (left) Optical image showing Cu can be completely etched away after the sulfurization process if no corrosion barrier is utilized. (middle) Optical image of the sample used to test the feasibility of graphene as the corrosion barrier. In one region, Ta is deposited on SiO<sub>2</sub>; whereas graphene is selectively deposited on Cu followed by the same Ta deposition in the other region. (right) After the sulfurization, most Cu remains thanks to the

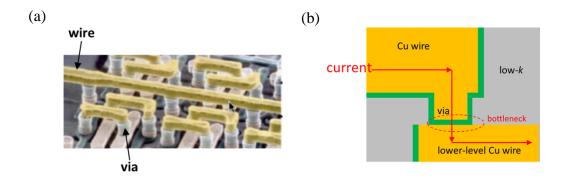

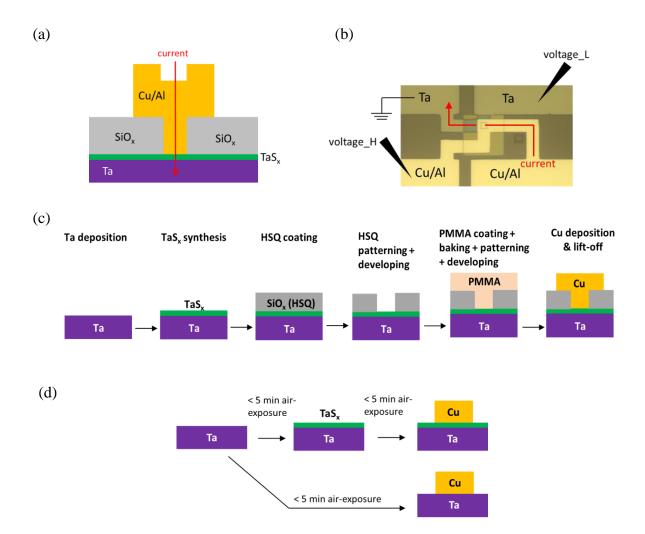

Fig. 5.1 (a) SEM image of an interconnect structure. Cu wires and vias can be observed. (source: Synopsis) (b) Schematic of the cross-section of an interconnect structure with two levels of Cu wires and a via connecting the wires. The direction of current flow is indicated. The conduction Fig. 5.2 (a) Schematic of the cross-section and (b) optical microscope image of the top view of the vertical Kelvin structure. Current flow from one of the top electrodes through  $TaS_x$  area defined by the  $SiO_x$  isolation, to one of the bottom electrodes. Voltage difference between the other top and bottom electrodes is measured. By separately measuring the current and voltage difference, accurate resistance can be obtained. (c) Process flow of the vertical Kelvin structure. Lithography is used for metal patterning. Multiple steps involving air exposure is unavoidable. (d) Modified test structure with a process flow that greatly reduces the duration of air exposure. Shadow masks are used for metal patterning.

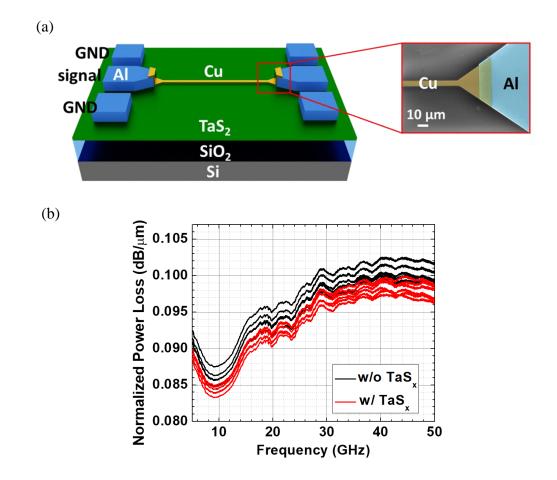

Fig. 6.1 (a) Device structure for RF transmission line measurements. Thicker Al is first deposited as the electrodes. Thin (to enlarge surface/interface scattering) Cu transmission line is then

## ABSTRACT

Copper (Cu) has been used as the main conductor in interconnects due to its low resistivity. However, because of its high diffusivity, diffusion barriers/liners (tantalum nitride/tantalum; TaN/Ta) must be incorporated to surround Cu wires. Otherwise, Cu ions/atoms will drift/diffuse through the inter-metal dielectric (IMD) that separates two distinct interconnects, resulting in circuit shorting and chip failures. The scaling limit of conventional Cu diffusion barriers/liners has become the bottleneck for interconnect technology, which in turn limits the IC performance. The interconnect half-pitch size will reach ~20 nm in the coming sub-5 nm technology nodes. Meanwhile, the TaN/Ta (barrier/liner) bilayer stack has to be > 4 nm to ensure acceptable liner and diffusion barrier properties. Since TaN/Ta occupy a significant portion of the interconnect cross-section and they are much more resistive than Cu, the effective conductance of an ultrascaled interconnect will be compromised by the thick bilayer. Therefore, two dimensional (2D) layered materials have been explored as diffusion barrier alternatives owing to their atomically thin body thicknesses. However, many of the proposed 2D barriers are prepared at too high temperatures to be compatible with the back-end-of-line (BEOL) technology. In addition, as important as the diffusion barrier properties, the liner properties of 2D materials must be evaluated, which has not yet been pursued.

The objective of the thesis is to develop a 2D barrier/liner that overcomes the issues mentioned. Therefore, we first visit various 2D layered materials to understand their fundamental capability as barrier candidates through theoretical calculations. Among the candidates, hexagonal-boronnitride (h-BN) and molybdenum disulfide (MoS<sub>2</sub>) are selected for experimental studies. In addition to studying their fundamental properties to know their potential, we have also developed techniques that can realize low-temperature-grown 2D layered materials. Metal-organic chemical vapor deposition (MOCVD) is adopted for the synthesis of BEOL-compatible MoS<sub>2</sub>. The electrical test results demonstrate the promises of integrating 2D layered materials to the state-of-the-art interconnect technology. Furthermore, by considering not only diffusion barrier properties but also liner properties, we develop another 2D layered material, tantalum sulfide (TaS<sub>x</sub>), using plasmaenhanced chemical vapor deposition (PECVD). The  $TaS_x$  is promising in both barrier and liner aspects and is BEOL-compatible. Therefore, we believed that the conventional TaN/Ta bilayer stack can be replaced with an ultra-thin  $TaS_x$  layer to maximize the Cu volume for ultra-scaled interconnects and improve the performance. Furthermore, Since via resistance has become the bottleneck for overall interconnect performance, we study the vertical conduction of  $TaS_x$ . Both the intrinsic and extrinsic properties of this material are investigated and engineering approaches to improve the vertical conduction are also tested. Finally, we explore the possibilities of benefiting from 2D materials in other applications and propose directions for future studies.

## **1. INRODUCTION**

#### 1.1 State-of-the-art Cu Interconnect Technology and its Challenges

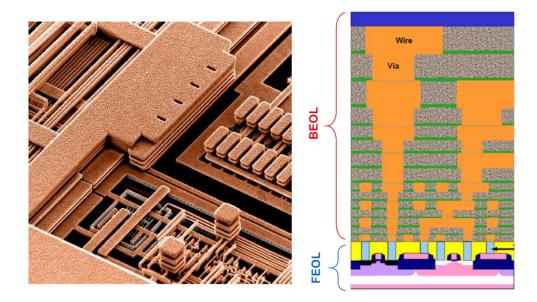

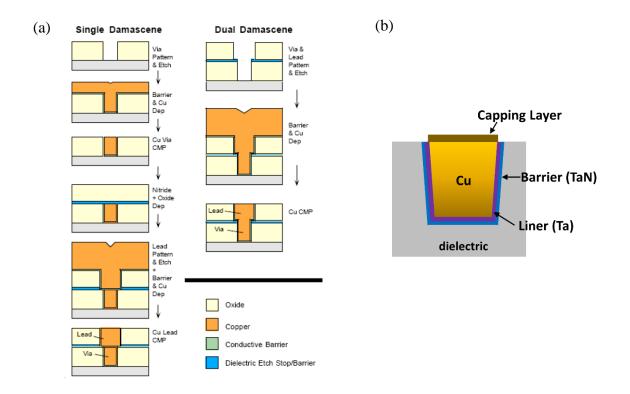

Ever since the inventions of transistors and integrated circuits (ICs), the computational capability has been escalating in a remarkable way, which tremendously changes human beings' lives. This is attributed the well-known Moores' Law, which predicts the number of transistors doubles approximately every eighteen months. Originally, the success of keeping the growth rate was realized by continuing scaling down transistors' dimensions. However, the increased challenges of transistor scaling as well as the scaling of other parts of an IC have slowed down the growth rate. In an IC chip, the regions consisting of transistors is also known as the front-end-of-line (FEOL). However, different transistors must be connected to each other to perform certain computational functions. The connecting bridges between transistors are called "interconnects." Interconnects are metal wires with various lengths, widths, and thicknesses, depending on the vertical levels they are located in an IC chip. Copper (Cu) has been the material of choice for interconnects in today's IC chips for more than 20 years. Before the integration scheme for Cu interconnects was available, aluminum (Al) was the main conductor for interconnects. However, with increasing demands of lower resistivity and better electromigration endurance, Al was eventually replaced with Cu in late 1990s, after many challenges of integration had been overcome. The regions consisting of interconnects is known as the back-end-of-line (BEOL). The top-view and cross-section of an IC chip are shown in Fig. 1.1. It clearly shows that transistors are in the very bottom level while there are many levels of interconnects above transistors. It can also be observed that these interconnects are buried in trenches surrounded by dielectrics, which is also known as the "Damascene Structure". The standard Damascene process is depicted in Fig. 1.2(a), which begins with the formation of trenches by etching the inter-metal dielectrics (IMDs). Next, barrier/liner (TaN/Ta) layers are deposited in these trenches followed by the deposition of a thin copper seeding layer. With the assistance of the seeding layer, the trenches are then filled with copper through electroplating. Finally, chemical mechanical polishing (CMP) is used to remove the excess Cu from the top of the trenches. The cross-section of a single interconnect is illustrated in Fig. 1.2(b). On the top of Cu, a capping layer (typically,  $SiN_x$ , Co, CoWP, etc.) is deposited to alleviate the damages from the CMP process. The purpose of barrier and liner layers will be

Fig. 1.1 (left) Scanning electron microscope (SEM) image of the multi-level Cu interconnects fabricated using the damascene process (courtesy: IBM Corp.). (right) Cross section of an IC chip, where multiple layers of interconnects can be observed on top of the transistor level [1] (courtesy: International Technology Roadmap for Semiconductors, ITRS).

introduced in the following paragraph. Note: although Cu electroplating is considered in the thesis, the current technology is using "Cu reflow" as the new approach for Cu formation [2].

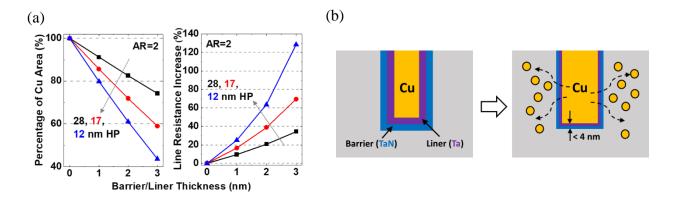

Although transistor scaling contributed to the continued scaling of an IC chip, the scaling of interconnects has become the bottleneck in recent years. Because of the high diffusivity of Cu, diffusion barriers must be incorporated to surround Cu wires. Otherwise, Cu ions/atoms will drift/diffuse through the IMDs that separates two distinct interconnects, resulting in circuit shorting. Conventionally, tantalum nitride (TaN) has been adopted as the diffusion barrier owing to its superior capability of blocking Cu diffusion [3], [4]. However, the adhesion of Cu to TaN is not ideal. To address this issue, tantalum (Ta) has been integrated in-between TaN and Cu to improve the adhesion. The optimized stack consists of a TaN layer deposited on low-*k* dielectrics, followed by a Ta layer before the Cu deposition, as depicted in Fig. 1.2(b). The barrier/liner (TaN/Ta) bilayer has been demonstrated to fulfill several requirements of the interconnect technology [3]. With the advent of sub-5 nm technology nodes, the interconnect half-pitch size will reach ~20 nm and below [1]. Meanwhile, the thickness of the conventional TaN/Ta bilayer cannot be reduced below ~4 nm just to maintain its capability of blocking Cu diffusion into the IMDs [5]. However, the TaN/Ta bilayer is much more resistive than Cu. In ultra-scaled Cu interconnects, TaN/Ta will occupy a large

portion of the cross-section area, which tremendously increases the line resistance, as shown in Fig. 1.3. The main challenge of scaling conventional TaN/Ta lies in their three-dimensional (3D) nature, which makes atomically thin and continuous TaN/Ta stack difficult to achieved fundamentally. Throughout this dissertation, I will discuss how 2D layered material can overcome this bottleneck.

Fig. 1.2 (a) Process flows of the formation of the Damascene Structure. (b) Schematic of the crosssection of a Cu interconnect. A resistive barrier/liner bilayer surrounds Cu and occupies a certain portion of the interconnect.

Fig. 1.3 (a) Percentage of Cu area (left) and increase in line resistance (right) in a single interconnect Damascene trench with various barrier/liner thicknesses and half-pitch (HP) sizes. Aspect ratio (AR) of the trench is fixed at 2. Line resistance drastically increases in extremely scaled interconnects with thicker barrier/liner. (b) Schematic of severe Cu diffusion as the thickness of a conventional TaN/Ta diffusion barrier/liner is scaled.

#### **1.2 Introduction to Two-dimensional Layered Materials**

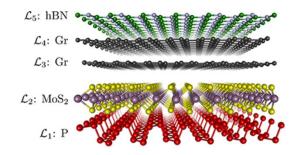

Two-dimensional (2D) layered materials, such as graphene [6], hexagonal-boron nitride (h-BN) [7] and transition metal dichalcogenides (TMDs) [8], [9], possess atomically thin body thicknesses. A few examples of these materials are shown in Fig. 1.4, even though tens of 2D materials have been discovered. The underlying reason that these materials can achieve the thicknesses is the van der Waals force interaction between layers. Unlike three-dimensional (3D) materials, where different atoms are normally bonded by covalence or ionic bonds, the van der Waals force interaction between 2D layers makes it possible and easier to separate layers from each other. The original interest of this atomically thin layer arose from the demand of a superior gate electrostatic control for extremely scaled transistors. A great number of achievements of decent transistor characteristics using 2D materials as the channel materials have been demonstrated over the past few years [10], [11]. To demonstrate field-effect transistors (FETs) with high performance, the 2D layers are normally exfoliated from chemical vapor transport (CVT) prepared bulks to ensure highest possible film quality. The sizes of these 2D "flakes" are normally in micrometer scale.

In addition to the applications for FETs, the 2D nature of these materials inspires people of using them as Cu diffusion barriers to solve the obstacle mentioned in the previous section. Early demonstrations of using graphene as Cu diffusion barrier demonstrates the materials' potential [12]–[14]. However, to evaluate the feasibility of integrating these novel 2D layered materials with the existing Cu interconnect technology, a wide variety of aspects needed to be evaluated, which is the focus of this dissertation.

Fig. 1.4 Examples of 2D layered materials. The van der Waals force interaction between layers makes it possible to separate layers from each other and realize atomically thin films. Reprinted with permission from Cancès *et al.* J. Math. Phys. **58** (2017) Copyright @ 2017 American institute of Physics.

#### 1.3 Motivation of Integrating 2D Layered Materials with Cu Interconnects

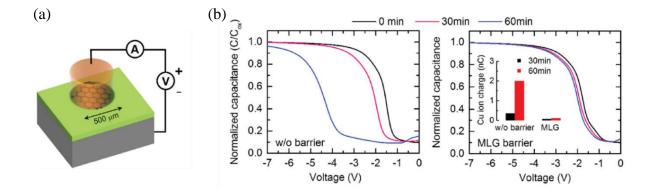

As pointed out in Section 1.1, the fundamental obstacles of using conventional barrier/liner lie in their 3D nature. Given their atomically thin nature, it is intuitive to consider 2D layered materials as diffusion barrier alternatives. Our early work has demonstrated that graphene has a superior capability of blocking Cu diffusion despite its atomic thickness [15]. Figure 1.5(a) illustrates the test structure and method, where a constant electric field is applied across the capacitor structure to drive Cu ions into the dielectric. The presence of positively charged Cu ions results in a flatband voltage ( $V_{FB}$ ) shift that can be observed in a capacitance-voltage (C-V) measurement, as shown in Fig. 1.5(b). It is observed that with graphene being inserted in-between Cu and the dielectric,  $V_{FB}$  shift can be largely suppressed, indicating graphene blocks Cu diffusion. In addition, by encapsulating Cu with graphene, it has been shown that the electrical and thermal conductivity of Cu are enhanced due to suppression of the surface scattering between Cu and the barrier/liner [16], as the resulted briefly summarized in Fig. 1.6.

Fig. 1.5 (a) Metal-oxide-semiconductor (MOS) capacitor structures used for Cu diffusion tests. Graphene is inserted in-between Cu and SiO<sub>2</sub> for the devices with barrier while the control devices have no graphene. (b) After the electrical stressing, devices without graphene show obvious flatband voltage ( $V_{FB}$ ) shift, indicating significant Cu diffusion. Devices with graphene barrier show negligible  $V_{FB}$  shift due to suppression of Cu diffusion. Reprinted with permission from Mehta *et al.* Nanoscale **9** (2017) Copyright @ 2017 Royal Society of Chemistry.

Fig. 1.6 (a) Cu nanowire encapsulated by graphene. (b) With the encapsulation of graphene, the resistivity of Cu nanowires decreases due to the suppression of surface scattering. Reprinted with permission from Mehta *et al.* Nano Lett. **15** (2015) Copyright @ 2015 American Chemical Society.

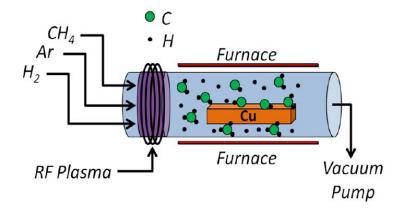

Fig. 1.7 Schematic of the plasma-enhanced chemical vapor deposition (PECVD) system for graphene growth. Cu substrate is illustrated here only as an example. Growth on other substrates is also possible. Reprinted with permission from Mehta *et al.* Nano Lett. **15** (2015) Copyright @ 2015 American Chemical Society.

Despite the abovementioned advantages of graphene, in the meantime, a group of 2D layered materials exists, whose properties are complementary yet distinct from those of graphene. Theoretical calculations predict high-energy barriers in some of these materials to prevent molecule diffusion [17], [18]. Inspired by the graphene works, in this dissertation, the discussions will focus on diffusion barrier properties as well as other properties of different 2D layered materials. In addition, the syntheses of BEOL-compatible 2D materials is also one of the main focuses in this thesis. Our previous work has demonstrated that low-temperature grown graphene can be realized by utilizing the energy of plasma since plasma can dissociate carbon bonds so that high temperatures are not required to provide thermal energy [19]. The plasma-enhanced chemical vapor deposition (PECVD) system is depicted in Fig. 1.7. Similar approaches are adopted for the low-temperature syntheses of other 2D materials. In short, this thesis covers aspects of material synthesis, material/electrical characterizations, and various techniques of evaluating 2D materials' properties, such as diffusion barrier and liner properties.

#### **1.4** Synopsis of the Thesis

The description of my work starts from Chapter 2, where the intrinsic diffusion barrier properties of 2D layered material other than graphene are evaluated. First principle density functional theory (DFT) calculations are utilized to estimate the potential of various 2D layered materials. The results demonstrate promising diffusion barrier properties of many of the candidates. The materials selected for experimental studies include hexagonal-boron-nitride (h-BN) and molybdenum disulfide (MoS<sub>2</sub>). Intrinsic diffusion barrier properties of these films are investigated by conducting the standard reliability test vehicle, time-dependent dielectric breakdown (TDDB) measurements on high-quality films. The results show superior diffusion barrier properties of these two materials. Moreover, STEM (scanning transmission electron microscopy) in conjunction with EDS (energy dispersive X-ray spectroscopy) and EELS (electron energy loss spectroscopy) are used for structural analysis and compositional/chemical mapping of the interface and inter-diffusion processes. This work was carried out in collaboration with Prof. Strachan and his group at Purdue University, Prof. Eric Pop and his group at Stanford University, and Prof. Moon Kim and his group at the University of Texas at Dallas.

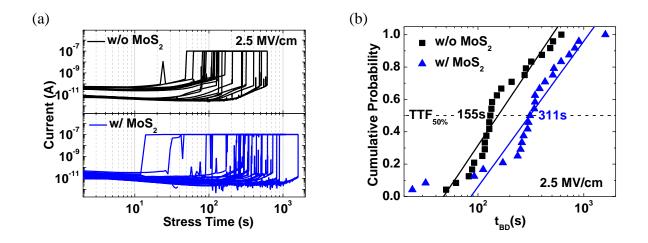

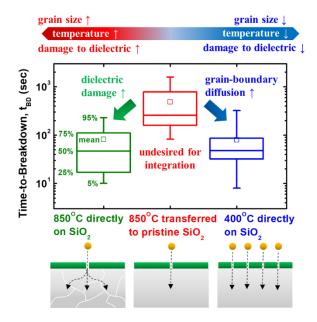

Next, in Chapter 3, MoS<sub>2</sub> barrier grown at low temperature (400 °C) compatible to the technology is demonstrated. Unlike Chapter 2, where the fundamental properties of 2D are studied using highest-possible-quality films grown at high temperatures, this chapter focuses on realizing a BEOL-compatible 2D barrier. The growth method, material characterizations, and barrier property tests are discussed. In addition, this low-temperature grown MoS<sub>2</sub> is compared with the high-temperature grown one in Chapter 2 for their diffusion barrier properties. This work was carried out in collaboration with Prof. Joshua Robinson and his group at Pennsylvania State University, as well as Dr. Ryan Scott Smith and Ketan Shah at Globalfoundries.

In Chapter 4, another 2D layered material, tantalum sulfide  $(TaS_x)$  is discussed. The reason of choosing  $TaS_x$  is not only because of its superior diffusion barrier property, but also of its liner properties, which are not discussed in previous chapters. In fact, none of the works using 2D layered materials for Cu interconnects have study the liner properties, which are essential to the technology integration. This chapter first introduces the low-temperature growth of  $TaS_x$  by our PECVD system. The material characterizations are also systematically conducted. Finally, electrical and other tests show the superior barrier and liner properties of this material. This work was carried out in collaboration with Prof. Moon Kim and Prof. Robert Wallace and their groups at the University of Texas at Dallas. It was also in collaboration with Dr. Kevin L. Lin, Dr. Carl H. Naylor, and Dr. Han Li at Intel Corporation.

In Chapter 5, vertical conduction of 2D layered materials is studied since it is directly related to "via resistance", which has become a bottleneck of interconnect performance. Due to the several advantages of  $TaS_x$  demonstrated in Chapter 4, the material is chosen for the analyses. We first confirm the existence of oxides on  $TaS_x$  and their serious impacts on vertical conduction. Then, we develop two approaches in the hope to avoid the oxides from being formed at the interface of metal and 2D barrier/liner. Finally, the intrinsic vertical conduction across high-quality  $TaS_2$  is assessed, and a projection of its advantage in ultra-scaled interconnects is performed. This work was carried out partially in collaboration with Dr. Dimitry Zemlyanov at Purdue University.

Finally, Chapter 6 describes other possible applications that could benefit from 2D materials. One of them is the application in radio-frequency (RF) transmission lines. The reduction of the surface

scattering (hence the resistivity) at Cu/2D interface discussed in Chapter 4 could indicate the possibility of reducing the power loss in RF transmission lines. We show that  $TaS_x$  can lower RF power loss in transmission lines. The work was carried out in collaboration with Prof. Dana Weinstein and her group at Purdue University. In addition,  $TaS_x$  is further integrated with cobalt (Co) interconnects. The results show that Co diffusion is suppressed and Co resistivity is reduced with  $TaS_x$  being used as the barrier/liner. Finally, directions for future development is suggested.

# 2. TWO-DIMENSIONAL LAYERED MATERIALS BEYOND GRAPHENE AS CU DIFFUSION BARRIERS

Most of the material in this chapter has been reprinted with permission from "C.-L. Lo, M. Catalano, K. K. H. Smithe, L. Wang, S. Zhang, E. Pop, M. J. Kim, and Z. Chen; npj 2D Materials and Applications, vol. 1, no. 42, 2017". Copyright @ 2017, Springer Nature, "C.-L. Lo, K. K. H. Smithe, R. Mehta, S. Chugh, E. Pop, and Z. Chen; IEEE Intl. Reliability Physics Symp. (IRPS), 2017". Copyright @ 2017, IEEE, and "C.-L. Lo, B. A. Helfrecht, Y. He, D. M. Guzman, N. Onofrio, S. Zhang, D. Weinstein, A. Strachan, and Z. Chen; in Journal of Applied Physics, vol. 120, no. 8, 2020". Copyright @ 2020, American Institute of Physics.

#### 2.1 Introduction

Although graphene has been demonstrated to have superior capability of blocking Cu diffusion despite its atomic thickness, in the meantime, a group of other two-dimensional (2D) layered materials exists, whose properties are complementary yet distinct from those of graphene. For instance, hexagonal boron nitride (h-BN) is an atomically thin 2D insulator (band gap ~6 eV) [7] and molybdenum disulfide (MoS<sub>2</sub>) is a 2D semiconductor with a band gap ~2 eV [20]. Theoretical calculations predict high-energy barriers in some of these materials to prevent molecule diffusion [17], [18]. In the development of conventional diffusion barrier materials, various material types including both metals and insulators have been investigated, judged by the interface requirements of different applications [21], [22]. While it is still a rather unexplored field with many unknowns in these 2D materials such as Cu wetting and adhesion, interface scattering, and CMOS compatibility, it is important to evaluate the potential of these atomically thin 2D materials as ultra-thin barriers and make thorough comparisons.

In this chapter, we provide an overview on both theoretical and experimental studies of intrinsic diffusion barrier properties of various 2D materials. First principle density functional theory (DFT) calculations are employed to investigate barrier energies of various 2D materials for Cu diffusion. Although many of the candidates possess potential, we choose h-BN and MoS<sub>2</sub> for experimental analyses since high-quality, large-area, and continuous films of these two materials are available, which is not the case for many of the candidates. Their diffusion barrier properties are investigated by time-dependent dielectric breakdown (TDDB) measurements. We observe that the lifetime of intra- and inter-layer dielectrics can be significantly extended with the presence of the tested 2D

barriers. In addition, using scanning transmission electron microscopy (STEM), energy dispersive X-ray spectroscopy (EDS), and electron energy loss spectroscopy (EELS), we confirm that the examined ultra-thin 2D barriers can efficiently mitigate Cu diffusion and are promising alternative barrier solutions for interconnect technology. For the purpose of studying the fundamental/intrinsic properties, the materials chosen in the chapter are grown at high temperatures to achieve the highest possible quality. Practical considerations of the integrability to the technologies will be discussed in the following two chapters.

### 2.2 Simulation and Experimental Procedures

#### 2.2.1 Density Functional Theory (DFT) Calculations

The geometry optimization minimum potential energy surfaces for Cu diffusion across TMDs were carried out using DFT as implemented in the Vienna ab-initio simulation package (VASP) [23], [24]. Projector-augmented-wave (PAW) potentials [25], [26] were used to account for the electron-ion interactions, and the electron exchange-correlation potential was calculated using the generalized gradient approximation (GGA) within the Perdew-Burke-Ernzerhof (PBE) [27] scheme using real-space projections. Since long-range dispersion interactions are not captured by the GGA functional, we employed Grimme's DFT-D3 energy correction scheme to account for these interactions [28]. In the DFT-D3 scheme, the Kohn-Sham DFT energy is corrected by adding a pairwise term that depends on the local environment of each atom. The kinetic energy cutoff for all calculations was set to 500 eV and, due to the relatively large simulation size, a gamma-centered  $4 \times 4 \times 1$  mesh was used for the k-space sampling. A Gaussian smearing of 0.05 eV and an electronic relaxation tolerance of  $1 \times 10^{-5}$  eV was used for all calculations.

We used the climbing image nudged elastic band (NEB) method as implemented in VASP [29] to determine minimum potential energy surface and diffusion paths between known initial and final geometries with the Cu atom at local minima (on top of a metal atom for the 2H structures and opposite a chalcogen atom for the 1T structures) on either side of a  $4 \times 4$  monolayer TMD with approximately 19-20 Å of vacuum between out-of-plane periodic images. The minima were obtained by structural relaxations using a conjugate gradient (CG) algorithm with a force tolerance of 0.01 eV/Å. The NEB calculations were initialized from a set of geometries interpolating

between initial and final structures; then, the ionic positions of the different geometries are iteratively optimized using only the ionic-force components perpendicular to the hypertangent. The energy along the diffusion path was determined by spline interpolation based on the total energy of the individual geometries.

The NEB structural relaxations were carried out using either the damped molecular dynamics or quasi-Newton algorithms. If the NEB forces could not be converged to 0.01 eV/Å under "normal" precision (the VASP input specification PREC = Normal), the precision was increased (PREC = Accurate). If convergence could still not be achieved, the density of the FFT grid was increased (ADDGRID = True). Only 2H-TaS<sub>2</sub> could not be converged to 0.01 eV/Å and was instead converged to 0.05 eV/Å.

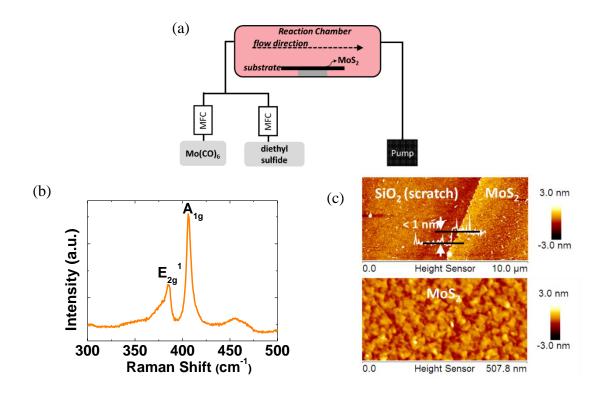

#### 2.2.2 Preparation of 2D Materials

Cu foils with h-BN grown on both sides by CVD at 1000 °C were first coated with polymethyl methacrylate (PMMA) on one side. The side with/without PMMA is identified as the top/bottom side throughout the descriptions. h-BN on the bottom side was completely etched away by Ar plasma. Then, the sample was placed in 1 M iron chloride (FeCl<sub>3</sub>) solution, with the bottom side facing down, to etch away the exposed Cu. After Cu was completely etched, the sample was immersed in DI water for 10 minutes, followed by 1 M HCl solution for 10 minutes, and another 10 minutes in DI water. The PMMA/h-BN film was then picked up with a 20 nm SiO<sub>2</sub> on Si substrate and PMMA was finally dissolved by acetone. The STEM cross-section in Fig. 2.2(a) reveals there may be small thickness variations in our h-BN sample, ranging between 3-4 layers. MoS<sub>2</sub> films were directly grown on 30 nm SiO<sub>2</sub> on Si substrates by CVD at 850 °C. Details of the CVD growth can be found elsewhere [30]. 1L MoS<sub>2</sub> was identified by Raman spectroscopy, with characteristic E' peak at 384.5 cm<sup>-1</sup> and A<sub>1</sub> at 405 cm<sup>-1</sup>, respectively, as shown in Fig. 2.2(c). In addition, although 1L MoS<sub>2</sub> was dominant, characteristic Raman peaks associated with 2L MoS<sub>2</sub> were also found occasionally (~10% coverage). To transfer the MoS<sub>2</sub> film off the growth substrate, the sample was spin-coated with PMMA and immersed in DI water. A diamond scribe was used to create some scratches at the edges, which allows water to penetrate into the interface of the MoS<sub>2</sub> film and the substrate. The PMMA/MoS<sub>2</sub> was then detached from the substrate in DI water and transferred to the target substrate. Finally, PMMA was dissolved by acetone.

Both h-BN and MoS<sub>2</sub> samples have continuous film coverage with areas larger than 1 cm<sup>2</sup>, such that large arrays of devices can be fabricated to perform statistical electrical measurements. We would like to emphasize that, the use of transfer method or high-temperature growth in this chapter is intended to study the fundamental diffusion barrier properties of large-area, high quality 2D layered materials, rather than providing a direct solution to interconnect technologies.

#### 2.2.3 Fabrication of MOS Capacitor Structure

To perform electrical measurements, a metal-oxide-semiconductor (MOS) capacitor structure was fabricated, as depicted in Fig. 2.3. Devices with 2D barrier layers inserted between Cu and SiO<sub>2</sub> were evaluated for the diffusion barrier properties, while devices without any 2D barriers were prepared as control samples. Heavily-doped Si (resistivity  $< 5 \text{ m}\Omega$ -cm) substrates with 20 nm or 30 nm SiO<sub>2</sub> were used for the MOS capacitor sample fabrication. After transferring or growing a 2D film, Cu/Al (~30 nm/20 nm) electrodes with diameters of 100 µm were deposited using e-beam evaporation through a shadow mask, with Cu in contact with the 2D material and Al on top. The sample was then coated with photoresist and placed into 6:1 buffered oxide etch (BOE) to etch away the SiO<sub>2</sub> on the bottom side of the substrate, followed by 50 nm Al deposition to form an ohmic contact to the Si substrate bottom. Finally, the top photoresist was removed by acetone.

Three types of barrier samples were compared: i) One to two layer (1-2L) h-BN grown by chemical vapor deposition (CVD) on a Cu foil was transferred onto a 20 nm SiO<sub>2</sub>/Si substrate twice to form a 3-4L h-BN barrier; ii) Single-layer (1L) MoS<sub>2</sub> with some small two-layer (2L) regions was directly grown on a 30 nm SiO<sub>2</sub>/Si substrate by CVD [30] at 850 °C; iii) 1L MoS<sub>2</sub> from the same CVD growth was transferred to a 20 nm SiO<sub>2</sub>/Si substrate for a direct process comparison that will be discussed. Note that, it will be shown possible in the next chapters to lower the growth temperature to be back-end-of-line (BEOL) compatible, which is not the focus of this chapter. This chapter aims to demonstrate the intrinsic barrier properties of various 2D materials by using high quality films from high temperature growth.

#### 2.2.4 TEM/EDS/EELS Analysis

STEM cross-sectional samples were prepared with a FEI Nova 200 dual-beam FIB/SEM by using the lift-out method. The region of interest above the Al metal pad was protected during the focused

ion beam milling, by depositing SiO<sub>2</sub> and Pt layers on top of the sample. Both high resolution transmission electron microscopy (HREM) images, atomic STEM HAADF and bright field (BF) images were obtained in a JEOL ARM200F microscope equipped with a spherical aberration (Cs) corrector (CEOS GmbH, Heidelberg, Germany) and operated at 200 kV. The corrector was carefully tuned by the Zemlin-tableau method with Cs = 0.5  $\mu$ m and the resolution was demonstrated to be around 1 Å. EDS was performed with an Aztec Energy Advanced Microanalysis System with X-MaxN 100N TLE Windowless 100 mm<sup>2</sup> analytical silicon drift detector. Line scan profiles were obtained by scanning the electron probe perpendicularly to the interface of interest. EELS was also performed by using a Gatan parallel electron energy loss spectrometer with better than 1 eV energy resolution.

#### 2.3 **Results of DFT Calculations**

Although the 2D layered materials used for the experimental studies in this chapter have larger grain sizes, making diffusion through perfect crystal sites dominant, grain boundaries diffusion is also calculated here to provide general insight for many practical situations. Figures 2.1(a) and 2.1(b) show the lowest potential energy surfaces for Cu diffusing across various single-layer, perfect crystals of MX<sub>2</sub> TMDs with M=Mo, W, Ta and X=S, Se, Te. We show results for the two most stable phases 2H (space group P-6m2) and 1T (space group P-3m1). These calculations are performed on defect-free, perfect crystals that are hardly produced in real growth effort. In fact, most 2D materials in literature and those available in the market show rather high defect and impurity densities as well as limited grain sizes. Grain boundaries have been established as the dominant diffusion paths in the case of TaN/Ta [31]–[33], and they can certainly play important roles in the 2D materials of interest [34]. Nevertheless, exploring performance in ideal materials by calculations is essential for comparing intrinsic properties among different materials and identifying diffusion mechanisms. Our DFT results show that sulfides impose the highest barriers to diffusion with a reduction as we move to selenides and tellurides. In fact, quite surprisingly, Cu prefers interstitial sites over surface sites for 2H tellurides [35]. Due to the great interest in TaS<sub>2</sub> for reasons to be addressed in Chapter 4, the material will be discussed in further detail to fully evaluate its potential. Figures 2.1(a) and 2.1(b) show that 2H-TaS<sub>2</sub> is preferable over 1T-TaS<sub>2</sub> because of its higher energy barrier. In addition, 2H-TaS<sub>2</sub> is easier to be produced by lowtemperature syntheses [36]. It is important to compare these new 2D materials with the conventional TaN barrier that has been thoroughly studied both theoretically and experimentally. Although the comparison of calculated energy barriers for 2D materials and experimentally extracted values for TaN is rather crude, it is helpful to gain some initial insights in order to quickly identify promising candidates. Experimental barrier energy extraction of 3.27eV in single crystalline TaN by Wang et al. [31] and the calculated energies for 2D materials are included in the left panel of Fig. 2.1(c). Based on these comparisons, we conclude that graphene, h-BN and some sulfides can be as good as or even better than single crystallin TaN in terms of barrier energy and can be considered for Cu diffusion barrier applications. As mentioned earlier, materials used in practice are normally polycrystalline with grain boundaries. The right panel of Fig. 2.1(c) displays experimental extraction of reduced barrier energy range from 0.14-1.4 eV in TaN due to diffusion through grain boundaries [32], [37], [38]. The barrier energy for 1T-TaS<sub>2</sub> is calculated to be 1.5 eV [39], higher than that of TaN. It would be interesting to have the same to be calculated for 2H-TaS<sub>2</sub> as well. Surprisingly, the value for graphene obtained from the same work by Zhao et al. [34] reduced significantly. It is worth pointing out that even though 2D materials are not obviously superior than TaN in terms of grain boundary diffusion, it is theoretically possible to realize a single atomic layer of a 2D material with very large grain size. On the contrary, due to the 3D nature of TaN, achieving the same type of TaN film is not possible.

Fig. 2.1 (a) DFT-calculated barrier energy for Cu diffusion across various single-layer, perfect crystals of (a) 1T and (b) 2H TMDs. (c) Summary of barrier energies of various single crystal materials and materials with grain boundaries, both from this work (h-BN and materials in (a) and (b)) and literature (graphene, grain boundary diffusion of 1T-TaS<sub>2</sub>, and TaN). It can be clearly observed that the energies for diffusion across single crystals are much higher than those across grain boundaries. Some 2D materials show comparable or superior performance than TaN.

## 2.4 TDDB Measurements and Lifetime Prediction

Although DFT calculations in the previous section provide prediction of the potential of various 2D materials as the diffusion barrier, experimental verification can only be conducted on largearea and continuous films, which is not available for many 2D materials yet. Therefore, in this section, we choose h-BN and MoS<sub>2</sub> for experimental analyses since films that meet the requirement are available. To rule out the variations generated by defects and grain boundaries in CVD-grown 2D films, or other imperfections from the not-yet-optimized CVD recipes, TDDB was adopted to evaluate the diffusion barrier properties of these 2D materials since it provides a statistical approach for a fair analysis. In addition, TDDB has been widely accepted as a test vehicle for assessment of Cu interconnect reliability [40]–[47]. Hundreds of devices (diameter=100 µm; spacing between two devices  $\sim 350 \ \mu\text{m}$ ) were fabricated across large-area, continuous films for statistical assessments. In our TDDB setup, a positive constant electric field (E-field) was applied at room temperature to the top Cu electrode of the device-under-test, with the bottom p<sup>++</sup> Si being grounded, as shown in Fig. 2.3. If the positive E-field drives Cu ions into SiO<sub>2</sub>, these ions can accumulate and form a conductive path in the dielectric and/or assist in Poole-Frenkel tunneling [43], which leads to device breakdown. Time-to-breakdown (tBD) of each device was recorded when the device broke down and the leakage current density reached  $1.3 \times 10^{-2} \,\mu A/\mu m^2$  (equivalent to 100 µA from a circular metal pad with 100 µm diameter). Once t<sub>BD</sub> of more than 10 devices (more than 15 in most cases) was obtained, an evaluation of the dielectric quality that takes the variability into account was finally achieved. If significant Cu diffusion is present, t<sub>BD</sub> will be reduced due to Cu-induced breakdown, as illustrated in the left part of Fig. 2.3. If a 2D barrier can mitigate the Cu ion diffusion, tBD is expected to be extended due to the lower probability of conduction path formation, which is depicted in the right part of Fig. 2.3. We would like to further emphasize that, the capacitor structure used here facilitates the study on intrinsic material properties [41], compared to the conventional inter-digitated electrode structures [43], [45], whose breakdown mechanisms are often affected by chemical-mechanical polishing (CMP) processes. Furthermore, the large area of the capacitor provides a fair imitation of real interconnects considering the large diffusion area due to the extended wire length.

Fig. 2.4(a) shows the current evolution with time for devices with and without h-BN under a stress of 7 MV/cm. We observe that devices without h-BN barriers reached breakdown earlier in general.

Fig. 2.2 (a) STEM cross-sectional image of transferred h-BN. (b) Optical images of directly-grown CVD MoS<sub>2</sub> films on SiO<sub>2</sub>. Large MoS<sub>2</sub> grains are triangular shapes. The film consists of mostly 1L MoS<sub>2</sub> with some 2L regions. The empty areas are exposed SiO<sub>2</sub>. (c) Raman spectra of MoS<sub>2</sub> on 30 nm SiO<sub>2</sub> on Si substrate. Characteristic peaks of 1L and 2L MoS<sub>2</sub> can both be identified, with 1L being dominant. The wavelength of the laser used for Raman measurements was 532 nm. All measurements on both h-BN and MoS<sub>2</sub> were conducted in regions with large-area (> 1 cm<sup>2</sup>), continuous film coverage.

Fig. 2.3 MOS capacitors used for barrier property evaluation. Cu diffusion into SiO<sub>2</sub> with and without 2D barriers in place under constant-electric-field stress is illustrated. Note that an Al layer (not shown) was deposited both above Cu and beneath Si.

Fig. 2.4 (a) Current evolution with time for multiple devices with and without h-BN under the stress condition of 7 MV/cm. Devices without barriers break down earlier in general. (b) TDDB results at various E-fields for devices with and without the h-BN barrier. Time-to-breakdown (t<sub>BD</sub>) of the h-BN devices is significantly increased. (c) Lifetime predictions based on three analytical models. With the presence of h-BN, device lifetime at low fields can be enhanced from  $10^5$  s to  $7.5 \times 10^6$  s, based on the E-model.

Moreover, before the breakdown occurred, the currents of the devices without h-BN were generally higher. Defining the breakdown current at  $1.3 \times 10^{-2} \,\mu\text{A}/\mu\text{m}^2$ , t<sub>BD</sub> of different devices can be obtained from Fig. 2.4(a). TDDB results of devices with and without h-BN at various E-fields of 6, 7, and 8 MV/cm are compared in Fig. 2.4(b). Each data point represents t<sub>BD</sub> of a single device. At a certain E-field, the device with the shortest/longest tBD was assigned to have the lowest/highest value of the cumulative probability. Therefore, the slope of the fitted line for any given E-field is always positive. With the presence of the h-BN barrier, tBD of devices has clearly increased, indicating the suppression of Cu diffusion. The less-steep slope of the 8 MV/cm line of the h-BN devices is attributed to device variations, which occasionally is inevitable for transferred-CVD films. Despite this, the median-time-to-failure (TTF<sub>50%</sub>) defined at probability of 0.5 is still a fair indication of the average device reliability since it was statistically obtained from a large number of devices. The purpose of performing TDDB measurements at various E-fields is to allow extrapolation of the device lifetime under normal operating conditions (much lower E-fields) by fitting with some analytic models [40]–[44]. Otherwise, directly conducting TDDB at low E-fields can be extremely time consuming. Among numerous proposed models, E-model [40], 1/E-model [41], [42], and sqrt-E-model [43], [44] are chosen for low field lifetime predictions, as shown in Fig. 2.4(c). The equations of these models with only the E-field dependent terms shown can be expressed as:

| E-model: $\ln(TTF_{50\%}) \sim -\gamma E$               | (2.1) |

|---------------------------------------------------------|-------|

| 1/E-model: $\ln(TTF_{50\%}) \sim (G/E)$                 | (2.2) |

| sqrt-E-model: $\ln(TTF_{50\%}) \sim -2\beta_S \sqrt{E}$ | (2.3) |

where  $\gamma$ , *G*, and  $\beta$ s are regarded as constants in this study. While various models emphasizing different breakdown mechanisms have been investigated extensively for decades, it is well understood that they can vary significantly with different materials, processes, and structures. Since detailed breakdown mechanisms are not yet explored in these diffusion barrier materials, a lot more research is required to develop sufficient understanding and build models that can eventually provide precise predictions in the future. The models adopted in this study include the most conservative one (E-model) and a relatively optimistic one (1/E-model), based on which qualitative comparisons without detailed mechanism analyses have been accomplished. Our

results demonstrate a general enhancement of dielectric lifetime regardless of the model used. In Fig. 2.4(c), under the normal operating condition, devices with h-BN have ~50 times longer lifetime (from ~ $10^5$  to  $7.5 \times 10^6$  s) than devices without barriers, based on the prediction of the E-model.

We now turn to the MoS<sub>2</sub> barriers. Field dependent TDDB measurement results are plotted in Figs. 2.5(a)-(c). Based on TTF<sub>50%</sub> of the directly-grown MoS<sub>2</sub> (Fig. 2.5(b)) devices and the control samples (Fig. 2.5(a)) at different E-fields, comparison of the lifetime prediction is provided in Fig. 2.5(d). We observe that, with the presence of the MoS<sub>2</sub> barrier, the reliability of the dielectric underneath Cu under normal operating conditions is significantly enhanced, from ~10^5 to 3.7  $\times$  $10^8$  s, showing more than three orders of magnitude improvement in device lifetime. It is worth noting that, despite the longer TTF50% of the devices with transferred h-BN at high E-fields, the predicted lifetime of the devices with directly-grown MoS<sub>2</sub> is superior at low E-fields. This discrepancy can be attributed to SiO<sub>2</sub> quality degradation due to thermal stress during the CVD growth, which is confirmed in Fig. 2.5(e). The sulfur-thermal annealed SiO<sub>2</sub>/Si sample (labeled as "after 850 °C growth") went through the same CVD process but intentionally received no MoS2 growth. During the CVD growth, the high-temperature facilitated decomposition of SiO<sub>2</sub> and/or thermal stress-induced diffusion of precursor residues into SiO<sub>2</sub> can generate defects in the dielectric [48]–[50]. As a result, the sulfur-thermal annealed SiO<sub>2</sub>/Si sample has lower t<sub>BD</sub> and higher leakage current before the breakdown. This can be minimized once the growth recipe is optimized. It is acknowledged that low temperature growth processes need to be developed to meet the BEOL requirements and prevent thermal damage to the dielectrics. Interestingly, at low Efields, the extrapolated lifetime of both SiO<sub>2</sub>/Si control substrates are very similar, as shown by the black curves in Fig. 2.4(c) vs. Fig. 2.5(d). This suggests that the aforementioned CVD-induced SiO<sub>2</sub> defects do not contribute much to the reduction of TTF<sub>50%</sub> at low E-fields. In contrast, TTF<sub>50%</sub> degrades more at high E-fields when the energy barrier for Cu ions to overcome to transport through these defect states is lowered by the E-fields. Therefore, at low E-fields, the lifetime of devices with the transferred h-BN and directly-grown MoS<sub>2</sub> can still be compared even though they have gone through different processes. To further verify the proposed mechanism, MoS<sub>2</sub> is removed from its original growth substrate and transferred onto the same 20 nm SiO<sub>2</sub>/Si substrate used for the h-BN samples. As shown in Fig. 2.5(c), TTF<sub>50%</sub> at high E-fields is higher than that of

Fig. 2.5 (a)(b)(c) TDDB results at various E-fields of devices (a) without MoS<sub>2</sub>, (b) with directlygrown MoS<sub>2</sub>, and (c) with transferred MoS<sub>2</sub> as the diffusion barrier. (d) Lifetime prediction of directly-grown MoS<sub>2</sub>, compared to that of the control sample using various models. With the presence of MoS<sub>2</sub>, device lifetime can be enhanced from  $10^5$  s to  $3.7 \times 10^8$  s, based on the E-model. (e) Current evolution with time of multiple devices before and after the thermal stress from the CVD growth. The sulfur-thermal annealed devices (labeled as "after 850 °C growth") went through the same CVD process but intentionally received no MoS<sub>2</sub> growth. These devices had higher leakage currents and shorter breakdown time. (f) Comparison of the predicted lifetime for devices with different 2D barriers and from different preparation processes, based on the E-model. Directlygrown MoS<sub>2</sub> performs the best as a diffusion barrier.

the directly-grown  $MoS_2$  and rather close to the h-BN samples shown in Fig. 2.4(b), which can be attributed to the superior  $SiO_2$  quality. However, when extrapolated to the normal operating conditions, the transferred  $MoS_2$  sample shows worse performance than the directly-grown  $MoS_2$ , as discussed in next paragraph.

The comparison of the device lifetime with different materials and from different processes is shown in Fig. 2.5(f). With the presence of transferred h-BN, transferred MoS<sub>2</sub>, and directly-grown MoS<sub>2</sub>, the device lifetime at low E-fields can be enhanced from ~10<sup>5</sup> s (without barrier) to 7.5  $\times$  $10^6$  s,  $3.1 \times 10^6$ , and  $3.7 \times 10^8$  s, respectively, based on the most conservative expectation from the E-model. The summary of the material information and the lifetime improvement is listed in Table 2.1. Since the grain size of the h-BN and MoS<sub>2</sub> films used in this work is rather similar (~micrometer), we conclude that grain boundary density is not the dominant factor in device lifetime. In fact, we conclude that directly-grown MoS<sub>2</sub> gives the best performance in mitigating Cu ion diffusion. Interestingly, devices with transferred h-BN and transferred MoS<sub>2</sub> show similar E-field dependent behaviors, indicating the lifetime of these devices is limited by the film transfer process instead of individual material properties. Defects, cracks and impurities introduced by the mechanical transfer process limit the barrier quality to a large extent. Although optimization of the transfer methods can certainly bring improvement [51], it will remain challenging to realize largescale transfer of 2D barrier materials with consistent reliability in VLSI technology. We therefore conclude that, directly-grown 2D materials are highly preferred to improve the reliability and device lifetime.

While this chapter focuses on testing diffusion barrier properties of 2D materials, we acknowledge there might be additional advantages and functionalities these materials can bring to the interconnect technology, which will require further investigations. For example, it has been shown that single layer MoS<sub>2</sub> with a body thickness of ~0.7 nm can be rather conductive despite its semiconductor nature [11]. The conventional diffusion barrier, TaNx, generally has a bulk resistivity of a few hundred  $\mu\Omega$ -cm. When being scaled down to 2-3nm, the deposited TaNx layer becomes TaONx in most areas where it is in direct contact with the interlayer dielectric, resulting in a largely increased resistivity (~few thousand  $\mu\Omega$ -cm). In some circumstances where conductive diffusion barriers are requested (e.g. shunting the current through tiny voids in Cu formed in the

| Material                        | Layer number | Thickness     | Lifetime improvement<br>at 0.5 MV/cm (E-model) |

|---------------------------------|--------------|---------------|------------------------------------------------|

| Transferred h-BN                | 3 - 4        | ~1 – 1.3 nm   | ~50×                                           |

| Transferred MoS <sub>2</sub>    | 1 - 2        | ~0.6 – 1.3 nm | ~20×                                           |

| Directly-grown MoS <sub>2</sub> | 1 - 2        | ~0.6 – 1.3 nm | ~1000×                                         |

Table 2.1 Material information and lifetime improvement in samples with different barriers.

early stage of electromigration) [52], MoS<sub>2</sub> can actually outperform ultra-scaled conventional barriers. In addition, phase engineering [53] can also convert semiconducting 2H-phase MoS<sub>2</sub> into metallic 1T-phase MoS<sub>2</sub> to carry out a high conductivity.

Another major concern is that electromigration lifetime generally decreases for every interconnect generation. When interconnect dimensions continue to scale down, the interfacial mass transport becomes the dominant factor responsible for the reduction of the lifetime. In a standard damascene structure, the bottom and sides of the Cu line are covered by the diffusion barrier/liner layer where the bonding strength is rather strong, while the top surface is covered by a capping layer to strengthen the bonding at the interface. While graphene has been recently demonstrated to improve Cu electromigration lifetime [54], the bonding strength between Cu and 2D materials has not been widely studied yet. Thorough studies should be carried out on MoS<sub>2</sub> and h-BN to examine their impacts on electromigration lifetime in addition to their diffusion barrier properties.

#### 2.5 STEM/EDS/EELS Analysis

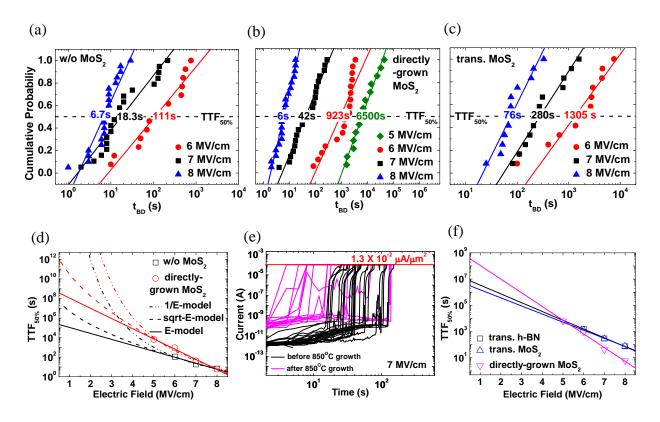

Besides electrical measurements, STEM in conjunction with EDS and EELS were used for structural analysis and compositional/chemical mapping of the interface and inter-diffusion processes. Devices without a barrier, with transferred h-BN barrier, and with directly- grown MoS<sub>2</sub> were analyzed. Each device had an Al cap on top to prevent Cu oxidation and was electrically stressed at 6 MV/cm for 250 s. Under this stress condition, only the control device without a barrier broke down, whereas devices with 2D barriers maintained their initial current values and no breakdown was observed. Fig. 2.6(a) shows the HAADF (high-angle annular dark-field) STEM cross-sectional image of the MoS<sub>2</sub> sample. As the heaviest element, Cu gives the brightest contrast while SiO<sub>2</sub>/Si and Al appear relatively darker, as expected. Between Al and Cu, there appears to

be a uniform layer with a light contrast. EDS suggests that this layer was formed by intermixing of Al with diffused Cu. In both STEM image and EDS line scans, the Cu/SiO<sub>2</sub> interface appears sharp with a MoS<sub>2</sub> layer clearly detected in between, and Cu diffusion into SiO<sub>2</sub> is greatly suppressed.

In the device with the transferred h-BN barrier, the Al and Cu regions were hardly distinguishable, as observed from both the STEM and EDS line scan profile in Fig. 2.6(b). This strong interdiffusion of Al and Cu could be a result of poor Cu adhesion on h-BN. At the Cu/SiO<sub>2</sub> interface, a very weak N signal (not shown) can be identified for the h-BN layers, while the B signal is too small to be detected in EDS. To further verify the existence and position of the h-BN layer, EELS was conducted given its superior resolution for lighter elements. As shown in Fig. 2.6(c), B and N signals were detected between the Cu and SiO<sub>2</sub> layer. Similar to the MoS<sub>2</sub> sample, Cu diffusion into SiO<sub>2</sub> is prevented.

In contrast, the MOS capacitor structure of the control device without any barrier was severely altered by the electrical stress, with Figs. 2.6(d) and 2.6(e) as two examples. In Fig. 2.6(d), a ball-like feature displaying strong Cu signals was formed. In Fig. 2.6(e), a large amount of Cu diffused through SiO<sub>2</sub> and reached the Si substrate. This phenomenon has been observed and identified as copper silicide formation by others [12]–[14], where Cu ions reacted with Si after the diffusion. Note that the devices in previous reports were thermally stressed; while electrical field stress was used in this work, with all measurements at room temperature. This can explain why crystalline copper silicide was not clearly observed here, possibly due to the lack of thermal energy.

Comparing the TEM cross-sections in Figs. 2.6(a) and 2.6(b), we conclude that Cu started to diffuse into SiO<sub>2</sub> in the transferred h-BN device even though no breakdown was measured and the device structure was not changed; whereas no such diffusion was observed at all in the device with directly-grown MoS<sub>2</sub> barrier. Similar results were observed in STEM cross-sections of six other positions (three for h-BN and three for MoS<sub>2</sub>). Therefore, we conclude that directly-grownMoS<sub>2</sub> performs better as a diffusion barrier, which is consistent with the TDDB results.

Fig. 2.6 Structural, compositional, and chemical analyses. STEM cross-sections and EDS line scan profiles of devices (a) with directly-grown MoS<sub>2</sub>, (b) with transferred h-BN, and (d)(e) without any barriers. The structures of control devices without barriers were completely damaged after the electrical stress (6 MV/cm; 250 s). The device with either h-BN or MoS<sub>2</sub> barrier remained unaltered and Cu signals were barely found in the SiO<sub>2</sub> region. (c) EELS line scan profile of the device with h-BN barrier. B and N signals can be detected in-between Cu and SiO<sub>2</sub> layers. Cu diffusion into SiO<sub>2</sub> was suppressed by h-BN barrier.

#### 2.6 Conclusion

In this chapter, the barrier energies for Cu diffusion of multiple 2D materials are predicted using DFT calculations, with the results showing potential of many 2D materials. Experimentally, the diffusion barrier properties of two types of 2D materials, h-BN and MoS<sub>2</sub> have been evaluated using TDDB measurements and with STEM, EDS, and EELS analysis. Predictions of substantial device lifetime improvement are made by analytical models based on experimentally measured times-to-breakdown. The work in this chapter provides strong evidence that these atomically thin 2D materials are capable of suppressing Cu diffusion into surrounding dielectrics, identifying them as potential sub-nanometer thin barrier solutions for interconnect technology. We further conclude that direct growth of 2D barriers on dielectric substrates is favored over that of transferred 2D barriers, at least with the present state of the art in both processes. Future studies must focus on a more detailed understanding of the diffusion and breakdown mechanisms through 2D materials, and an optimization of the 2D material deposition to be BEOL compatible.

# 3. DEVELOPMENT AND EVALUATIONS OF BACK-END-OF-LINE COMPATIBLE TWO-DIMENSIONAL DIFFUSION BARRIERS

Most of the material in this chapter has been reprinted with permission from "C.-L. Lo, K. Zhang, R. S. Smith, K. Shah, J. A. Robinson, and Z. Chen; IEEE Electron Device Letters, vol. 39, no. 6, pp. 873-876, 2018". Copyright @ 2018, IEEE, "C.-L. Lo, S. Zhang, T. Shen, J. Appenzeller, Z. Chen; in Proc. of IEEE Device Research Conference, 2017". Copyright @ 2017, IEEE, and "C.-L. Lo, K. Zhang, J. A. Robinson, and Z. Chen; in Proc. of International Symposium on VLSI Technology, Systems and Applications (VLSI-TSA), 2018". Copyright @ 2018, and " C.-L. Lo, B. A. Helfrecht, Y. He, D. M. Guzman, N. Onofrio, S. Zhang, D. Weinstein, A. Strachan, and Z. Chen; in Journal of Applied Physics, vol. 120, no. 8, 2020". Copyright @ 2020, American Institute of Physics.

#### 3.1 Introduction

In the previous chapter, we have shown the promising diffusion barrier properties of 2D layered materials, h-BN and MoS<sub>2</sub> specifically. Together with other graphene barrier works, it is convincing that 2D layered materials are great candidates of diffusion barrier alternatives. However, despite the abovementioned benefits of 2D layered materials, a BEOL compatible growth process that can directly deposit ultrathin 2D barriers on dielectrics has not yet been realized. The obstacle lies in the requirement of high temperature and the substrate dependent growth [55], [56]. Diffusion barriers need to be directly deposited on the dielectrics of the Damascene Structures. However, for some materials, such as graphene, growth on dielectrics is more challenging than on Cu [16], [54], especially at low temperatures. An approach of growing 2D materials on catalytic substrates followed by a transfer process to substrate of interest is usually adopted for planar structures [13], [57], which often introduces defects to the barrier material and raises concerns of conformal coverage for Damascene structures. Table 2.1 summarizes works using 2D material as diffusion barriers. It is obviously that each method has its own issue for the BEOL integration. In this chapter, a single-layer (1L)  $MoS_2$  (~0.62 nm) directly grown on dielectrics at 400 °C is achieved by metal-organic chemical vapor deposition (MOCVD). We will show that these barriers can effectively prevent Cu diffusion and enhance the dielectric reliability. In addition, diffusion barrier property of this BEOL-compatible MoS<sub>2</sub> and that of the hightemperature-grown MoS<sub>2</sub> in the previous chapter will be compared.

| Material                         | Thickness                                     | Growth<br>Temperature | Accomplishment                           | Method                               |

|----------------------------------|-----------------------------------------------|-----------------------|------------------------------------------|--------------------------------------|

| Graphene [16]                    | 1 nm                                          | 650 °C                | Reduce surface<br>scattering/resistivity | Grown on Cu                          |

| Graphene [54]                    | > 10nm (1-2 layers of<br>Gr + 10 nm a-carbon) | 400 °C                | Improve electromigration<br>lifetime     | Grown on Cu                          |

| MoS <sub>2</sub> (Chap. 2)       | < 1 nm                                        | 850 °C                | Mitigate Cu diffusion                    | Direct-grown on<br>SiO <sub>2</sub>  |

| Graphene [57]                    | < 1 nm                                        | 1000 °C               | Mitigate Cu diffusion                    | Transfer from Cu<br>foil             |

| Graphene/graphe<br>ne oxide [14] | < 1 nm / ~ 1 nm                               | 750 °C                | Mitigate Cu diffusion                    | Transfer from Cu<br>substrate        |