# DIGITAL SIGNAL PROCESSING ARCHITECTURE DESIGN FOR CLOSED-LOOP ELECTRICAL NERVE STIMULATION SYSTEMS

by

Jui-Wei Tsai

## **A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical and Computer Engineering West Lafayette, Indiana December 2020

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

| Dr. Pedro P | Irazoqui, | Chair |

|-------------|-----------|-------|

|-------------|-----------|-------|

Department of Electrical and Computer Engineering

Dr. Kaushik Roy

Department of Electrical and Computer Engineering

Dr. Anand Raghunathan

Department of Electrical and Computer Engineering

Dr. Vijay Raghunathan

Department of Electrical and Computer Engineering

Dr. Matthew P. Ward

Department of Biomedical Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of the Graduate Program

To my beloved wife, daughter and parents.

## ACKNOWLEDGMENTS

The journey toward PhD degree is never easy, and I wouldn't have been able to complete it without tremendous help from many people.

First, I would like to thank my major advisor, Dr. Pedro Irazoqui, who appreciates my skills and lets me work in his lab throughout these years. Thank you for supporting my research and being patient with me. I'd also like to thank Dr. Kaushik Roy, Dr. Anand Raghunathan, Dr. Vijay Raghunathan, and Dr. Matthew Ward, for being interested in my work and willing to be my committee members. I'm also grateful for Dr. Michael Capano, the graduate coordinator of ECE Dept., who has been a patient mentor in my difficult time.

I would like to thank my lab colleagues, Dr. Hansraj Bhamra, Dr. Young-Joon Kim, Dr. Yu-Wen Huang, Dr. Oren Gall, Dr. John Lynch, Dr. Steven Lee, Dr. Rebecca Bercich, Dr. Henry Mei, Dr. Daniel Pederson, Dr. Quan Yuan, Dr. Kurt Qing, Dr. Muhammad Arafat, Dr. Jesse Somann, Dr. Jack Williams, Brandon Coventry, Henry Zhang, Grant (Zhi) Wang, Kyle Thackston, Chris Quinkert, Jay Shah, Vivek Ganesh, Gang Seo, Kaitlyn Neihouser, Ethan Biggs, Ryan Budde, and Gabriel Albors, the managing director of the Center for Implantable Devices. Thank you for many valuable discussions and helps in my experiments. I'm especially thankful for Dr. Hansraj Bhamra and Brandon Coventry who were always willing to talk with me whenever I felt hopeless about my PhD program.

I owe my thanks to Dr. Mark Johnson and Neal (Nien-Shiang) Chang, the manager of Taiwan Semiconductor Research Institute, Hsinchu City, Taiwan, who provided me with great technical assistances in ASIC design, especially its CAD tools. I also want to thank the teaching assistants of the ECE Senior Design course, Nathan Conrad, Shelly (Hengying) Shan, Steve Rausch and Sutton Hathorn, for giving me lot of valuable suggestions on the design of wireless devices.

I would like to thank the pastors of St. Thomas Aquinas, West Lafayette, IN, Fr. Patrick, Fr. Timothy, and Fr. Cassen. I want to give thanks to many brothers and sisters in Christ, Thomas Combiths, Susan Combiths, Maria (Eunjin) Cheon, En-Pei Han, Yu-Chen Lin, Jesyin Lai and

Tsung-Tai Yeh. Thank you for your kind-heartedness, generosity, and, most importantly, earnest praying for my PhD career. I also want to thank Master Kyu-Young Chai, the grand master of Chai Taekwondo, Lafayette, IN, and Coach Carlos Soto, the head coach of Impact Zone Training Center, West Lafayette, IN. You helped me build my physical and mental strength and showed your care about my life in the USA.

I'm also grateful for Dr. Ching-Chang Chien and Dr. Yu-Chuan Su, the professors of ESS Dept., NTHU, Taiwan, and Dr. Song-Nien Tang, the assistant professor of CS Dept., CYCU, Taiwan. I wouldn't have come to Purdue without you giving me the opportunity to work with you back in Taiwan. Thank you for always caring about my career at Purdue.

I would like to express my sincerest gratitude to my wife, Maria Teresa Kuo, who always stands with me in every despairing moment, my daughter, Katie Tsai, the little angel who is always a cheer for me, my parents, Mr. Jung-Chieh Tsai and Mrs. Yue-Chun Kuo, who bring me up and have always been my role model throughout these 35 years, my parents-in-laws, Mr. Jose (Yung-Chung) Kuo and Mrs. Bernadette (Hui-Fen) Hu, who believe in me and let Teresa stay with me in these years, my sister, Joanna (Jui-Yu) Tsai, and my brother-in-law, Jose (Chen-Wei) Kuo. It is your love that keeps encouraging me to stick with this program no matter what happened. I would also like to thank Mr. Andy (Te-Hsiu) Huang, my elementary school teacher, for your unceasingly care since my childhood. "*Don't forget why you started*". It is what you told me in 2018 when I lost my assistantship, got stuck in my research, and even thought about going home, which still reminds and motivates me today. This thesis is especially dedicated to Mr. Jose (Yung-Chung) Kuo and Mr. Andy (Te-Hsiu) Huang, sadly, who left us on 2020. Hope you'll be proud to see me complete my PhD program, and hope you meet my beloved uncle Mr. Jung-Chin Tsai and grandparents in heaven.

Last but not the least, I would like to give this glory to the Lord. It's not by my strength, but by His grace, that I walked through each mountain and valley and finished this program. I would also like to thank whoever helped me and encouraged me in this journey yet I forgot to mention you in this acknowledgement. I wouldn't have made it without each of you, thank you.

"Trust in the LORD with all your heart, on your own intelligence do not rely; In all your ways be mindful of him, and he will make straight your paths." - Proverb 3:5-6

# TABLE OF CONTENTS

|                                                                           | OF TA                                                       | BLES                                                                                                                                                                                                                                      | 9                                                                                                                          |

|---------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| LIST (                                                                    | OF FIC                                                      | JURES                                                                                                                                                                                                                                     |                                                                                                                            |

| Abbrev                                                                    | viatior                                                     | s                                                                                                                                                                                                                                         | 14                                                                                                                         |

| ABST                                                                      | RACT                                                        |                                                                                                                                                                                                                                           | 16                                                                                                                         |

| 1. IN                                                                     | ITROI                                                       | DUCTION                                                                                                                                                                                                                                   |                                                                                                                            |

| 1.1                                                                       | Bac                                                         | kground                                                                                                                                                                                                                                   |                                                                                                                            |

| 1.2                                                                       | Aut                                                         | onomous Nerve Control                                                                                                                                                                                                                     |                                                                                                                            |

| 1.3                                                                       | Neu                                                         | ral Response Telemetry                                                                                                                                                                                                                    |                                                                                                                            |

| 1.4                                                                       | Elec                                                        | trically-Evoked Compound Action Potential                                                                                                                                                                                                 |                                                                                                                            |

| 1.5                                                                       | Rea                                                         | I-Time Digital Signal Processing for Closed-Loop Neurostimulation                                                                                                                                                                         |                                                                                                                            |

| 1.6                                                                       | Mot                                                         | ivation                                                                                                                                                                                                                                   |                                                                                                                            |

| 1.7                                                                       | Out                                                         | line of Thesis                                                                                                                                                                                                                            |                                                                                                                            |

| 2. A                                                                      | DSP /                                                       | ARCHITECTURE FOR REAL-TIME EVOKED COMPOUND ACTION                                                                                                                                                                                         | N                                                                                                                          |

| POTE                                                                      | NTIAI                                                       | RECOVERY IN NEURAL RESPONSE TELEMETRY SYSTEM                                                                                                                                                                                              |                                                                                                                            |

| 2.1                                                                       | Intr                                                        | oduction                                                                                                                                                                                                                                  | 35                                                                                                                         |

|                                                                           |                                                             |                                                                                                                                                                                                                                           |                                                                                                                            |

| 2.2                                                                       | Bid                                                         | rectional-Filtered Coherent Averaging                                                                                                                                                                                                     |                                                                                                                            |

| 2.2<br>2.3                                                                |                                                             |                                                                                                                                                                                                                                           |                                                                                                                            |

| 2.3                                                                       |                                                             | rectional-Filtered Coherent Averaging                                                                                                                                                                                                     | 40<br>46                                                                                                                   |

| 2.3<br>2                                                                  | Arc                                                         | rectional-Filtered Coherent Averaging                                                                                                                                                                                                     |                                                                                                                            |

| 2.3<br>2.3<br>2.3                                                         | Arc<br>3.1                                                  | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview                                                                                                                                                              |                                                                                                                            |

| 2.3<br>2.3<br>2.3<br>2.3                                                  | Arc<br>3.1<br>3.2                                           | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview<br>Stimulation Controller                                                                                                                                    |                                                                                                                            |

| 2.3<br>2.3<br>2.3<br>2.3<br>2.3                                           | Arc<br>3.1<br>3.2<br>3.3                                    | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview<br>Stimulation Controller<br>BFCA Core                                                                                                                       |                                                                                                                            |

| 2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3                                    | Arc<br>3.1<br>3.2<br>3.3<br>3.4                             | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview<br>Stimulation Controller<br>BFCA Core<br>Exponentially-Weighted Moving Average                                                                              |                                                                                                                            |

| 2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3                                    | Arc<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6               | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview<br>Stimulation Controller<br>BFCA Core<br>Exponentially-Weighted Moving Average<br>Configurable Folded IIR filter Design                                     | 40<br>46<br>46<br>47<br>47<br>49<br>54<br>54<br>56<br>60                                                                   |

| 2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.4                      | Arc<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6               | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview<br>Stimulation Controller<br>BFCA Core<br>Exponentially-Weighted Moving Average<br>Configurable Folded IIR filter Design<br>Output Buffer                    |                                                                                                                            |

| 2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.4<br>2.4<br>2.4        | Arc<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Exp        | rectional-Filtered Coherent Averaging<br>hitecture Design<br>System Overview<br>Stimulation Controller<br>BFCA Core<br>Exponentially-Weighted Moving Average<br>Configurable Folded IIR filter Design<br>Output Buffer<br>eriment Results | $ \begin{array}{c}  & 40 \\  & 46 \\  & 46 \\  & 47 \\  & 49 \\  & 54 \\  & 56 \\  & 60 \\  & 60 \\  & 60 \\ \end{array} $ |

| 2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.3<br>2.4<br>2.4<br>2.4<br>2.4 | Arc<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>Exp<br>4.1 | rectional-Filtered Coherent Averaging                                                                                                                                                                                                     | 40 $46$ $46$ $47$ $49$ $54$ $56$ $60$ $60$ $60$ $60$ $62$                                                                  |

| 3. FRI | EE: FIBER-RESPONSE EXTRACTION ENGINE ON A CUSTOM-MADE |     |

|--------|-------------------------------------------------------|-----|

| WEARA  | ABLE DEVICE FOR AUTONOMOUS NERVE ACTIVATION CONTROL   | 73  |

| 3.1    | Introduction                                          | 73  |

| 3.2    | System Overview                                       | 77  |

| 3.3    | Architecture Design                                   | 80  |

| 3.3.   | .1 BFCA Core in FREE                                  | 80  |

| 3.3.   | .2 Peak Detector                                      | 81  |

| 3.3.   | .3 Fiber Response Classifier                          | 85  |

| 3.3.   | .4 Output Buffer in FREE                              | 87  |

| 3.4    | PCB Prototype of Wearable Device                      | 88  |

| 3.5    | Experiment Results                                    | 92  |

| 3.5.   | .1 Experiment Setup                                   | 92  |

| 3.5.   | .2 Precision Comparison                               | 94  |

| 3.5.   | .3 In-Vivo Test Results 1                             | 100 |

| 3.5.   | .4 ASIC Implementation 1                              | 102 |

| 3.6    | Conclusion of This Chapter 1                          | 104 |

| 4. CO  | NCLUSION AND FUTURE WORK 1                            | 105 |

| 4.1    | Conclusion1                                           | 105 |

| 4.2    | Future Work1                                          | 106 |

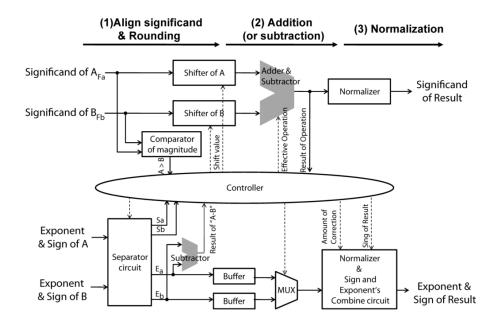

| 4.2.   | .1 Half-Precision Floating-Point Computation 1        | 106 |

| 4.2.   | .2 Data Compression of ECAP                           | 108 |

| 4.2.   | .3 Implantable Wireless Device 1                      | 111 |

| REFERI | ENCES 1                                               | 116 |

| VITA   |                                                       | 126 |

## LIST OF TABLES

| Table 2.1 | Comparison with other filtering techniques                         | 71 |

|-----------|--------------------------------------------------------------------|----|

| Table 3.1 | Peak Detection Algorithm                                           | 83 |

| Table 3.2 | List of the components used in the PMU PCB                         | 91 |

| Table 3.3 | Performance comparison between hardware and software processing 10 | 03 |

| Table 4.1 | Comparison of the low-power COTS Bluetooth modules [151] 1         | 15 |

## LIST OF FIGURES

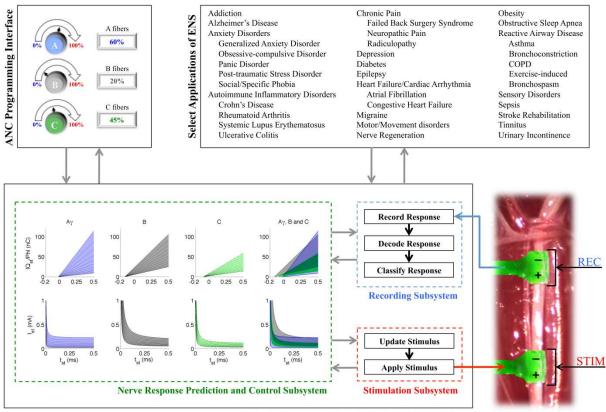

| Fig. 1.1 Block diagram of the autonomous nerve control (ANC) system and its applications. [35]                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

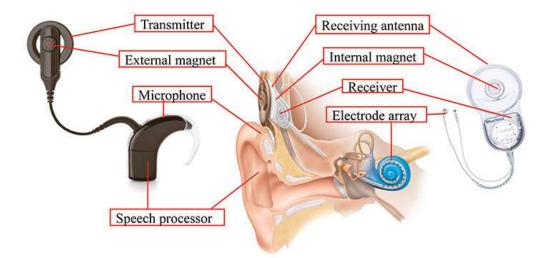

| Fig. 1.2 A typical modern cochlear implant system that provides electrical stimuli to auditory nerve [42]                                                                                                                                                                        |

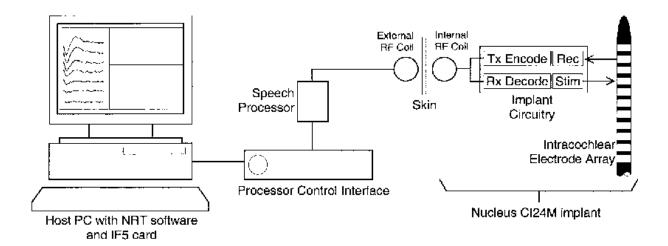

| Fig. 1.3 Nueral Response Telemetry (NRT) system in Nucleus CI24M cochlear implant [43] 23                                                                                                                                                                                        |

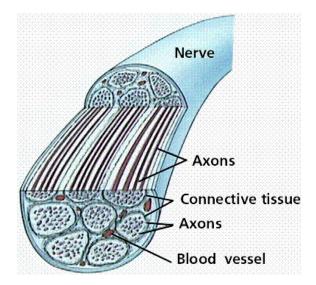

| Fig. 1.4 Cross-section of a nerve and group of nerve fibers (axons) [48]                                                                                                                                                                                                         |

| Fig. 1.5 Classification of nerve fiber types [49]                                                                                                                                                                                                                                |

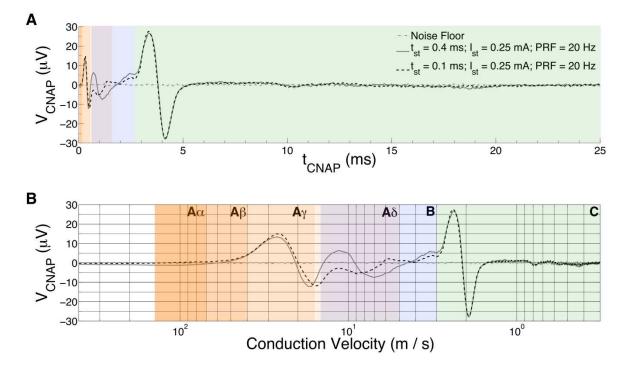

| Fig. 1.6 Classification of nerve fiber responses on ECAP waveforms plotted (A) against time axis and (B) as a function of conduction velocity. The ECAP responses are obtained from the left cervical vagus nerve of rat ( <i>Conduction distance</i> = $8.0 \pm 0.5$ mm) [35]25 |

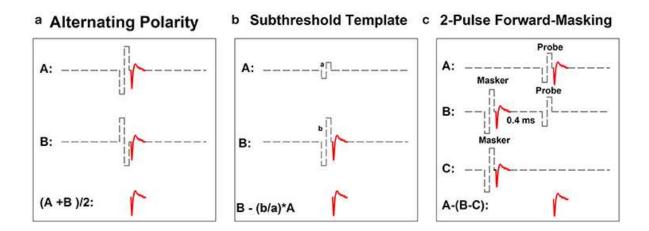

| Fig. 1.7 The three most commonly used methods for stimulus artifact reduction in ECAP recording: (a) alternating polarity, (b) subthreshold template subtraction, and (c) 2-pulse forward masking paradigm [50]                                                                  |

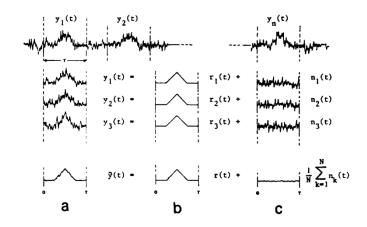

| Fig. 1.8 Principle of the coherent avearing (CA) technique [52]                                                                                                                                                                                                                  |

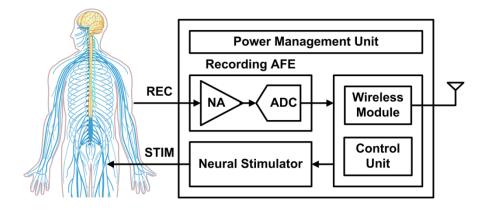

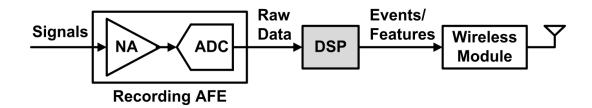

| Fig. 1.9 High-level block diagram of a typical wireless wearable (or implantable) device for closed-loop neurostimulation                                                                                                                                                        |

| Fig. 1.10 Illustration of a real-time digital signal processing (DSP) engine on a wireless device.                                                                                                                                                                               |

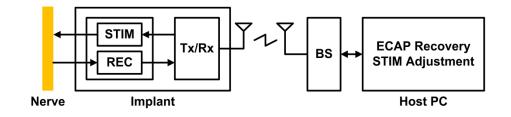

| Fig. 2.1 Illustration of Conventional bidirectional neural response telemetry (NRT) systems36                                                                                                                                                                                    |

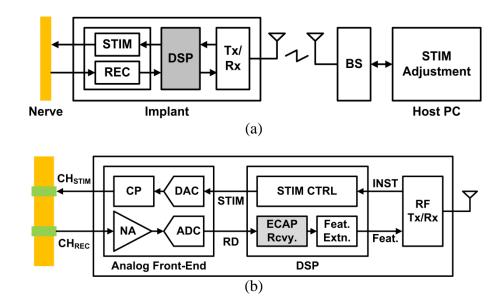

| Fig. 2.2 (a) The NRT systems with a digital signal processor. (b) Details of stimulation and recording analog front-ends (AFE) and digital signal processor on the implant                                                                                                       |

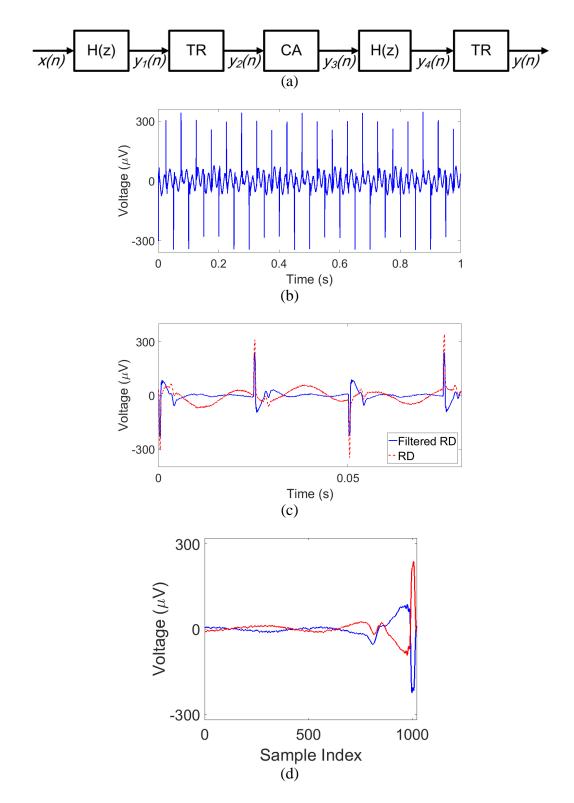

| Fig. 2.3 Principle of the proposed bidirectional-filtered coherent averaging (BFCA) method combined with the alternating-polarity (AP) stimulation method for stimulus artifact rejection and distortion-free denoising of ECAP                                                  |

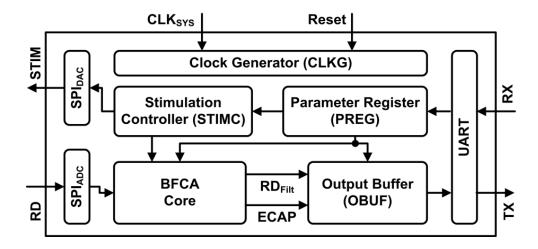

| Fig. 2.4 Block diagram of the proposed DSP architecture for real-time ECAP recovery                                                                                                                                                                                              |

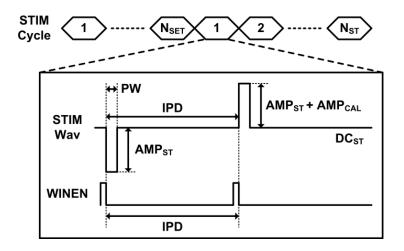

| Fig. 2.5 Generation of the alternating-polarity stimulus pulse and time-locked windowing control in stimulation controller                                                                                                                                                       |

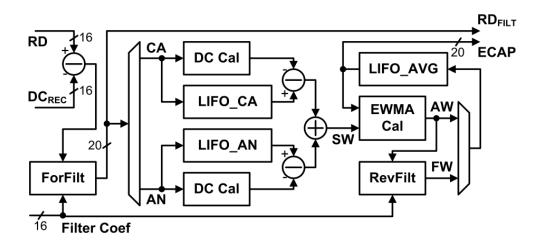

| Fig. 2.6 Schematic of the BFCA core                                                                                                                                                                                                                                              |

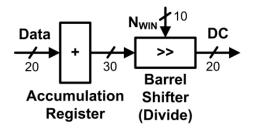

| Fig. 2.7 Schematic of the DC calculator                                                                                                                                                                                                                                          |

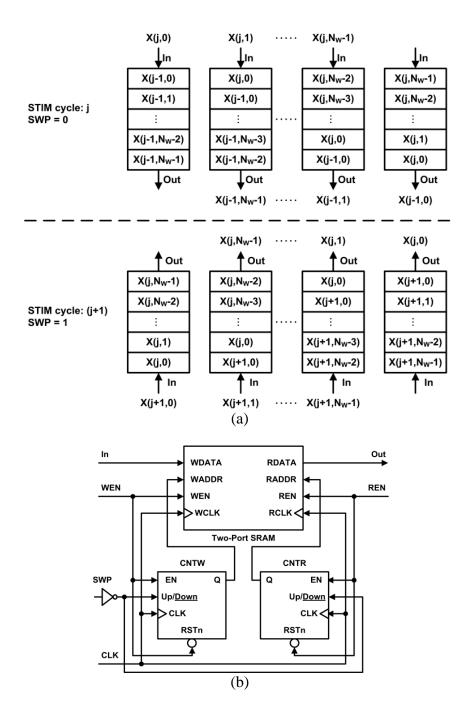

| Fig. 2.8 (a) Time reversal via LIFO register and (b) its implementation with a two-port SRAM and two binary up/down counters                                                                                                                                                     |

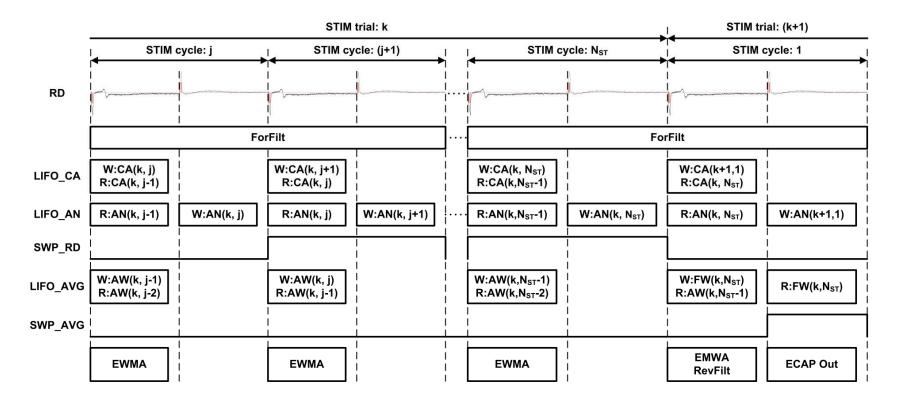

| Fig. 2.9 Timing diagram of the BFCA core under continuous neural data input                                                                                                                                                                                                      |

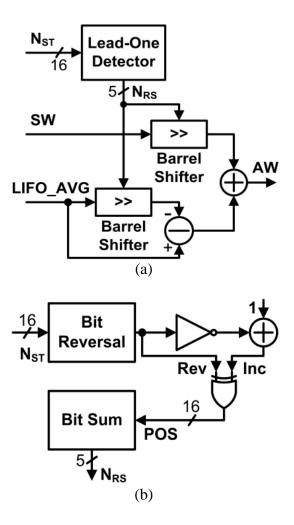

| Fig. 2.10 Schematics of the (a) exponentially-weighted moving-average (EWMA) calculator and (b) lead-one detector for estimation of weighting factor in EWMA                                                                                                                               |

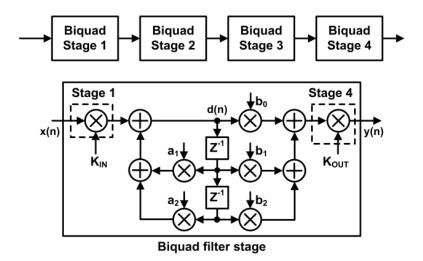

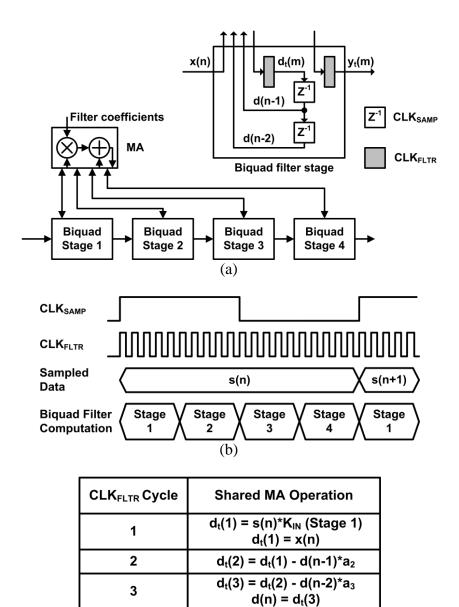

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.11 A conventional configurable 4-stage IIR filter                                                                                                                                                                                                                                   |

| Fig. 2.12 (a) The proposed configurable, folded 4-stage IIR filter with shared multiply-add (MA) unit, (b) its timing diagram, and (c) shared <i>MA</i> operation of a biquad filter stage                                                                                                 |

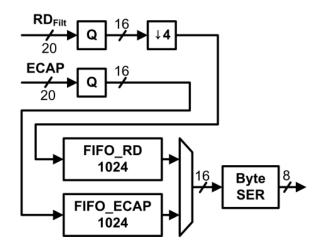

| Fig. 2.13 Schematic of the output buffer                                                                                                                                                                                                                                                   |

| Fig. 2.14 Power consumption of the DSP architecture in 180-nm CMOS process                                                                                                                                                                                                                 |

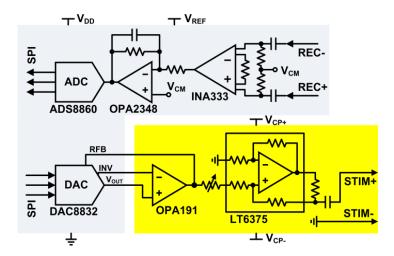

| Fig. 2.15 Circuit schematic of the stimulation and recording AFE                                                                                                                                                                                                                           |

| Fig. 2.16    Setup of in-vivo electrical nerve stimulation for verification of proposed DSP architecture                                                                                                                                                                                   |

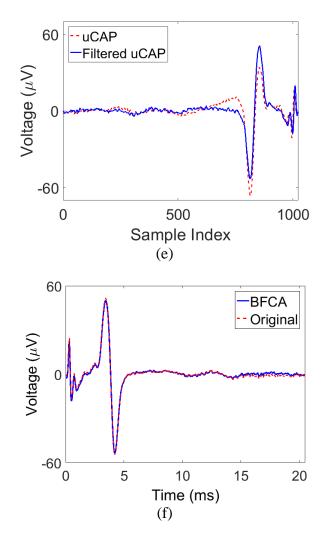

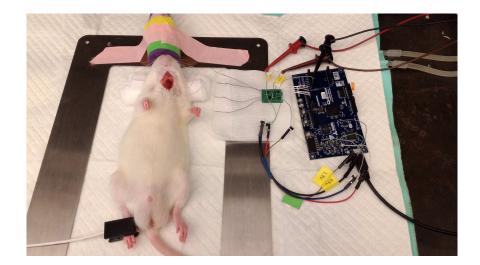

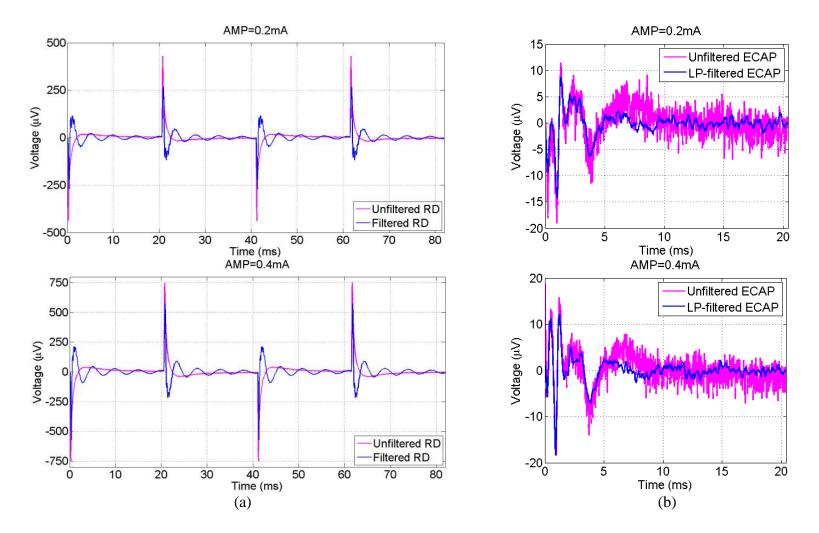

| Fig. 2.17 FPGA measurement results from stimulation trials with stimulus parameters $PW = 0.2$ ms, $PRF = 20$ Hz and $ttrain = 1$ s: (a) windowed raw data and (b) computed ECAP responses of two stimulation trials with stimulus current amplitude of 0.2 mA and 0.4 mA, respectively 65 |

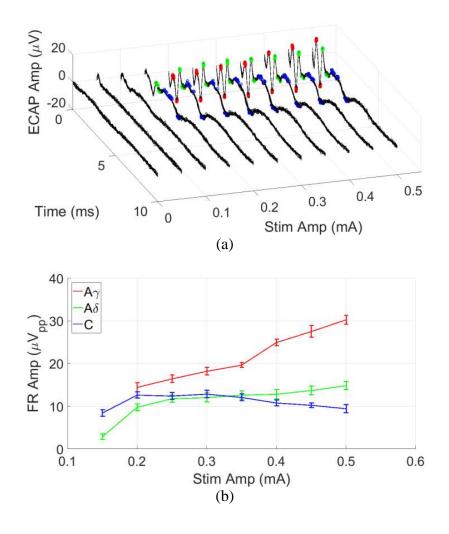

| Fig. 2.18 (a) FPGA measurement results of linear-phase filtered ECAP responses collected from stimulation trials with stimulus amplitude varying from 0 to 0.5 mA. (b) Amplitude growth function of nerve fiber responses designated by peaks on ECAP responses                            |

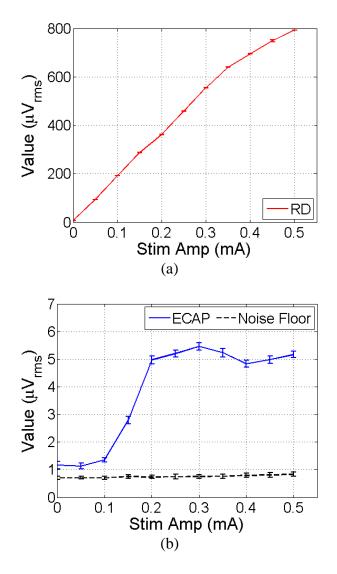

| Fig. 2.19 Root-mean-square (rms) value of stimulus artifacts in (a) raw data and (b) ECAP responses measured from FPGA. The rms value of noise floor in (b) is obtained from a 10-ms segment on each ECAP waveform containing no stimulus artifacts or nerve fiber responses 68            |

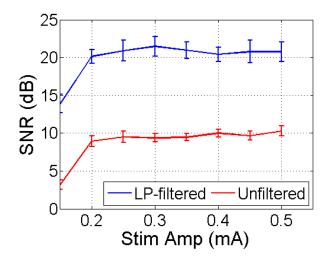

| Fig. 2.20 Signal-to-noise ratio (SNR) of linear-phase filtered versus unfiltered ECAP responses measured from FPGA                                                                                                                                                                         |

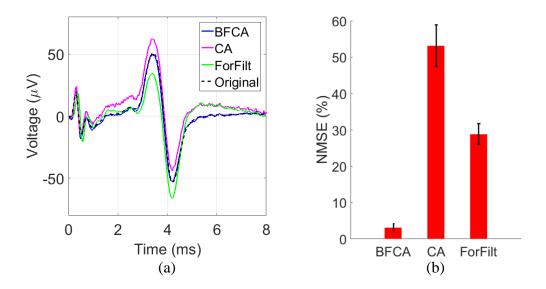

| Fig. 2.21 Waveform distortion caused by forward filtering (ForFilt), coherent averaging (CA) and linear-phase filtering via BFCA: (a) demonstration and (b) a quantitative comparison using normalized mean-square error (NMSE) between filtered and original noise-free ECAP waveforms    |

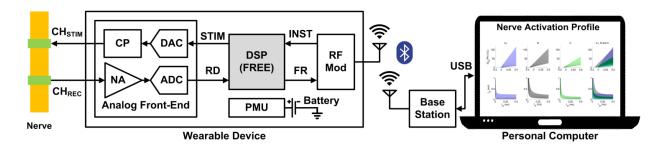

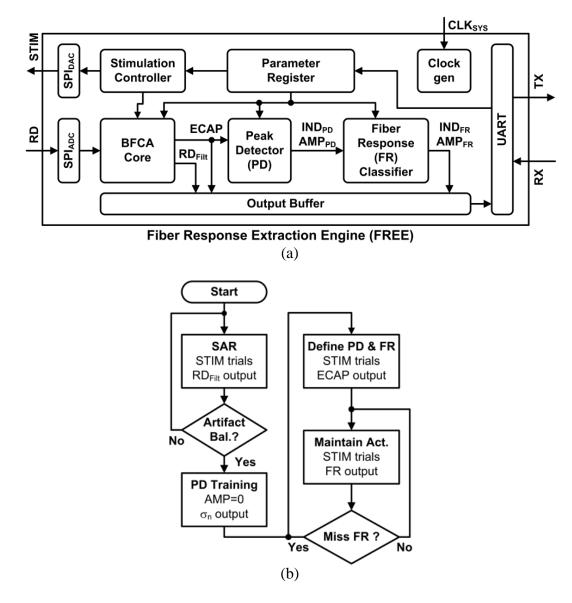

| Fig. 3.1 Top-level block diagram of the wireless wearable device in a closed-loop electrical nerve system and the proposed fiber-response extraction engine (FREE), a dedicated DSP engine for autonomous nerve activation control                                                         |

| Fig. 3.2 (a) Block diagram of the proposed fiber-response extraction engine (FREE) and (b) the flowchart of its operation                                                                                                                                                                  |

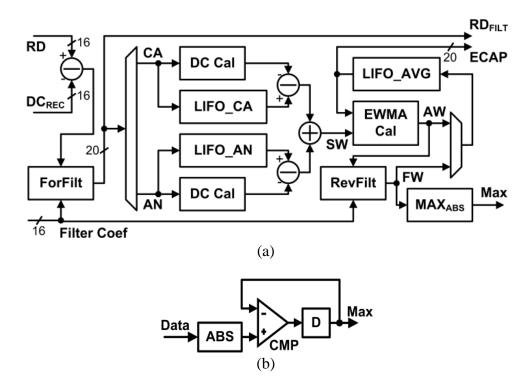

| Fig. 3.3 (a) Architecture of the BFCA core in FREE and (b) the schematic of the maximal absolute value detector                                                                                                                                                                            |

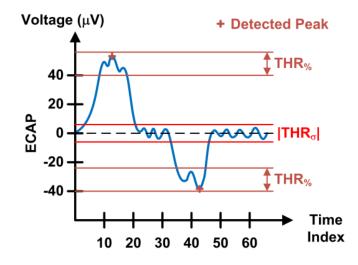

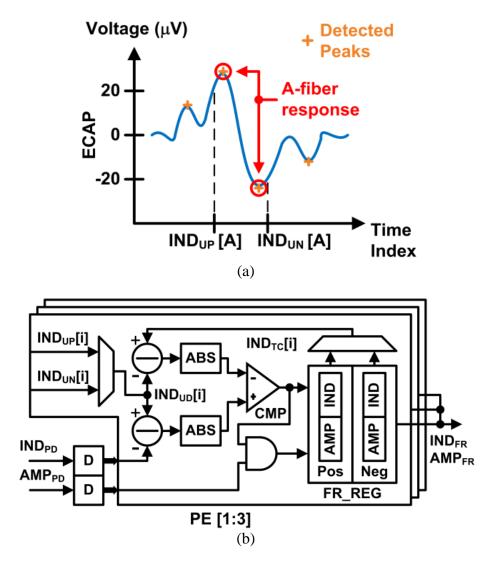

| Fig. 3.4 Illustration of the peak-detection principle                                                                                                                                                                                                                                      |

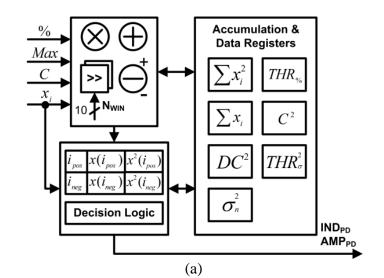

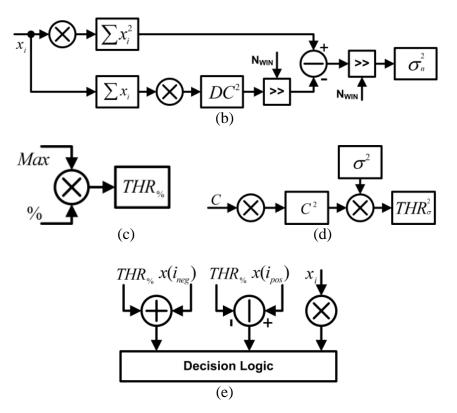

| Fig. 3.5 (a) Architecture of the neak detector. Data nath in the neak detector for (b) calculation                                                                                                                                                                                         |

| Fig. 3.6 (a) Principle of fiber-response (FR) classification and (b) its architecture                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

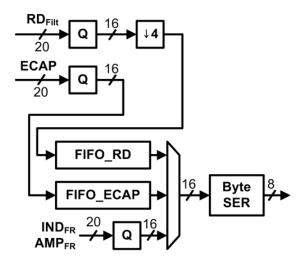

| Fig. 3.7 Schematic of the output buffer in FREE                                                                                                                                                                                                                                                                                                                                                                               |

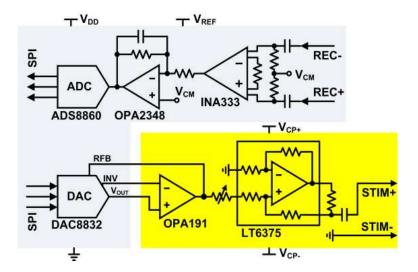

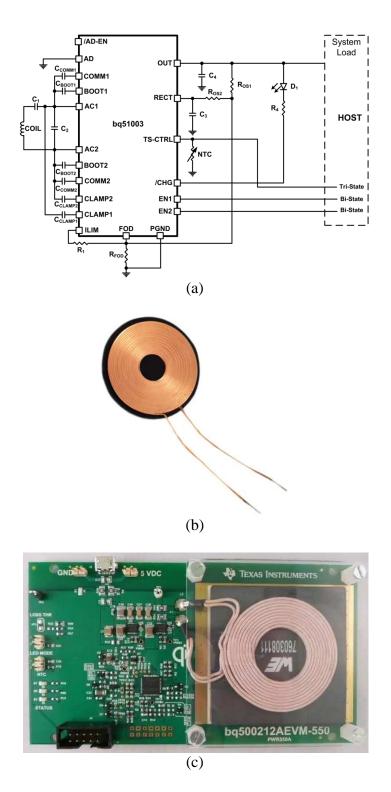

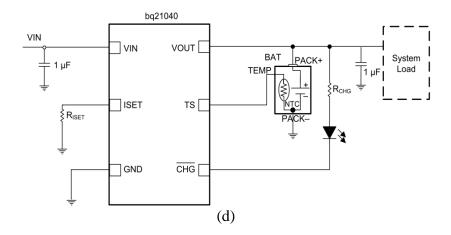

| Fig. 3.8 Schematic of the stimulation and recording analog front-end (AFE) in the wearable device                                                                                                                                                                                                                                                                                                                             |

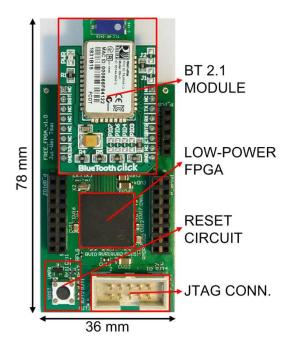

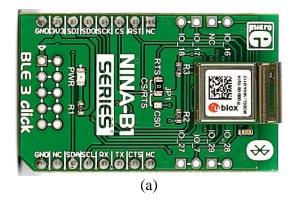

| Fig. 3.9 PCB prototype of the wireless signal processing (WSP) platform with major components annotated                                                                                                                                                                                                                                                                                                                       |

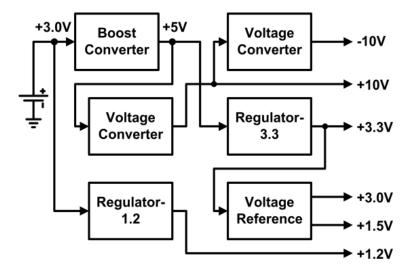

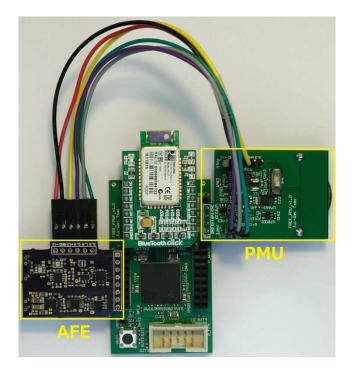

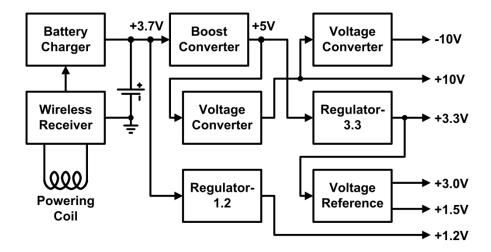

| Fig. 3.10 Block diagram of the power-management unit (PMU) for the power supply of the AFE and WSP platform                                                                                                                                                                                                                                                                                                                   |

| Fig. 3.11 The assembled PCB prototype of the wearable device                                                                                                                                                                                                                                                                                                                                                                  |

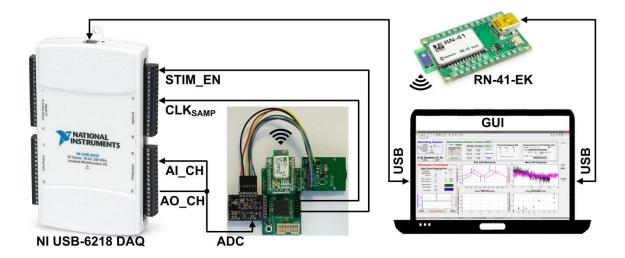

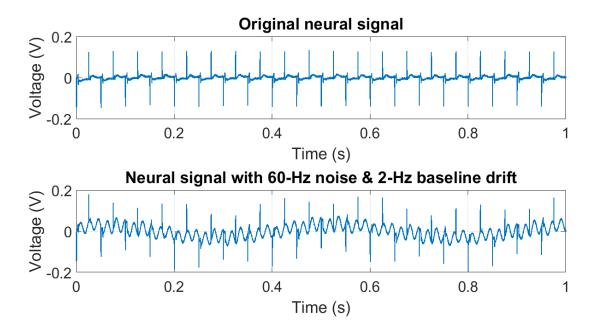

| Fig. 3.12 Illustration of experiment setup for performance comparison between hardware (HW) and software (SW) processing                                                                                                                                                                                                                                                                                                      |

| Fig. 3.13 Plots of the original neural signal recorded in a single stimulation trial that contains ECAP responses and the neural signal superimposed with 60-Hz noise and 2-Hz baseline drift as the input data for HW and SW comparison. The input data should be shifted by $+Vcm$ to meet the dynamic range of the ADC on AFE                                                                                              |

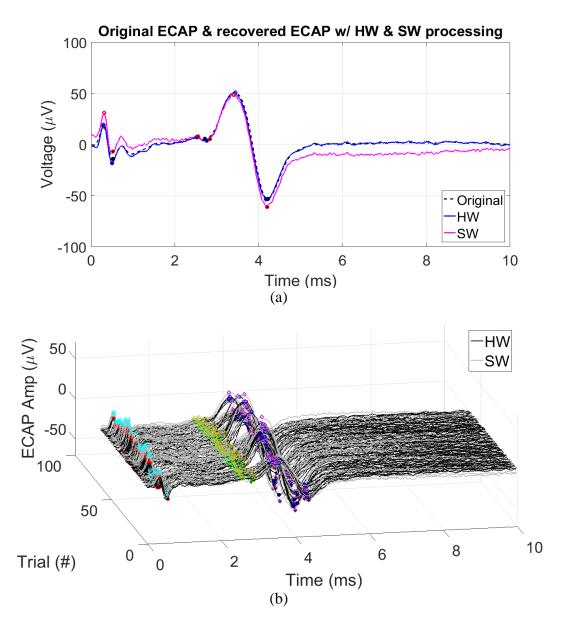

| Fig. 3.14 (a) An example of recovered ECAP via HW- and SW-processing versus the original ECAP waveform. (b) All HW- and SW-recovered ECAP responses from the entire input data set (66 trials)                                                                                                                                                                                                                                |

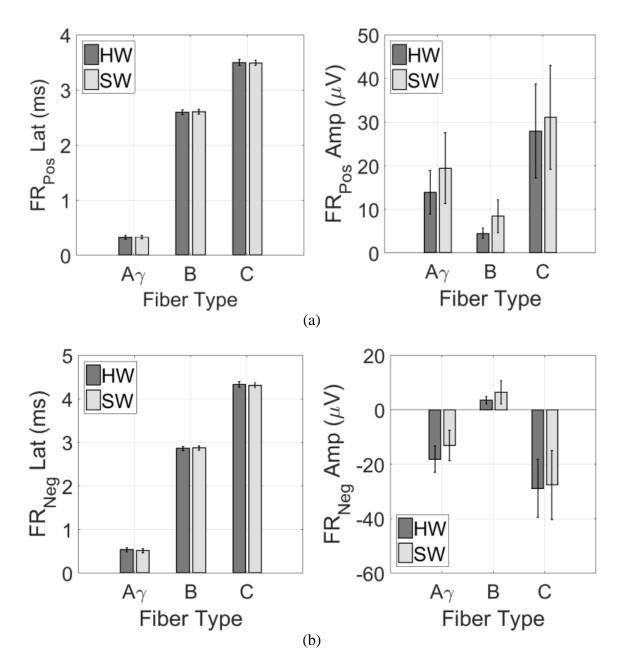

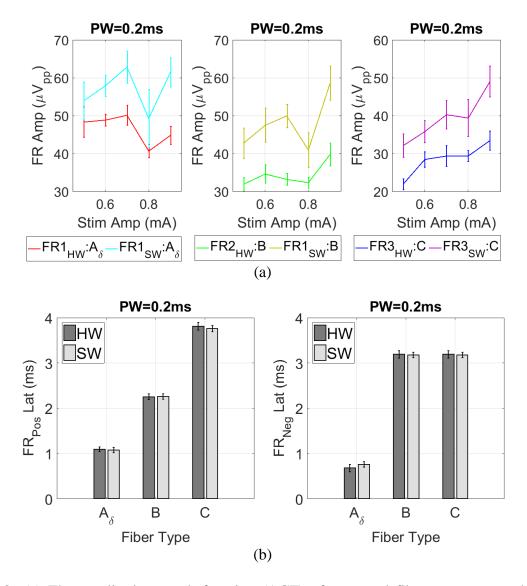

| Fig. 3.15 Mean latency and amplitude of extracted (a) positive and (b) negative fiber responses.<br>Both the positive and negative fiber responses extracted from HW have less amplitude variation than those from SW owing to the more effective removal of periodic noises on HW                                                                                                                                            |

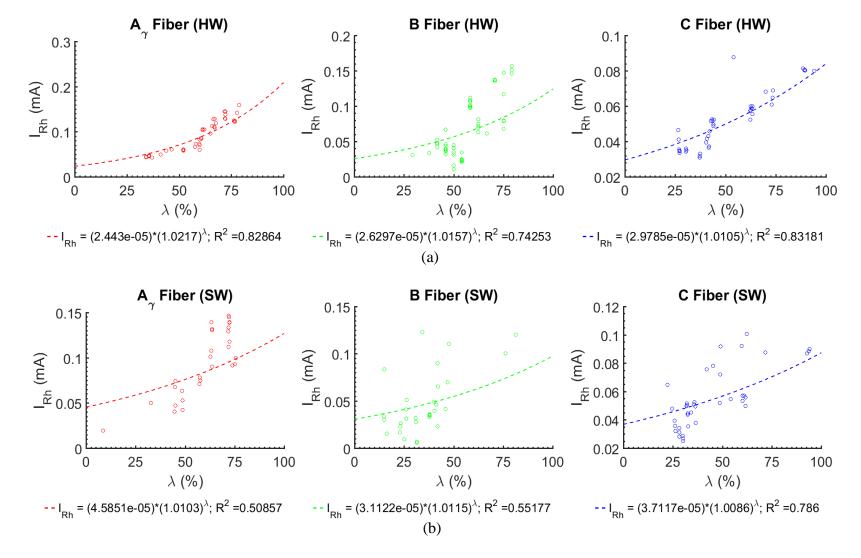

| Fig. 3.16 Slope-activation data of extracted fiber responses from (a) HW and (b) SW and the predicted slope-activation relationship (i.e., rheobase currents $I_{Rh}$ as a function of the percent activation level $\lambda$ ). The classification precision of fiber responses from HW and SW is reflected by the coefficient of determination R <sup>2</sup> which represents the goodness-of-fit of predicted $I_{Rh}$ 99 |

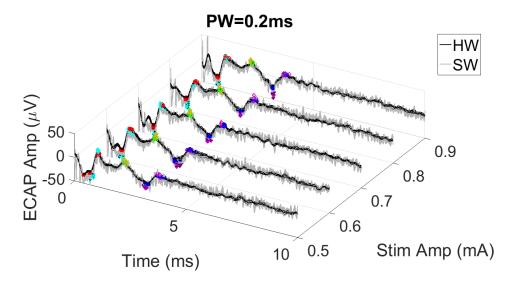

| Fig. 3.17 <i>In-vivo</i> test results ( $PW$ = stimulus pulse width = 0.2 ms; $PRF$ = pulse repetition frequency = 20 Hz; $t_{train}$ = stimulus train duration = 1 s) of HW- and SW- recovered ECAP waveforms and extracted fiber responses                                                                                                                                                                                  |

| Fig. 3.18 (a) The amplitude growth function (AGF) of extracted fiber responses and (c) the mean latency of positive and negative fiber responses extracted from HW and SW in in- <i>vivo</i> tests.                                                                                                                                                                                                                           |

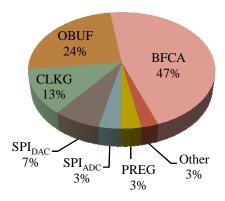

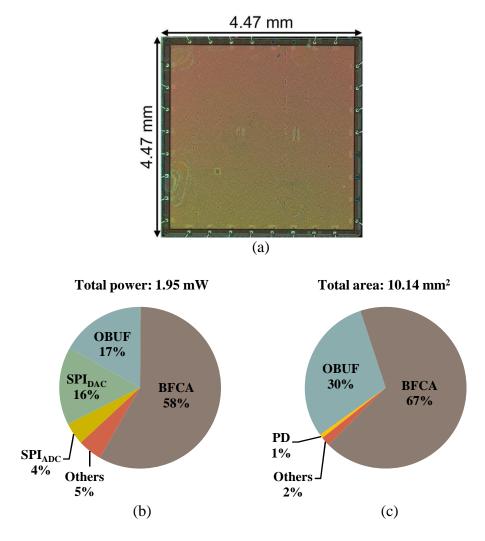

| Fig. 3.19 The ASIC implementation of proposed FREE in 180-nm CMOS technology: (a) die photo and breakdown of its (b) power and (c) area consumption                                                                                                                                                                                                                                                                           |

| Fig. 4.1 Block diagram of a half-precision bit-serial floating-point adder [132] 107                                                                                                                                                                                                                                                                                                                                          |

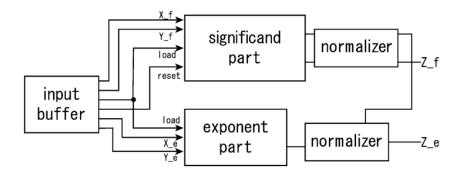

| Fig. 4.2 Block diagram of a half-precision floating-point multiplier, where $(X_e, Y_e)$ and $(X_f, Y_f)$ are exponents and fractions of two input signals, respectively, "load" and "reset" are control signals for each part, and $Z_e$ and $Z_f$ are the exponent and fraction of multiplier output [133].                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                               |

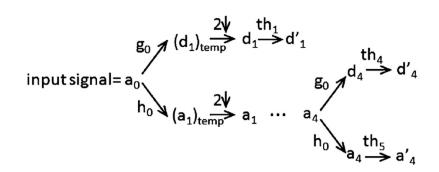

Fig. 4.3 Illustration of DWT algorithm for data compression with 4 levels of decomposition [63].

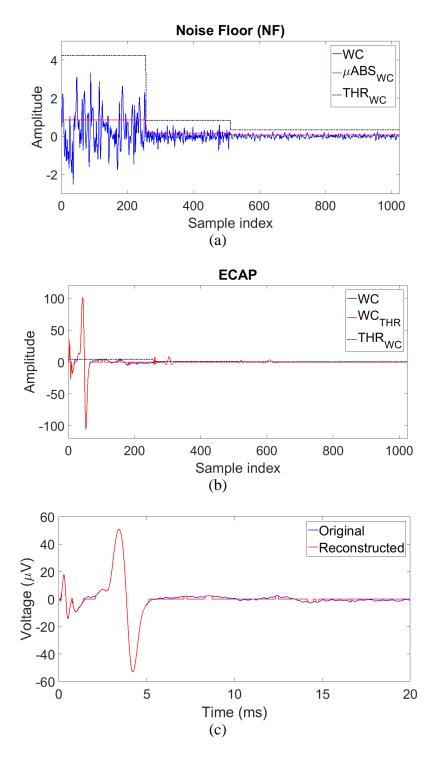

Fig. 4.4 Data compression of an ECAP waveform using 2-level Haar wavelet DWT: (a) derivation of the threshold (*THR*<sub>WC</sub>) based on the mean of absolute value of wavelet coefficients ( $\mu ABS_{WC}$ ), (b) origical versus thresholded wavelet coefficients (*WC*<sub>THR</sub>) of an ECAP waveform, and (c) origical versus reconstructed ECAP waveform. 110

## ABBREVIATIONS

| ADC  | Analog-to-Digital Converter                   |

|------|-----------------------------------------------|

| AFE  | Analog Front End                              |

| AGF  | Amplitude Growth Function                     |

| ANC  | Autonomous Nerve Control                      |

| AP   | Alternating Polarity                          |

| ASIC | Application-Specific Integrated Circuit       |

| BFCA | Bidirectional-Filtered Coherent Averaging     |

| BLE  | Bluetooth Low-Energy                          |

| BS   | Base Station                                  |

| CA   | Coherent Averaging                            |

| CMOS | Complementary Metal Oxide Semiconductor       |

| CMRR | Common Mode Rejection Ratio                   |

| COTS | Commercial Off-the-Shelf                      |

| СР   | Charge Pump                                   |

| DAC  | Digital-to-Analog Converter                   |

| DBS  | Deep Brain Stimulation                        |

| DSP  | Digital Signal Processing                     |

| DTFT | Discrete-Time Fourier Transform               |

| DWT  | Discrete Wavelet Transform                    |

| ECAP | Electrically-Evoked Compound Action Potential |

| ECG  | Electroencephalogram                          |

| ECoG | Electrocorticogram                            |

| EEG  | Electroencephalogram                          |

| ENG  | Electroneurogram                              |

| ENS  | Electrical Nerve Stimulation                  |

| EWMA | Exponentially-Weighted Moving Averaging       |

| FDA  | Food and Drug Administration                  |

| FIFO | First-In-First-Out                            |

| FIR  | Finite Impulse Response                       |

|      |                                               |

| FPGA | Field-Programmable Gate Array               |

|------|---------------------------------------------|

| FREE | Fiber Response Extraction Engine            |

| GUI  | Graphic Users Interface                     |

| IC   | Integrated Circuit                          |

| IIR  | Infinite Impulse Response                   |

| LFP  | Local Field Potentials                      |

| LIFO | Last-In-First-Out                           |

| LP   | Linear Phase                                |

| MCU  | Microcontroller Unit                        |

| NA   | Neural Amplifier                            |

| NAP  | Nerve Activation Profile                    |

| NMSE | Normalized Mean-Square Error                |

| NRT  | Neural Response Telemetry                   |

| PC   | Personal Computer                           |

| PCB  | Printed Circuit Board                       |

| PMU  | Power Management Unit                       |

| RF   | Radio Frequency                             |

| RLE  | Run-Length Encoding                         |

| RX   | Receiver                                    |

| SAR  | Stimulus Artifact Rejection                 |

| SoC  | System-on-Chip                              |

| SQNR | Signal-to-Quantization-Noise Ratio          |

| SNR  | Signal-to-Noise Ratio                       |

| SPI  | Serial Peripheral Interface                 |

| SRAM | Static Random-Access Memory                 |

| TX   | Transmitter                                 |

| UART | Universal Asynchronous Receiver-Transmitter |

| USB  | Universal Serial Bus                        |

| VLSI | Very-Large Scale Integration                |

| VNS  | Vagus Nerve Stimulation                     |

| WPT  | Wireless Power Transfer                     |

|      |                                             |

## ABSTRACT

Author:Tsai, Jui-Wei.PhD Institution: Purdue University Degree Received:December 2020 Title: Digital Signal Processing Architecture Design for Closed-Loop Electrical Nerve Stimulation Systems. Committee Chair: Pedro Irazoqui

Electrical nerve stimulation (ENS) is an emerging therapy for many neurological disorders. Compared with conventional one-way stimulations, closed-loop ENS approaches increase the stimulation efficacy and minimize patient's discomfort by constantly adjusting the stimulation parameters according to the feedback biomarkers from patients. Wireless neurostimulation devices capable of both stimulation and telemetry of recorded physiological signals are welcome for closed-loop ENS systems to improve the quality and reduce the costs of treatments, and realtime digital signal processing (DSP) engines processing and extracting features from recorded signals can reduce the data transmission rate and the resulting power consumption of wireless devices. Electrically-evoked compound action potential (ECAP) is an objective measure of nerve activity and has been used as the feedback biomarker in closed-loop ENS systems including neural response telemetry (NRT) systems and a newly proposed autonomous nerve control (ANC) platform. It's desirable to design a DSP engine for real-time processing of ECAP in closed-loop ENS systems.

This thesis focuses on developing the DSP architecture for real-time processing of ECAP, including stimulus artifact rejection (SAR), denoising, and extraction of nerve fiber responses as biomedical features, and its VLSI implementation for optimal hardware costs. The first part presents the DSP architecture for real-time SAR and denoising of ECAP in NRT systems. A bidirectional-filtered coherent averaging (BFCA) method is proposed, which enables the configurable linear-phase filter to be realized hardware efficiently for distortion-free filtering of ECAPs and can be easily combined with the alternating-polarity (AP) stimulation method for SAR. Design techniques including folded-IIR filter and division-free averaging are incorporated to reduce the computation cost. The second part presents the fiber-response extraction engine (FREE), a dedicated DSP engine for nerve activation control in the ANC platform. FREE

employs the DSP architecture of the BFCA method combined with the AP stimulation, and the architecture of computationally efficient peak detection and classification algorithms for fiber response extraction from ECAP. FREE is mapped onto a custom-made and battery-powered wearable wireless device incorporating a low-power FPGA, a Bluetooth transceiver, a stimulation and recording analog front-end and a power-management unit. In comparison with previous software-based signal processing, FREE not only reduces the data rate of wireless devices but also improves the precision of fiber response classification in noisy environments, which contributes to the construction of high-accuracy nerve activation profile in the ANC platform. An application-specific integrated circuit (ASIC) version of FREE is implemented in 180-nm CMOS technology, with total chip area and core power consumption of 19.98 mm<sup>2</sup> and 1.95 mW, respectively.

## **1. INTRODUCTION**

#### 1.1 Background

Nervous system is a complex network spreading through the human body that carries message from brain to various parts of body for regulation of physiological functions, including breath, heart rate, sensation, speech, and even stomach movement during digestion [1]. These physiological functions may be modulated externally by stimulating particular branches of central or peripheral nervous systems, which is also known as neuromodulation [2-4]. Ever since the United States Food & Drug Administration (FDA) approved deep brain stimulation (DBS) as a valid treatment of tremor in 1997 [5], neuromodulation becomes an emerging therapeutic for various neuro- logical diseases. Neuromodulation not only provides another option for patients who're resistant to medication, but also possesses the capacity to target and dose a certain nerve and brain area more precisely, making it a popular treatment alternative to pharmaceutical approach. For instance, DBS utilizes implanted microelectrodes in the brain through which electrical stimulus is delivered to targeted brain area and has been employed in the treatments for Parkinson disease, chronic pain, and other neurological disorders including depression [6, 7]. Spinal cord stimulation (SCS) provides therapy for chronic and intractable pains by intervening in transmission of pain signals along the spinal cords with electrical pulses [8-10]. Applications of neuromodulation to other neurological or psychiatric disorders have been demonstrated and are still being investigated today [11, 12].

Electrical nerve stimulation (ENS) is one neuromodulation technique that involves stimulating nerves with electric current in order to modulate propagation of neural signals along nerve. Ever since the first patient-wearable ENS device was patented in the United States in 1974 [13], ENS has been widely used in clinical therapy for acute and chronic pains, and its application in the treatment for other neurological diseases has also received attention in these decades [14-16]. In human's nervous system, vagus nerve is the longest cranial nerve extending from the brain stem to the colon; it controls important sensory and motor functions, including the visceral sensation of lungs, heart, and digestive tract and muscles in the heart and digestive tract for the regulation (VNS) is one of

the most renowned ENS that was approved by the FDA for epilepsy treatment in 1997 and approved for major depressive disorder treatment in 2005 [19, 20]. Although the mechanism of VNS still requires more elucidation, studies have shown the efficacy of VNS and its mild side effects [21]. VNS has been approved for seizure reduction in Canada and more than 15 countries in Europe [22].

Most commercial neurostimulation systems today are in an open-loop manner, where devices with pre-programmed electrical stimulus is connected to targeted nerve or brain area via implanted microelectrodes, and stimulus parameters are tuned per week or month according to patient's subjective experience in treatment. For example, the VNS device produced by LivaNova and the responsive neurostimulation device produced by NeuroPace are two commercialized open-loop neurostimulators [23]. As the clinical experiences of open-loop neurostimulation accumulate, its problems become more evident, including low stimulation efficiency (either too much or too little dosing), slow reaction to patient's condition that easily causes patient's discomfort, and side effects associated with the therapy, all of which results from lacking objective measurement of how patients react to applied stimulus. A closed-loop neurostimulation system can improve stimulation efficiency and reduce discomforts and side effects on patients by recording physiological signals from patients and constantly adjusting stimulus strength in response to changes in recorded signals [24-26]. Efforts have been made in developing closed-loop neurostimulation systems and devices for various neurological diseases [27, 28]. In closed-loop VNS for epilepsy, stimulation is triggered at the onset of seizure, which can be detected in real-time based on heart rate change, electroencephalogram (EEG) and electrocardiogram (ECG) signals [29-32]. Closed-loop DBS comprises stimulation, sensing of biomarkers such as local field potentials (LFPs), action potentials, electrocorticogram (ECoG), and EEG, and detection of their features [33]. A review of closed-loop DBS systems and devices can be found in [34]. An FDA-approved closed-loop SCS system, the RestoreSensor system (Medtronic, Minneapolis, MN, USA), is also proposed, which automatically adjusts stimulus parameters according to patient's body position sensed by a 3-axis accelerometer [24]. In brief, a closed-loop neurostimulation system must be able to sense physiological signals effectively from patients, precisely locate the biomarkers in recorded signals, and detect change in biomarkers and adjust stimulus strength in response to the change in real-time.

The Autonomous Neural Control (ANC) System

Fig. 1.1 Block diagram of the autonomous nerve control (ANC) system and its applications. [35]

#### **1.2** Autonomous Nerve Control

A nerve comprises mainly bundle of cable-like nerve fibers (also called axon), each of which is a projection of nerve cell (neuron) that transmit electrical signals known as action potentials to different muscles, tissues and organs [36]. According to Gasser [37], nerve fibers can be classified into three types based on their physical features and signal conduction properties - group A (fast, myelinated), group B (slow, myelinated), and group C (slow, unmyelinated). It's believed that the electrical stimulation modulates the activity of nerve fibers and thus sensory and motor functions the nerve fibers map to, which is one explanation for the mechanism of VNS [38]. Based on this theory, if the activation of nerve fibers can be properly controlled, the efficacy of VNS can be greatly improved and the severity of side effects in open-loop VNS can also be minimized. To address this issue, Matthew et al. propose the autonomous nerve control

(ANC) system [35], a responsive closed-loop ENS system that automatically adjusts stimulus strength using measured nerve activation level.

Fig. 1.1 shows the block diagram of ANC system and its applications. In ANC, electrical stimulus is first applied onto a nerve via a stimulation electrode and the electrically-evoked compound action potential (ECAP) on the nerve in response to the stimulus is derived from the neural signals acquired from the recording electrode on the nerve adjacent to the stimulation electrode. ANC then identifies and classifies nerve fiber responses on ECAP waveform in real time. The amplitude responses of targeted nerve fiber together with stimulus parameters are clustered for construction of a patient-specific nerve activation profile (NAP), which predicts how nerve will respond to stimulus with any strength. In closed-loop stimulation, ANC constantly adjusts stimulus parameters according to the derived NAP to control the activation of targeted nerve fiber. ANC is first tested in VNS of rats to demonstrated its capacity to most efficiently control the activation of vagal A, B or C fibers [35] and can be applied to other ENS-based therapeutics for various neurological diseases, e.g. addiction, chronic pain, motor and sensory disorders.

ANC introduces great benefits to both patients and physicians. From patient's side, the period of treatment can be lowered to help patients save their time cost, and quality of treatment is also improved through the minimization of discomfort and side effects. For physicians, ANC provides an objective dosing standard based on the level of nerve activation, and save physicians from the time-consuming process of stimulus parameter tuning. ANC also enable physicians to selectively control the activation of fiber group (A, B or C fiber) and hence the physiological functions that fiber group maps to.

### **1.3** Neural Response Telemetry

It is estimated that around 466 million people worldwide suffer from some degree of hearing loss, 34 million of which are children [39]. Several causes of hearing loss includes genetics, aging, exposure to noise, infections, birth complications and traumas to ear. Hearing loss results in not only inconvenience to patients but also physical, psychological and social problems (e.g. headache, stress, low self-esteem, isolation from community, etc.). Ever since 1957, when

Fig. 1.2 A typical modern cochlear implant system that provides electrical stimuli to auditory nerve [42].

French physician Djourno and his colleagues regained the hearing of two totally deafened patients using electrical stimulation, cochlear implant has been a popular management for hearing loss that provides partial hearing to deafened patients. Today, cochlear implant is one of the most successful neural prosthesis with more than 120,000 people implanted worldwide [40, 41]. The goal of cochlear implant is to replace the normal acoustic hearing process with electrical signals that directly stimulate auditory nerve to restore functional hearing. Fig. 1.2 illustrates a typical modern cochlear implant system [42]. The sound is first sensed with a microphone, processed and encoded into digital signals by speech processor, and transmitted to the implant with the radio frequency (RF) transmitter. On the receiver that is placed under the skin behind the ear, digital signals are received with the antenna, decoded and converted into electric current. A stimulator on the receiver deliver the electric current to auditory nerve via the electrode array implanted in the cochlea, which's then interpreted as sound.

Fig. 1.3 Nueral Response Telemetry (NRT) system in Nucleus CI24M cochlear implant [43].

Due to the difference in the structure of auditory nerve, the performance of cochlear implant can be unpredictable and vary in patients. This problem can be solved via the measurement of nerve function. In 1995, a bidirectional neural response telemetry (NRT) system was incorporated into the Nucleus CI24M cochlear implant to wirelessly monitor the ECAPs in response to the electrical stimuli on auditory nerve [44]. Fig. 1.3 shows the NRT system in Nucleus CI24M [43]. The stimulation parameters are first transmitted from speech processor to implant via RF link. On the implant side, digital signals are received and decoded (Rx Decode), and the electrical stimuli (Stim) corresponding to stimulation parameters are delivered onto auditory nerve via intra-cochlear electrode. Neural signals recorded (Rec) from electrode neighboring to the stimulation one are encoded digitally and transmitted (Tx Encode) back to speech processor and host PC. On the host PC, stimulus artifacts recorded along with neural signals are removed with dedicated algorithms. For example, the mask-probe paradigm proposed by Brown et al. [45] is adopted in Nucleus CI24M cochlear implant [43]. The ECAP response to the electrical stimulus is derived by coherently averaging all responses collected from a stimulation trial containing identical, repeated stimulus pulses. Features on the ECAP waveform are then identified, and stimulus strength is adjusted accordingly. Clinical studies have validated the capacity of NRT to wirelessly measure ECAP responses [43, 46, 47], and it can be equivalently applied to other ENS systems requiring wireless monitoring of ECAP responses on the nerve, including the newly proposed ANC platform.

Fig. 1.4 Cross-section of a nerve and group of nerve fibers (axons) [48].

### 1.4 Electrically-Evoked Compound Action Potential

Fig. 1.4 illustrates the cross-section of a nerve and its nerve fibers (axons) on which action potentials propagate [48]. When electrical stimulus above stimulation threshold (the minimum required stimulation current to elicit an action potential) is applied to a nerve, groups of nerve fibers are activated simultaneously. The summation of all evoked action potentials from activated fibers is called compound action potential. Instead of the action potential of single axon, it is the electrically-evoked compound action potential (ECAP) that can be recorded externally as it propagates along the nerve. Several approaches to interfacing electrodes with nerves for ECAP recording have been referred in [49]. Cuff electrodes, which are designed to fit around nerve without invasion, possess the advantage of maintaining stable and long-term contact with nerve yet exerting little pressure. This makes cuff electrode suitable for implantation and the most popular electrode for nerve stimulation and ECAP recording.

| Type of fiber | Diameter<br>(micrometers) | Conduction velocity<br>(m/sec) | General function                                                                        |

|---------------|---------------------------|--------------------------------|-----------------------------------------------------------------------------------------|

| Α-α           | 13–22                     | 70–120                         | $\alpha\text{-motoneurons},$ muscle spindle primary endings, Golgi tendon organs, touch |

| Α-β           | 8–13                      | 40-70                          | Touch, kinesthesia, muscle spindle secondary endings                                    |

| Α-γ           | 4–8                       | 15–40                          | Touch, pressure, γ-motoneurons                                                          |

| Α-δ           | 1–4                       | 5–15                           | Pain, crude touch, pressure, temperature                                                |

| В             | 1–3                       | 3–14                           | Preganglionic autonomic                                                                 |

| с             | 0.1–1                     | 0.2–2                          | Pain, touch, pressure, temperature, postganglionic autonomic                            |

Fig. 1.5 Classification of nerve fiber types [49].

Fig. 1.6 Classification of nerve fiber responses on ECAP waveforms plotted (A) against time axis and (B) as a function of conduction velocity. The ECAP responses are obtained from the left cervical vagus nerve of rat (*Conduction distance* =  $8.0 \pm 0.5$  mm) [35].

The action potentials of nerve fibers of the same group propagate along a nerve at a constant velocity called conduction velocity, which is proportional to the diameter of fibers [37]. Fig. 1.5 shows the classification of nerve fibers in letter systems established by Gasser [37] based on their conduction velocity [49]. When the ECAPs are recorded on a nerve at a fixed and known conduction distance (i.e., the distance between stimulation and recording electrode on a nerve), the responses of nerve fiber groups with specific conduction velocity form peaks with constant latency on ECAP waveform. As the stimulus strength is increased, the amplitude of peaks grow

Fig. 1.7 The three most commonly used methods for stimulus artifact reduction in ECAP recording: (a) alternating polarity, (b) subthreshold template subtraction, and (c) 2-pulse forward masking paradigm [50].

accordingly owing to more fibers of that group activated. Fig. 1.6 shows the classification of nerve fiber responses on ECAP waveforms recorded at approximately 8-mm conduction distance [35], where the responses of A, B and C fibers, whose conduction velocities are listed in Fig. 1.5, peak separately within a fixed time range on ECAP waveforms. The latency and amplitude of these peaks, which indicate the type of activated nerve fiber and its activation level, respectively, are important biomedical features on ECAP waveforms. It should be kept in mind that a proper conduction distance must be chosen in order to separate the responses of different fiber groups while keep their response amplitudes.

Recording of ECAP on nerves is inevitably accompanied by stimulus artifact and ambient noise [50]. Such stimulus artifact usually contaminates the recorded ECAP signal and, at large enough amplitude, even saturates the recording amplifier, which hinders the amplifier from further recording. Stimulus artifact results mainly from the voltage gradients between the recording electrodes caused by current flowing through the tissues around nerves, and the electromagnetic coupling between stimulation and recording electrode [51], which can be reduced by increasing conduction distance (i.e., placing recording electrode further away from stimulation electrode). For implantable devices (e.g. cochlear implants) in which large enough conduction distance to completely eliminate stimulus artifact is impractical, additional techniques are required to suppress stimulus artifact. Fig. 1.7 illustrates the three most commonly used stimulus artifact

Fig. 1.8 Principle of the coherent avearing (CA) technique [52].

rejection (SAR) techniques in ECAP recording: alternating polarity, subthreshold template subtraction, and two-pulse forward masking paradigm [50]. The alternating polarity method in Fig. 1.7 (a) utilizes two stimulus pulses, a cathodal pulse and an anodal one, whose amplitude and shape are the same and polarity is opposite. On the ground that the polarity of ECAP response does not change with that of stimulus, stimulus artifact is removed by summing the cathodal and anodal responses whose stimulus artifacts have symmetric shape and opposite polarity. In the subtreshold template subtraction method, a pure stimulus artifact is evoked with a subthreshold stimulus pulse (i.e., stimulus below stimulation threshold), which serves as the template. The stimulus artifact is removed by subtracting the evoked response (ECAP plus artifact) with a scaled template. The two-pulse forward masking paradigm utilizes the refractory period of nerve where another stimulation leads to no ECAP [46] and aims to obtain a pure stimulus artifact within this period. As seen in Fig. 1.7 (c), either masker or probe pulse alone elicits both ECAP response and stimulus artifact, whereas the probe pulse within the refractory period that follows after the masker pulse elicits only a stimulus artifact. Artifact is then removed by summing the responses to the abovementioned stimuli (i.e., masker, probe, and masker plus probe).

Coherent averaging (CA), also called ensemble averaging, is a commonly used technique to recover evoked responses from recording noise and other signals that are not correlated to the evoked response and degrade the signal-to-noise ratio (SNR) [52-54]. The CA is based on the

principle that the response to the applied stimulus remains invariant throughout the entire stimulation, which is generally true for stimulation trials lasting for only seconds. Fig. 1.8 illustrates the principle of CA technique [52]. Assume that a series of *N* equidistant and identical stimuli are applied, and  $y_i(t)$  is the output signal after the i-th stimulus that contains response  $r_i(t)$  and noise  $n_i(t)$ , i.e.,  $y_i(t) = r_i(t) + n_i(t)$ . The coherently averaged signal  $\hat{y}(t)$  is the time-aligned averaging of all output signals from N stimuli, namely,  $\hat{y}(t) = \frac{1}{N} \sum_{i=1}^{N} y_i(t) = r(t) + \frac{1}{N} \sum_{i=1}^{N} n_i(t)$ , based on the invariance of response r(t) (i.e.,  $r(t) = r_1(t) = \cdots = r_N(t)$ ). The random noise plus uncorrelated signals  $\frac{1}{N} \sum_{i=1}^{N} n_i(t)$  will then be averaged toward zero. CA is also equivalent to a low-pass finite-impulse-response (FIR) filter. Detailed descriptions and equations can be found in [52].

In short, ECAP is a direct and objective measurement of nerve activity and function and has been adopted as a biomarker in various diagnoses of neural diseases [49, 50] and closed-loop ENS systems such as previously mentioned cochlear implants and ANC platform, in combination with the stimulus-artifact-rejection techniques and CA. Its recording, processing and characterization still present challenges yet deserve more studies for improvement of neurological therapeutics.

#### 1.5 Real-Time Digital Signal Processing for Closed-Loop Neurostimulation

As mentioned in Section 1.1, closed-loop neurostimulation requires continuous monitoring of physiological signals from patients and stimulation of nervous system with stimulus strength constantly adjusted in response to changes in recorded signals, which, until today, is achieved with medical equipments connected to patients via external cables in most clinical treatments. This is problematic, as these equipments and their setup are generally costly in time and money, and most importantly, the transcutaneous cable connection between nervous system and equipments results in not only patient's discomfort but also the risk of injury or inflammation on nerve, which degrades the quality of treatments. The progress in consumer electronics and semiconductor technologies has thus promoted the development of wireless wearable (or implantable) devices for various closed-loop neurostimulation systems in commercial off-the-shelf (COTS) components or application-specific integrated circuits (ASICs) [55-59].

Fig. 1.9 High-level block diagram of a typical wireless wearable (or implantable) device for closed-loop neurostimulation.

Fig. 1.9 illustrates the high-level block diagram of a typical wireless, wearable (or implantable) closed-loop neurostimulation device. Neural signals from central or peripheral nervous system as well as other physiological signals (e.g. EEG, ECG) are recorded and digitized with neural amplifier (NA) and analog-to-digital converter (ADC) in recording analog front-end (AFE), respectively. The wireless module provides a bidirectional communication interface, by which digitized data from ADC are transmitted and user commands are received. Electrical stimuli are generated with the neural stimulator according to the stimulus parameters decoded from received user commands by the control unit, and delivered to targeted nerve or brain areas. The device is powered using battery or wireless power transfer (WPT), and the power supply of each building block is generated with the power management unit.

In order to extend the lifetime of battery and avoid excessive density of WPT that can heat up and damage tissues, power consumption is always the first consideration in designing wireless devices. The Federal Communications Commission restricts the maximum power density of electromagnetic field to  $6 \text{ W/m}^2$  at 915 MHz and  $10 \text{ W/m}^2$  at 2.4 and 5.8 GHz [60]. On the other hand, the resolution of neural or physiological signals recorded from wireless device and the corresponding data transmission rate must be high enough for users to distinguish the change in signals and adjust stimulus parameters accordingly. For instance, a 192-kbps sampling rate per channel (8 bits × 24-kHz sampling frequency) is required for recording of action potential (also called "spike") from a neuron, and the resulting data rate of a 64-channel wireless neural

Fig. 1.10 Illustration of a real-time digital signal processing (DSP) engine on a wireless device.

recording device is as high as 11.71 Mbps [61]. Unfortunately, continuous transmission of recorded raw data at high rate is power-costly for the wireless module dominating the power consumption of wireless device. For example, the power consumption of a Bluetooth transceiver during transmission can reach up to 102.6 mW (57 mA at 1.8-V voltage supply) at 0.72-Mbps data rate [62]. Besides, data transmission at high rate results in high data error rate that also degrades the fidelity of recorded signals. As there's limited room for improvement in the power dissipation of wireless module, a better approach to saving power cost of wireless device in closed-loop systems is to reduce the data rate of device by sending only key information in recorded signals relevant to stimulation adjustment.

A real-time digital signal processing (DSP) engine capable of decoding recorded neural or physiological signals can effectively reduce the data transmission rate of wireless devices, and its role on a wireless device is illustrated in Fig. 1.10. Digitized data from ADC are processed by the DSP engine in real time, and only the detected events or extracted features on recorded signals are transmitted by the wireless module at full resolution, based on which the stimulation intensity is adjusted. Such DSP engine can be implemented in microcontroller, field-programmable gate array (FPGA) or ASIC, on which the DSP algorithms must be computationally efficient in order to minimize the implementation cost. Several examples of digital processor for neural signal processing are given as follows. A spike-sorting DSP chip in 90-nm complementary metal-oxide-semiconductor (CMOS) process is presented in [61] for detection and feature extraction of neuron spikes from 64 channels simultaneously, which has a power dissipation of only 130  $\mu$ W and reduces data rate from 11.71 Mbps to 1.02 Mbps. A neural signal processor is proposed for a 32-channel neural recording system which utilizes discrete wavelet transform (DWT) and run length encoding (RLE) for neural data compression [63]. This processor, implemented in 130-nm

CMOS process, consumes 800  $\mu$ W of power and reduces the maximum data rate of a 32-channel neural implant to 1 Mbps. A general-purpose wireless brain-machine-brain interface (BMBI) is reported in [64], which incorporates a microcontroller-based neural signal processor for digital filtering, feature extraction, spike detection, and compressed sensing. In [65], real-time algorithms for decoding of electroneurogram (ENG) are implemented onto an off-the-shelf DSP processor, which consist of denoising, spike detection, spike sorting by template matching, and classification. For optimal performance and lower area and power cost, very-large-scale integration (VLSI) architecture for real-time DSP and its implementation in either FPGA or ASIC are usually preferred.

#### 1.6 Motivation

There has been significant progress in development of wireless wearable (or implantable) device and real-time DSP algorithm and architecture for various closed-loop neurostimulation systems. Surprisingly, today's closed-loop ENS systems that measure ECAP as feedback biomarker, such as the NRT system in cochlear implant and the newly proposed ANC platform [35], still rely on the offline processing of continuously recorded and transmitted neural data on software. For instance, the Nucleus CI24M cochlear implant incorporates a custom NRT software for postprocessing of received neural data [43], including the SAR and CA techniques for recovery of ECAP responses described in previous sections and feature extraction from ECAP signals, and similar signal-processing steps are implemented on MATLAB software in ANC. The required data rate for transmission of neural data (e.g. 800-kbps input data rate in ANC) will be too high for wireless devices to work with these closed-loop ENS systems while satisfy the low power demand. It's favorable to have a DSP engine for ECAP processing that comprises SAR, denoising, and extraction of features such as fiber responses described in Section 1.4, to reduce the data rate of wireless device in these systems. A VLSI architecture of such DSP engine is especially desirable for performance and hardware cost optimization.

Although CA technique has been widely adopted in many ECAP-based closed-loop ENS platforms for noise removal, its efficacy is strongly dependent on the number of averaging (i.e., the number of stimuli). A large number of stimuli and hence long stimulus train duration is needed to boost the filtering capacity of CA, which also adds power consumption to wireless

device due to increase in the length of data recording and transmission time. Another deficiency of CA is its limited ability to remove periodic noises, such as electromagnetic interferences (e.g. 60-Hz power line) and baseline wanders (caused by patient's movement) which are prevalent in neural recording, especially when periodic noises are time-locked to stimulus pulses. Such noises, if not properly eliminated, will introduce inaccuracy onto biomedical features of ECAP (fiber responses), which adversely influences the tuning of stimulus parameters in closed-loop stimulation. Digital filters remove periodic noises more effectively and can be efficiently implemented in real-time DSP in finite impulse response (FIR) or infinite impulse response (IIR) structures [66]. Unfortunately, most digital filters, especially IIR filters which are more computationally efficient, have nonlinear phase response; This causes phase-frequency distortion of filtered signals (i.e., all frequency components of input signal shifted in time unequally) which results in the deformation of ECAP waveform and its features. It's possible to achieve zero-phase filtering and hence avoid distortion of ECAP waveform by applying a filter both forward and backward in time, which's also known as forward-backward filtering [67]. However, this technique requires a time-reversal operation on the entire input data stream (i.e., all neural data recorded during the stimulus train) and are still performed with offline software processing today. A distortion-free and computationally efficient filtering technique for more effective periodic noises removal and its VLSI architecture is essential to realize a real-time DSP engine for ECAP processing.