# ADVANCED LOW-COST ELECTRO-MAGNETIC AND MACHINE LEARNING SIDE-CHANNEL ATTACKS

A Thesis

Submitted to the Faculty

of

Purdue University

by

Josef A. Danial

In Partial Fulfillment of the

Requirements for the Degree

of

## MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

December 2020

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF THESIS APPROVAL

Dr. Shreyas Sen, Chair

School of Electrical and Computer Engineering

Dr. Avinash Kak School of Electrical and Computer Engineering Dr. Irith Pomeranz School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of Electrical and Computer Engineering

### ACKNOWLEDGMENTS

First, I would like to thank my advisor Shreyas Sen for his insight and guidance in and out of academics.

I would also like to specifically thank Debayan Das for his constant support, encouragement, and willingness to help with any problem.

Additionally, I would like to thank all the members of the SPARC Lab for their help over the past two years.

Finally, I would like to thank my family for their support throughout my entire education.

## TABLE OF CONTENTS

|    |      |         |                                              | Pa  | ge   |

|----|------|---------|----------------------------------------------|-----|------|

| LI | ST O | F TAB   | LES                                          | • ` | vii  |

| LI | ST O | F FIGU  | JRES                                         | . v | riii |

| AI | BBRE | VIATI   | ONS                                          | . x | iii  |

| AI | BSTR | ACT     |                                              | . x | civ  |

| 1  | INTI | RODU    | CTION                                        |     | 1    |

|    | 1.1  | SCNIF   | FER                                          |     | 3    |

|    | 1.2  | Cross   | Device EM-ML SCA                             |     | 3    |

|    | 1.3  | Additi  | onal Side-Channel Attacks                    |     | 4    |

| 2  | SCNI | FFER: L | OW-COST, AUTOMATED, EFFICIENT ELECTROMAGNETI | C   |      |

|    | SIDE | E-CHAI  | NEL SNIFFING                                 | •   | 5    |

|    | 2.1  | Introd  | uction                                       |     | 5    |

|    |      | 2.1.1   | Motivation                                   |     | 6    |

|    |      | 2.1.2   | Contribution                                 |     | 8    |

|    |      | 2.1.3   | Chapter Organization                         |     | 9    |

|    | 2.2  | Backg   | round and Related Work                       |     | 10   |

|    | 2.3  | SCNIF   | FER: Low Cost Automated EM Scanning          |     | 13   |

|    |      | 2.3.1   | Low Cost EM Scanning Setup                   |     | 13   |

|    |      | 2.3.2   | Automated EM Scanning                        |     | 18   |

|    | 2.4  | Signal  | Leakage Measurement using SCNIFFER           |     | 18   |

|    |      | 2.4.1   | Signal Amplitude for Leakage Measurement     |     | 19   |

|    |      | 2.4.2   | TVLA for Leakage Measurement                 |     | 21   |

|    |      | 2.4.3   | SNR for Leakage Measurement                  |     | 22   |

|    |      | 2.4.4   | Correlation among Amplitude, TVLA, SNR, MTD  | •   | 22   |

|    | 2.5  | Greed   | y Gradient-Search Heuristic                  |     | 23   |

|   |     | 2.5.1   | Algorithm Description                                                        | 23 |

|---|-----|---------|------------------------------------------------------------------------------|----|

|   |     | 2.5.2   | Algorithm Performance                                                        | 24 |

|   | 2.6 | Result  | 8                                                                            | 29 |

|   |     | 2.6.1   | TVLA Based SCNIFFER                                                          | 29 |

|   |     | 2.6.2   | SNR Based SCNIFFER                                                           | 30 |

|   |     | 2.6.3   | Number of Traces Needed For SCNIFFER Attacks                                 | 31 |

|   |     | 2.6.4   | Effect of Cryptographic Algorithm on Convergence                             | 32 |

|   |     | 2.6.5   | Effect of Architecture on Convergence                                        | 35 |

|   |     | 2.6.6   | Effect of Masking on Convergence                                             | 36 |

|   | 2.7 | Conclu  | usions                                                                       | 37 |

| 3 |     |         | CROSS-DEVICE DEEP LEARNING SIDE-CHANNEL AT-<br>NG ELECTROMAGNETIC SIGNATURES | 38 |

|   | 3.1 | INTR    | ODUCTION                                                                     | 38 |

|   |     | 3.1.1   | Motivation                                                                   | 38 |

|   |     | 3.1.2   | Contribution                                                                 | 40 |

|   | 3.2 | BACK    | GROUND & RELATED WORK                                                        | 41 |

|   |     | 3.2.1   | EM Side Channel Attacks                                                      | 41 |

|   |     | 3.2.2   | ML-SCA Attacks                                                               | 42 |

|   | 3.3 | EM-X    | -DL SCA ATTACK                                                               | 42 |

|   |     | 3.3.1   | DNN Architecture & Training                                                  | 43 |

|   |     | 3.3.2   | Single-Trace Attack with Pre-Processing                                      | 46 |

|   | 3.4 | EM-X    | -DL SCA: EFFICIENT SELECTION OF TRAINING DEVICES                             | 47 |

|   |     | 3.4.1   | Cross-Device Accuracy Variance                                               | 48 |

|   |     | 3.4.2   | Bivariate POI Based Device Selection                                         | 48 |

|   | 3.5 | EM L    | EAKAGE ASSESSMENT & ATTACK                                                   | 49 |

|   | 3.6 | REMA    | ARKS & CONCLUSION                                                            | 51 |

| 4 | ADI | DITION  | AL SIDE-CHANNEL ATTACKS                                                      | 57 |

|   | 4.1 | Efficie | nt EM Attack: Power to EM Mapping                                            | 57 |

|   |     |         |                                                                              |    |

# Page

v

## Page

vi

|   |      | 4.1.1  | Introduction                                                                                  | 57 |

|---|------|--------|-----------------------------------------------------------------------------------------------|----|

|   |      | 4.1.2  | Background                                                                                    | 57 |

|   |      | 4.1.3  | Transfer Function Approximation Methods                                                       | 57 |

|   |      | 4.1.4  | Results                                                                                       | 58 |

|   |      | 4.1.5  | Conclusion                                                                                    | 60 |

|   | 4.2  | Side-C | Channel Resilience with High Level Synthesis                                                  | 61 |

|   |      | 4.2.1  | Introduction                                                                                  | 61 |

|   |      | 4.2.2  | Background                                                                                    | 62 |

|   |      | 4.2.3  | Initial Leakage Assessment                                                                    | 63 |

|   |      | 4.2.4  | White-Box Analysis                                                                            | 65 |

|   |      | 4.2.5  | Dynamic Implementation                                                                        | 66 |

|   |      | 4.2.6  | Conclusion                                                                                    | 68 |

|   | 4.3  |        | Channel Analysis on Future ML Systems: Neural Cryptography<br>Generative Adversarial Networks | 69 |

|   |      | 4.3.1  | Introduction                                                                                  | 69 |

|   |      | 4.3.2  | Background and Related Works                                                                  | 69 |

|   |      | 4.3.3  | GAN Cryptography Security Analysis                                                            | 69 |

|   |      | 4.3.4  | Real-World Limitations                                                                        | 72 |

|   |      | 4.3.5  | Conclusion                                                                                    | 73 |

| 5 | CON  | ICLUS  | ION                                                                                           | 75 |

| R | EFER | ENCE   | S                                                                                             | 76 |

| - |      |        |                                                                                               | -  |

### LIST OF TABLES

| Tabl | le                                                                                                                                                                                                                                                                                             | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1  | Comparison with previous works. SCNIFFER is significantly lower cost compared to previous works, and additionally is the only system designed to maximize the effectiveness of an attack, as other systems seek only the location of most informative leakage.                                 |      |

| 2.2  | Summary of the main components of the SCNIFFER system, their costs, performance, and a comparison to Riscure's EM Probe Station.                                                                                                                                                               |      |

| 2.3  | Comparison of different leakage measures used with SCNIFFER, as well as results of a full exhaustive search. The total traces includes the traces needed for the initial search, gradient search, and CEMA. The exhaustive search total traces includes a 1000 trace CEMA at all 100 locations |      |

| 3.1  | Literature Review for Profiled-Attack Scenario                                                                                                                                                                                                                                                 | . 41 |

| 3.2  | Cross-Device attack Performance of Deep Learning-based Methods for dif-<br>ferent Pre-Processing Techniques                                                                                                                                                                                    |      |

| 4.1  | Summary of AES-128 implementations produced through HLS. HLS op-<br>tions have a large effect on both the size and speed of an implementation as<br>well as the side channel leakage. The dynamic implementation combines<br>several variants, leading to the much higher resource use         |      |

### LIST OF FIGURES

| Figu | ıre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page   |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

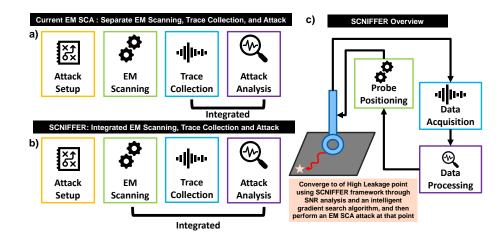

| 2.1  | (a, b) Comparison between existing EM SCA systems and SCNIFFER.<br>While current frameworks have integrated trace collection and attack and<br>analysis, SCNIFFER integrates EM scanning as well. (c) High level overview<br>of proposed SCNIFFER framework. SCNIFFER analyzes EM leakage and uses<br>a gradient descent algorithm to locate points of high informative leakage<br>at which the EM SCA attack should be performed                                                                   | -<br>- |

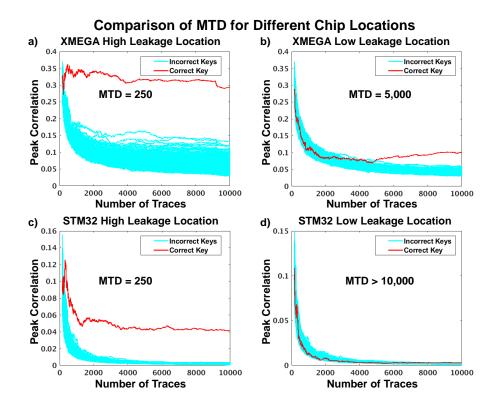

| 2.2  | The difference in MTD between a CEMA attack at a point of high leakage<br>vs. at a point of low leakage for both an 8-bit XMEGA microcontroller<br>(a, b) and a 32-bit STM32F3 microcontroller (c, d). At a location of high<br>leakage, the correct key separates in 250 traces for both microcontrollers,<br>while a low leakage location requires $> 20 \times$ more traces on the XMEGA.<br>At a low leakage location on the STM32F3, the key does not separate at<br>all within 10,000 traces. | •<br>• |

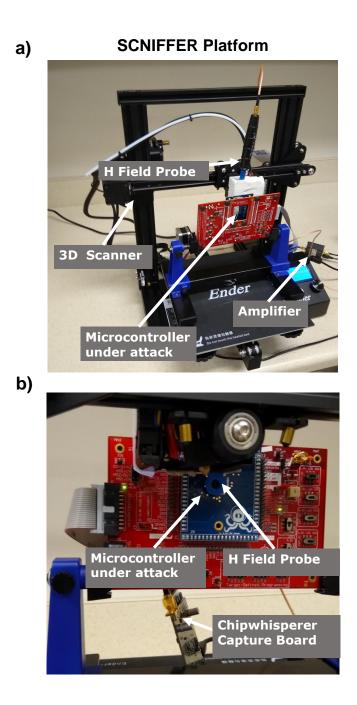

| 2.3  | <ul><li>(a) The complete EM Scanning and trace capture set-up system, including the 3-D printer, Chipwhisperer system, EM probe, amplifier, and victim.</li><li>(b) Close-up of scanner, showing probe and victim board</li></ul>                                                                                                                                                                                                                                                                   |        |

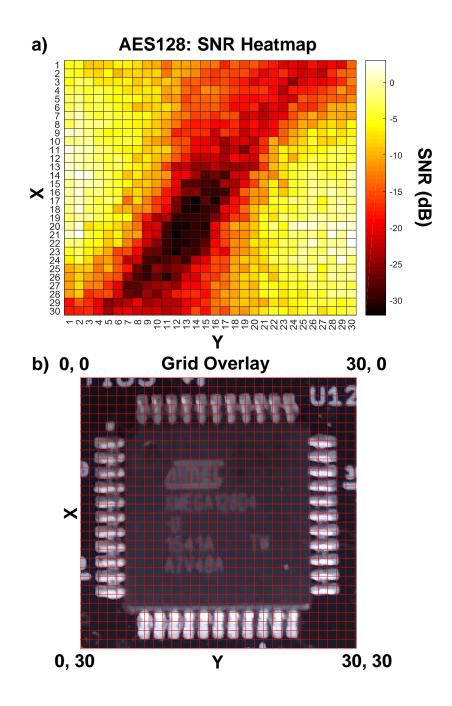

| 2.4  | (a) Heatmap of the SNR values obtained by performing a full $30 \times 30$ scan<br>of the 8-bit target microcontroller. (b) This shows the grid divisions where<br>leakage measurements were performed. 1000 traces were used to compute<br>the SNR values at each point. The part of the target microcontroller board<br>which leak the most information can be observed                                                                                                                           | ;      |

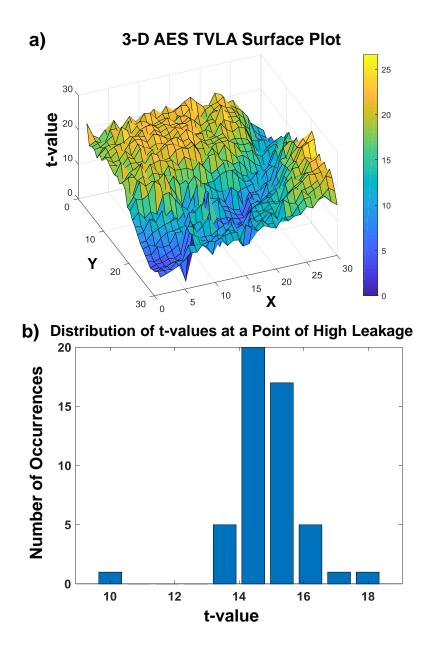

| 2.5  | (a) TVLA surface plot. Again, the surface is not smooth or monotonic, as there are many local minima and maxima, as in Figure 2.6(a). (b) Histogram of TVLA measurements at a single point. 50 TVLA measurements were made at a point of high leakage, each done as in (a), using 400 traces each. Given the distribution much wider seen in (b), the increased roughness of the surface in (a) can be explained.                                                                                   |        |

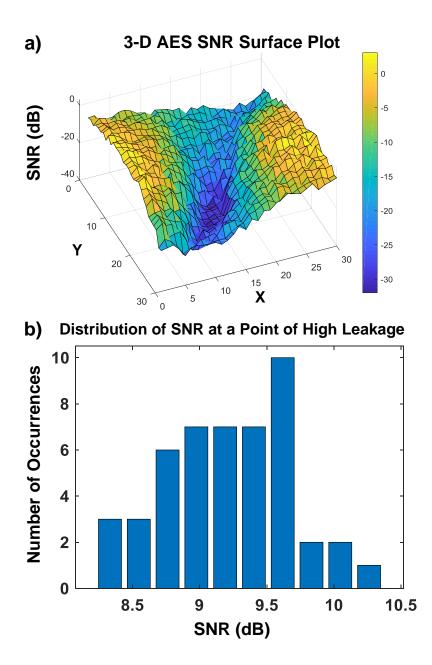

| 2.6  | (a) SNR surface plot of the same scan as Figure 2.4(a). Here it can be clearly seen that the surface is not smooth or monotonic, as there are many local minima and maxima. (b) Histogram of SNR measurements at a single point. 50 SNR measurements were made at 1 point. This distribution can explain some of the roughness of the surface seen in (a).                                                                                                                                          | :      |

| ix |  |

|----|--|

|    |  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

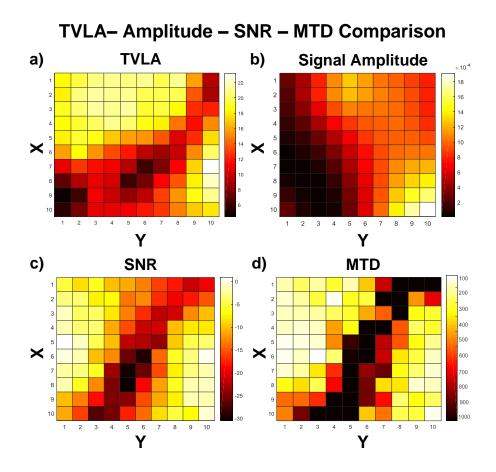

| 2.7  | $10 \times 10$ heatmap of (a) TVLA values (b) signal amplitudes (c) SNR values<br>and (d) MTDs. From these plots TVLA and SNR appear to correlate to<br>MTD much better than the signal amplitude. While amplitude is easy<br>to measure, it is clear that high amplitude of leakage does not necessarily<br>correspond to high information leakage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 21  |

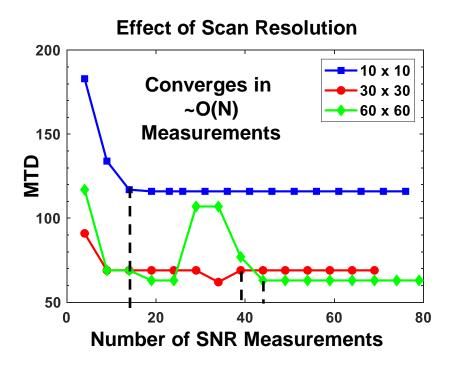

| 2.8  | Leakage vs. number of SNR measurements for varying grid scales. Each SNR measurement is computed using 1000 traces collected at the measured location. The data for the $30 \times 30$ grid was the same as in Figures 2.4 and 2.6(a). The full $60 \times 60$ and $10 \times 10$ grids were also collected, allowing the performance of the algorithm to be seen at various degrees of measurement resolution. Through these results, it can be seen that even as the size of the search space increases by $N^2$ , the time to converge increases by only $N^2$ .                                                                                                                                                                                                                                                                                                             | V. 26 |

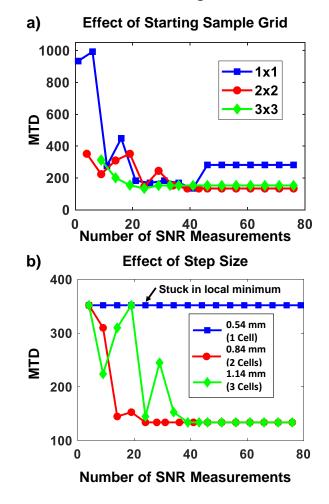

| 2.9  | (a) MTD vs number of SNR measurements performed for varying the initial sample grid size parameter. Note that the $2 \times 2$ and $3 \times 3$ grids locate the point of high leakage within 40 SNR measurements, while a single initial sample point results in a higher MTD, and after 45 such measurements. For all initial sample grid sizes, a step size of 1.14mm was used. (b) This demonstrates the effect of step size on performance. A step size too small can result in the algorithm getting stuck in a local maximum, and in this case as the step size increased, convergence sped up, however, for much larger step sizes, it is possible to overshoot the location of highest leakage, resulting in slower, less smooth convergence. For all step sizes, a $2 \times 2$ initial sample grid was used. Both (a) and (b) used a $30 \times 30$ scan resolution. | . 27  |

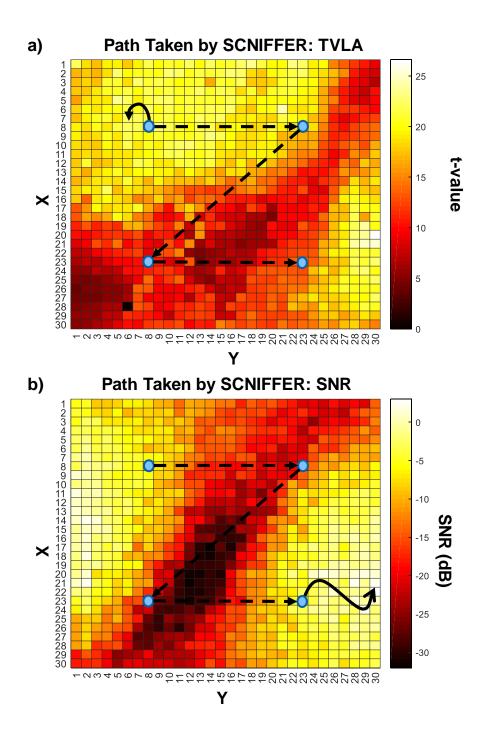

| 2.10 | Heatmaps for AES running on the 8-bit microcontroller, with the path taken by SCNIFFER shown for TVLA in (a), and SNR in (b). The same search algorithm parameters were used in all cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 28  |

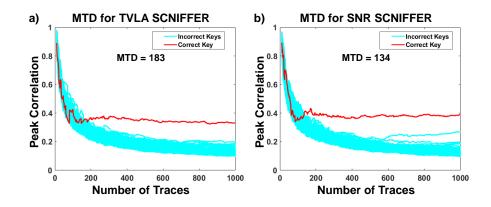

| 2.11 | MTD plots at locations found by SCNIFFER using TVLA as a leakage measure (a), and SNR as a leakage measure (b). While the MTD is not the minimum, it is fairly close to the minimum for both measures, with SNR having a slightly lower MTD than TVLA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 29  |

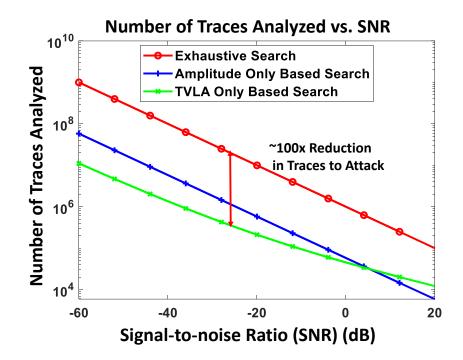

| 2.12 | Number of traces required for TVLA and SNR based SCNIFFER compared to exhaustive search vs. SNR for the case of a $10 \times 10$ scan. The $\sim 100 \times$ reduction is due to the fact that an exhaustive search must perform a CEMA at each location, while SCNIFFER only visits N locations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 31  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

Figure

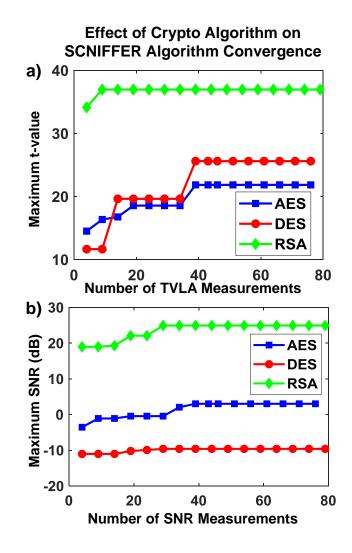

| 2.13 | (a) Max t-value vs. number of TVLA tests performed for all cryptographic<br>algorithms (AES, DES, RSA), showing the scanning algorithm performs<br>well, finding the point of max leakage within 40 TVLA tests in all cases,<br>with a grid size of $30 \times 30$ . The initial sampling grid was $2 \times 2$ and the<br>step size was 0.84mm. Note that for RSA, one of the initial samples is<br>already close to the maximum, and this maximum is found in just one<br>step. For AES and DES, whose leakage patterns are less smooth, and<br>have smaller areas of high leakage, the time to converge is higher. (b)<br>Max SNR vs. number of SNR measurements for all algorithms (AES,<br>DES, RSA). The search algorithm again performs well, converging in all<br>cases in about $O(N)$ measurements ( $N = 30$ in this case) |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

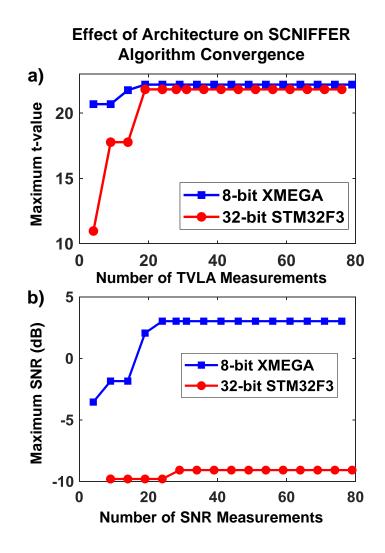

| 2.14 | (a) Max t-value vs. number of measurements for both the 8-bit XMEGA microcontroller and the 32-bit STM32F3 microcontroller. The algorithm converges within $O(N)$ measurements, where $N = 30$ in both cases. the algorithm parameters used are the same as in Figure 2.13. (b) Max SNR vs. number of measurements for both microcontroller architectures, again showing convergence in $O(N)$ measurements. The parameters used are the same as those in part (a)                                                                                                                                                                                                                                                                                                                                                                    |

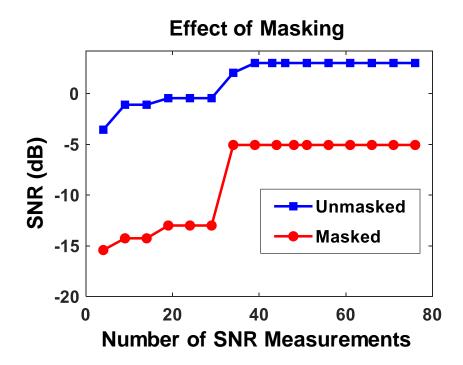

| 2.15 | Max SNR vs. number of SNR measurements for the unmasked and a masked implementation of AES on the 8-bit microcontroller. The algorithm converges within $O(N)$ measurements, where $N = 30$ in both cases. The algorithm parameters used are the same as in Figure 2.13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

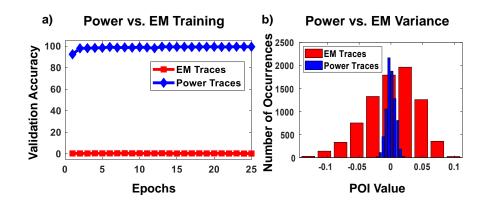

| 3.1  | (a) DNN training with raw power and EM traces. The model learns quickly<br>from power, but is unable to learn from raw EM traces. (b) The variance<br>of a point of interest (time sample 103) for both power and EM traces,<br>demonstrating significantly lower SNR of the EM traces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

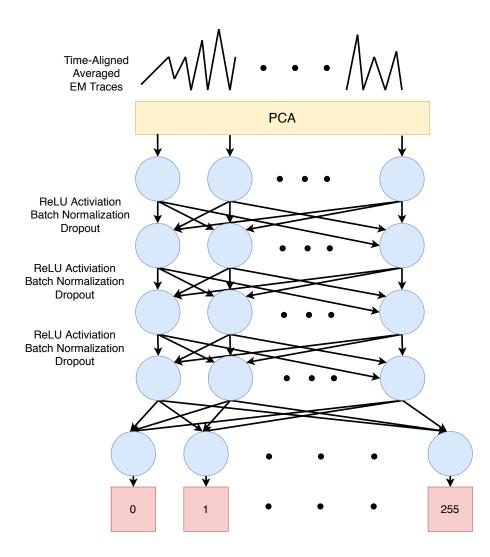

| 3.2  | Architecture of the proposed DNN. The network contains 3 dense layers, following each dense layer is a ReLU activation function, batch normal-<br>ization, and finally a dropout layer. The final output layer provides the output class predictions - the key byte, and thus is size 256, and uses a softmax activation function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

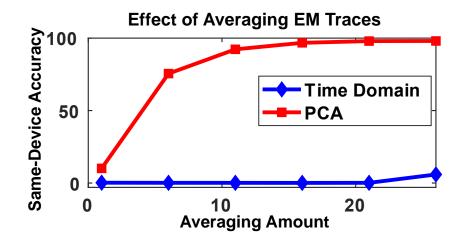

| 3.3  | Effect of averaging on the test accuracy of the 256-class DNN when using<br>raw traces and PCA-transformed traces. Increasing averaging hardly al-<br>lows the DNN to learn from the time-domain EM traces. With PCA used<br>as a pre-processing step, averaging upto $20 \times$ smoothly increases the test<br>accuracy to > 99% for the same device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Page

| •  |  |

|----|--|

| X1 |  |

| re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Pag                                                                                                                                                                                                                                                                                                                                                                                          | ge                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

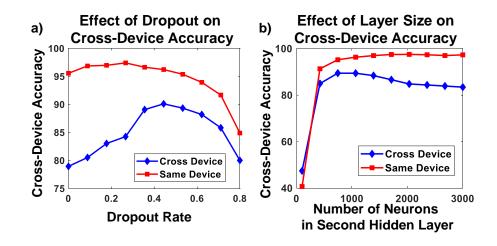

| Effect of hyperparameters on both same- and cross-device test accuracy for the PCA-DNN model. (a) Dropout between the first and second hidden layers helps prevent overfitting, maximizing cross-device accuracy at a dropout rate of 0.45. (b) Layer size also demonstrates a similar trend, and reaches maximum cross-device accuracy at $\sim 1000$ for the second hidden layer.                                                                                                                                                                                                                                             | . 4                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                                                                                                                                                                                                                                                                                                                                           |

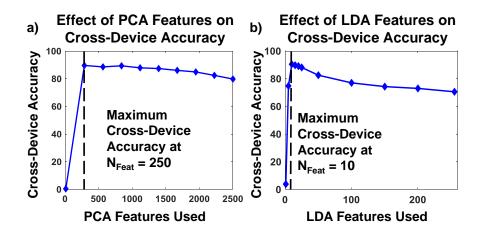

| PCA and LDA reach their respective peaks (250 and 10) with relatively few features compared to the size of the original traces (3000). As LDA features are chosen to maximize the class separation, while PCA maximizes variance, LDA is a more efficient technique for this higher dimensional data as it can train the DNN significantly faster.                                                                                                                                                                                                                                                                              | . 4                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                                                                                                                                                                                                                                                                                                                                           |

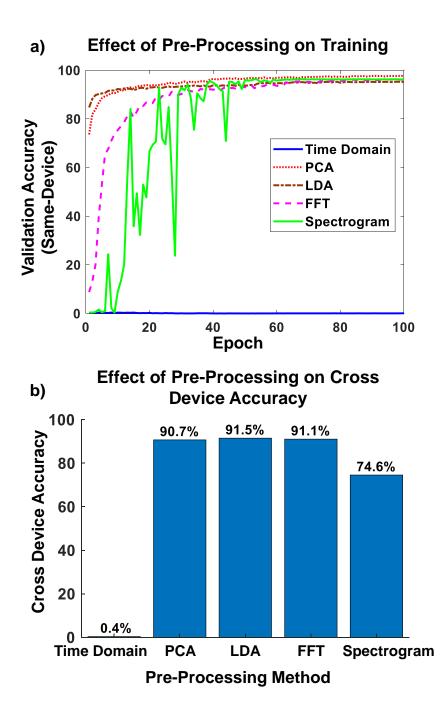

| Effect of the different pre-processing techniques on (a) the DNN training accuracy, (b) the cross-device attack (EM-X-DL) accuracy. While all the pre-processing techniques result in high validation (same-device) accuracy, PCA, LDA, FFT result in > 90% cross-device accuracy, while spectrogram yields 74.6% cross-device accuracy.                                                                                                                                                                                                                                                                                        | . e                                                                                                                                                                                                                                                                                                                                                                                          | 52                                                                                                                                                                                                                                                                                                                                                                                           |

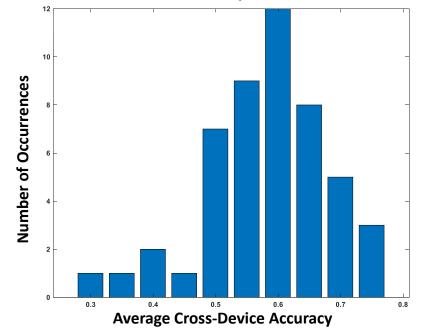

| Distribution of cross-device accuracy of the 256-class PCA-DNN trained on random subsets of 6 devices. The mean accuracy is 60%, however, the depending on the subset, it can vary significantly between $30 - 75\%$ , highlighting the need for an intelligent selection of the training devices.                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                                                                                                                                                                                                                                                                                                                                                           |

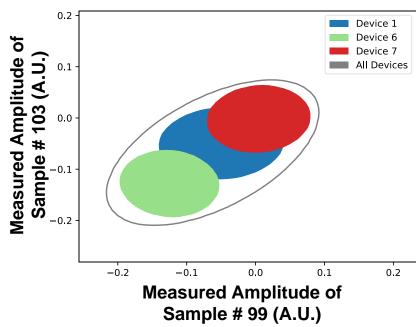

| Bivariate analysis of the first 3 devices chosen by Algorithm 2. The top three chosen devices already span a large portion of the distribution containing all devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                              | 54                                                                                                                                                                                                                                                                                                                                                                                           |

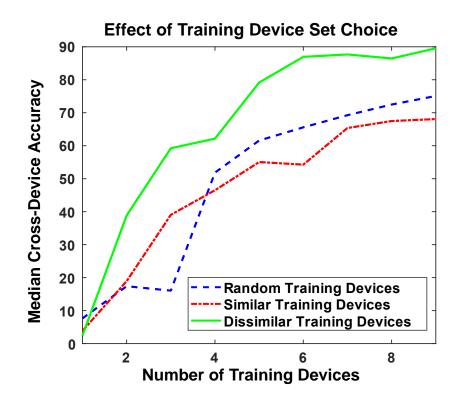

| Depending on the choice of devices used for training, cross-device accuracy varies significantly. Choosing "dissimilar" devices by algorithm 2 gives high accuracy, while choosing "similar" training devices yields a low cross-device accuracy. Randomly selecting devices shows slightly higher test accuracies than choosing "similar" devices.                                                                                                                                                                                                                                                                             | ۲.<br>ر                                                                                                                                                                                                                                                                                                                                                                                      | 55                                                                                                                                                                                                                                                                                                                                                                                           |

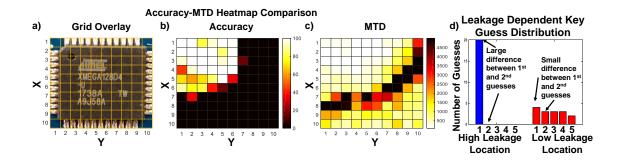

| (a) $10 \times 10$ virtual grid overlay of the chip. (b, c) Comparison of EM-X-DL model accuracy to CEMA-MTD. The ML model is able to predict with high accuracy in the region of the chip with low MTD values, however, when the MTD rises above 250, the model is unable to correctly predict the key values. (d) EM-X-DL model predictions on 20 samples from a high leakage location (1,1), and a low leakage location (9, 4) on a test device. At a location with high leakage, the frequency of the highest predicted key byte value is distinguishable from the next, demonstrating the high confidence of the attacker. | ۲.                                                                                                                                                                                                                                                                                                                                                                                           | 56                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Effect of hyperparameters on both same- and cross-device test accuracy for<br>the PCA-DNN model. (a) Dropout between the first and second hidden<br>layers helps prevent overfitting, maximizing cross-device accuracy at a<br>dropout rate of 0.45. (b) Layer size also demonstrates a similar trend, and<br>reaches maximum cross-device accuracy at ~ 1000 for the second hidden<br>layer | Effect of hyperparameters on both same- and cross-device test accuracy for<br>the PCA-DNN model. (a) Dropout between the first and second hidden<br>layers helps prevent overfitting, maximizing cross-device accuracy at a<br>dropout rate of 0.45. (b) Layer size also demonstrates a similar trend, and<br>reaches maximum cross-device accuracy at ~ 1000 for the second hidden<br>layer |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                           | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

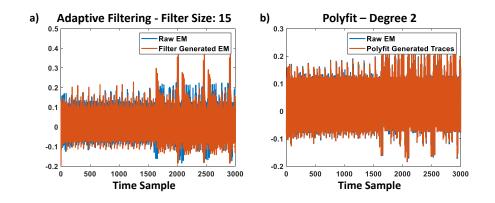

| 4.1  | (a) True EM trace compared to a trace generated with adaptive filtering, with a filter size of 15. (b) True EM trace compared to a trace generated with polynomial fitting and a degree of 2.                                                                                                                                                                                | . 59 |

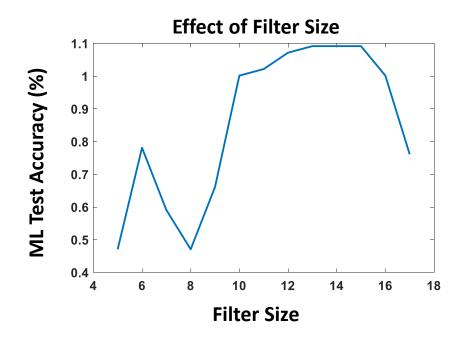

| 4.2  | At small filter sizes, the generated traces are unable to be classified by the ML model. As filter size increases, the accuracy begins to rise slightly above the level of a random guess, to a maximum of $1.1\%$ .                                                                                                                                                         | . 60 |

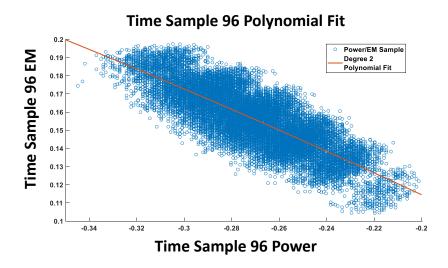

| 4.3  | Power vs. EM for time sample 96 and the polynomial fit for this time sample. While not perfect, polyfit results in lower MSE and better SCA-ML performance.                                                                                                                                                                                                                  | . 61 |

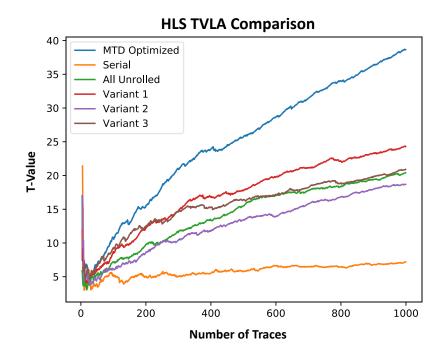

| 4.4  | Incremental TVLA for all variants investigated. The initial serial imple-<br>mentation shows low leakage under TVLA, and the dynamic implementa-<br>tion shows high leakage, however TVLA does not necessarily correlate to<br>the true security of an implementation                                                                                                        | . 65 |

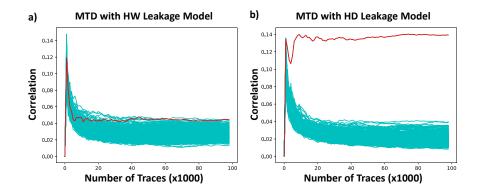

| 4.5  | (a) CPA using a HW leakage model. The key is recoverd after 94,000 traces. (b) CPA using a HD model. The key is now recovered in only 2,000 traces.                                                                                                                                                                                                                          | . 67 |

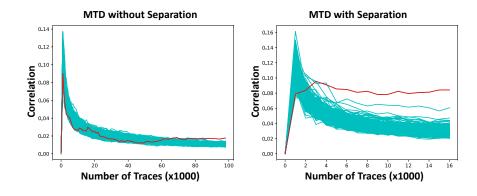

| 4.6  | (a) CPA performed on the dynamic implementation of AES, with the attack succeeding at 81,000 traces. (b) After separating traces by implementation, CPA succeeds after 5,000 traces.                                                                                                                                                                                         | . 68 |

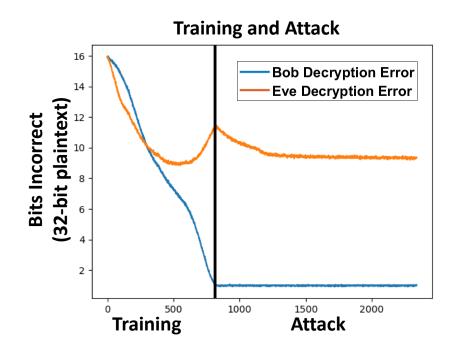

| 4.7  | During the training phase, both Bob and Eve are able to reduce decryption<br>error at first, then Alice and Bob begin to use the secret key, and Eve's<br>decryption error increases. Once training ends, the attack phase begins.<br>Eve is able to further reduce the decryption error during the attack, but<br>not to the level of Bob                                   | . 71 |

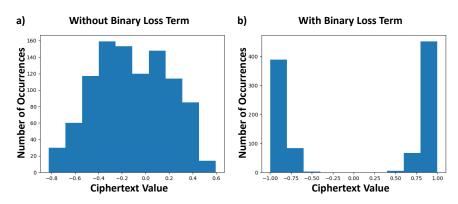

| 4.8  | (a) Distribution of ciphertext values for 1000 encryptions when using the standard loss function and hard tanh activation functions. (b) Distribution of ciphertext values for 1000 encryptions with binary loss term and normal tanh activation functions. While ciphertexts appear more binary, information is stored in small variations - not -1 to +1 changes. $\ldots$ | . 73 |

### ABBREVIATIONS

- SCA side-channel analysis

- ML machine learning

- MSE Mean Square Error

- TVLA test vector leakage assessment

- MTD Minimum Traces to Disclosure

- CPA Correlation Power Analysis

- CEMA Correlation EM Analysis

- DPA Differential Power Analysis

- DEMA Differential EM Analysis

- DNN Deep Neural Network

- CNN Convolutional Neural Network

- SNR signal to noise ratio

- AES advanced encryption standard

- DES Data Encryption Standard

- RSA Rivest–Shamir–Adleman

- PCA Principle Component analysis

- POI Point of Interest

- LDA Linear Discriminant Analysis

- FFT Fast Fourier Transform

- HW Hamming Weight

- HD Hamming Distance

- HLS High Level Synthesis

### ABSTRACT

Danial, Josef A. MS, Purdue University, December 2020. Advanced Low-Cost Electro-Magnetic and Machine Learning Side-Channel Attacks. Major Professor: Shreyas Sen.

Side-channel analysis (SCA) is a prominent tool to break mathematically secure cryptographic engines, especially on resource-constrained devices. SCA attacks utilize physical leakage vectors like the power consumption, electromagnetic (EM) radiation, timing, cache hits/misses, that reduce the complexity of determining a secret key drastically, going from  $2^{128}$  for brute force attacks to  $2^{12}$  for SCA in the case of AES-128. Additionally, EM SCA attacks can be performed non-invasively without any modifications to the target under attack, unlike power SCA. To develop defenses against EM SCA, designers must evaluate the cryptographic implementations against the most powerful side-channel attacks. In this work, systems and techniques that improve EM side-channel analysis have been explored, making it lower-cost and more accessible to the research community to develop better countermeasures against such attacks. The first chapter of this thesis presents SCNIFFER, a platform to perform efficient end-to-end EM SCA attacks. SCNIFFER introduces leakage localization - an often-overlooked step in EM attacks – into the loop of an attack. Following SCNIFFER, the second chapter presents a practical machine learning (ML) based EM SCA attack on AES-128. This attack addresses issues dealing with low signal-to-noise ratio (SNR) EM measurements, proposing training and pre-processing techniques to perform an efficient profiling attack. In the final chapter, methods for mapping from power to EM measurements, are analyzed, which can enable training a ML model with much lower number of encryption traces. Additionally, SCA evaluation of highlevel synthesis (HLS) based cryptographic algorithms is performed, along with the study of futuristic neural encryption techniques.

### 1. INTRODUCTION

Side-channel analysis allows adversaries to recover secret information using far less processing than brute force attacks by taking advantage of additional information from a side-channel such as execution time, power consumption, electromagnetic emissions, or even sound. These side channels give attackers information based on the implementation of a cryptographic algorithm, and can be used to efficiently recover secrets even if the cryptographic algorithm itself is secure. This thesis focuses on attacks using the electromagnetic side-channel, and the closely related power sidechannel. In order to create effective defenses against side-channel attacks, designers must subject cryptographic implementations to the most powerful side-channel attacks, thus by improving side-channel attacks, more effective countermeasures can be developed, and the security of cryptography implementations more accurately estimated.

Of critical importance to the practicality of EM and power based side-channel attacks is the signal to noise ratio (SNR) of the EM/power measurements. In the study of side-channel analysis, SNR has a particular meaning:  $\mathbf{SNR} = \frac{VAR[Q]}{VAR[N]}$ , where Q is the targeted side-channel leakage, and N is the noise. Noise - in the side-channel sense - has two main components: First, the traditional measurement noise due to thermal effects and quantization errors during measurement, and second, algorithmic noise. Algorithmic noise is composed of any variation in the side channel signal originating from the targeted device, but not caused by the specific operation being analyzed. This could be due to other processes executing concurrently, or even a part of the algorithm under analysis that does not provide useful information.

Measurement noise can be addressed relatively easily by averaging, amplification, or the use of high precision measurement equipment. Algorithmic noise on the other hand does not benefit from amplification or high precision measurements, as the source of the noise is the same as the information leakage. Averaging can help reduce some types of algorithmic noise, but not always. This leads to one of the main benefits of EM measurements over power, that being the ability to selectively collect leakage from a particular section of a cryptographic implementation. By measuring EM leakage from a specific location, algorithmic noise can be reduced, as the signal recorded is related to only the informative leakage, and other sources of algorithmic noise are not sensed. While EM measurements do allow for reduced algorithmic noise, they often also result in increased measurement noise. Furthermore, for EM measurements to reduce algorithmic noise, the measurements must be made at the correct position, and locating this position can be difficult and time consuming, but is often overlooked in existing literature. Additionally, while measurement noise is frequently regarded as a non-issue, modern countermeasures specifically inject noise or attenuate leakage signals beyond what can be addressed through amplification or higher precision measurements. While averaging can fix this, it requires more measurements to be made - meaning the countermeasure is effective.

By addressing these issues, more powerful side-channel attacks can be created. The fist chapter introduces SCNIFFER a platform for efficiently localizing exploitable EM leakage. This allows attackers to benefit from the reduced algorithmic noise of localized EM measurements without exhaustively searching for a high leakage position. The next chapter presents a practical machine learning based EM attack. In this attack, various processing methods are proposed to address the problem of low SNR EM measurements, allowing powerful ML attacks to use EM measurements. In the final chapter a variety of topics are covered, starting with an additional method to improve EM-ML SCA attacks - power to EM mapping. Following this is an SCA evaluation of cryptographic implementations created through high level synthesis. Finally, neural network based cryptosystems are studied.

#### 1.1 SCNIFFER

The first chapter proposes SCNIFFER: a low-cost, automated EM Side Channel leakage SNIFFing platform to perform efficient end-to-end Side-Channel attacks. Presently, to perform EM SCA on an embedded device, the entire chip is manually scanned and the MTD (Minimum Traces to Disclosure) analysis is performed at each point on the chip to reveal the secret key of the encryption algorithm. However, an automated end-to-end framework for EM leakage localization, trace acquisition, and attack has been missing. Using a leakage measure such as Test Vector Leakage Assessment (TVLA), or the signal to noise ratio (SNR), we propose a greedy gradientsearch heuristic that converges to one of the points of highest EM leakage on the chip (dimension:  $N \times N$ ) within O(N) iterations, and then perform Correlational EM Analysis (CEMA) at that point. This reduces the CEMA attack time by  $\sim N$  times compared to an exhaustive MTD analysis, and by  $> 20 \times$  compared to choosing an attack location at random. We demonstrate SCNIFFER using a low-cost custom-built 3-D scanner with an H-field probe (< \$500) compared to > \$50,000 commercial EM scanners, and a variety of microcontrollers as the devices under attack. The SCNIFFER framework is evaluated for several cryptographic algorithms (AES-128, DES, RSA)

running on both an 8-bit Atmega microcontroller and a 32-bit ARM microcontroller to find a point of high leakage and then perform a CEMA at that point.

### 1.2 Cross Device EM-ML SCA

The second chapter presents a Cross-device Deep-Learning based Electromagnetic (EM-X-DL) side-channel analysis (SCA), achieving > 90% single-trace attack accuracy on AES-128, even in the presence of significantly lower signal-to-noise ratio (SNR), compared to power SCA. With an intelligent selection of multiple training devices and proper choice of hyperparameters, the proposed 256-class deep neural network (DNN) can be trained efficiently utilizing pre-processing techniques like PCA, LDA, and FFT on the target encryption engine running on an 8-bit Atmel microcontroller. Finally, an efficient end-to-end SCA leakage detection and attack framework using EM-X-DL demonstrates high confidence of an attacker with ;20 averaged EM traces.

### 1.3 Additional Side-Channel Attacks

The final chapter investigates three topics: Power to EM mapping, the security of high-level synthesis generated implementations of AES, and neural encryption through adversarial training. Power to EM mapping would allow EM-ML SCA models, such as the one in the previous chapter, to be trained by collecting high SNR power traces and using a mapping to create EM trace. Through this the number of measurements would be reduced. Different methods for finding a mapping are compared, and the performance of generated EM traces in an ML-SCA model is investigated. Finally, neural encryption is studied as a possible target for side channel attacks. The security of a neural cryptosystem is analyzed, and it is to be rather insecure, able to be broken without needing side-channel information.

## 2. SCNIFFER: LOW-COST, AUTOMATED, EFFICIENT ELECTROMAGNETIC SIDE-CHANEL SNIFFING

### 2.1 Introduction

As the internet of things (IoT) continues to grow, security of many edge nodes has become critical. With many of these edge nodes being simple microcontrollers, sidechannel attacks pose a powerful threat to their security. In the world of cryptography, side-channel attacks have long been identified as a threat to the security of computing and communication systems attempting to provide confidentiality and integrity of sensitive data, since the introduction of Differential Power Analysis in [1]. By analyzing physical side-channel information, such as power consumption, timing, or electromagnetic emissions, cryptographic algorithms that are mathematically secure can be broken efficiently.

EM side-channel analysis (SCA) is a method of using the information found in the electromagnetic emissions of a cryptographic system to extract the secret key, compromising the security of such a system. Such attacks have been shown to be capable of actually extracting secret key information, as in [2] and [3]. These EM emissions originate from current consumption of an IC running cryptographic algorithms, which while flowing through the metal layers of an IC cause EM radiation as described in [4]. The EM emissions can either be caused by key-dependent operations or other operations. EM emissions caused by key-dependent operations contribute to the side-channel signal, while EM emissions caused by other operations contribute to algorithmic noise. EM SCA attacks have successfully been used in the real world on PCs, shown in [5] and [6], and also on Smart Cards, in [7] [8]. One powerful and commonly used side-channel analysis technique is correlational electromagnetic analysis (CEMA). In CEMA, EM measurements are taken while a cryptographic algorithm is

Fig. 2.1. (a, b) Comparison between existing EM SCA systems and SCNIFFER. While current frameworks have integrated trace collection and attack and analysis, SCNIFFER integrates EM scanning as well. (c) High level overview of proposed SCNIFFER framework. SCNIFFER analyzes EM leakage and uses a gradient descent algorithm to locate points of high informative leakage at which the EM SCA attack should be performed.

executing on the target system (each measurement is known as a trace), and these traces are correlated with a leakage model, such as the Hamming Weight or Hamming Distance of data at a particular point in an algorithm [1], under a hypothesis of a subset of the secret key. In a successful attack, the hypothesis that results in maximum correlation corresponds to the secret key. Thanks to the divide and conquer nature of side-channel analysis, the cost of performing an SCA attack is linear in the key size, rather than exponential, as in brute force or other cryptanalysis methods.

### 2.1.1 Motivation

EM side-channel attacks, while powerful in that they are non-invasive and do not require any physical changes to the system being attacked, and benefit from allowing an attacker to choose the location with maximum information leakage (SNR), introduce a number of additional challenges compared to the power SCA attacks.

Fig. 2.2. The difference in MTD between a CEMA attack at a point of high leakage vs. at a point of low leakage for both an 8-bit XMEGA microcontroller (a, b) and a 32-bit STM32F3 microcontroller (c, d). At a location of high leakage, the correct key separates in 250 traces for both microcontrollers, while a low leakage location requires >  $20 \times$  more traces on the XMEGA. At a low leakage location on the STM32F3, the key does not separate at all within 10,000 traces.

Firstly, as the EM signals go through a power to EM transformation that reduces amplitude compared to the measurement noise floor, meaning more traces, or more expensive measurement equipment may be needed to perform an attack. Secondly, unlike power attacks, EM attacks require attackers to choose the location of the attack in the system to capture the EM traces. However, scanning a device to determine this point is is not currently integrated into current frameworks (Figure 2.1(a)). This choice of location can have a drastic impact on the effectiveness and efficiency of an attack. As seen in Figure 2.2, depending on where the EM probe is placed on a chip, the MTD for a CEMA attack can vary by  $> 20\times$ , even for the small 9mm x 9mm Atmega and STM microcontrollers used as the target devices for this chapter. Current methods for determining the best location to perform CEMA are based on exhaustive search, simply performing a CEMA attack at most locations. Alternatively, it is also possible to choose an arbitrary location, and use as many traces as necessary to perform the CEMA. Practically, if the size of the system is larger, finding the correct location of the EM leakage becomes extremely challenging and requires scanning the entire chip/system.

Given the limitations of present attack systems, in this chapter, we propose a lowcost, fully automated, end-to-end platform for performing efficient EM side-channel attacks. SCNIFFER integrates EM scanning, trace collection, and attack/analysis into a single framework (Figure 2.1(b)). A high level overview of the SCNIFFER framework is shown in Figure 2.1(c). The core of this framework is a  $\sim$  \$200 3-D printer, which we have modified to utilize as a low-cost EM scanner. SCNIFFER also uses a greedy gradient-search heuristic using a leakage measure, such as test vector leakage assessment (TVLA), or SNR to quickly and automatically locate a point of high data-dependent leakage (referred to as simply high leakage throughout this work). Finally, once the point is determined, the proposed SCNIFFER framework performs the correlational or differential EM analysis (CEMA/DEMA) at this point. While both CEMA and DEMA are possible attacks, in this chapter, we will demonstrate results with CEMA. Such an automated low-cost attack platform significantly increases the threat surface for IoT devices, however, it should be noted that SCNIFFER does not constitute a new attack; and existing countermeasures against EM SCA attack are effective against SCNIFFER. The SCNIFFER system presented in this chapter is published in [9].

### 2.1.2 Contribution

Specific contributions of this chapter are:

- Low-cost Automated EM Side-channel Analysis Framework: A fullyautomated system for efficiently scanning a cryptographic chip and finding a location of high leakage to mount an end-to-end EM SCA attack is proposed. The entire attack set-up is extremely low-cost, owing to the custom-built EM scanner (adapting a ~ \$200 3-D printer) used for mounting the attack, compared to the commercially available EM probe stations, which are very costly (> \$50,000). The system achieves 100µm spatial resolution, and has a scan range of 220mm × 220mm, and is easily replicable (Section 3).

- Integrated EM Scanning, Trace Collection, and Attack: EM Scanning is brought in the loop of the attack framework through the proposed greedy gradient-descent heuristic algorithm, which analyzes leakage on-the-fly to efficiently scan the chip and locate a point of high leakage. This algorithm converges to a high leakage location on an  $N \times N$  chip within O(N) iterations. This algorithm is evaluated with both TVLA and SNR as the measures of leakage, and results for the complete system on a variety of cryptographic targets are shown (Sections 4, 5, 6).

### 2.1.3 Chapter Organization

The remainder of the chapter is organized as follows. Section 2 provides the background and summarizes the existing works on EM Scanning and side-channel attacks. In Section 3, the SCNIFFER framework is introduced and the low cost, custom-built EM scanning platform is presented. Section 4 describes two options for measuring leakage, TVLA and SNR, and provides motivation for finding a point of high leakage. In Section 5, the gradient-descent algorithm for efficiently determining a point of high information leakage is proposed. Next, Section 6 provides results of running the system on microcontrollers of varying architectures, cryptographic algorithms executed, and measures of leakage. Finally, Section 7 concludes the chapter.

#### 2.2 Background and Related Work

IoT devices have been successfully attacked using side channel attacks, for example CPA was used to extract encryption keys from Philips Hue smart lamps in [10]. EM side-channel attacks were first proposed in [11], and share many properties with power side-channel attacks, however, can be performed at a distance, even up to one meter, as in [12]. One of the most powerful EM SCA attacks is CEMA, which is the straightforward application of Correlation Power analysis (CPA) [13] on EM traces.

However, to make these profiled and non-profiled EM SCA attacks more practical and real-time on any embedded platform/device, the trace capture and the attack needs to be automated and more efficient.

SCNIFFER can use several methods of assessing leakage, for instance, simple signal magnitude, Test Vector Leakage Assessment (TVLA) [14], or SNR [15]. In **TVLA**, two sets of traces are collected. In one set, both the key and plaintext used as input to the algorithm under test are kept fixed, and in the other the plaintext is varied randomly, while the key remains fixed. To assess the leakage, one then performs Welch's t-test for each time point of the trace. Welch's t-test is given by  $t = \frac{\bar{X}_1 - \bar{X}_2}{\sqrt{\frac{s_1^2}{N_1} + \frac{s_2^2}{N_2}}}$ , where  $\bar{X}_1, \bar{X}_2$  are the sample means of the two sets,  $s_1, s_2$  are sample standard deviations for the sets, and  $N_1, N_2$  are the sizes of the sets. If the maximum t-value at a point is above 4.5, one can conclude leakage is present with 99.999% confidence. Meanwhile, we consider the signal to noise ratio as defined in [15], to be  $\mathbf{SNR} = \frac{VAR[Q]}{VAR[N]}$ , where Q is the side channel leakage, and N is the noise. Unlike TVLA, which does not guarantee exploitable leakage, SNR defined in this way can be directly related to the success rate of a CEMA attack [15].

Once SCNIFFER has chosen a point to attack, CEMA is used to recover the secret key. CEMA revolves around making hypotheses on secret values, then predicting the EM leakage of an intermediate variable based on the key. Measurements (traces) are taken while the device performs encryption, then the measurements are correlated with the predicted leakage for all hypotheses. The hypothesis that results in the

### Table 2.1.

Comparison with previous works. SCNIFFER is significantly lower cost compared to previous works, and additionally is the only system designed to maximize the effectiveness of an attack, as other systems seek only the location of most informative leakage.

|              | Search<br>Technique  | Search<br>Metric       | Attack<br>Technique | Positioning<br>Accuracy | Cost       | System<br>Focus         |

|--------------|----------------------|------------------------|---------------------|-------------------------|------------|-------------------------|

| [18]         | Exhaustive<br>Search | SNR                    | CEMA                | 100µm                   | >\$10,000* | Leakage<br>Localization |

| [19]         | Exhaustive<br>Search | Difference<br>of Means | Template<br>Attack  | 50µm                    | >\$10,000* | Leakage<br>Localization |

| [20]         | Greedy<br>Search     | DEMA                   | DEMA                | 2.5µm                   | >\$50,000* | Leakage<br>Localization |

| This<br>work | Gradient<br>Search   | TVLA/SNR               | CEMA                | 100µm                   | ~\$500     | End-to-End<br>Attack    |

\* Estimated cost of system based on listed components and specifications

largest correlation is taken as the guess for the secret value. The number of traces needed to recover the key in this way is then the minimum traces to disclosure (MTD). In this chapter, the secret values are the bytes of the AES key, and the intermediate variable is the first round sbox output, and Hamming Weight, that is, the number of 1's in the binary representation of this variable, is used as the leakage model of data at this point.

Addressing the issue of finding where a chip leaks the most EM radiation has been investigated in [16], and [17]. EM scanning with a focus on side-channel attacks, that is, determining where the most cryptographic information leaks within a chip has been addressed in [18], [19], and [20]. However, such methods focus on observing the leakage over the entire chip, not efficiently finding the point or region of the maximum leakage. This causes these methods to take a long time and a majority of the time is spent collecting data that is unnecessary for an attacker. More recently in [21], an adaptive method to determine the location of greatest cryptographic leakage without resorting to exhaustive search is presented. However, this method performs a full SCA attack at each location analyzed, again making it unsuitable for an attacker, whose goal is only a single successful attack. By creating a framework that minimizes this

Fig. 2.3. (a) The complete EM Scanning and trace capture set-up system, including the 3-D printer, Chipwhisperer system, EM probe, amplifier, and victim. (b) Close-up of scanner, showing probe and victim board.

unnecessary data collection, EM side-channel attacks can be made more efficient, powerful, and practical, requiring far fewer traces to reveal the secret key of the cryptographic algorithm. Additionally, these platforms can be orders of magnitude more costly than the system proposed in this chapter, for instance the Riscure EM Probe station [22] itself can cost  $\sim$  \$50,000, while the entire SCNIFFER system costs < \$500. Table 2.1 compares the SCNIFFER system to previous works. Note that while all previous works as shown in the table aim to locate the point of greatest informative leakage, only SCNIFFER focuses on minimizing the total number of traces needed for a successful attack. SCNIFFER is the first fully-automated, efficient EM SCA attack framework and the system is described in the following section.

### 2.3 SCNIFFER: Low Cost Automated EM Scanning

The SCNIFFER system is designed for low cost and automation. In this section, we first describe the physical components that make up SCNIFFER, then discuss the automation aspect of the system.

#### 2.3.1 Low Cost EM Scanning Setup

The scanning hardware consists of an Ender-3 3-D printer [23] with a 10mm loop diameter H-field probe attached to the extruder, the Chipwhisperer [24] platform for interfacing with the victim (The CW309T-XMEGA mounted on the 308 UFO Target board) and trace collection, an amplifier to amplify the EM probe output, and finally a PC to control both the 3-D printer and the Chipwhisperer Lite capture board. While such EM scanning systems do exist, for instance, Riscure's EM Scanning Station, we chose to create such a system from scratch for the following reasons: 1) Commercial scanning systems (like Riscure [22]) scanning station is orders of magnitude more expensive and 2) It is very straightforward to interface with the custom system to develop the scanning algorithm. As seen in Table 2.2, the cost of a commercial scanner is orders of magnitude higher than SCNIFFER, and while it is hard to know if this price

### Table 2.2.

Summary of the main components of the SCNIFFER system, their costs, performance, and a comparison to Riscure's EM Probe Station.

|                                               | Scanner | Amplifier    | Probe  |

|-----------------------------------------------|---------|--------------|--------|

| Picture                                       |         | RF-OUT CC-SV | IN .   |

| Cost                                          | \$200   | \$50         | \$10   |

| SCNIFFER<br>Specifications                    | 100 µm  | 20dB         | 16mm^2 |

| Riscure EM Probe<br>Station<br>Specifications | 2.5 µm  | -            | 1mm^2  |

has been inflated by the selling company, it is reasonable for prices to be higher, as there are not many EM scanners on the market.

To manipulate the probe, an Ender-3 3-D printer, running stock firmware was used. This model of printer has a minimum step size of 0.1mm, and can be controlled via a USB serial connection. It has a maximum movement speed of 180 mm/s, with a print area of  $220mm \times 220mm \times 250mm$ . The precision and speed offered by this 3-D printer are sufficient to complete a  $50 \times 50$  scan of the  $9mm \times 9mm$  IC used in testing in an acceptable time. Additional justification for the choice of printer, beyond the cost includes the ease of interfacing, the form factor, maintainability, and software support. The open source firmware used by this printer is well documented, and can be controlled through an exposed serial port, making interfacing very easy. The printer also has an open form factor that allows the probe and victim board to be mounted easily. While the durability and hardware support would not be as good as a commercial EM scanner, the simple construction and use of off-the-shelf components make maintenance straightforward. The software support is quite strong, being open source, and the printer is plug-and-play compatible with any device with a serial port. The system is capable of performing a  $30 \times 30$  scan of the chip in  $\sim 15$  minutes, and perform an amplitude scan in  $\sim 75$  minutes. The probe used is a commercial H-field probe for performing EMC measurements, and the signal is amplified before being passed to the Chipwhisperer capture board. While the probe used does not have extremely high spatial resolution, the probe resolution matches the scan resolution, allowing heatmaps such as the one in Figure 2.4(a) to be created, and Chipwhisperer is able to capture enough information leakage for the target devices considered, leading to low MTDs when probed at appropriate locations, as seen in figure 2.2, while still being low cost. Even though this probe is on the larger side, the SCNIFFER platform is compatible with more sensitive probes and is expected to become more precise with such probes. The complete system is shown in Figure 2.3(a) showing the 3-D printer, the probe, Chipwhisperer system, and PC. The probe and victim IC are shown in detail in Figure 2.3(b). The probe position can be controlled manually, through the 3-D printer controls, or programmatically through the serial connection to a PC, as it is in the SCNIFFER system.

The major cost savings in the SCNIFFER system come from using a low cost 3-D printer to control the probe, instead of a high cost motorized table. The total cost of the 3-D printer, probe and amplifier used in SCNIFFER is  $\sim$  \$500, which is a few orders of magnitude less expensive than many motorized tables by themselves, and nearly two orders of magnitude less expensive than systems such as Riscure's EM probe station ( $\sim$  \$50,000). While more expensive scanners, probes and measurement systems could improve spatial and frequency resolution, such a system would only be available to very sophisticated attackers. As SCNIFFER aims to demonstrate that practical, low-cost attacks are possible using systems two orders of magnitude cheaper than existing scanners, high-cost, high resolution components are not used. Table 2.2 summarizes these components, including their costs and performance compared to the Riscure system.

Fig. 2.4. (a) Heatmap of the SNR values obtained by performing a full  $30 \times 30$  scan of the 8-bit target microcontroller. (b) This shows the grid divisions where leakage measurements were performed. 1000 traces were used to compute the SNR values at each point. The part of the target microcontroller board which leak the most information can be observed.

Fig. 2.5. (a) TVLA surface plot. Again, the surface is not smooth or monotonic, as there are many local minima and maxima, as in Figure 2.6(a). (b) Histogram of TVLA measurements at a single point. 50 TVLA measurements were made at a point of high leakage, each done as in (a), using 400 traces each. Given the distribution much wider seen in (b), the increased roughness of the surface in (a) can be explained.

### 2.3.2 Automated EM Scanning

Now that the SCNIFFER system's low cost hardware has been described, we move to the automated scanning and attack procedure. The basic premise of the automated system is to locate a point on the target device where the chosen leakage measure is high by using the scanning algorithm specified in Section 5, and then to automatically perform CEMA at this point. This removes the need for an expert to manually analyze example traces to choose a location for an attack.