# HARDWARE-SOFTWARE CODESIGN FOR EFFICIENT MACHINE LEARNING USING IN-MEMORY COMPUTING

A Dissertation

Submitted to the Faculty

of

Purdue University

by

Aayush Ankit

In Partial Fulfillment of the

Requirements for the Degree

of

Doctor of Philosophy

December 2020

Purdue University

West Lafayette, Indiana

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF DISSERTATION APPROVAL

Dr. Kaushik Roy, Chair

School of Electrical and Computer Engineering

Dr. Anand Raghunathan

School of Electrical and Computer Engineering

Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

Dr. Shreyas Sen

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

Head of the School Graduate Program

Dedicated to Maa, Papa, Pratyush, family and friends without whose unconditional love and support none of this would have been possible.

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Professor Kaushik Roy, who has been an exemplary role model for me in all aspects, whether in his intelligence and integrity as a researcher, his passion and clarity as a teacher, or his humility and compassion as a person. Kaushik always puts people first and is concerned about their well-being before being concerned about their technical progress, always willing to listen and always willing to help. Undoubtedly, over the years, his insightful and critical suggestions, work ethics, and inspiration to pursue exciting problems have shaped me as a researcher. His immense energy for research and constant drive for pursuing challenging problems, deeply motivated me and showed the path towards overcoming numerous challenges throughout my PhD. His strong emphasis on crisp and precise communication and presentation skills, and high-quality writing helped me significantly grow my non-technical skills. I deeply thank him for being an outstanding mentor, critic, and advisor to me through the course of my PhD. He continues to inspire us who work with him to strive for high standards of academic excellence and character through the example that he sets.

I would also like to thank the rest of my committee, Professors Anand Raghunathan, Shreyas Sen, and Vijay Raghunathan, for going above and beyond their duty in their responsiveness and guidance throughout my PhD. My work is much stronger because of their contributions.

I would also like to thank Dr. Dejan Milojicic, Dr. John Paul Strachan, and Dr. Sai Rahul Chalamalasetti from Hewlett Packard Labs. Getting to know them has helped my in my career because of the opportunities they opened up for me and the confidence they instilled in me by believing in me.

Lastly, I would like to thank the members of Nanoelectronics Research Laboratory for their feedback and companionship throughout this journey and for being a fun bunch of people. I especially would like to thank Abhronil Sengupta, Indranil Chakraborty, Deboleena Roy, and Mustafa Fayez Ali for their brilliance, eagerness to help others, numerous brain-storming and fun discussions, and remarkable work ethic.

Lastly, I am not who I am without my parents, my sibling, my dear friends Carol Martin, Abhinav Gupta, Aamir Raihan, and Chankyu Lee. I thank them wholeheartedly for their love and support. They are my biggest blessing.

## TABLE OF CONTENTS

|    |      |         | I                                                   | Page |

|----|------|---------|-----------------------------------------------------|------|

| AI | BSTR | CACT    |                                                     | xi   |

| LI | ST O | F TAB   | LES                                                 | xiii |

| LI | ST O | F FIGU  | URES                                                | xiv  |

| 1  | INT  | RODU    | CTION                                               | 1    |

|    | 1.1  | Machi   | ne Learning and its Computational Challenges        | 1    |

|    | 1.2  | Analo   | g In-memory Computing                               | 2    |

|    | 1.3  | Disser  | tation Overview                                     | 3    |

| 2  | REL  | ATED    | WORK AND BACKGROUND                                 | 5    |

|    | 2.1  | Infere  | nce Accelerator Architectures                       | 5    |

|    |      | 2.1.1   | CMOS Digital In-/Near-memory Accelerators           | 5    |

|    |      | 2.1.2   | Memristor-based Analog In-/Near-memory Accelerators | 6    |

|    |      | 2.1.3   | Memristor Manufacturability and Non-ideality        | 7    |

|    | 2.2  | Softwa  | are Optimizations (Weight Pruning)                  | 8    |

|    | 2.3  | Traini  | ng Accelerator Architectures                        | 9    |

|    | 2.4  | GPGF    | PU Tensor Core                                      | 10   |

| 3  | PUN  | IA - IN | FERENCE ACCELERATOR ARCHITECTURE                    | 13   |

|    | 3.1  | Introd  | luction                                             | 13   |

|    | 3.2  | Workl   | oad Characterization                                | 15   |

|    |      | 3.2.1   | Multi-Layer Perceptron (MLP)                        | 15   |

|    |      | 3.2.2   | Long Short-Term Memory (LSTM)                       | 17   |

|    |      | 3.2.3   | Convolutional Neural Network (CNN)                  | 18   |

|    |      | 3.2.4   | Other ML Workloads                                  | 19   |

|    | 3.3  | Core    | Architecture                                        | 20   |

|    |      | 3.3.1   | Instruction Execution Pipeline                      | 20   |

|   |     |        |                                          | Pag | е |

|---|-----|--------|------------------------------------------|-----|---|

|   |     | 3.3.2  | Matrix-Vector Multiplication Unit (MVMU) | . 2 | 2 |

|   |     | 3.3.3  | Vector Functional Unit (VFU)             | . 2 | 4 |

|   |     | 3.3.4  | Register File                            | . 2 | 5 |

|   |     | 3.3.5  | Memory Unit (MU)                         | . 2 | 7 |

|   |     | 3.3.6  | Static Instruction Usage                 | . 2 | 7 |

|   |     | 3.3.7  | Summary                                  | . 2 | 8 |

|   | 3.4 | Tile A | Architecture                             | . 2 | 9 |

|   |     | 3.4.1  | Shared Memory                            | . 2 | 9 |

|   |     | 3.4.2  | Receive Buffer                           | . 3 | 1 |

|   |     | 3.4.3  | Summary                                  | . 3 | 2 |

|   | 3.5 | Node   | Architecture                             | . 3 | 2 |

|   | 3.6 | Instru | ction Set Architecture                   | . 3 | 3 |

|   |     | 3.6.1  | Core Instructions                        | . 3 | 3 |

|   |     | 3.6.2  | Tile Instructions                        | . 3 | 5 |

|   | 3.7 | Evalua | ation Methodology                        | . 3 | 6 |

|   |     | 3.7.1  | PUMA Simulator                           | . 3 | 6 |

|   |     | 3.7.2  | System and Workloads                     | . 3 | 9 |

|   | 3.8 | Result | ts                                       | . 3 | 9 |

|   |     | 3.8.1  | Inference Energy                         | . 3 | 9 |

|   |     | 3.8.2  | Inference Latency                        | . 4 | 0 |

|   |     | 3.8.3  | Batch Throughput and Energy              | . 4 | 1 |

|   |     | 3.8.4  | Comparison with ML Accelerators          | . 4 | 2 |

|   |     | 3.8.5  | Evaluation of Optimizations              | . 4 | 6 |

|   |     | 3.8.6  | Design Space Exploration                 | . 4 | 6 |

|   | 3.9 | Concl  | usion                                    | . 4 | 7 |

| 4 | TRA | NNSF   | ORMER - SOFTWARE OPTIMIZATION            | . 4 | 9 |

|   | 4.1 | Introd | luction                                  | . 4 | 9 |

|   | 4.2 | TraNN  | Nsformer Framework                       | . 5 | 1 |

|   |     |        | Р                                                             | age |

|---|-----|--------|---------------------------------------------------------------|-----|

|   |     | 4.2.1  | Spectral Clustering                                           | 53  |

|   |     | 4.2.2  | Size Constrained Iterative Clustering (SCIC)                  | 54  |

|   |     | 4.2.3  | Integrated Training Approach                                  | 56  |

|   | 4.3 | Impac  | et on Crossbar-based Architecture                             | 57  |

|   | 4.4 | Exper  | imental Methodology                                           | 59  |

|   | 4.5 | Result | ts                                                            | 60  |

|   |     | 4.5.1  | Algorithm-level Analysis                                      | 61  |

|   |     | 4.5.2  | Area and Energy Comparisons for Crossbar-based Architecture . | 63  |

|   | 4.6 | Concl  | usions                                                        | 65  |

| 5 | PAN | THER   | - TRAINING ACCELERATOR ARCHITECTURE                           | 66  |

|   | 5.1 | Introd | luction                                                       | 66  |

|   | 5.2 | Backg  | round                                                         | 69  |

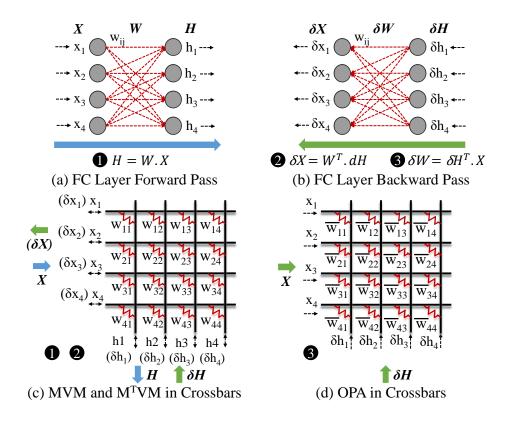

|   |     | 5.2.1  | Deep Neural Network Training                                  | 69  |

|   |     | 5.2.2  | Using Crossbars for Training                                  | 69  |

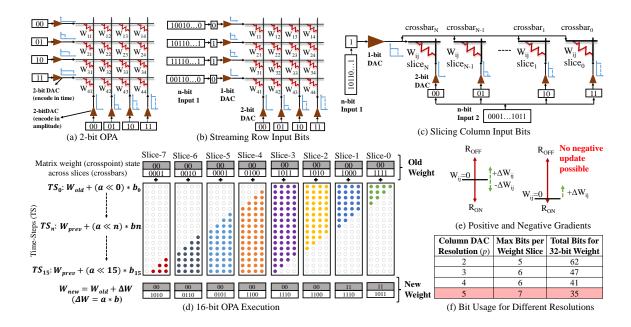

|   | 5.3 | Enhar  | ncing ReRAM-based OPA Precision                               | 72  |

|   |     | 5.3.1  | Bit Slicing the OPA Operation                                 | 72  |

|   |     | 5.3.2  | Bits to Handle Overflow                                       | 74  |

|   |     | 5.3.3  | Number of Slices vs. Bits Per Slice                           | 75  |

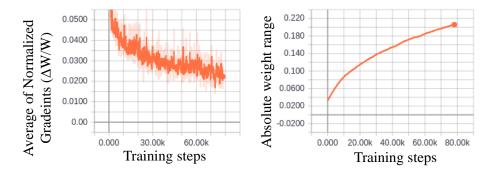

|   |     | 5.3.4  | Heterogeneous Weight Slicing                                  | 76  |

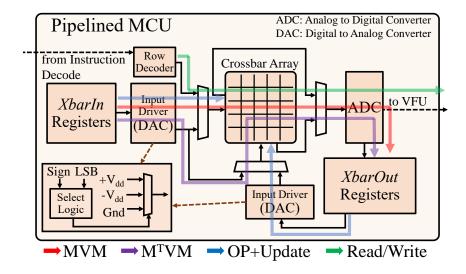

|   | 5.4 | Matri  | x Computation Unit (MCU)                                      | 77  |

|   |     | 5.4.1  | MCU Organization                                              | 77  |

|   |     | 5.4.2  | Variant #1 for SGD Acceleration                               | 78  |

|   |     | 5.4.3  | Variant #2 for Mini-Batch SGD Acceleration                    | 79  |

|   |     | 5.4.4  | Variant #3 for Mini-Batch SGD with Large Batches              | 81  |

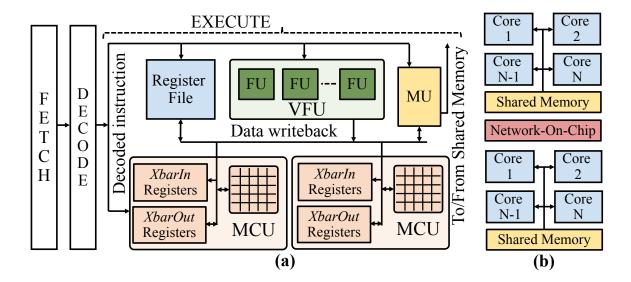

|   | 5.5 | Progra | ammable Accelerator                                           | 81  |

|   |     | 5.5.1  | Accelerator Organization                                      | 82  |

|   |     | 5.5.2  | ISA Considerations                                            | 83  |

|   |     | 5.5.3  | Compiler Support                                              | 84  |

|   |     |        |                                                    | Page |

|---|-----|--------|----------------------------------------------------|------|

|   |     | 5.5.4  | Implementing Convolutional Layers                  | . 85 |

|   | 5.6 | Metho  | odology                                            | . 87 |

|   |     | 5.6.1  | Architecture Simulator                             | . 87 |

|   |     | 5.6.2  | Functional Simulator                               | . 89 |

|   |     | 5.6.3  | Baselines                                          | . 89 |

|   |     | 5.6.4  | Workloads                                          | . 91 |

|   | 5.7 | Evalu  | ation                                              | . 92 |

|   |     | 5.7.1  | Impact of Slice Bits and CRS Frequency on Accuracy | . 92 |

|   |     | 5.7.2  | Impact of Heterogeneous Weight Slicing             | . 94 |

|   |     | 5.7.3  | Variant #1 SGD Energy Comparison                   | . 95 |

|   |     | 5.7.4  | Variant #2 Mini-Batch SGD Energy                   | . 95 |

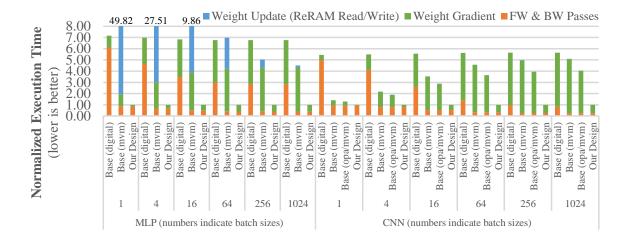

|   |     | 5.7.5  | Variant #2 Execution Time                          | . 96 |

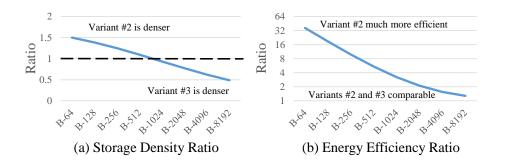

|   |     | 5.7.6  | Comparing Variants #2 and #3                       | . 97 |

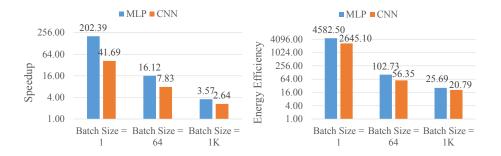

|   |     | 5.7.7  | Comparison with GPUs                               | . 97 |

|   |     | 5.7.8  | Sensistivity to ReRAM endurance                    | . 98 |

|   | 5.8 | Concl  | usion                                              | . 99 |

| 6 | TIM | ON - C | GPGPU TENSOR CORE                                  | 100  |

|   | 6.1 | Introd | luction                                            | 100  |

|   | 6.2 | Backg  | ground                                             | 102  |

|   |     | 6.2.1  | Background on In-Memory Computing                  | 102  |

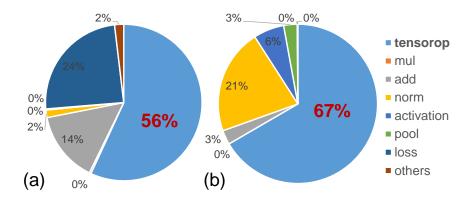

|   | 6.3 | GPGI   | PU Characterization                                | 104  |

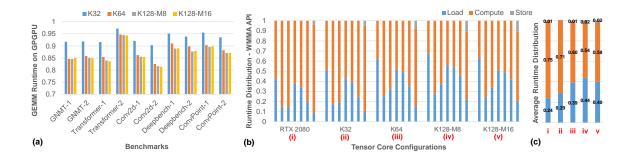

|   |     | 6.3.1  | Workload Characterization                          | 104  |

|   |     | 6.3.2  | Inefficiency of GPU Tensor Cores                   | 105  |

|   |     | 6.3.3  | Summary                                            | 109  |

|   | 6.4 | TIMC   | ON Architecture                                    | 110  |

|   |     | 6.4.1  | Baseline Tensor Core Architecture (Turing GPU)     | 110  |

|   |     | 6.4.2  | TIMON Dataflow                                     | 110  |

|   |     | 6.4.3  | TIMON Microarchitecture                            | 114  |

|       |        |                                             | Pag  | ;e |

|-------|--------|---------------------------------------------|------|----|

|       | 6.4.4  | TIMON Register Mapping                      | . 11 | 7  |

| 6.5   | TIMO   | N Instruction Extension                     | . 11 | 8  |

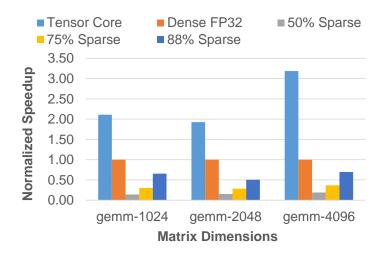

| 6.6   | Suppor | rting Model Compression                     | . 12 | 1  |

|       | 6.6.1  | Irregular Quantization                      | . 12 | 1  |

|       | 6.6.2  | Unstructured Sparsity                       | . 12 | 2  |

| 6.7   | Evalua | ation Methodology and Results               | . 12 | 4  |

|       | 6.7.1  | Methodology                                 | . 12 | 4  |

|       | 6.7.2  | GPGPU performance analysis                  | . 12 | 6  |

|       | 6.7.3  | Tensor core analysis - TIMON versus Turning | . 12 | 8  |

|       | 6.7.4  | Model Compression on TIMON                  | . 12 | 8  |

|       | 6.7.5  | Area Overheads and Circuit Non-Idealities   | . 13 | 0  |

| 6.8   | Conclu | asion                                       | . 13 | 1  |

| 7 SUN | MARY   |                                             | . 13 | 2  |

| REFER | RENCES | 5                                           | . 13 | 4  |

| VITA  |        |                                             | 15   | 6  |

## ABSTRACT

Ankit, Aayush Ph.D., Purdue University, December 2020. Hardware-Software Codesign for Efficient Machine Learning using In-Memory Computing. Major Professor: Kaushik Roy.

General-purpose computing systems have benefited from technology scaling for several decades but are now hitting a performance/energy wall. This trend has led to a growing interest in domain-specific accelerators. Machine Learning (ML) workloads in particular have received tremendous attention because of their pervasiveness across applications. ML workloads tend to be data-intensive and perform many matrix operations. Their execution on digital CMOS hardware is typically characterized by high data movement costs. To overcome this limitation, in-memory computing primitives (CMOS, NVM) have been demonstrated to perform matrix operations with high efficiency by overcoming the low memory bandwidth and high memory energy issues. While such primitives have shown tremendous potential at the device-circuit levels, the system-level implications remain unclear, as they are not a drop-in replacement for traditional memory structures (register file, caches etc.).

First, this thesis explores the potential of in-memory computing towards domain-specific accelerators for inference, sparse inference, and training. To improve inference efficiency PUMA is proposed, which is a spatial architecture built with Non-Volatile Memory (NVM) crossbars. PUMA leverages the high on-chip storage density and analog computation capabilities of NVM to accelerate a wide range of ML applications. It supplements NVM crossbars with CMOS digital units, an instruction execution pipeline, and a specialized ISA to enable efficient coverage across different ML workloads and enhance programmability. It also includes a hardware-software codesign to optimize data movement. The evaluations show that PUMA achieves significant

energy and latency improvements for ML inference compared to the state-of-the-art GPUs, CPUs, and ASICs. Subsequently, the proposed accelerator is extended for sparse inference. The over-parametrized nature of typical ML models has motivated model-compression techniques such as network pruning to improve the inference efficiency. However, sparse models obtained by typical network pruning lead to inefficient execution particularly on in-memory hardware. To address this, TraNNsformer is proposed which prunes the connectivity matrix while forming clusters with the remaining connections during the training process to transform the original model into an optimally pruned and maximally clustered mapping. Next, the applicability of the proposed in-memory accelerator (PUMA) is explored for ML training. Despite the storage density and analog computing benefits, NVMs suffer from high write cost, which is detrimental for ML training because of weight updates being a common case. To address this, a bit-slicing technique is proposed that enables performing high-precision analog outer-products on NVM crossbars to realize the weight update without using typical reads and writes. This technique is incorporated into an ISA-programmable architecture namely PANTHER, which enables different training algorithms and different layers types.

Despite the effectiveness of domain-specific accelerators for ML acceleration, general-purpose systems such as General Purpose Graphics Processing Unit (GPGPU) have continued to play an important role in ML inference and training owing to their wider availability and lower engineering costs for hardware-software developments. Subsequently, modern GPGPUs have introduced domain-specific units for matrix multiplication namely tensor core to meet the growing performance demands of ML. However, even with the improved throughput, tensor cores are inherently limited by the bandwidth of large register file sizes in GPGPU. To this effect, the implication of in-memory computing based tensor cores on GPGPU is explored. We show that GPGPU augmented with in-memory tensor cores enables overcoming the bandwidth limitation of register file, and provides the required flexibility for emerging application trends such as quantization and sparsity.

## LIST OF TABLES

| Tabl | e                                                                                                                                                    | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1  | Workload Characterization                                                                                                                            | . 16 |

| 3.2  | Instruction Set Architecture Overview                                                                                                                | . 21 |

| 3.3  | Shared memory sizing                                                                                                                                 | . 30 |

| 3.4  | Data Movement Cost                                                                                                                                   | . 33 |

| 3.5  | PUMA Hardware Characteristics                                                                                                                        | . 37 |

| 3.6  | Benchmarking Platforms                                                                                                                               | . 38 |

| 3.7  | Benchmarks                                                                                                                                           | . 38 |

| 3.8  | Comparison with ML Accelerators                                                                                                                      | . 43 |

| 3.9  | Programmability Comparison with ISAAC                                                                                                                | . 43 |

| 3.10 | Evaluation of Optimizations                                                                                                                          | . 45 |

| 4.1  | MLP benchmarks                                                                                                                                       | . 59 |

| 5.1  | Dataflow for SGD                                                                                                                                     | . 79 |

| 5.2  | Dataflow for Mini-Batch SGD                                                                                                                          | . 80 |

| 5.3  | Summary of platforms                                                                                                                                 | . 89 |

| 5.4  | Details of workloads                                                                                                                                 | . 91 |

| 6.1  | HMMA data reuse and resulting WMMA cycles. Ops = $2 \times M \times N \times K$ , Bytes = $2 \times (2 \times M \times N + M \times K + N \times K)$ | 108  |

| 6.2  | GEMM benchmarks                                                                                                                                      | 125  |

| 6.3  | Area comparison of TIMON/Turing tensor cores                                                                                                         | 130  |

| 6.4  | TIMON's accuracy under circuit non-idealities                                                                                                        | 130  |

## LIST OF FIGURES

| Figu | re Pag                                                                                                                                                                                                                                                                                                                                | зe         |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.1  | Increase in the performance density of CMOS hardware [13]                                                                                                                                                                                                                                                                             | 2          |

| 1.2  | Increase in the computational requirements of ML models [13] $\dots \dots$                                                                                                                                                                                                                                                            | 3          |

| 3.1  | Core Architecture                                                                                                                                                                                                                                                                                                                     | 21         |

| 3.2  | MVM with Crossbars                                                                                                                                                                                                                                                                                                                    | 22         |

| 3.3  | ROM-Embedded RAM                                                                                                                                                                                                                                                                                                                      | 26         |

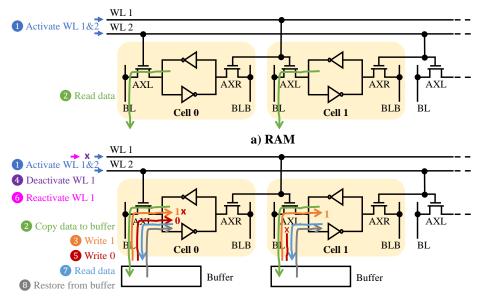

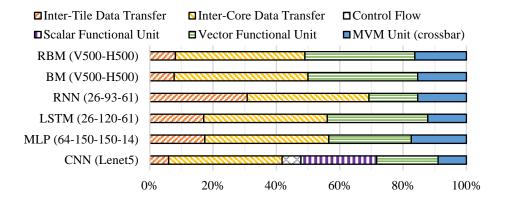

| 3.4  | Static instruction usage showing the importance of different execution units. 2                                                                                                                                                                                                                                                       | 28         |

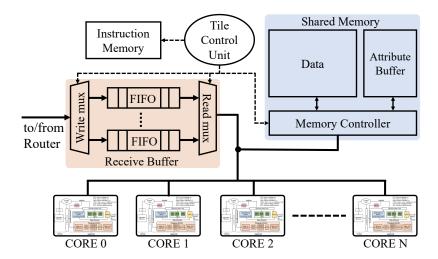

| 3.5  | Tile Architecture                                                                                                                                                                                                                                                                                                                     | 29         |

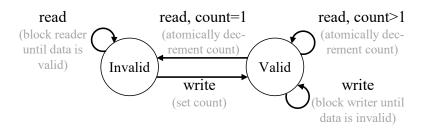

| 3.6  | Inter-core synchronization mechanism                                                                                                                                                                                                                                                                                                  | 30         |

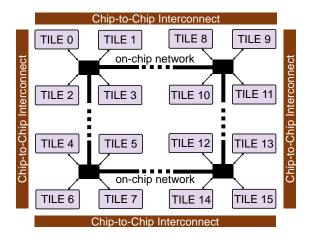

| 3.7  | Node architecture                                                                                                                                                                                                                                                                                                                     | 32         |

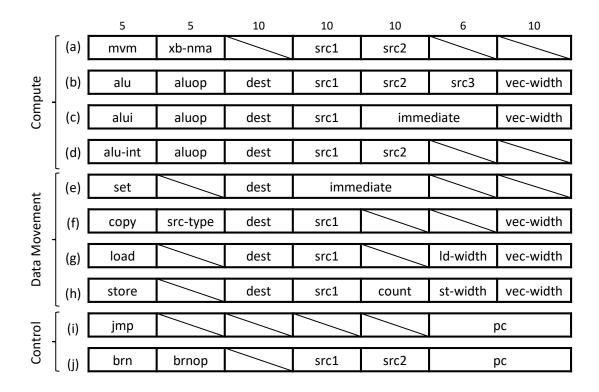

| 3.8  | ISA Encoding of Core Instructions                                                                                                                                                                                                                                                                                                     | 34         |

| 3.9  | ISA Encoding of Tile Instructions                                                                                                                                                                                                                                                                                                     | 36         |

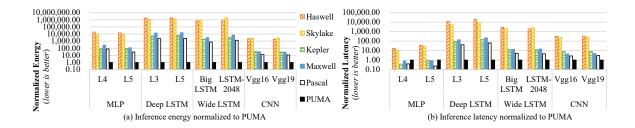

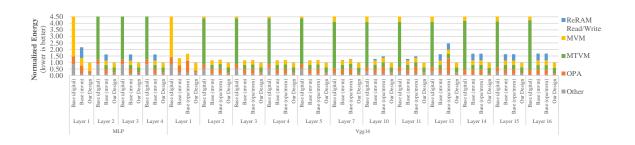

| 3.10 | Inference Energy and Latency Results                                                                                                                                                                                                                                                                                                  | }9         |

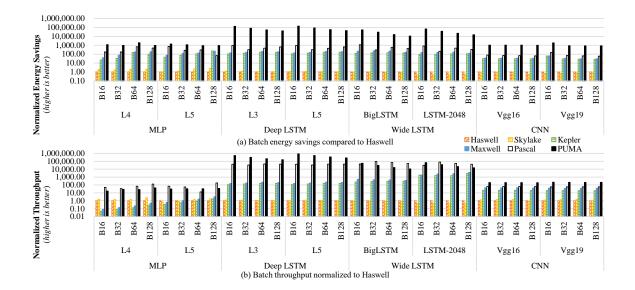

| 3.11 | Batch Inference Throughput and Energy Results                                                                                                                                                                                                                                                                                         | 12         |

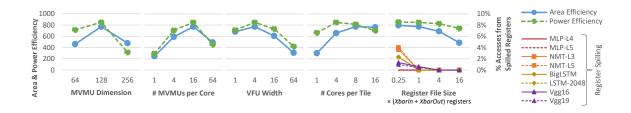

| 3.12 | Design Space Exploration: Tile Area Efficiency in GOPS/s/mm² and Tile Power Efficiency in GOPS/s/W                                                                                                                                                                                                                                    | 14         |

| 3.13 | Inference Accuracy                                                                                                                                                                                                                                                                                                                    | <b>L</b> 7 |

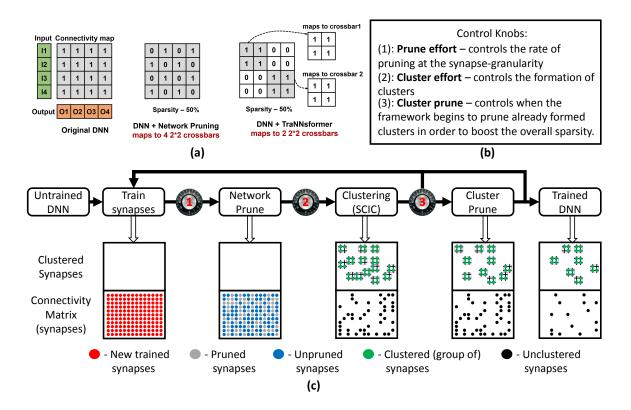

| 4.1  | (a) Illustration of Network pruning and TraNNsformer: pruning leads to irregular sparsity, TraNNsformer forms smaller clusters that are mapped efficiently to crossbars (1/0 only represents presence/absence of connection), (b) Description of control knobs in the framework, (c) Logical flow of TraNNsformer during DNN training | 51         |

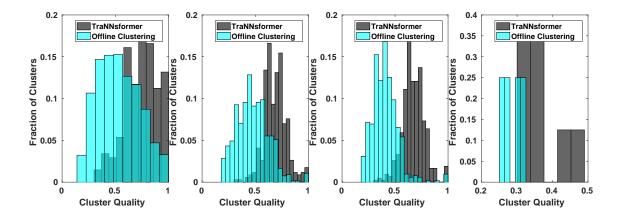

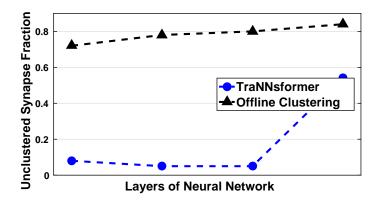

| 4.2  | Comparison of crossbar utilization (cluster quality) between Offline Clustering and TraNNsformer                                                                                                                                                                                                                                      | 31         |

| Figu | re                                                                                                                                                                                                                                                                                                                     | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.3  | Comparison of fraction of unclustered weights between Offline Clustering and TraNNsformer (the data points correspond to the layers of DNN). Note that the last fully connected layer consists of a small fraction of weights $(<1\%)$ , thereby having insignificant effect on overall unclustered synapse comparison |      |

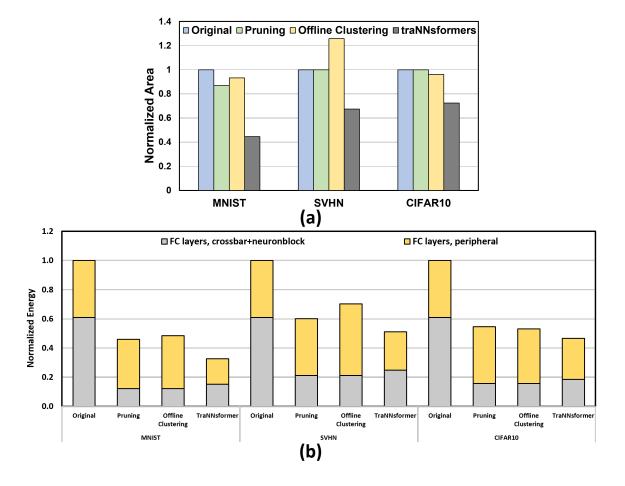

| 4.4  | Comparison of area consumption on crossbar based architecture for different DNN training approaches                                                                                                                                                                                                                    | . 63 |

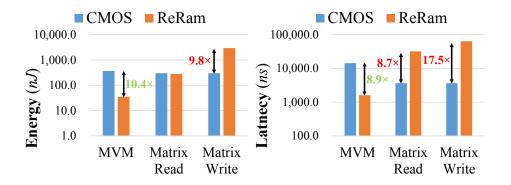

| 5.1  | Comparing CMOS and ReRAM Primitives                                                                                                                                                                                                                                                                                    | . 67 |

| 5.2  | FC Layer Matrix Operations in Crossbars                                                                                                                                                                                                                                                                                | . 70 |

| 5.3  | Bit Slicing OPA to Enhance its Precision                                                                                                                                                                                                                                                                               | . 73 |

| 5.4  | Weight Gradients across Training Steps                                                                                                                                                                                                                                                                                 | . 76 |

| 5.5  | Matrix Computation Unit                                                                                                                                                                                                                                                                                                | . 78 |

| 5.6  | Architecture Overview                                                                                                                                                                                                                                                                                                  | . 82 |

| 5.7  | Convolutional Layer Matrix Operations in Crossbars                                                                                                                                                                                                                                                                     | . 85 |

| 5.8  | Computational graph obtained using TensorBoard for (a) example model (b) example model with PANTHER OPA                                                                                                                                                                                                                | . 88 |

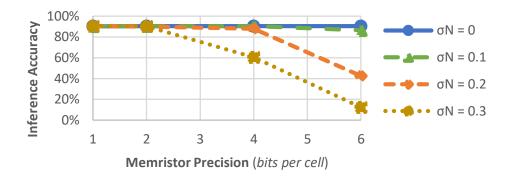

| 5.9  | Impact of Slice Bits and CRS Frequency on Accuracy                                                                                                                                                                                                                                                                     | . 92 |

| 5.10 | Heterogeneous Weight-Slicing                                                                                                                                                                                                                                                                                           | . 93 |

| 5.11 | SGD Energy (high bars are clipped)                                                                                                                                                                                                                                                                                     | . 94 |

| 5.12 | Mini-batch SGD Energy (high bars are clipped)                                                                                                                                                                                                                                                                          | . 94 |

| 5.13 | Execution Time                                                                                                                                                                                                                                                                                                         | . 96 |

| 5.14 | Variant #2 vs. Variant #3                                                                                                                                                                                                                                                                                              | . 97 |

| 5.15 | PANTHER's speedup and energy-efficiency compared to GPU                                                                                                                                                                                                                                                                | . 98 |

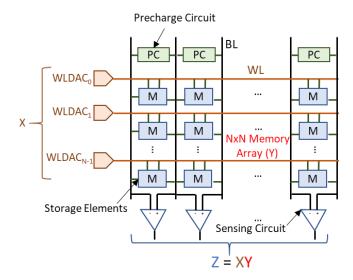

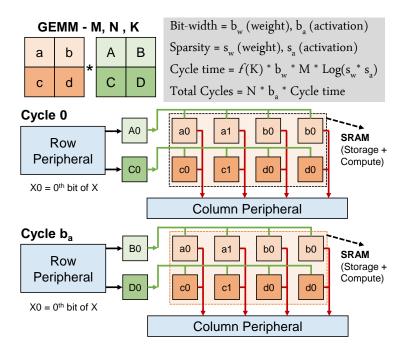

| 6.1  | Illustration of in-memory computing primitive                                                                                                                                                                                                                                                                          | 103  |

| 6.2  | Runtime distribution of tensor core operations (tensorop) compared to other compute operations in RTX 2080 Ti for (a) Transformer, and (b) ResNet-18                                                                                                                                                                   | 105  |

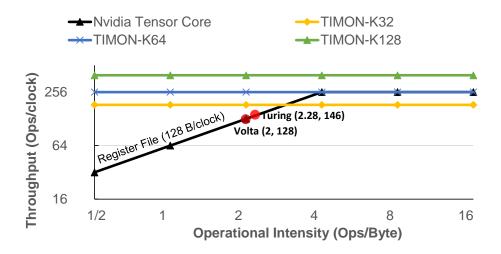

| 6.3  | Roofline of digital CMOS tensor core (Nvidia GPU), and in-memory tensor core (TIMON)                                                                                                                                                                                                                                   | 106  |

| 6.4  | Efficiency of sparse GEMMs on GPGPUs                                                                                                                                                                                                                                                                                   | 108  |

| 6.5  | Abstract view of TIMON's compute unit                                                                                                                                                                                                                                                                                  | 109  |

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Page  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

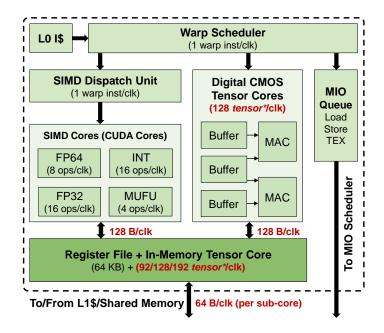

| 6.6  | Nvidia GPGPU Sub-Core [241] enhanced with TIMON (dark green). $tensor$ consists of 2 ops - multiply, add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 111   |

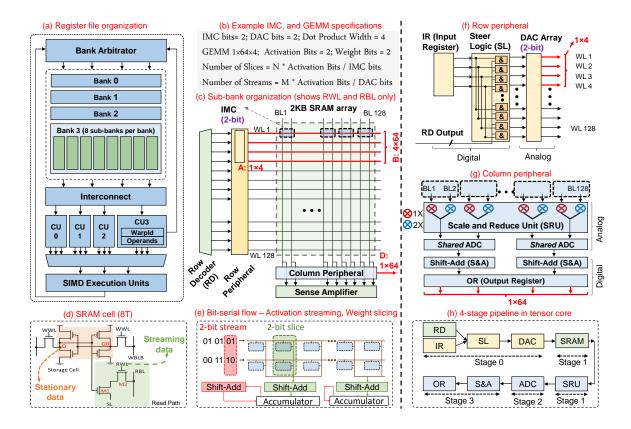

| 6.7  | (a) GPGPU Register File. (b) Sub-bank, and GEMM configurations used for illustration. (c) Organization of a 2KB sub-bank composed of 128 entries/wordlines (WL), and four 4B physical registers i.e. 128 bitlines (BL). Each sub-bank re-purposed to read/write an entry and do in-memory GEMM computation on a matrix stored in SRAM rows, and a matrix stored in row peripheral. (d) 8T SRAM cell showing where the stationary data resides and where streaming data is applied. (e) Bit-serial arithmetic for GEMM with generic bit-width for stationary and streaming data (f) Row peripheral for TIMON. (g) Column peripheral for TIMON. (h) 4-stage pipeline for parallel streams | 112   |

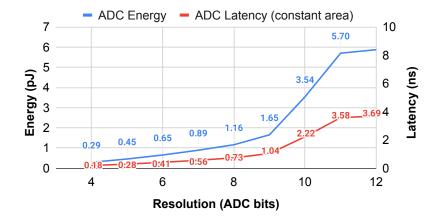

| 6.8  | ADC energy, latency for different bits at 45nm node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 115   |

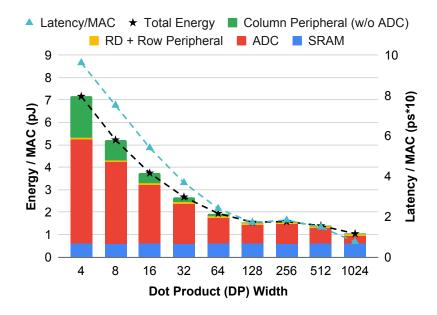

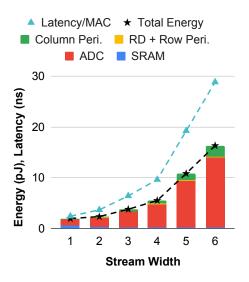

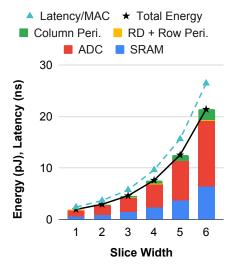

| 6.9  | Impact of DP width on energy, latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 116   |

| 6.10 | Impact of stream,<br>slice widths on energy, latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 117   |

| 6.11 | Modified register mapping for bit-alignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 118   |

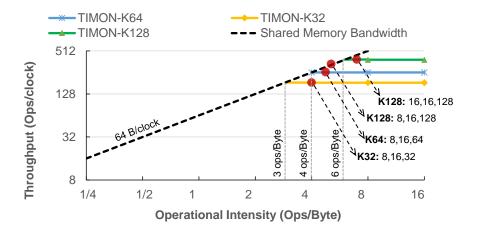

| 6.12 | Roofline of TIMON with respect to shared memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 120   |

| 6.13 | GPGPU warp occupancy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121   |

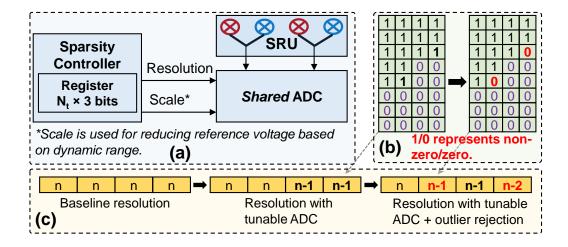

| 6.14 | (a) TIMON's column peripheral with sparsity controller. (b) Illustration of outlier rejection technique. (c) Impact of TIMON's hardware-software codesign on ADC resolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 122   |

| 6.15 | Illustration of outlier rejection methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 123   |

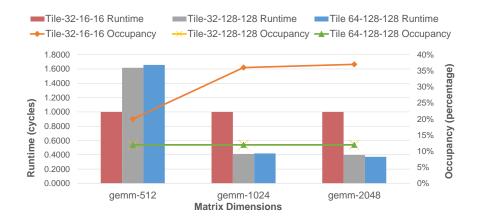

| 6.16 | (a) Comparison of GPGPU runtimes with different TIMON configurations normalized to GPGPU with Turing tensor cores. (b) Runtime distribution of WMMA API between Load, Compute, Store for seven instances in Conv2d-2 benchmark on Turing tensor cores and TIMON configurations. (c) Average runtime distribution on seven instances                                                                                                                                                                                                                                                                                                                                                     | 126   |

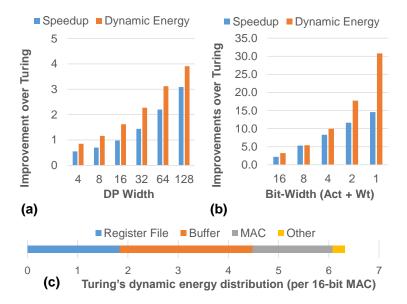

| 6.17 | TIMON's speedup and dynamic energy normalized to Turing tensor core for different (a) DP widths, (b) bit-widths of activation (Act) and weight (Wt). (c) Turing tensor core's dynamic energy distribution for 16-bit MAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C.127 |

| 6.18 | Impact of outlier rejection on column sparsity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 129   |

| 6.19 | Impact of tunable ADC and outlier rejection on (a) ADC resolution, (b) Tensor Core's energy and runtime                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 129   |

## 1. INTRODUCTION

## 1.1 Machine Learning and its Computational Challenges

Machine Learning (ML) is the scientific study of computation models that learn to perform specific tasks without requiring explicit instructions, as defined by Arthur Samuel in 1959. This is inspired from the magnificent ability of the human brain to perform myriad tasks by just learning from the environment. On the contrary, traditional computer programs built for specific purpose exhibit a behavior defined by the hand-crafted heuristics that statically define their behavior. Consequently, the overarching goal of ML has been to achieve human brain-level intelligence.

The past decade has seen a tremendous surge in the usage of the ML algorithms across different application domains such as image and video processing [1,2], speech and language processing [3,4], medical imaging [5], gameplay [6] and robotics [7]. More recently ML algorithms have also superseded human brain capabilities in specific applications, for example Google's AlphaGo [1] and Baidu's DeepSpeech2 [8]. The increasing abilities in terms of accuracy has led to the successful proliferation of ML based personal assistants in commercial products used in day-to-day life such as Siri, Alexa and Google Now.

While these algorithmic feats are remarkable, the ever increasing hardware costs driving these developments are alarming. For instance, the AlphaGo algorithm runs on hundreds of KiloWatts of power which is about four orders of magnitude higher than the human brain. Consequently, the algorithm performance is moving closer to the human brain whereas the hardware cost is moving farther. Furthermore, aspirations have always grown faster than the technology available to satisfy them. To this effect, there is a need to look beyond today's general purpose systems in order to bridge the huge disparity in the hardware costs of ML algorithms and the brain.

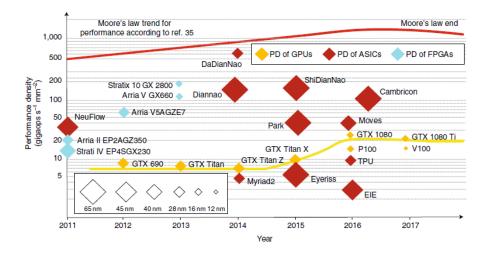

Fig. 1.1. Increase in the performance density of CMOS hardware [13]

## 1.2 Analog In-memory Computing

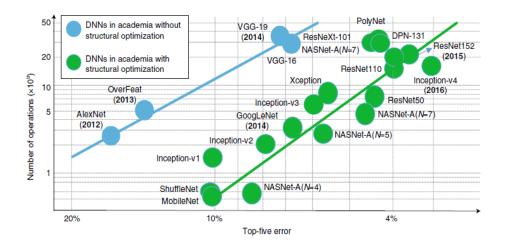

Owing to the high computational needs of ML particularly Matrix Vector Multiplication (MVM) operations, there has been active research in ML accelerator architectures built with CMOS digital technology. Several projects such as DianNao [9], Tensor Processing Unit [10] and Brainwave [11] have proposed ML hardware that achieve orders of magnitude higher efficiency compared to general purpose systems (CPU, GPU). However, the trends in increase in the performance density of digital CMOS hardware (Figure 1.1) and the computation requirements of ML (Figure 1.2), clearly highlight that ML models are growing at a faster rate than conventional CMOS hardware (or digital CMOS). Furthermore, ML workloads tend to be data-intensive and their execution on digital CMOS hardware is typically characterized by high data movement costs relative to compute [12]. To this end, analog in-memory computing using memristive and SRAM technologies have shown tremendous potential owing to their efficient dot product computation capabilities.

Memristive crossbars can store a matrix with high storage density and perform MVM operations with very low energy and latency [14–20]. Each crosspoint in the crossbar stores a multi-bit value in one memristor device, which enables high storage

Fig. 1.2. Increase in the computational requirements of ML models [13]

density [21]. Upon applying an input voltage at the crossbar's rows, we get the MVM result as output current at the crossbar's columns based on Kirchhoff's law. A crossbar thus performs MVM in one computational step – including  $O(n^2)$  multiplications and additions for an  $n \times n$  matrix – which typically takes many steps in digital logic. It also combines compute and storage in a single device to alleviate data movement, thereby providing intrinsic suitability for data-intensive workloads [22, 23]. Several recent works have also demonstrated such in-memory MVM capability in SRAM technology [24, 25]. While SRAM technology has lower storage density compared to memristive technology, its high endurance, reliability and efficient writes makes it an attractive choice for augmenting existing systems such as CPU, GPU with in-memory computing capabilities.

## 1.3 Dissertation Overview

## Thesis Statement

This dissertation proposes an ISA-programmable accelerator architecture built with memristive crossbars for ML inference called PUMA and shows that hybrid

CMOS-memristive technologies can achieve orders of magnitude higher efficiency than CMOS systems (CPUs, GPUs and ASICs) [26]. In addition to that, it also proposes a software optimization called *TraNNsformer* to enable efficient inference of emerging ML workloads namely sparse DNNs [27]. Subsequently, it proposes *PANTHER* which extends the PUMA architecture for performing ML training as well. Lastly, it proposes an in-memory tensor core (*TIMON*) for General Purpose Graphics Processing Unit (GPGPU) to improve the efficiency of conventional architectures for ML workloads.

## Layout

The rest of the dissertation is organized as follows. Chapter 2 discusses the prior works in ML accelerators, software optimization (weight pruning) for ML, and GPGPU tensor cores. Chapters 3 and 4 cover the proposed PUMA accelerator architecture [26,28] and TraNNsformer software optimization [27,29]. Chapter 5 covers the proposed extensions for training - PANTHER [30]. Chapter 6 covers in-memory computing in GPGPU register file - TIMON.

## 2. RELATED WORK AND BACKGROUND

In this section we review the research on ML accelerator architectures, software optimizations for ML, and GPGPU tensor cores and register file. We also look into how the proposed *PUMA*: inference accelerator architecture, *TraNNsformer*: software optimization, *PANTHER*: training accelerator architecture, and *TIMON*: in-memory tensor core distinguish from the related works.

#### 2.1 Inference Accelerator Architectures

Owing to the ever increasing computation demands of machine learning and its growing pervasiveness across application domains, past years have seen significant body of research in accelerators for machine learning. In this section, we review some of these implementations for CMOS Digital, and Memristor-based Analog accelerators. Finally, we discuss the manufacturability and non-ideality concerns associated with memristor technology.

## 2.1.1 CMOS Digital In-/Near-memory Accelerators

Sze et al. [31] provide a thorough survey of the many neural network accelerators and the differences between them. In the digital realm, accelerators can be classified as weight stationary spatial architectures (such as NeuFlow [32], Sankaradas et al. [33], Chakradhar et al. [34], Gokhale et al. [35], Origami [36], and Paer et al. [37]), output stationary spatial architectures (such as Peemen et al. [38], ShiDianNao [39], and Gupta et al. [40]), spatial architectures with no local reuse (such as DianNao [9], DaDianNao [41], and Zhang et al. [42]), and row stationary spatial architectures (such as Eyeriss [43]). Many accelerator designs have also proposed

support for optimizations and features including weight pruning and exploiting sparsity such as in Minerva [44], Cnvlutin [45], EIE [46], SCNN [47], Cambricon-X [48], Chung et al. [49], Pragmatic [50], and CirCNN [51], reducing precision such as in Stripes [52] and YodaNN [53], layer fusing such as in Alwani et al. [54], leveraging stochastic computing such as in Kim et al. [55] and SC-DNN [56], and adaptation to meet QoS and QoR requirements such as ELNA [57]. Accelerators vary in their degree of flexibility, ranging from custom accelerators specialized for a particular field such as Murray et al. [58] and Yazdani et al. [59] to accelerators that are fully programmable via an instruction set architecture such as PuDianNao [60], Cambricon [61], Cambricon-X [48], ScaleDeep [62], and Google's TPU [10]. Besides ASICs, accelerators have also been generated for FPGAs such as in CNP [63], Peemen et al. [38], Zhang et al. [42], DeepBurning [64], Tabla [65], DNNWeaver [66], and Shen et al. [67]. All these works remain in the digital domain, while PUMA focuses on hybrid digital-analog computing.

Chung et al. [11] propose Brainwave, which is a spatial accelerator built with FPGAs. Compared to Brainwave, a PUMA core performs 0.26 million 16-bit ops, equivalent to 1.04 million 8-bit ops, per coalesced MVM instruction. A Brainwave NPU performs 1.3million 8-bit ops per instruction. Therefore, PUMA and Brainwave have comparable control granularity while PUMA has 40.8x higher storage-density (Brainwave Stratix10 estimate).

Near-memory computing using DRAM has been proposed in past accelerators such as Neurocube [68], TETRIS [69], DRISA [70], and RAMANN [71]. PUMA uses non-volatile memristive crossbars for acceleration.

## 2.1.2 Memristor-based Analog In-/Near-memory Accelerators

The use of memristive crossbars for accelerating neural networks has received much attention in recent years [72–75]. Accelerators leveraging memristive crossbars include Hu et al. [76], SPINDLE [77], DNP [78], RENO [79], Memristive Boltz-

mann Machine [80], ISAAC [23], Prime [22], PipeLayer [81], TIME [82], Group Scissor [83], and RESPARC [84]. These accelerators have been demonstrated on several types of networks including BSBs [76], MLPs [77, 79, 82], SNNs [78, 84–87], Boltzman Machines [80], and CNNs [22, 23, 81–83]. Some accelerators support inference only [22, 23, 76, 77, 79, 84] while others also support training [78, 80–82]. NEUTRAMS [88] provides a framework for transforming neural networks to configure such accelerators. These accelerators vary in their degrees of flexibility, but even the most flexible rely on datapath configuration and have only been demonstrated on a few types of networks. PUMA is the first memristor-based accelerator for machine learning inference that is ISA-programmable and general-purpose.

Fujiki et al. [89] propose an ISA-programmable memristor-based accelerator. Their accelerator is a data-parallel accelerator whereas PUMA is a data-flow accelerator with more capability for producer-consumer synchronization. Moreover, their accelerator optimizes crossbars for vector operations in general-purpose workloads whereas PUMA optimizes crossbars for MVM operations prevalent in machine learning and uses digital VFUs for vector operations rather than crossbars.

## 2.1.3 Memristor Manufacturability and Non-ideality

There have been concerns in the community about memristor manufacturability. We distinguish between medium-density embedded memristor applications and high-density storage-class memory (SCM). Memristors in PUMA use 1T1R configuration which have been shown to have good manufacturability [90]. They are very different from SCM, where the selector transistor may be replaced with an in-line two-terminal selector device for higher density which complicates manufacturability. Panasonic formed a joined venture with UMC foundry in 2017 to enable integration of memristors to UMC 40nm CMOS process with first samples planned in 2018 [91]. TSMC also completed development of their own memristor technology that entered risk production in 40nm ULP CMOS process node at the end of 2017 [92].

Memristor technology suffers from non-idealities such as read/write noise, asymmetric non-linearity in conductance vs programming pulses, IR-drop, source and sense resistances; stuck-at-faults; and process variations. These can lead to significant degradation in the classification accuracy [93]. Past research has shown that the iterative nature of DNN training and careful re-training enables recovering the accuracy loss from non-idealities [94–97], faults [98] and variations [99]. Furthermore, PUMA uses low bit-resolution memristor cells to gain higher noise margin for mitigating the accuracy degradation from non-idealities.

## 2.2 Software Optimizations (Weight Pruning)

Weight pruning has been proposed to achieve significant reduction in DNN size, while maintaining the required accuracy [12,100–103]. A reduction in the number of weights at the algorithm level opens up the potential to leverage this weight sparsity for efficient DNN execution at the hardware level. Consequently, this leads to two orthogonal research directions geared towards CMOS architectures 1) specialized accelerators for sparse DNNs, and 2) software transformations. Several specialized accelerators have been proposed to maximize the DNN efficiency for resource and energy constrained platforms [46,48,104–107], which have explored novel techniques to store the sparse matrix for reducing the memory requirements as well as exploiting the weight sparsity to save unnecessary computations. The software transformation approaches have explored techniques to obtain sparsity in a structured or regular manner, such that these sparse DNNs can be executed on CPU, GPU as well as general-purpose ML accelerators [105, 108–113] efficiently.

While the past works on designing specialized accelerators have shown significant improvements for DNN execution on CMOS hardware, these techniques are not amenable to crossbar-based architectures. The separability between storage and computation available on CMOS systems enables designing specialized CMOS accelerators to leverage sparsity. Herein, the sparse matrix can be stored in a compressed format

(in off-chip memory), which can be later decompressed during computations to enable correct computations (in SIMD units). However, a crossbar performs in-memory processing, where the computations are performed by the same crossbar which stores the weight matrix. This does not involve explicit memory fetches for the weight matrix, thereby removing the flexibility to store data in a compressed manner. Further, owing to the difference in the computation nature of CMOS and crosbar-based hardware, the software transformations for CMOS systems are not suitable to MCA systems.

Recently, software transformation approaches for crosbsar-based architectures have been proposed [114–116]. [114] focuses on clustering the synapses after the training process finishes i.e. offline clustering. [115] proposes pruning of convolution layers to reduce the throughput overhead by implementing pruning based on semi-folded mapping scheme. [116] uses the approach of hierarchical clustering to map DNNs on 3D ICs. Trannsformer distinguishes from the prior works as it proposes an integrated training framework for optimizing fully connected layers of DNNs.

## 2.3 Training Accelerator Architectures

Various ReRAM-based training accelerators [81,82] have been proposed, but they rely on expensive serial reads and writes to accomplish weight updates. We avoid these reads and writes by leveraging the in-crossbar OPA operations [117,118], and extending their precision for practical trainability. Our crossbar architecture can be used to enhance existing accelerators.

ReRAM-based accelerators have also been proposed for DNN inference [22, 23, 26, 80], graph processing [119], scientific computing [120], and general purpose data parallel applications [89]. Our work focuses on DNN training.

Analog [121, 122] and DRAM-based [68–70] accelerators have been proposed as alternatives to digital-CMOS accelerators. Our work uses ReRAM as an alternative.

Many accelerators use digital CMOS technology for accelerating DNNs, including those that mainly target inference [43,45,46,48,52,54,57,59,104,123–131] or also target

training [41, 61, 132–135]. Frameworks that assist with designing such accelerators deal with challenges such as power optimizations [44], stochastic computing [55, 56], pruning [49], targeting FPGAs [64–66, 136, 137], and scaling [138].

Many accelerators use digital CMOS technology for accelerating DNNs, including those that mainly target inference [31] or also target training [135]. Our work uses hybrid digital-analog computation based on ReRAM crossbars, not just CMOS.

Recent works have explored training DNNs with reduced precisions in floating-point arithmetic domain such as bfloat16 [139], float8 [140] as well as fixed-point arithmetic domain [141, 142]. While floating-point arithmetic is not amenable to ReRam-based hardware (without modifications), the reductions in fixed-point precision can be exploited in PANTHER by reducing the MCU width (number of slices) to improve training energy and time.

ReRAM technology suffers from imprecise writes due to non-idealities (noise and non-linearity) and manufacturability issues (stuck-at-faults and process variations). However, the iterative nature of DNN training and careful re-training helps recover the accuracy loss from non-idealities [94], faults [98], and variations [143]. Re-training is a fine-tuning process (typically 1 epoch) with insignificant cost compared to training.

### 2.4 GPGPU Tensor Core

Inference Accelerators: Domain-specific architectures for inference have been explored both in industry [10, 144] and academia [31, 43, 129]. Many works also support model compression techniques such as quantization [46, 145, 146], and sparsity [104, 147–152]. Alike Nvidia GPU tensor cores<sup>1</sup>, majority of these accelerators leverage data reuse to overcome the memory bandwidth/energy limitations. However, the key difference lies in the amount of data reuse obtained at the area (thereby power) cost. GPU tensor cores operate at computational intensity of about 2 Ops/Byte (Section 6.3) and consume  $0.21mm^2$  die area per sub-core at 45nm node (Section 6.7.5).

<sup>&</sup>lt;sup>1</sup>leverages data reuse by using local buffers in tensor cores to reduce register file access (Section 6.3).

On the other hand, Eyeriss, a custom architecture, achieves an order of magnitude higher computation intensity, and consumes 5.87 mm<sup>2</sup> die area at 45nm node [153]. The 28× higher area requirement is because the higher data reuse comes at the cost of significantly higher buffer size and computation units. As a result, the smaller area versions of such accelerators incorporated as tensor core in GPGPUs have low data reuse, and are limited by low bandwidth and high energy of GPGPU register file.

Register File Optimizations: Several past works have explored optimizations to reduce dynamic energy and leakage energy in GPGPU register files by caching [154], virtualization [155], emerging memory technologies [156, 157], and fine-grained access control [158]. These techniques reduce energy consumption, but do not improve inference performance.

Past research have also explored compiler optimizations such as register packing [159], and register coalescing [160] to reduce the register file bandwidth requirements for workloads with lower bit-width operands such as 1/2/3 bytes. These techniques can improve inference on quantized workloads, but the improvements obtained are linear at best due to linear reduction in register file accesses with bit-width reduction. Since quantization reduces the number of computations quadratically (bit-serial multiplier [146]), it would be ideal to obtain quadratic benefits in inference performance as well.

GPGPU Tensor Cores: Nvidia GPUs recently introduced tensor cores for inference acceleration in 2018 (Turing [161]). As mentioned before, they suffer from register file bandwidth/energy limitations. Further, existing tensor cores do not offer the required flexibility for model compression techniques. Recently, [162] explored accelerating workloads with *structured* sparity on tensor cores. However, it does not improve the performance on dense GEMMs, or support the more commonly used model compression techniques such as quantization, and *unstructured* sparsity.

TIMON leverages in-memory computing to overcome GPGPU register file bandwidth and energy limitations to achieve higher efficiency compared to existing GPGPU tensor core on dense GEMMs. Further, TIMON enables flexible support for irregular quantization, and unstructured sparsity.

## 3. PUMA - INFERENCE ACCELERATOR ARCHITECTURE

## 3.1 Introduction

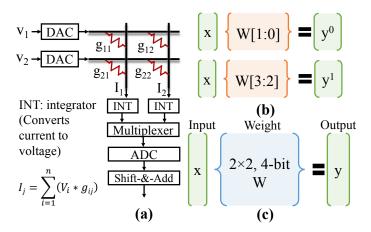

ML workloads tend to be data-intensive and perform a large number of Matrix Vector Multiplication (MVM) operations. Their execution on digital CMOS hardware is typically characterized by high data movement costs relative to compute [12]. To overcome this limitation, memristive crossbars can store a matrix with high storage density and perform MVM operations with very low energy and latency [14–19]. Each crosspoint in the crossbar stores a multi-bit value in one memristor device, which enables high storage density [21]. Upon applying an input voltage at the crossbar's rows, we get the MVM result as output current at the crossbar's columns based on Kirchhoff's law. A crossbar thus performs MVM in one computational step – including  $O(n^2)$  multiplications and additions for an  $n \times n$  matrix – which typically takes many steps in digital logic. It also combines compute and storage in a single device to alleviate data movement, thereby providing intrinsic suitability for data-intensive workloads [22, 23].

Memristive crossbars have been used to build special-purpose accelerators for Convolutional Neural Networks (CNN) and Multi Layer Perceptrons (MLP) [22, 23, 79], but these designs lack several important features for supporting general ML workloads. First, each design supports one or two types of neural networks, where layers are encoded as state machines. This approach is not scalable to a larger variety of workloads due to increased decoding overhead and complexity. Second, existing accelerators lack the types of operations needed by general ML workloads. For example, Long Short-Term Memory (LSTM) [163] workloads require multiple vector linear and transcendental functions which cannot be executed on crossbars efficiently

and are not supported by existing designs. Third, existing designs do not provide flexible data movement and control operations to capture the variety of access and reuse patterns in different workloads. Since crossbars have high write latency [164], they typically store constant data while variable inputs are routed between them in a spatial architecture. This data movement can amount to a significant portion of the total energy consumption which calls for flexible operations to optimize the data movement. Fourth, some designs use deep pipelines [23] which are not suitable for general workloads with control flow. Finally, other designs [22] make optimistic assumptions about precision which may not be suitable for all types of workloads.

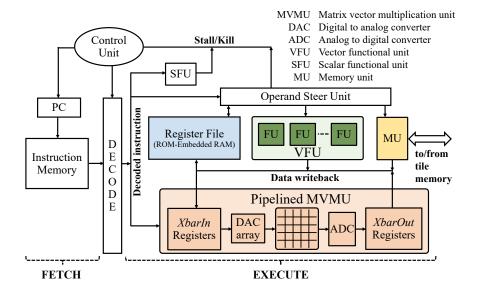

To address these limitations, we present PUMA, a Programmable Ultra-efficient Memristor-based Accelerator. PUMA is a spatial architecture designed to preserve the storage density of memristive crossbars to enable mapping ML applications using on-chip memory only. It supplements crossbars with an instruction execution pipeline and a specialized ISA that enables compact representation of ML workloads with low decoder complexity. It employs temporal SIMD units and a ROM-Embedded RAM [165] for area-efficient linear and transcendental vector computations. It includes a microarchitecture and ISA co-designed to optimize data movement and maximize area and energy efficiency. To the best of our knowledge, PUMA is the first programmable and general-purpose ML inference accelerator built with hybrid CMOS-memristor technology.

A naïve approach to generality is not viable because of the huge disparity in compute and storage density between the two technologies. CMOS digital logic has an order of magnitude higher area requirement than a crossbar for equal output width ( $\sim 20\times$ , see Table 3.5). Moreover, a crossbar's storage density (2-bit cells) is  $160MB/mm^2$ , which is at least an order of magnitude higher than SRAM (6T, 1-bit cell) [23]. A 90mm<sup>2</sup> PUMA node can store ML models with up to 69MB of weight data. Note that the PUMA microarchitecture and ISA are equally suitable to crossbars made from emerging technologies other than memristors such as STT-MRAM [20], NOR Flash [166], etc.

We make the following contributions:

- A programmable and highly efficient architecture exposed by a specialized ISA for scalable acceleration of a wide variety of ML applications using memristive crossbars.

- A detailed simulator which incorporates functionality, timing, and power models of the architecture.

- An evaluation across ML workloads showing that PUMA can achieve promising performance and energy efficiency compared to state-of-the-art CPUs, GPUs, TPU, and application-specific memristor-based accelerators.

#### 3.2 Workload Characterization

This section characterizes different ML inference workloads with a batch size of one. The characteristics are summarized in Table 3.1. The section's objective is to provide insights on the suitability of memristive crossbars for accelerating ML workloads and highlight implications on the proposed architecture.

## 3.2.1 Multi-Layer Perceptron (MLP)

MLPs are neural networks used in common classification tasks such as digit-recognition, web-search, etc. [167, 168]. Each layer is fully-connected and applies a nonlinear function to the weighted-sum of outputs from the previous layer. The weighted-sum is essentially an MVM operation. Equation 3.1 shows the computations in a typical MLP (act is nonlinear):

$$O[y] = act(B[y] + \sum_{x=0}^{n-1} I[x] \times W[x][y])$$

(3.1)

MLPs are simple, capturing the features common across the ML workloads we discuss: dominance of MVM operations, high data parallelism, and use of nonlinear operations.

Table 3.1. Workload Characterization

| Characteristic            | MLP    | LSTM   | CNN     |

|---------------------------|--------|--------|---------|

| Dominance of MVM          | Yes    | Yes    | Yes     |

| High data parallelism     | Yes    | Yes    | Yes     |

| Nonlinear operations      | Yes    | Yes    | Yes     |

| Linear operations         | No     | Yes    | No      |

| Trancendental operations  | No     | Yes    | Yes     |

| Weight data reuse         | No     | Yes    | Yes     |

| Input data reuse          | No     | No     | Yes     |

| Bounded resource          | Memory | Memory | Compute |

| Sequential access pattern | Yes    | Yes    | No      |

### Dominance of MVM

MVM operations are  $O(n^2)$  in space and computational complexity, whereas the nonlinear operations are O(n), where n is the matrix dimension (layer size). MVMs are therefore the dominant operation in MLPs (and other ML workloads). This property makes memristive crossbars suitable for acceleration since they perform analog MVMs with low energy/latency.

### High data parallelism

MLPs (and other ML workloads) have massive amounts of data parallelism. Moreover, practical model sizes are larger than the typical on-chip storage that can be provided by SRAM. For this reason, CMOS implementations suffer from costly DRAM accesses which are particularly taxing due to the absence of data reuse to amortize them. On the other hand, crossbars have extremely high area efficiency which allows deploying many of them on a single chip. Doing so not only captures the high data parallelism in these workloads, but it also provides high storage density to fit models on-chip and bypass costly DRAM accesses.

## Nonlinear operations

In addition to MVM operations, MLPs (and other ML workloads) perform non-linear vector operations (e.g., ReLU). Since these operations cannot be performed in crossbars, an implication on the architecture is the need to provide digital functional units to support them. Such functional units consume significantly more area  $(\sim 20\times)$  than crossbars for equal output width (see Table 3.5). The challenge is to size these units appropriately to provide sufficient throughput without offsetting crossbar area/energy efficiency.

## 3.2.2 Long Short-Term Memory (LSTM)

LSTMs are the state-of-the-art technique for sequence processing tasks like speech processing, language modelling, etc. [163]. Each layer is fully connected and performs linear and nonlinear operations on the weighted-sum of outputs and the previous state. These operations translate into two MVMs followed by multiple (typically four) vector arithmetic operations and (typically four) nonlinear functions. Equations 3.2 to 3.4 show the computations in a typical LSTM:

$$F_{t}[y] = act(B[f] + \sum_{x=0}^{n-1} (H, I)[x] \times W_{f}[x][y])$$

(3.2)

$$C_{t}[y] = \sum_{x=0}^{n-1} (f_{t}[y] \times C_{t-1}[y] + g_{t}[y] \times Cp_{t-1}[y])$$

(3.3)

$$H_{t}[y] = \sum_{x=0}^{n-1} (h_{t}[y] \times C_{t}[y])$$

(3.4)

To the best of our knowledge, PUMA is the first memristor-based accelerator demonstrated with LSTMs.

## Linear and transcendental operations

Unlike MLPs, LSTMs also perform linear vector operations. Moreover, the typical nonlinear vector operations in LSTMs are transcendental (e.g. tanh, sigmoid). Sup-

porting these operations has the same implication on the architecture as discussed in Section 3.2.1 for nonlinear operations. Transcendental operations are particularly challenging due to their high complexity.

## Weight reuse

Another key distinction of LSTMs compared to MLPs is data reuse. LSTM inputs consist of a sequence of vectors processed across multiple time-steps with the same weights. This feature benefits CMOS architectures by amortizing DRAM accesses for loading weights, but is not advantageous to memristive crossbars. That said, the scope of weight reuse in LSTMs is only over a few inputs so the workload remains memory-bound. It still suffers in CMOS hardware from insufficient amortization of DRAM accesses.

## 3.2.3 Convolutional Neural Network (CNN)

CNNs are widely used for image recognition and classification [169]. They typically include several convolutional, pooling, and response normalization layers. A convolution layer consists of weight kernels strided across the input image in a sliding window fashion. It exhibits a non-sequential memory access pattern since a window of the input consists of parts of the input image from different rows. Equation 3.5 shows the computations in a typical convolutional layer of a CNN:

$$O[m][x][y] = act(B[m] + \sum_{i=0}^{R-1} \sum_{j=0}^{S-1} \sum_{k=0}^{C-1} I[k][Ux+i][Uy+j] \times W[m][k][i][j])$$

(3.5)

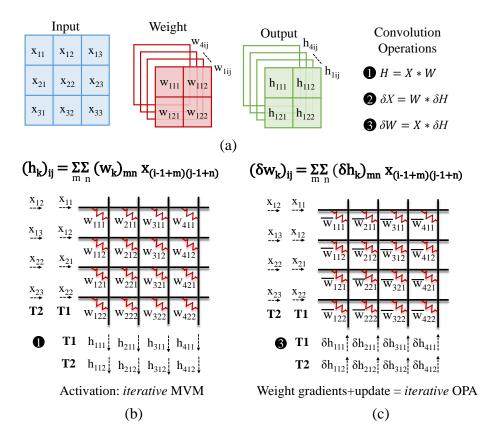

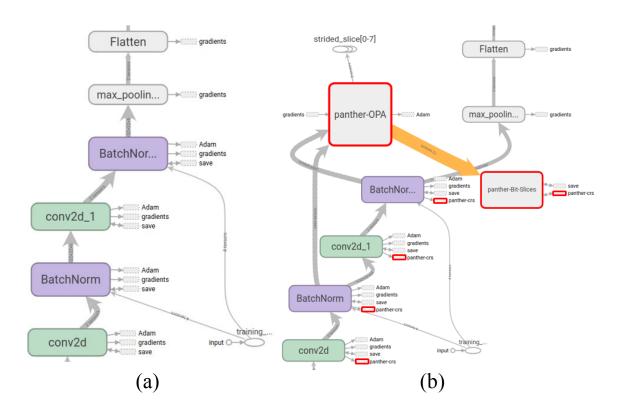

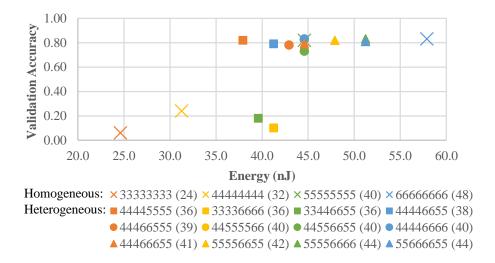

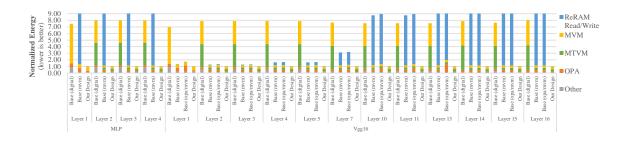

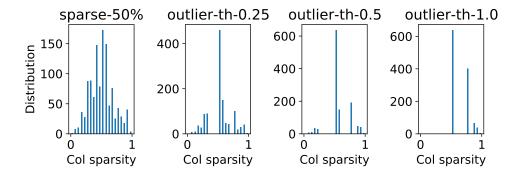

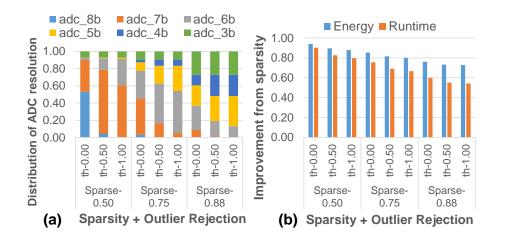

## Input reuse and compute intensity