## PRACTICAL AND RELIABLE WIRELESS POWER SUPPLY DESIGN FOR LOW POWER IMPLANTABLE MEDICAL DEVICES

by

**Christopher John Quinkert**

#### **A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical and Computer Engineering West Lafayette ,Indiana December 2020

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

### Dr. Pedro Irazoqui, Chair

Department of Electrical and Computer Engineering

#### **Dr. Sunil Bhave**

Department of Electrical and Computer Engineering

## **Dr. Byunghoo Jung**

Department of Electrical and Computer Engineering

### **Dr. Scott Sudhoff**

Department of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

I dedicate this work to my family members, whose examples were the motivation for me to push myself to continue school beyond my undergraduate degree.

### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Pedro Irazoqui, for his guidance, knowledge, and genuine care with which he has given me through the course of my 7 years in his lab. His ability to direct, motivate, and support my efforts throughout my time as a graduate student was more important than anything else. I would like to thank my committee members, Dr. Sunil Bhave, Dr. Byunghoo Jung, and Dr. Scott Sudhoff for their direction, feedback, and support of my research and academic pursuits in the classroom.

In addition, I owe a great deal of gratitude to the many members of the Center for Implantable Devices over the years in the support of my work, including, but not limited to, Dr. Kyle Thackston, Jay Shah, Dr. Dan Pederson, Dr. Jesse Somann, Dr. Muhammad Abdullah Arafat, Dr. Jack Williams, Dr. Henry Mei, Dr. Hansraj Bhamra, Johson Tsai, Dr. Quan Yuan, Dr. Rebecca Bercich, Dr. Steven Lee, Dr. Matthew Ward, Dr. Ranajay Mandal, Kelsey Bayer, Kelsey McNulty, Kaitlyn Neihouser, Curtis Slaughbaugh, Grant Wang, Vivek Ganesh, Brett Collar, Georgia Lawlor, and Ethan Biggs. I would like to especially thank Dr. Kyle Thackston and Jay Shah for providing guidance in project work as well as keeping me sane while in the laboratory. In addition, I would not have been able to have successfully utilized lab resources or learned proper project and time management without the training and guidance provided by Gabriel Albors.

I would like to thank my family - my mother, my father, my brother, my grandmother, my uncle and godfather Bob, my aunt Karen, and my godmother MaryEllen - for their constant love, guidance, and support in all of the tough times while finishing my degree. Finally, I would like to thank my fiancée, Georgia, for sticking with me during the entirety of my degree and truly being the only thing keeping me going through to the end; it would not have been possible without you.

# TABLE OF CONTENTS

| LIST             | OF TABLES                                                      | 7  |

|------------------|----------------------------------------------------------------|----|

| LIST OF FIGURES  |                                                                |    |

| LIST OF ACRONYMS |                                                                |    |

| ABST             | RACT 1                                                         | 5  |

| 1. II            | NTRODUCTION 1                                                  | 6  |

| 1.1              | Inductive Wireless Power 1                                     | 6  |

| 1.2              | Resonant Cavity Wireless Powering Background 1                 | 7  |

| 1.3              | Turn-On Transients In Dynamic Impedance Elements 1             | 7  |

| 1.4              | Battery Integration                                            | 8  |

| 2. W             | IRELESS POWER DEVLIERY AND IMPLANTABLE DEVICE DESIGN 1         | 9  |

| 2.1              | Device to Be Powered: The Bionode 1                            | 9  |

| 2.2              | Powernode: Static Impedance Design                             | 1  |

| 2.3              | Resonant Cavity Dynamic Impedance Matching 2                   | 3  |

| 2.4              | Resonant Cavity Frequency Tracking                             | 7  |

| 2.5              | Dynamic Impedance Matching Circuits and Elements               | 8  |

| 2.6              | Experimental Results                                           | 4  |

| 2.7              | Summary                                                        | 9  |

| 2.8              | Turn-On Transients Challenges                                  | 9  |

| 3. N             | OVEL COIL-TO-COIL TRANSIENT TURN-ON POWER REDUCTION SOLUTION 4 | ·1 |

| 3.1              | Potential Coil Configurations and Selection                    | ·1 |

| 3.2              | Circuit Topology                                               | -2 |

| 3.3              | Measured Results                                               | .4 |

| 3.4              | Summary 4                                                      | .6 |

| 4. A             | SIC FOR FLEXIBLE IMPLANTABLE DEVICES WITH BATTERY AND WIRELES  | S  |

| POW              | ER                                                             | .7 |

| 4.1              | Power Conversion Topology Selection 4                          | .7 |

| 4.2              | General NIBB Converter Concerns                                | 1  |

| 4.3              | Power Switch Sizing and Driving                                | 3  |

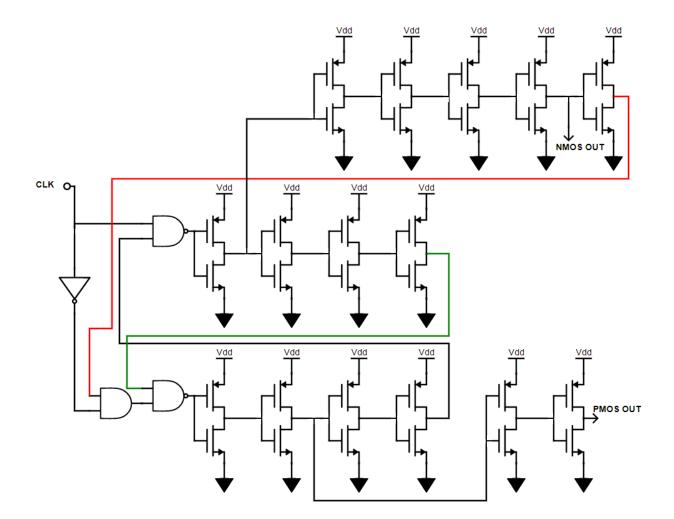

| 4.4              | Power Switch Body Bias                                         | 5  |

| 4.5        | High Voltage Selection                  |  |  |  |

|------------|-----------------------------------------|--|--|--|

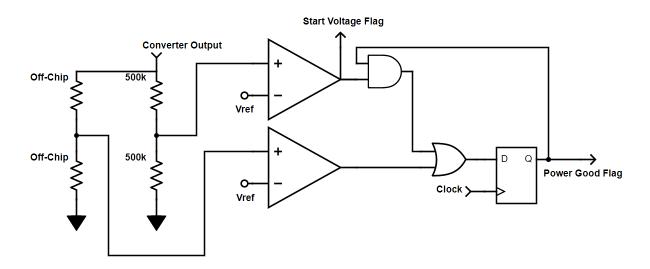

| 4.6        | Input and Output Voltage "Binning" 58   |  |  |  |

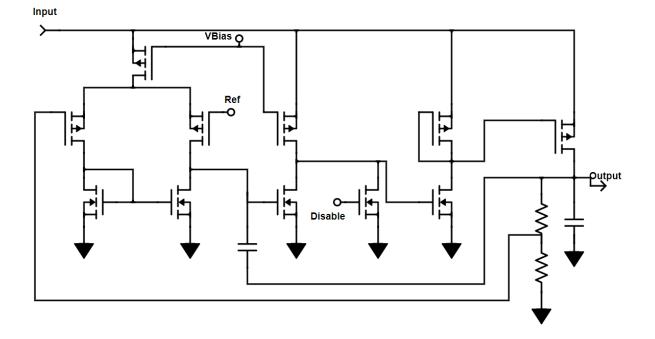

| 4.7        | Comparator Selection and Design         |  |  |  |

| 4.8        | Start-up and Soft Start                 |  |  |  |

| 4.9        | Output LDO                              |  |  |  |

| 4.10       | Combining PWM and PFM65                 |  |  |  |

| 4.11       | Digital Core And Signal Generation      |  |  |  |

| 4.12       | Duty Cycle Determination                |  |  |  |

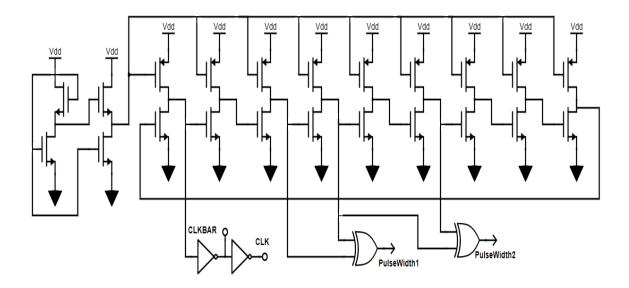

| 4.13       | Non-Overlapping Signals                 |  |  |  |

| 4.14       | PFM                                     |  |  |  |

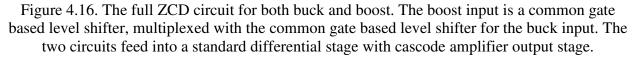

| 4.15       | ZCD Design                              |  |  |  |

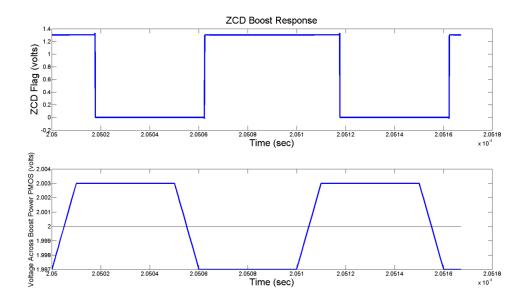

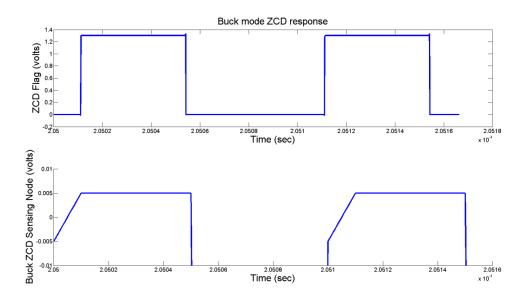

| 4.16       | ZCD Simulation Results                  |  |  |  |

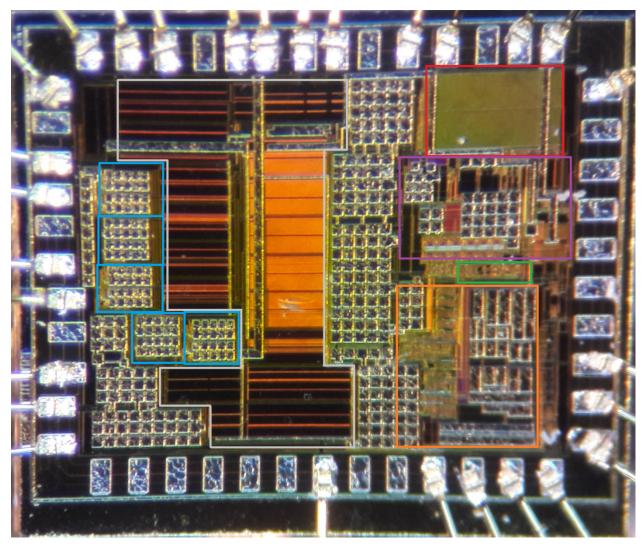

| 4.17       | Fabricated Chip and Measurement Results |  |  |  |

| 4.18       | Discussion                              |  |  |  |

| 4.19       | In Vivo Test of Device                  |  |  |  |

| 5. CO      | ONCLUSIONS AND FUTURE WORK              |  |  |  |

| 5.1        | Conclusions                             |  |  |  |

| 5.2        | Future work                             |  |  |  |

| REFERENCES |                                         |  |  |  |

| VITA       |                                         |  |  |  |

## LIST OF TABLES

| Table 4.1. The description of the operation mode and duty cycle for every input and output voltage bin case                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.2. A comparison of state of the art ZCD circuits. *Estimated from micrograph                                                                                                                                                                          |

| Table 4.3. A table detailing the state of the art in NIBBC topologies from various process nodes.<br>*estimate from Photovoltaic cell range and LiPo Battery Range, ** estimate from specifications,<br>*** estimate from micrograph, ****estimate from plots |

## LIST OF FIGURES

Figure 2.1. A Bionode assembled at the coil and PCB level (left), and a Bionode fully packaged in a hermetically sealed glass case with electrodes, ready for implantation (right) [19]......20

Figure 2.6. Plot of reflection  $|S_{11}|^2$  versus frequency measured for the cavity with a vector network analyzer. A rat "phantom" mimicking the electrical properties of a rat sized at 280-300g is moved to various radii (r) in the cavity. The value  $f_o$  can be determined by the frequency at which minimum reflection occurs. It is shown that  $f_o$  decreases as an animal moves inward...... 25

Figure 2.11. Transformation of static J-inverter impedance matching to include a parallel changing capacitive element to track with changes in  $f_o$ . The parallel capacitive network includes the capacitor bank as well as series capacitor to limit the capacitance seen to reduce step size and allow for finer tuning. 29

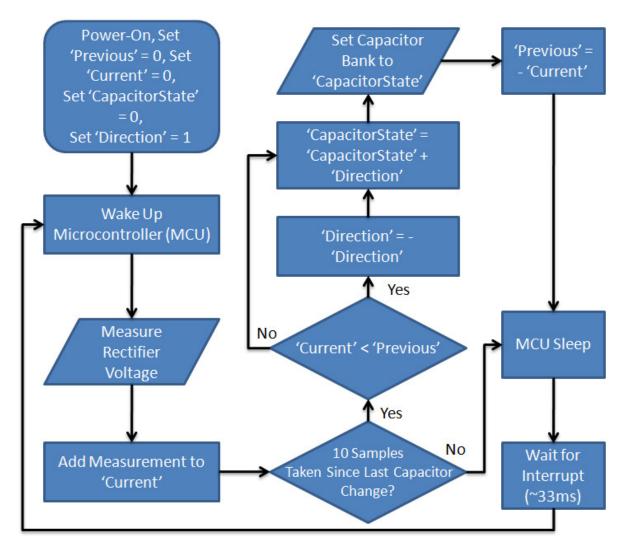

Figure 2.13. The algorithm implemented by the Powernode microcontroller. The device wakes up for small increments to save power and measure the rectified voltage ten times. Next, the capacitance of the bank is increased. Ten more measurements are taken. If the rectified voltage is lower, the capacitance increment direction is flipped and the capacitance is changed in this direction. If the voltage is higher, the direction remains the same and the capacitance is changed in the same direction. After each set of operations, the device is put to sleep to save power. ..... 32

Figure 2.18. Plot of power transfer efficiency percentage for an implant positioned at various radii in coil orientation "A". The cases shown include when the device has both frequency tracking and dynamic IM ("Z Matching"), no improvements where the implant is statically tuned to 345.52 MHz, and no improvements where the implant is statically tuned to 344.11 MHz. .... 37

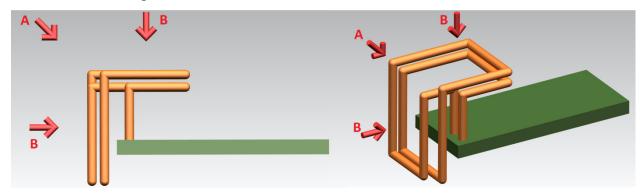

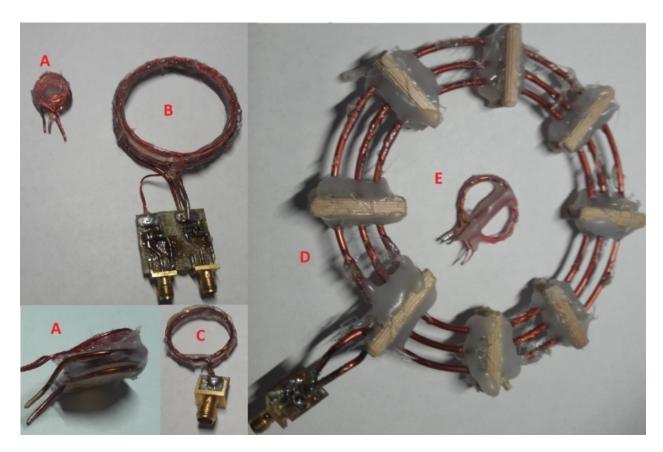

Figure 3.1. In the first test setup, transmit device B's two coils couple at different frequencies to receive device A's two coils. In the second test setup, transmit device D's coil couples at two frequency tones to receive device A's two coils, where A's first coil is tuned to first frequency, and A's second coil is tuned to the second frequency. In the third setup, transmit device D's coil couples to receive device E's two coils at the same single frequency. Device E contains two halfmoon coils with one being a wider band, low quality factor coil, and the other being a narrower band, high quality factor coil. 42

Figure 3.2. A schematic of the updated Powernode utilizing a similar circuit as before, but including two varactors as tunable capacitors. DC voltages applied to either side of the capacitors are AC-decoupled to prevent impedance contributions at high frequency. The LDO and switched capacitor circuits are omitted from this diagram purely for aesthetic purposes and readability. . 43

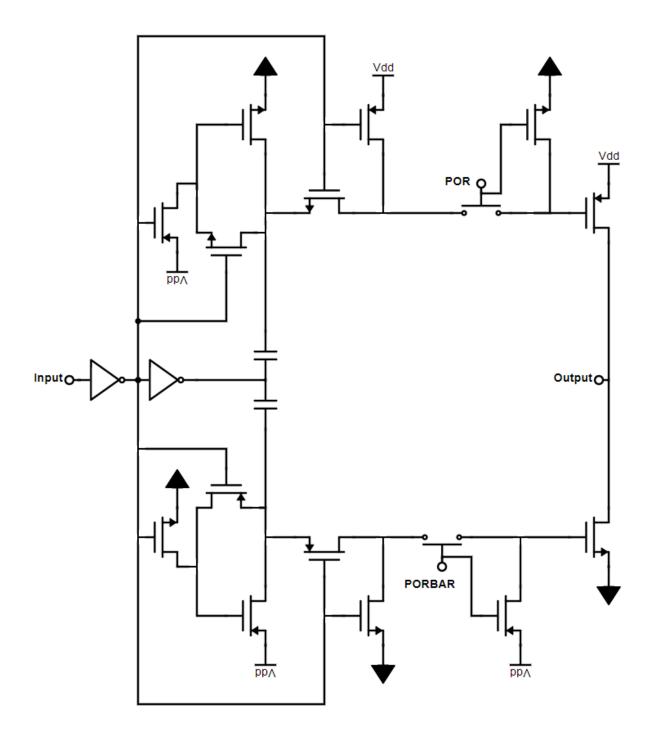

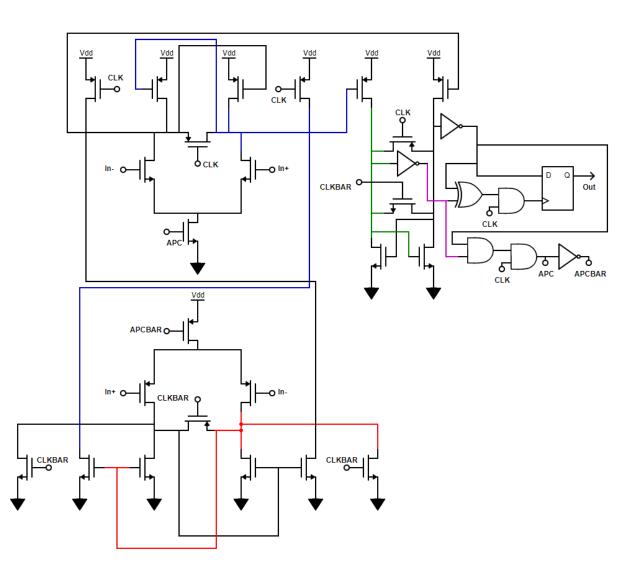

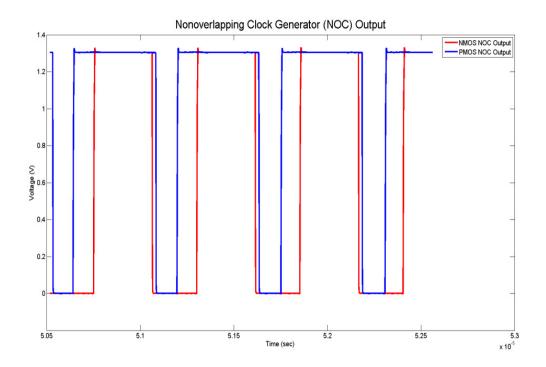

Figure 4.12. A standard topology for generating two non-overlapping clocks for the NIBBC to eliminate any time where the power NMOS and PMOS would be on and conducting at the same time. The clocks from this circuit drive the inputs of the gate drivers for the power switches....70

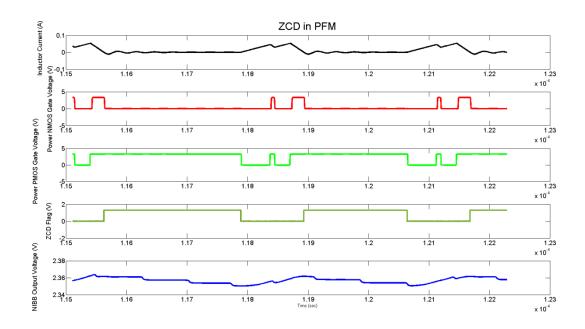

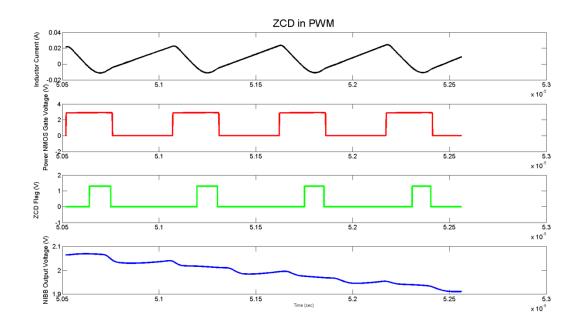

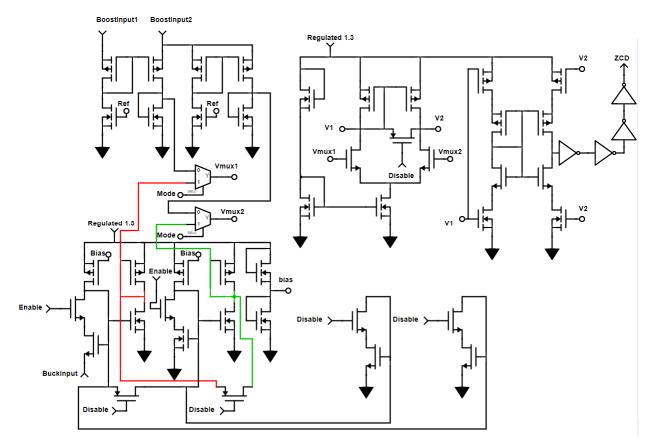

Figure 4.14. Proper buck operation of the ZCD in PFM mode. Upon two cycles of charging and discharging, the inductor is allowed to discharge to 0mA, prompting the ZCD flag to rise. The power NMOS is put in cutoff until the converter output falls to the desired regulated level.......74

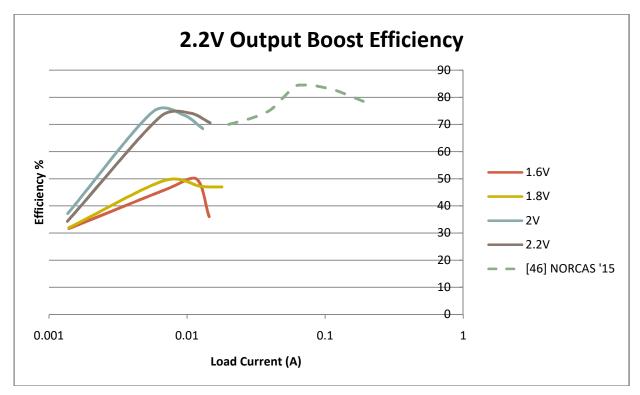

| Figure 4.28. Plot of the measure efficiency for 2.1V converter output in short mode for various input voltages                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

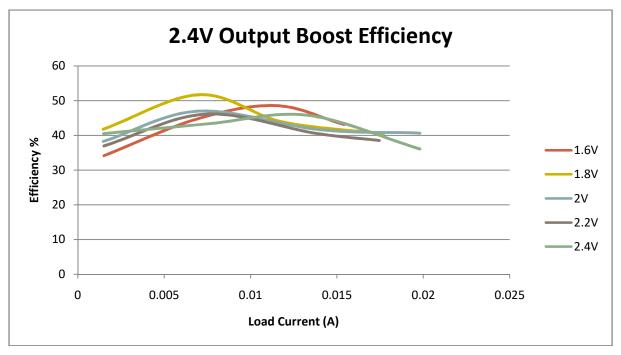

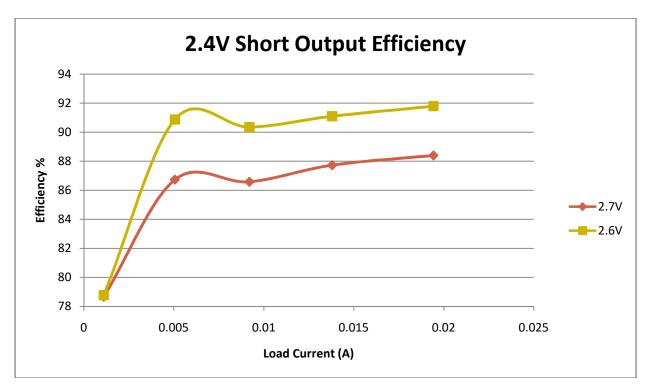

| Figure 4.29. Plot of the measure efficiency for 2.4V converter output in short mode for various input voltages                                                 |

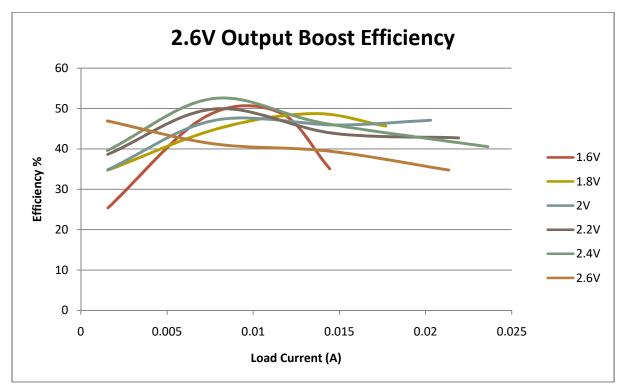

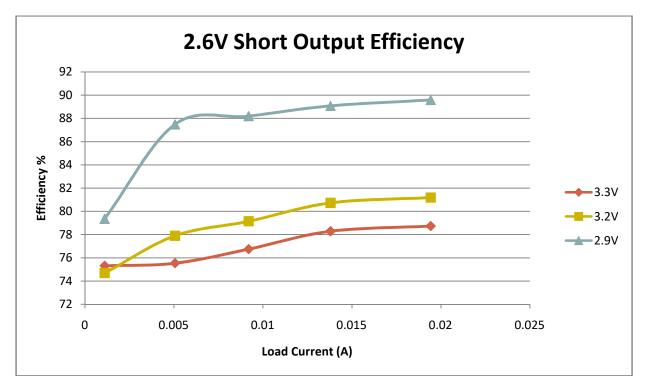

| Figure 4.30. Plot of the measure efficiency for 2.6V converter output in short mode for various input voltages                                                 |

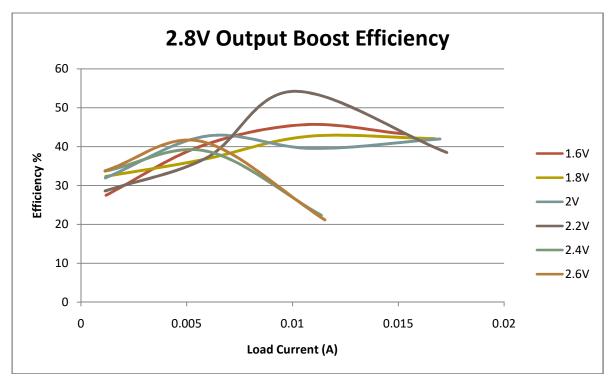

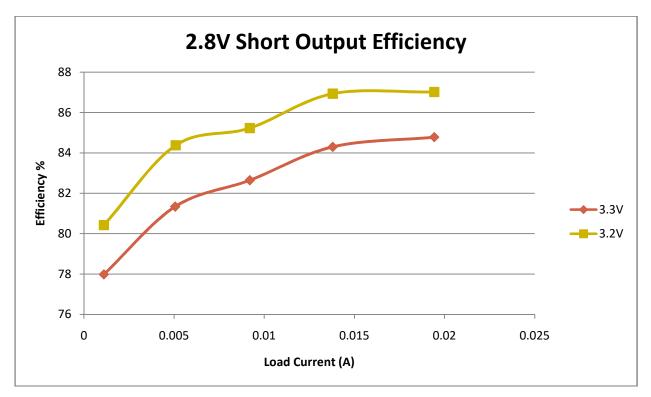

| Figure 4.31. Plot of the measure efficiency for 2.8V converter output in short mode for various input voltages                                                 |

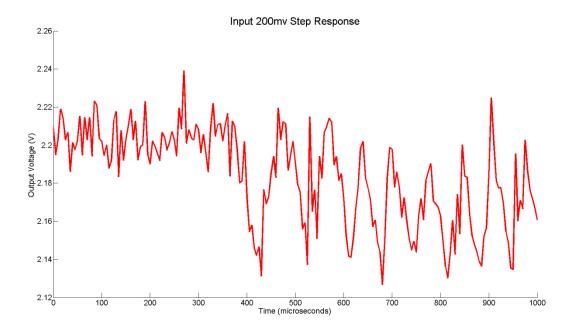

| Figure 4.32. Plot of the output voltage of the converter in response to a 200mV step response from 3.3V to 3.1V over the course of 395us to 405us              |

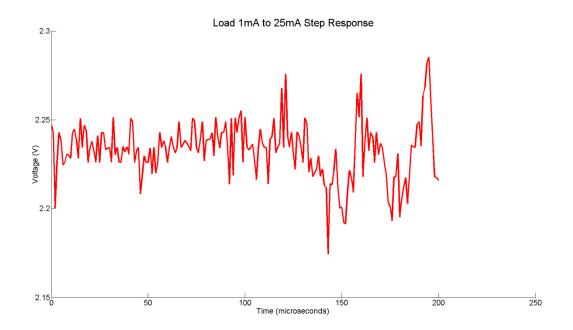

| Figure 4.33. Plot of the output voltage of the converter in response to a 24mA output current step response from 1mA to 25mA over the course of 135us to 145us |

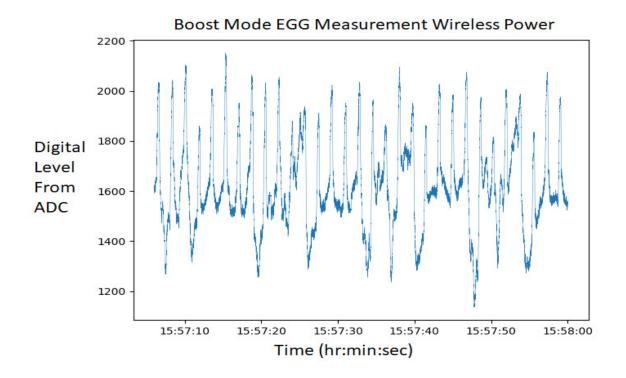

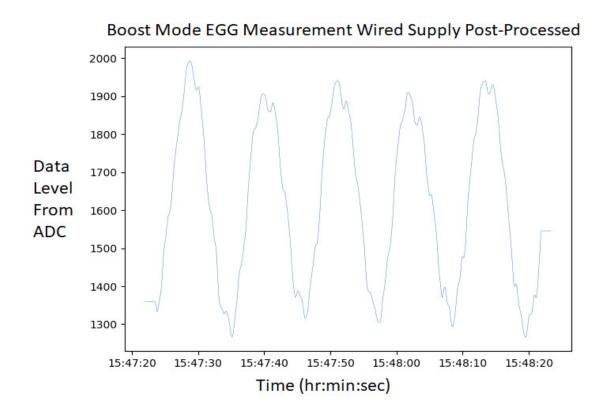

| Figure 4.34. Plot of EGG in a rat with 12-bit ADC on Bionode operating from boost mode NIBB powered by wireless power                                          |

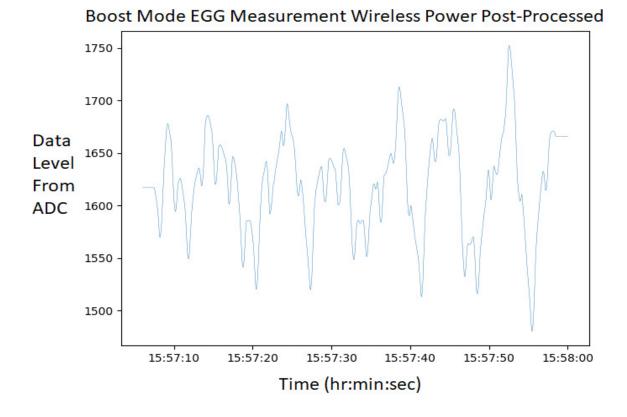

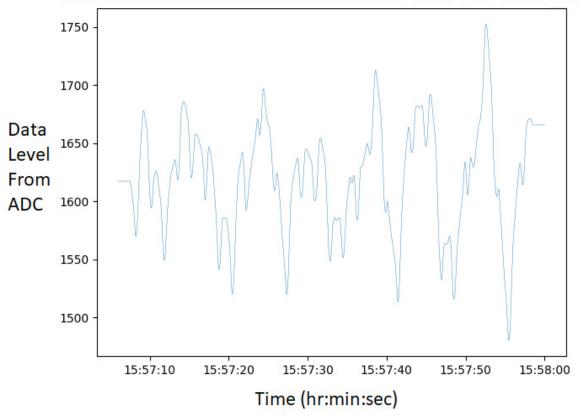

| Figure 4.35. Three second moving window average filter of EGG from data in Fig 4.34                                                                            |

| Figure 4.36. Plot of EGG in a rat with 12-bit ADC on Bionode operating from boost mode NIBB powered by wired wall supply power                                 |

| Figure 4.37. Three second moving window average filter of EGG from data in Fig 4.36                                                                            |

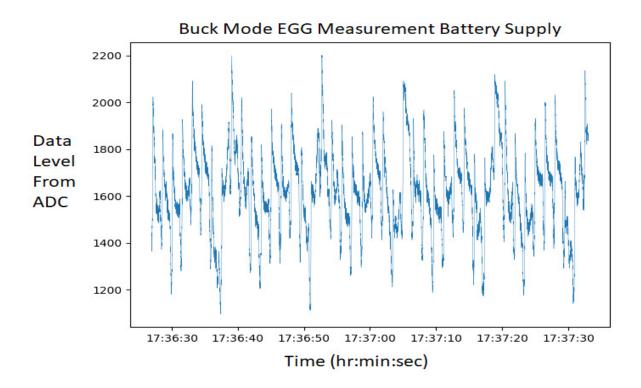

| Figure 4.38. Plot of EGG in a rat with 12-bit ADC on Bionode operating from buck mode NIBB powered by a 3V rechargeable lithium battery                        |

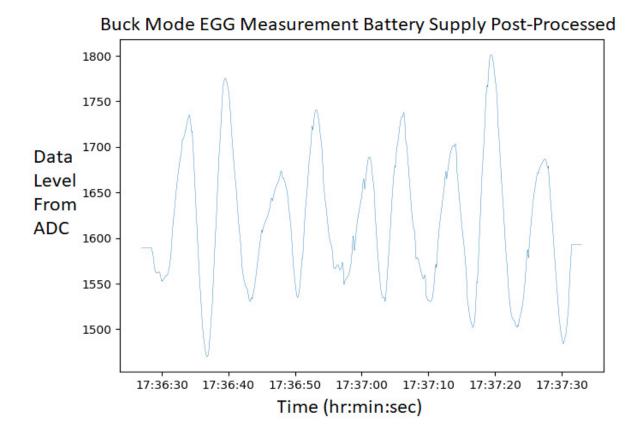

| Figure 4.39. Three second moving window average filter of EGG from data in Fig 4.38                                                                            |

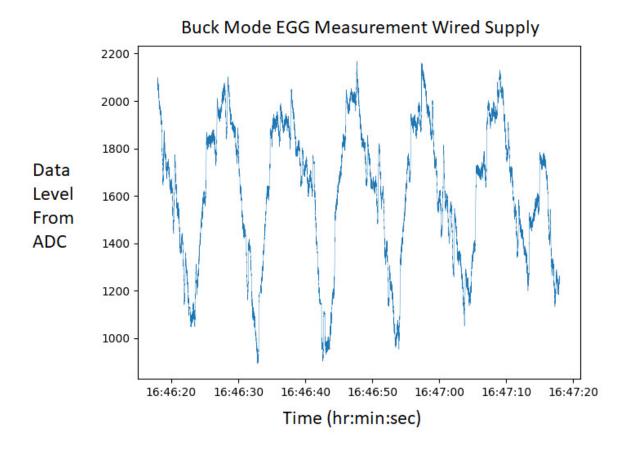

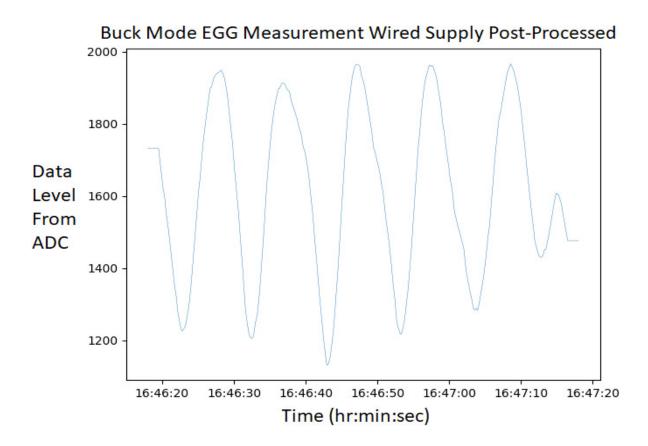

| Figure 4.40. Plot of EGG in a rat with 12-bit ADC on Bionode operating from buck mode NIBB powered by wired wall supply power                                  |

| Figure 4.41. Three second moving window average filter of EGG from data in Fig 4.40 101                                                                        |

## LIST OF ACRONYMS

| AC             | Alternating Current                         |

|----------------|---------------------------------------------|

| ADC            | Analog-to-Digital Converter                 |

| ASIC           | Application Specific Integrated Circuit     |

| BGR            | Bandgap Reference                           |

| CMOS           | Complimentary Metal Oxide Semiconductor     |

| DAC            | Digital-to-Analog Converter                 |

| DC             | Direct Current                              |

| EGG            | Electrogastrogram                           |

| ESR            | Equivalent Series Resistance                |

| $\mathbf{f}_0$ | Resonant Frequency                          |

| FCC            | Federal Communications Commission           |

| FPGA           | Field-Programmable Gate-Array               |

| HFSS           | High Frequency Structure Simulator          |

| High-Q         | High Quality Factor                         |

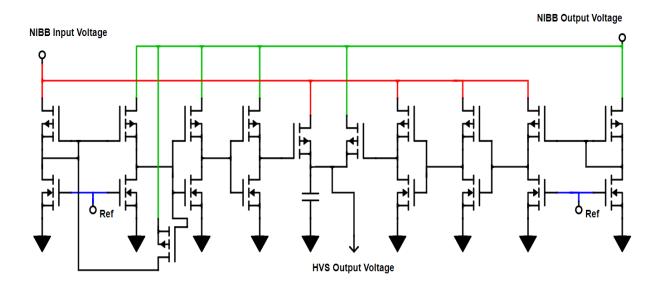

| HVS            | High Voltage Selector                       |

| IC             | Integrated Circuit                          |

| IM             | Impedance Matching                          |

| ISM            | Industrial, Scientific, and Medical         |

| LC             | Inductor and Capacitor                      |

| LDO            | Low-Dropout                                 |

| Low-Q          | Low Quality Factor                          |

| MIM            | Metal-Insulator-Metal                       |

| MOSFET         | Metal Oxide Silicon Field Effect Transistor |

| NIBB           | Non-Inverting Buck-Boost                    |

| NIBBC          | Non-Inverting Buck-Boost Converter          |

| NMOS           | N-Type Metal Oxide Semiconductor            |

| NOC            | Non-Overlapping Clock                       |

| PCB            | Printed Circuit Board                       |

| PFM            | Pulse Frequency Modulation                  |

|                |                                             |

| PLL   | Phase Locked Loop                       |

|-------|-----------------------------------------|

| PMIC  | Power Management Integrated Circuit     |

| PMOS  | P-Type Metal Oxide Semiconductor        |

| POR   | Power-On-Reset                          |

| PTE   | Power Transfer Efficiency               |

| PVT   | Process-Voltage-Temperature             |

| PWM   | Pulse Width Modulation                  |

| RF    | Radio Frequency                         |

| RLC   | Resistor, Inductor, and Capacitor       |

| SAR   | Successive-Approximation-Register       |

| SEPIC | Single-Ended Primary-Inductor Converter |

| VNA   | Vector Network Analyzer                 |

| WPT   | Wireless Power Transfer                 |

| ZCD   | Zero Current Detector                   |

### ABSTRACT

Implantable wireless devices are used to treat a variety of diseases that are not able to be treated with pharmaceuticals or traditional surgery, These implantable devices have use in the treatment of neurological disorders like epilepsy, optical disorders such as glaucoma, or injury related issues such as targeted muscle reinnervation. These devices can rely upon harvesting power from an inductive wireless power source and batteries. Improvements to how well the devices utilize this power directly increase the efficacy of the device operation as well as the device's lifetime, reducing the need for future surgeries or implantations.

I have designed an improvement to cavity resonator based wireless power by designing a dynamic impedance matching implantable power supply, capable of tracking with device motion throughout a changing magnetic field and tracking with changing powering frequencies. This cavity resonator based system presents further challenges practically in the turn-on cycle of the improved device.

I further design a coil-to-coil based wireless power system, capable of dynamically impedance matching a high quality factor coil to optimize power transfer during steady state, while also reducing turn-on transient power required in dynamic systems by utilizing a second low quality factor coil. This second coil has a broadband response and is capable of turning on at lower powers than that of the high quality factor coil. The low quality factor coil powers the circuitry that dynamically matches the impedance of the high quality factor coil, allowing for low power turn on while maintaining high power transfer at all operating frequencies to the implantable device.

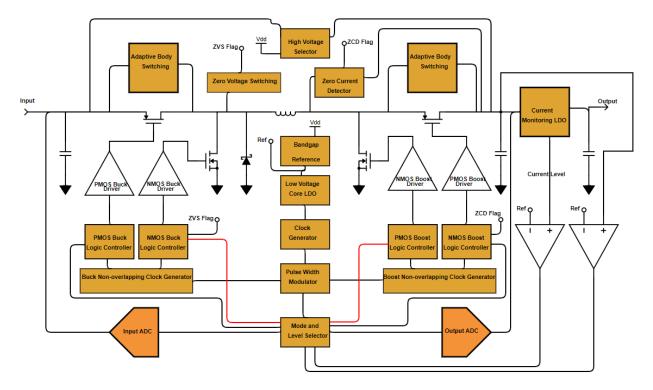

Finally, an integrated circuit is designed, fabricated, and tested that is capable of smoothly providing regulated DC power to the implantable device by stepping up from wireless power to a reasonable voltage level or stepping down from a battery to a reasonable voltage level for the device. The chip is fabricated in 0.18um CMOS process and is capable of providing power to the "Bionode" implantable device.

### 1. INTRODUCTION

Miniature implantable devices in animal models have long been a necessity for researchers looking to conduct long term physiological and behavioral studies in small freely moving animals. Many studies are done using devices that have a transcutaneous link like a headstage or skin cap, but these strategies require tethering the animal to some external wire or cable [1]. In an effort to allow these animals to freely move about their inhabited environment to conduct behavior studies, researchers have turned to wireless implantable devices to this end [1][2]. Within the realm of wireless implantable devices, powering the devices is a serious challenge [3]. Currently, devices tend to be powered by batteries [4-6], bioenergy harvesting [7, 8], or inductive coupling [9, 10]. Batteries by themselves provide stable power to implants, but they have the major issue of limited lifetime, which results in longer animal studies being impossible. Bioenergy harvesting tends to allow for devices with very small power budgets to operate, but devices performing complex functions, such as biopotential recording at high sampling rates and electrical stimulation at higher currents, require much higher continuous powering levels than can typically be provided by energy harvesting [11]. Inductive coupling provides a wireless power transfer (WPT) method that allows for longer lifetime implants with higher powering requirements[12, 13].

#### 1.1 Inductive Wireless Power

Traditionally, implantable devices have been wirelessly powered using a coil-to-coil near field methodology where one coil external to the host animal is excited to create a magnetic field, which is then collected by a coil on the implanted device [12-14]. This approach, however, is very sensitive to the alignment and distance between the two coils, limiting the amount of area and orientation that an animal can be allowed to freely move about [13]. In recent years, large chambers called resonant cavities have been developed to both provide housing for small rodents as well as deliver wireless powering with midfield powering to devices implanted within the animal [14, 15]. These resonant cavities provide a good means of wireless powering for devices with higher power consumption than most implants currently used, while still not exceeding specific absorption rate (SAR) that the FCC standards deem as dangerous to tissue [1, 16, 17].

To optimize WPT within these resonant cavities, the cavity must be excited with an alternating current waveform at its resonant frequency ( $f_o$ ). The resonant frequency of cavity structures is determined by the shape of the structure and the location and magnetic properties of its contents[13]. As a result, the  $f_o$  of a resonant cavity is determined by the size and location of a small animal being housed inside the structure. Due to this difficult complication, both the circuitry driving the cavity and the implanted device must be able to compensate for the changes in  $f_o$  if optimal WPT is to be found[18].

#### 1.2 Resonant Cavity Wireless Powering Background

Due to the transient nature of the animal host moving about the wireless powering resonant cavity chamber, the device can be expected to be in an off-state at certain times during operation. This can occur due to low coupling between the cavity and the implant or simply because the animal needs to be removed from the resonant cavity for a period of time. As such, the device must robustly power on as well as operate at the steady state. This complication results in careful consideration being required when designing wireless power harvesting implants. The system's PTE is determined largely by both the impedance match between the resonant cavity and the implant, as well as the quality factor of the impedance matching network's components. Because of this, impedance matching networks must be designed with correctly matched impedance as well as high quality factor. In the static impedance case, this is easily achieved with off-chip ceramic capacitors. However, when trying to dynamically adjust the impedance on the fly to compensate for the changing wireless power environment, other impedance elements must be used.

#### **1.3** Turn-On Transients In Dynamic Impedance Elements

When selecting and implementing these dynamic elements, often times the impedance can be quite different for the element when in the unpowered or off-state of the device compared to the steady state and properly powered impedance. In addition, many of these elements like capacitor banks or miller capacitors have low quality factor when not properly powered or biased. This low quality factor coupled with unknown off-state impedance can create a drastic cavity input power requirement for turning on the device, which is much higher than the steady state cavity input power requirement to maintain device operation.

#### **1.4 Battery Integration**

In some implantable devices, the circuits are powered purely by wireless power, which results in smaller implants but also in more off-time and instability depending on the powering environment. For other implantable devices, they run off of a battery to supply a limited lifetime's worth of power to the device. In the case of the wireless-only devices, the input voltage produced by the wireless power can be quite small at times, requiring a converter to step the voltage up to a usable level for the implant's signal acquisition and stimulation therapy delivery circuits. In the battery case, the nominal voltage of the battery may need a converter to efficiently step the voltage down to a usable level for the implant. In the most rigorous of implants, the power supply should be able to handle having both wireless power as well as battery supplies on the same device. In this scenario, the power supply should be able to efficiently and effectively step up low wireless power voltages when battery power is not available, while also stepping down battery voltages when wireless powering is insufficient. The ability to seamlessly transition between these two modes is critical to effective power supply for implants needing both power sources.

## 2. WIRELESS POWER DEVLIERY AND IMPLANTABLE DEVICE DESIGN

In this work, I use a resonant cavity, implement algorithms, and build upon the work from [1, 18] to further improve wireless powering in resonant cavities. In an effort to increase PTE for high power budget small implants exceeding 40mW continuously, higher Q-factor cavity resonators are used with narrower frequency response, which results in a need for exciting the cavities as close to their  $f_o$  as possible, as well as having a device capable of keeping its impedance and  $f_o$  finely tuned to match the cavity at all times. I present a system capable of accounting for both issues. Firstly, the system monitors how the resonant cavity's  $f_o$  changes in real time and updates the frequency with which the cavity is being excited to match  $f_0$ . Secondly, the implanted device matches its own self resonant frequency to that of the cavity's in real time with a dynamic impedance matching (IM) network. With both of these improvements, higher amounts of power are transferred to the implanted device for more locations in the resonant cavity even as the animal gains weight over time. I present a fully implantable power supply made of discrete off the shelf integrated circuits (ICs) and test it with the dynamic IM system on the bench top powering a device called the Bionode [19], which is capable of recording biopotentials and electrically stimulating the nervous system. Finally, I develop a solution including a rechargeable battery test it in vivo.

#### 2.1 Device to Be Powered: The Bionode

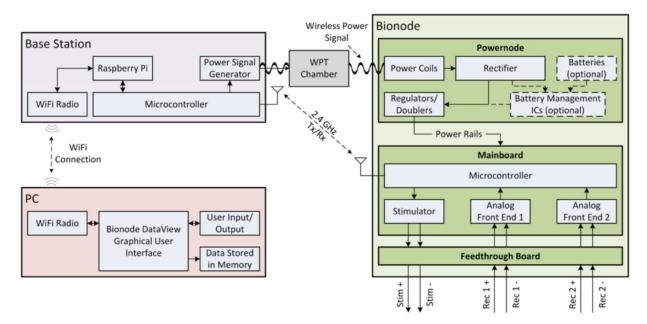

The Bionode is a multipurpose implantable device designed and fabricated by various members of the Center for Implantable Devices at Purdue University [19]. This device is comprised of two to three PCBs with off the shelf ICs on board. The Bionode runs off of wireless power and battery power and is capable of the following features: up to four channels of bio-signal acquisition, bio-sensor interfacing, one channel of balanced and biphasic electrical stimulation up to a few milliamperes of current, and two way data communication to provide stimulation and recording parameters to the device or provide data measurements out to the user in real time. After device fabrication, electrodes and sensors are attached to the Bionode, and the entire device is sealed in a mixture of glass, medial grade epoxy, and silicone to provide a

hermetic and non-toxic enclosure for the circuits. This device and packaging are shown in Fig 2.1 [19], and a block diagram of the board's functions are shown in Fig 2.2 [19].

Figure 2.1. A Bionode assembled at the coil and PCB level (left), and a Bionode fully packaged in a hermetically sealed glass case with electrodes, ready for implantation (right) [19].

Figure 2.2. This figure depicts the Bionode system from the block level .The user interfaces with a GUI on their PC, which controls the Base Station. The Base Station communicates with two way data to and from the Bionode implant and is able to power the implant. Finally, the Bionode has a two way data link, wireless power link, and interfaces with the body externally.

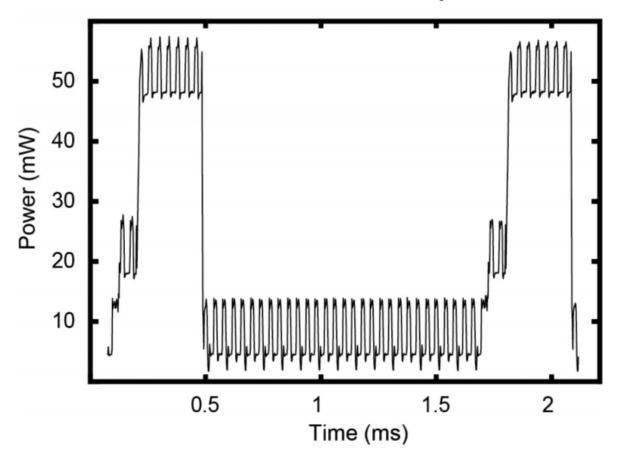

In particular, I designed and worked with the Bionode's power circuitry and wireless power link, called the "Powernode." This PCB and collection of ICs harvests wireless power from two separate metal coils, pointing in two separate directions, as well as utilizes two batteries to deliver multiple regulated and unregulated supplies for the sensitive circuits that measure biopotentials and stimulate the host animal. The Powernode is designed to provide power up to around 60mW of peak power and an average of 16mW during standard Bionode operation. These power requirements of the Bionode vary with the operation of the device; when radio transmission and stimulation are required, power needs are around 60mW, while when nothing but measurement is occurring, power consumption is closer to only a few milliwatts as shown in the plot of the power consumption in the average case in Fig 2.3. The main requirements of the Powernode is to provide stable, consistent regulated supplies to the digital circuits and analog measurement circuits, as well as high magnitude unregulated voltage supply rails to the stimulator for extra headroom when stimulating through higher impedances in the animal.

## **Bionode Power Consumption**

Figure 2.3. This is a standard power consumption curve over time for a Bionode circuit using the radio to send out measured data from the ADC and bio-signal acquisition circuits.

#### 2.2 Powernode: Static Impedance Design

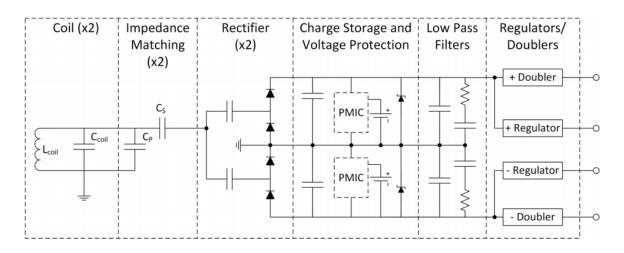

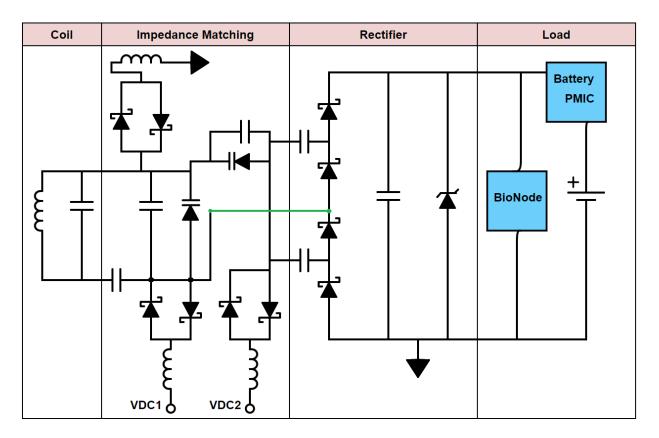

The Powernode's design is centered around using both the battery's power and the wireless power to provide supplies to the Bionode. The two coils each have their own

impedance matching circuit to provide maximal power transfer from the resonant cavity or transmitting powering coil to the receive coils on the Powernode. These two l-matching networks use two static capacitors that are initially predicted based on bandpass filter theory [15, 18, 20], and the capacitor values are manually tweaked for each device and animal to specifically tune the operating frequency and impedance of the implantable device to maximize power transfer efficiency. Each coil additionally has its own full wave rectifier doubler that converts the AC power received by the coils into a DC rectifier voltage to deliver power to the regulators and converters. The need for separate rectifiers is due to the two coils needing to be as electrically isolated and separate from each other as possible. If both coils shared the same rectifier, the resonant frequencies and impedances of the two coils are much harder to tune to a specific frequeny, and the two frequencies of each coil will be pushed further a part from each other and not able to be as close in frequency, resulting in a loss of efficiency at the desired operating frequency of the transmitting cavity or coil. These rectifiers produce a DC voltage drop across the full rectifier, and in this application, ground is chosen to be the midpoint of the rectifier, resulting in a positive and negative rectified voltage with respect to the rectifier's midpoint.

After rectification, the DC power available from the wireless power is able to be downregulated to multiple +1.8V and +0.9V supplies for the microcontroller, analog recording circuits, and low voltage digital control circuits on the Bionode. In addition to the +1.8V LDOs, the negative rectified voltage rail is down-regulated to -0.9V by an LDO for the same circuits. Finally, the stimulator requires a high negative and positive supply in the range of -5V to 10V and +5V to 10V, respectively. This is achieved with switched capacitor doubler ICs. To prevent the rectified voltages from having too much AC noise from the wireless power, additional low pass filters are added into the circuit. Finally, the rectifier's negative and positive supplies are clamped to -4.2V and +4.2V to protect circuits downstream from overvoltage effects and damge. The batteries are attached in parallel with the negative and positive rectified voltage, and are litium ion batteries with a nominal voltage of 3.6V and maximum voltage of 4.2V. These two batteries may charge or discharge depending on the state of operation. Should the wireless power the doing poorly and not providing enough charge, the batteries will discharge and power the Bionode. Conversely, should the wireless power be providing excess power for the Bionode, the batteries will recharge from excess power provided by the coils. These charging and discharging cycles are managed by two off the shelf PMICs. These functions and general circuit diagram are presented below in Fig 2.4.

Figure 2.4. The schematic of the static Powernode power supplies used to power the Bionode implant.

#### 2.3 Resonant Cavity Dynamic Impedance Matching

Because of the evolution of the Bionode technology over recent years for various grants and applications, the power demands of the device have slowly increased to higher levels. To accommodate these increased power demands, the wireless powering of the device must be improved to provide higher PTE at the same input power levels to the transmitting device. In the following section, I present background on the operation of the resonant cavity, static impedance matching of the Powernode, and design an improved dynamic impedance matching system for the implantable Bionode powered by the resonant cavity only.

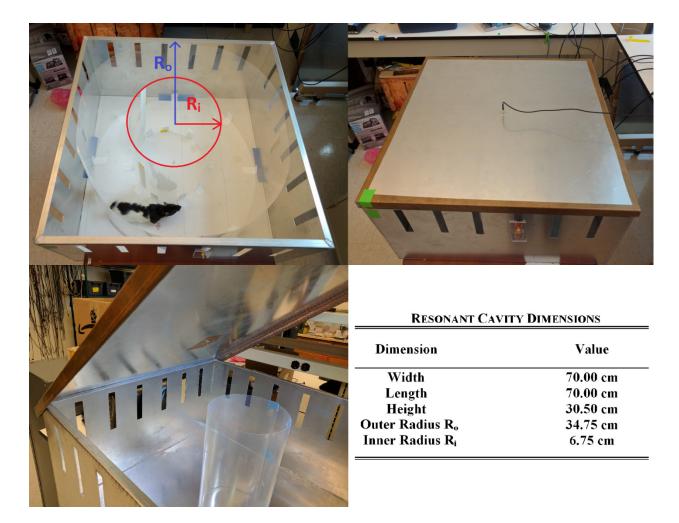

Fig. 2.5 shows an aluminum cavity resonator. This hollow structure simultaneously provides a housing structure for small rodents, such as rats or mice, to inhabit and provides wireless powering for implanted devices. The  $TM_{110}$  mode is excited with a probe in the center of the cavity with an AC signal to generate a circulating magnetic field [1]. From simulations, the fields mostly circulate around the center of the cavity with field strengths that in generally increase with increasing radius from the center -excluding the corners of the rectangle and the exact center of the cavity. In the corners and center of the cavity, the field strength is much weaker, and as a result, we add plastic barriers to prevent the animal from entering these low field strength regions [1].

Figure 2.5. The resonant cavity used to power implantable devices. An animal is housed in the enclosure and prevented from traversing low field strength portions of the cavity (top left). The cavity is excited externally (top right) by a probe in the center of the cavity (bottom left), and has specific dimensions that determine its resonant frequency (bottom right).

As shown in previous works, the resonant frequency of the cavity is a function of the dimensions of the structure [15]. Due to the size of our cavity,  $f_o$  is approximately 347.8 MHz when nothing is inside of the cavity, and we select the probe length for minimal loading. Fig. 2.6 demonstrates the power reflection measurement for this structure. We move a rat phantom, capable of mimicking the electrical properties of a rat weighing 280-300g, to various radii in the cavity. The frequency at which minimum reflection occurs indicates the resonant frequency for that loading condition. This frequency is much lower than the frequencies in the GHz range where wireless powering is less efficient for implantable devices due to higher tissue absorption of RF energy at high frequencies [21]. In this work only the TM<sub>110</sub> mode is harvested. In various

previous experiments, this mode was deemed to be the optimal excitation mode for implants of this size with the constraints placed on coil placement in the device. Other magnetic field modes can be generated with differing flux directions in resonant cavities, however, due to the requirements for animal housing, issues with interference between the two modes as well as harvesting of the two modes, and added required complexity of multiple well-spaced coils and associated electrical circuits, only the one mode is considered in this work.

Figure 2.6. Plot of reflection  $|S_{11}|^2$  versus frequency measured for the cavity with a vector network analyzer. A rat "phantom" mimicking the electrical properties of a rat sized at 280-300g is moved to various radii (r) in the cavity. The value  $f_o$  can be determined by the frequency at which minimum reflection occurs. It is shown that  $f_o$  decreases as an animal moves inward.

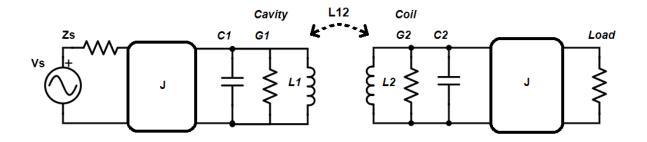

In Fig. 2.7, we model the cavity resonator as a parallel RLC with a 50 ohm AC signal source. The probe is modeled as a lumped capacitor, and the capacitive coupling between the probe and the resonator is a pi network. The pi network capacitances vary with the length of the copper probe used [16]. When an adding an animal to the outermost radius of the cavity resonator, the tissue acts as a lossy dielectric [15], and the resonant frequency of the cavity will decrease. As the animal moves further into the cavity to smaller radii, the resonant frequency further decreases due to the presence of stronger electric fields towards the center of the cavity.

This is a function of the animal's weight; thus, as an animal gains weight, this effect becomes more dramatic. We model the implantable as a parallel RLC circuit as well. Shown in Fig. 2.8, we include an IM circuit in the form of a J-inverter to maximize power transfer efficiency [13].

Figure 2.7. Circuit model of wireless power transfer as inductive coupling between two RLC circuits. The transmitting circuitry on the left includes an AC source and probe capacitance with impedance matching network in the form of a J-inverter. The receive circuitry on the right includes the RLC coil with impedance matching J-inverter and the connected load, which includes power management circuitry and the implantable device itself.

Figure 2.8. Realization of J-inverter matching circuitry as a half pi capacitor network to match the coil to the load impedance.

For a given frequency, we determine values for the IM network's two capacitors  $C_s$  and  $C_p$  based on the algorithm presented in [18]. In previous work [13], the frequency selected is either the resonant frequency of the cavity when the animal is either at the outermost region or when the animal is halfway between the outermost and innermost allowable radii.

However, the optimal PTE case exists when the animal is in this location and an AC signal at this specific frequency excites the cavity. As the animal moves and the resonant frequency of the cavity changes, the PTE decreases as both the cavity and receive device are not operated at the optimal frequency. To solve this issue of  $f_o$  changing and resulting in sub-optimal conditions, we need two solutions. We require a "frequency tracking" driving circuitry to update

the frequency exciting the cavity to match  $f_o$  and a "dynamically impedance matching" receive device on the implant to update the receive device's resonant frequency to keep up with  $f_o$ . When implementing both of these improvements, optimal PTE exists in the system.

#### 2.4 Resonant Cavity Frequency Tracking

To effectively keep up with the animal's motion in the cavity and have the driving frequency quickly track and update to the changing resonant frequency of the cavity, we use a driving system called the "basestation", fabricated on a four-layer PCB with discrete components capable of this task. The basestation and frequency tracking work described herein is the work of Grant Wang but is included for completeness on the discussion of the full system in the wake of any publication for citation.

Fig. 2.9 presents a block diagram of the functionality of the basestation. A separate microcontroller (Nordic Semiconductor, nRF51822) sets an ASK/FSK transmitter, capable of generating low power signals in the range of 280 MHz and 450 MHz (Maxim Integrated, MAX7060), to various frequencies. A low noise RF pre-amplifier (Analog Devices, HMC636ST89)amplifies this output signal, and then an output RF power amplifier (RFMD, RFPA3800) amplifies the signal again with high gain. Next, a dual junction circulator passes the signal to both protect the power amplifier as well as couple reflected power to a third port. An RF log detector (Linear Technology, LT5537) converts this reflected RF power into a DC output as a function of the RF amplitude, and the microcontroller's on-chip analog-to-digital converter then measures this DC output.

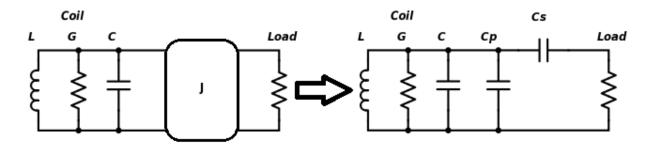

Figure 2.9. Block diagram of the functionality of the signal generation circuit on the basestation. A signal generator creates a waveform that is filtered and amplified before feeding the cavity. The reflected power is measured and a microcontroller updates the frequency of the signal generated as a result. The algorithm implemented by the basestation's microcontroller is straightforward and presented in Fig 2.10; the user selects a starting frequency to program the signal generating circuitry with to start. The ADC then samples the reflected power and increases the driving frequency. The system samples the reflected power once again. If the reflected power decreased, this means that more of the power is delivered to the cavity, which indicates that the driving frequency is closer to the resonant frequency then previously. As a result, the basestation continues to increase the frequency until it measures an increase in reflected power, at which point the basestation will start to decrease the frequency. This feedback loop repeats approximately 20 times per second, which is quick enough to keep up with the normal motion of rodent. Fig. 2.6 demonstrates the frequency changes seen for various locations of an average sized rat (280-300g) at various radii in the cavity where the expected frequency change from the animal results in frequencies between about 340 and 346 MHz.

Figure 2.10. The searching and tracking algorithm performed by the base station to find the best frequency to drive the cavity resonator with.

#### 2.5 Dynamic Impedance Matching Circuits and Elements

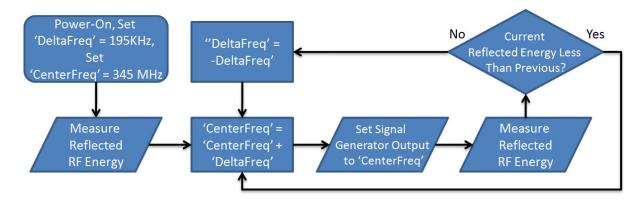

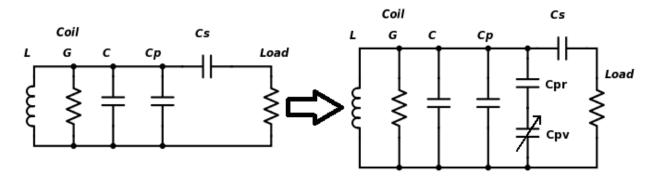

To account for changes in the frequency the cavity is driven at, the receive device's  $C_s$  and  $C_p$  ideally need updating with each frequency change. However, for the frequency ranges used and impedance of the implant used in this study, changes in  $C_p$  are a sufficient first step in helping increase PTE. Thus, as the frequency decreases,  $C_p$  must increase to compensate, and as the frequency increases,  $C_p$  must decrease.

Multiple options exist for dynamically varying capacitances, including varactors, miller capacitors, and multiplexed discrete capacitor tanks. Varactors require precise bias voltages to be established utilizing DACs, inductors, and additional diodes, which consumes additional area yet

is a potential solution. Miller capacitors using discrete silicon MOSFETs have speed limits lower than this frequency range and are not effective for this application as a result. Due to the presented constraints, we select a 5-bit multiplexed discrete capacitor bank (Peregrine Semiconductor, PE64102) to realize this circuit discretely. Fig. 2.11 shows a modified circuit of the receive coil and IM. The C<sub>s</sub> and C<sub>p</sub> discrete static capacitors are still present, but we add a series combination of the capacitor bank C<sub>pv</sub> and static capacitor C<sub>pr</sub> as an additional shunt element. The capacitor bank changes its value based on digital control signals from a microcontroller, while C<sub>t</sub> decrease the variable capacitance range to the necessary values and desired fine step size.

Figure 2.11. Transformation of static J-inverter impedance matching to include a parallel changing capacitive element to track with changes in  $f_o$ . The parallel capacitive network includes the capacitor bank as well as series capacitor to limit the capacitance seen to reduce step size and allow for finer tuning.

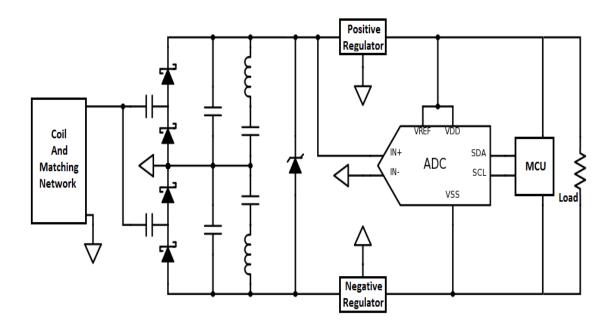

Fig. 2.12 shows the schematic of the updated Powernode. The Powernode is a circuit realized on a four-layer PCB and populated with discrete components. This circuit connects a coil and its respective tuning network and converts coupled RF energy into positive and negative DC supplies with respect to a center ground voltage using a full wave rectifier. The rectifier is voltage doubling and utilizes small forward drop, low reverse recovery time Schottky diodes to increase efficiency and reduce reverse leakage when switching in the 340 - 350 MHz range. In addition, each of the voltage rails generated by the rectifier has charge storage capacitors and notch filters with a center frequency of 345 MHz to reduce any of the RF signal from the coil that leaks through onto the DC lines and provide stable input voltages to regulators implemented from these rails. An 11Volt Zener diode prevents overvoltage damage to the later circuitry. The

two rectified DC output voltages are then down regulated to stable, accurate supplies for powering a microcontroller with on-chip ADC, capacitor bank, and Bionode device. We achieve this with positive 1.8V regulator and a negative 0.9V regulator.

Figure 2.12. Circuit model of the Powernode for power management. The output of the coil and matching is rectified with a full wave doubler, filtered, clamped, and down regulated. A microcontroller with ADC samples the rectified voltage and adjusts the capacitor bank in real time to track  $f_o$ .

The microcontroller implements the dynamic IM algorithm as well as manages power consumption from the Bionode device powered by the Powernode. Most times, the microcontroller (MCU) is asleep and drawing little power. Every 33 milliseconds, it wakes up for approximately 5 milliseconds to perform the dynamic IM algorithm. For nine wake-up cycles, the MCU samples the positive rectifier voltage, stores the value, and sleeps. On the tenth wake-up cycle, the MCU samples again and then based on previous capacitance values selected, current 10-cycle voltage average, and previous 10-cycle voltage average, it decides whether the coil's parallel capacitance should increase, decrease, or remain unchanged. This results in the capacitance being able to change up to 3 times a second, which is quick enough to keep up with the motion of a small rodent in the resonant cavity being used. The averaging period of 10 cycles

is due to the dynamic nature of the power consumption of the Bionode device. During radio transmissions (every 1.6 to 40 milliseconds depending on sampling rate), the Bionode consumes up to twenty times the baseline power consumption when not transmitting data. As a result, the rectifier voltage instantaneously decreases some. In an effort to reduce errors in IM changes, sampling the rectifier over 330 milliseconds and averaging the result successfully represses quick changes in rectifier voltage as the sampling frequency and the transmission frequency differ. We keep the algorithm simple intentionally due to intermittent power loss of the implant. During power loss, all previous variables and information are lost. This is a result of the inability to write to flash memory when implanted, which is a direct result of the possibility of corrupting the flash memory and causing algorithm failure if power is lost during a write operation to the flash memory. The algorithm used in this application is diagrammed below in Fig 2.13.

Figure 2.13. The algorithm implemented by the Powernode microcontroller. The device wakes up for small increments to save power and measure the rectified voltage ten times. Next, the capacitance of the bank is increased. Ten more measurements are taken. If the rectified voltage is lower, the capacitance increment direction is flipped and the capacitance is changed in this direction. If the voltage is higher, the direction remains the same and the capacitance is changed in the same direction. After each set of operations, the device is put to sleep to save power.

The Powernode has a single coil for simplicity of initial measurements and ease of construction. The coil selected for this device, dubbed a "two-axis coil", is a rectangular coil with a 90-degree bend placed halfway along its longer dimension as shown in Fig. 2.14. This coil can capture large quantities of flux in both the directions marked "A" and "B" in the figure. As a result, the device should be implanted such that one of the "B" directions is parallel with the animal's spine, and the other "B" direction is parallel to the animal's sagittal plane. The animals tend to habit the cavity such that either their spine is parallel or perpendicular to the flux in the

cavity based on previous work done with chronic implantations in these cavities with aforementioned "keep-out-zones".

Figure 2.14. A model of the Powernode board and two-axis coil. The coil receives flux in large quantities in the marked directions, any direction between, or any direction opposite the aforementioned directions.

We fabricate a two-axis coil with 22 AWG magnet wire, and measure its electrical properties at 345 MHz with a 1-port VNA measurement. Then we do the same measurement for the cavity resonator. Then, the algorithm developed in [18]using the measured values determine the approximate value of the IM network. Using the IM values, we populate the tuning network on the Powernode with 0201 capacitors (Johanson Technology) -without populating the capacitor bank- and the resonant frequency is measured with the VNA.

Based on the previous measurements with loading the cavity with a rat phantom similar to a young rat weighing around 260g at the outermost radius of the cavity and with a rat phantom similar to an old rat weighing around 400g at the innermost allowable radius of the cavity, we determine the minimum and maximum resonant frequencies that the device must match to be 340 MHz and 346 MHz. After manually changing the  $C_p$  value and measuring the resonant frequency for each value, the minimum and maximum  $C_p$  values determined are 1.8 and 2.0pF. Because the capacitance range of the capacitor bank is 1.88pF to 14pF, we place a discrete 0201 0.8 pF in series with the capacitance bank to set the dynamically tunable element to range between approximately 0.56 pF and 0.75 pF. When placed in parallel with a 1.2 pF discrete capacitor, the total parallel capacitance varies between 1.76 pF and 1.95 pF, which are close to the necessary values for the desired frequency range.

#### 2.6 Experimental Results

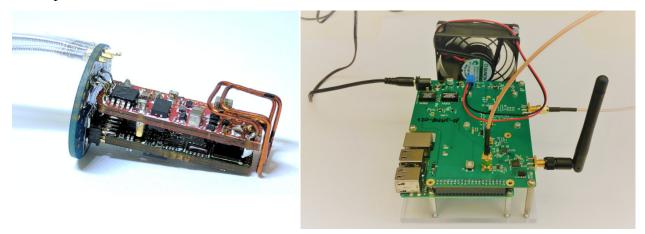

The purpose of the Powernode is to provide stable and adequate power to the Bionode as previously discussed. All of the on-board features come at the cost of power consumptions that vary based on the sampling rate of the device's data acquisition circuitry. The device being used specifically in this wireless power improvement study consumes an average of approximately of 8.1mWand 48.6mW for common total sampling rates of 1 kilosample per second (kSa) and 25kSa, respectively. Fig. 2.15 is an example of the Bionode system and basestation system used in this particular work.

Figure 2.15. Picture of a full implantable device on the left and basestation on the right. The Powernode is the red board, and a two-axis coil is attached. The basestation has an attached antenna for data telemetry, an SMA connection for reflected power measurement, and an SMA connection to power the cavity with the generated waveform.

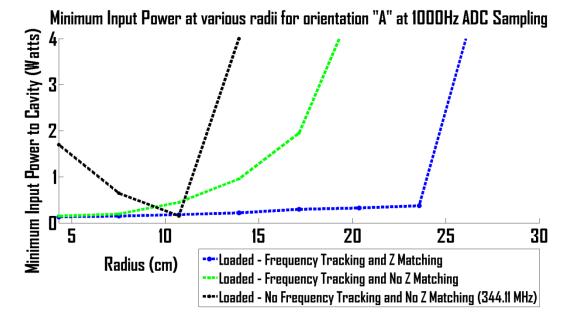

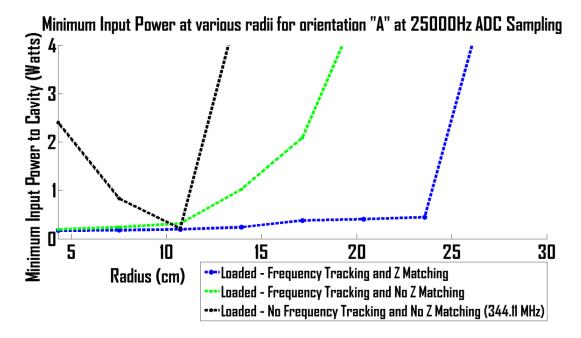

We test the complete system on the bench-top using a resonant cavity described above and a rat "phantom" - a combination of materials including TX-151 used to mimic magnetic properties of tissue - with properties similar to a 280-300g rat. We then place a full implantable device including Powernode, Bionode, and electrodes in the same orientation at various radii (with the rat phantom moving as well) in the cavity. The specific orientation is such that the flux lines in the cavity enter the coil in direction "A" shown in Fig. 2.14. An SMA cable then connects the basestation to the cavity. We measure the minimum power on the Basestation inputted to the cavity required to turn on the Bionode device for each of these locations for various cases. The first test case uses the device without either the frequency tracking or dynamic IM and manually tuning the device to the average frequency (when the animal is at the middle allowable radius) of the cavity while also driving the cavity at that average frequency only for various locations of the phantom and device. This case shows the power transfer that can be expected from systems employing wireless power in a high-Q factor resonant cavity without any of the improvements presented in this paper. Next, we test the case where frequency tracking is employed for an implant that has been manually tuned to the frequency when the animal is at the largest radius in the cavity but does not have dynamic matching. Finally, we show the case where the system implements both frequency tracking and dynamic IM. Fig. 2.16 and Fig. 2.17 present the minimum input power to the cavity to reliably use the Bionode system at various radii in the cavity at two separate sampling rates. Due to saturation and non-linear effects from the power amplifier on the basestation when the outputted power gets in the range of 3.9 to 4 Watts, we mark all measurements in that range as 4 Watts in Fig. 2.16. and Fig. 2.17. If there is no mark for a measurement and given radii, it means that the device cannot operate with 4 Watts inputted into the cavity.

Figure 2.16. Plot of the minimum power to the cavity required to operate an implant that consumes 8.1 mW on average (not including AC-DC conversion loss) at various radii in the cavity in coil orientation "A". The cases shown include with no improvements to the wireless powering, with just frequency tracking, and with both frequency tracking and dynamic IM ("Z Matching").

Figure 2.17. Plot of the minimum power to the cavity required to operate an implant that consumes 48.6 mW on average (not including AC-DC conversion loss) at various radii in the cavity in coil orientation "A". The cases shown include with no improvements to the wireless powering, with just frequency tracking, and with both frequency tracking and dynamic IM ("Z Matching").

Based on these measurements, for the orientation case of "A" and lowest power consumption case, the device with only frequency tracking shows modest improvements in both number of locations that the device could be operated in as well as the power transfer efficiency in nearly all locations. When combining the frequency tracking and dynamic IM, we see a drastic increase in number of locations the device can operated at as well as significant decrease in the amount of input power required in nearly all locations when adding in dynamic IM and frequency tracking. At the highest power consumption case, the improvements are even more apparent with the device with both dynamic IM and frequency tracking.

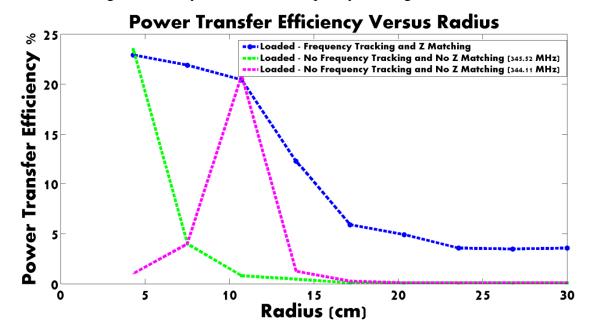

In addition to the minimum input power measurements taken, we directly measure  $S_{21}$  and calculate of PTE using a 2-port measurement with a VNA connecting to both the cavity and the output of the impedance matching network (the rest of the Powernode after the rectifier to the regulators was powered with a DC supply separately) for the same locations in the cavity. From

the  $S_{21}$  measurements from the VNA, we directly calculate the PTE percentage. The plots in Fig. 2.18 demonstrate the results of these measurements. Once again, we see improvements for all but the points where the frequency corresponds to where the device is tuned to statically. By taking averaging the difference between PTE for the frequency tracking and dynamic IM and the PTE for the better of the two measurements with no improvements, there is an increase of 10.38% PTE is found on average with the dynamic IM and frequency tracking.

Figure 2.18. Plot of power transfer efficiency percentage for an implant positioned at various radii in coil orientation "A". The cases shown include when the device has both frequency tracking and dynamic IM ("Z Matching"), no improvements where the implant is statically tuned to 345.52 MHz, and no improvements where the implant is statically tuned to 344.11 MHz.

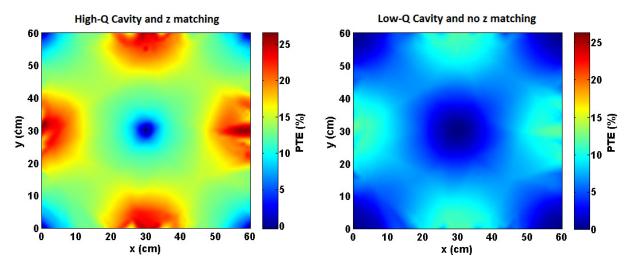

By simulating this High-Q cavity resonator in Ansys High Frequency Structure Simulator (HFSS), simulations of the magnetic field strength at each location in the cavity resonantor show that the height at which the implant sits largely does not affect the field strength or PTE. Taking this planar spatial field strength data as well as the measured data from this work, we curve fit the two data sets. The PTE is non-linearly correlated to the field strength under the following reasonable assumptions: the impedance of the receive device is matched well to the implantable circuitry due to the dynamic IM, the cavity is being driven at  $f_o$  due to the frequency tracking, and the small rodent has a negligible effect on the field strength. After curve fitting, we extrapolate the measured PTE data points to the entire planar area (ignoring the height) of the

cavity. As demonstrated in Fig. 2.19, the presented improvements to this high-Q cavity resonator based system demonstrate drastic improvements in PTE throughout the entire area when compared to lower-Q cavity resonator work without the dynamic IM or frequency tracking [1]. A comparison between a low-Q cavity without dynamic IM and a high-Q cavity with dynamic IM is critical due to the necessity of having dynamic IM in the high-Q cavity for reasonable operation to be expected at all. From the HFSS simulation data, one clear outlier data point out of the 60 by 60 point grid generated for Fig. 2.19 is removed and instead replaced with a spatial average of its four immediately surrounding points The point is located approximately at x of 4 and y of 32.The data in each of the plots uses measured data where magnetic flux is normal to the coil in the optimal position (orientation "A"), but the coil used in the lower-Q cavity is a traditional "one-axis coil" of similar flux-capturing area [1].

Figure 2.19. Plot of PTE for various spatial locations in the high-Q resonator using dynamic IM and frequency tracking created with curve fitting data to HFSS field strength simulation data (left). Plot of PTE for various spatial locations in a lower-Q resonator from previous work without dynamic IM [1].Both plots show data where flux is normal to the receive coil.

To verify functionality of the design, the device was implanted in a 280g rat. Because the two flux capturing coils do not account for the third axis which power may be received when the rat rears up on its hind legs, a rechargeable lithium ion battery was included similar to the Powernode in Fig 2.15 above. After implantation, the animal was placed in the resonant cavity during two separate recording sessions. In the first session of 6.4 hours, the cavity was driven with 4 Watts input with the frequency tracking and impedance matching active. The device's

battery was capable of delivering about 2 hours of power when not supplemented with any additional wireless power. The powering fidelity -calculated as the percentage of the total time that the device was on to the total amount of time the cavity was powered- during the session was 99.58%. For the second recording session of 2.77 hours, the experiment began with the batteries completely discharged at the beginning. The second session's power fidelity was measured to be 89.3% over 2.77 hours.

#### 2.7 Summary

In this work, I designed, built, and tested a complete system capable of providing improved power transfer efficiency for implantable devices with high power consumption needs in resonant cavities with higher Q factors. The system presented can compensate for the changing resonant frequency of the resonant cavity due to animal growth and motion through both frequency tracking and dynamic IM. By driving the resonant cavity, measuring the reflected power back from the cavity, and adjusting the frequency in the direction of reduced reflections, we drive the cavity at the optimal resonant frequency. Utilizing a bank of capacitors and sampling the output voltage of the rectifier, we vary the impedance of the implantable receive device to adjust for changes in the resonant frequency of the cavity to improve wireless power. These improvements combined increase the average PTE by a minimum of 10.38% for the best case orientation of the receive coil. Finally, I propose and implant a modified system containing a battery back-up and recharging in a freely behaving rat demonstrating the ability of the device to provide near perfect power transfer when the batteries are not allowed to discharge.

# 2.8 Turn-On Transients Challenges

The frequency tracking system and algorithm make sizeable improvements for systems with and without the implantable dynamic IM system and can be used with success as is. There is a substantial drawback to the dynamic IM receive system, however. When the device initially does not have power, the capacitor bank does not have power and the switches used in the bank have no power. As a result, there are more added parasitic elements added to the capacitor that work to decrease the quality factor of the whole IM network when the device is in an off state. This directly causes an increase in required input power to turn on the devices in comparison to

devices without the dynamic IM network. In addition, the proper cavity operating frequency may be different than the frequency of the device utilizing the off-state parasitic-filled bank. This undefined off-state capacitance can present an even greater barrier to turn-on.

# 3. NOVEL COIL-TO-COIL TRANSIENT TURN-ON POWER REDUCTION SOLUTION

To effectively solve the turn-on transient, we present the concept of a two-coil receive system. We statically tune the first coil to have a low-Q, broadband response, which separately powers a digital system that only exists to dynamically match the impedance of the second high-Q coil. Next, the second coil powers the Bionode device with a high-Q impedance matching providing high power at one frequency. As a result, the first coil turns on at a wider range of frequencies and lower power when designed correctly, reducing the impact of the turn-on transient.

#### 3.1 Potential Coil Configurations and Selection

In the receive two-coil system, two coils must be in close proximity and aligned in the same direction due to the constraints of implantable devices. This presents a challenge of reducing the two coils' effects on one another. To combat this, we consider a multitude of coil types, coil sizes, frequency bands, and coupling-reduction strategies. To reduce effects of the coils on each other, we explored and tested the three different setups shown in Fig. 3.1. Firstly, one transmit coil at one ISM band couples to one of the receive coils at the same frequency, and a second transmit coil at a second ISM band frequency couples to the second of the receive coils at the second ISM band frequency. Secondly, one transmit coil with a two-tone driving signal of two frequencies couples to two receive coils of the respective two frequencies. Thirdly, one transmit coil driven at a singular frequency couples with two receive coils at that singular frequency. Fig. 3.1 depicts these potential coil solutions. The first setups has issues with much of the power being wasted from coupling between the two large transmitting coils due to their spatial orientation. The second setup requires complex, restrictive, and inefficient two-tone generation and impedance matching methods on the transmit side as well as cross coupling between the two receive coils despite the frequency difference. The third setup suffers from high cross-coupling between the two receive coils and wasted power as a result. However, the third setup works if the two receive coils are coplanar and do not overlap in their windings so as to reduce coupling. This setup sacrifices the maximum achievable coupling and PTE as a result of reducing the areas of each coil to place them side by side. Fig. 3.1 shows the two half-moon receive coils as well as the simple planar pancake transmit coil.

Figure 3.1. In the first test setup, transmit device B's two coils couple at different frequencies to receive device A's two coils. In the second test setup, transmit device D's coil couples at two frequency tones to receive device A's two coils, where A's first coil is tuned to first frequency, and A's second coil is tuned to the second frequency. In the third setup, transmit device D's coil couples to receive device E's two coils at the same single frequency. Device E contains two halfmoon coils with one being a wider band, low quality factor coil, and the other being a narrower band, high quality factor coil.

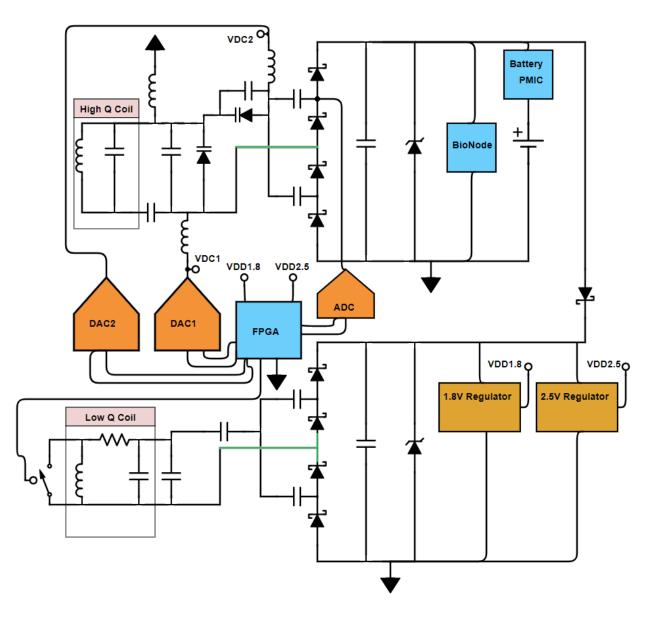

# 3.2 Circuit Topology

Due to the issue of undefined capacitance in the capacitor banks during turn-on, we use varactors controlled by DACs for bias to vary capacitance for  $C_s$  and  $C_p$  for this work instead of banks. In addition, for the sake of further reducing interference between the two receive coils, the system utilizes the 13.56 MHz ISM band. The lower frequency results in less effect of the first coil's tuning on the second coil's tuning (and vice versa) when compared to the 345 MHz range of the cavity-based work. Two DACs and the ground voltage bias the two varactors through

inductors to help reduce RF leakage into or out of the DACs and ground. The updated dynamic impedance matching network and rectifier are updated from the previously modeled system and shown in Fig 3.2. An FPGA programmed with the same algorithm discussed in the cavity based receive device, controls the DACs and acquires data from an ADC measuring the rectifier as before. The FPGA searches for the optimal capacitance match for the highest rectified voltage. Fig. 3.3 demonstrates the circuit schematic for the system. The startup cycle involves the low-Q coil receiving enough power to turn on, powering the DAC, ADC, and FPGA to begin matching the impedance of the high-Q coil. Once the rectifier of the high-Q coil is at a higher voltage than the rectifier of the low-Q coil, a schottky diode allows the high-Q rectifier to begin powering the tuning circuitry and digital controls itself. Finally, the low-Q coil is intentionally detuned by shorting across the coil with a switch to further reduce the effect of the low-Q coil on the high-Q coil during steady state operation.

Figure 3.2. A schematic of the updated Powernode utilizing a similar circuit as before, but including two varactors as tunable capacitors. DC voltages applied to either side of the capacitors are AC-decoupled to prevent impedance contributions at high frequency. The LDO and switched capacitor circuits are omitted from this diagram purely for aesthetic purposes and readability.

Figure 3.3. Schematic of the two-coil circuit design for improving turn-on transient in wireless powering. The low-Q coil power on first at a wide range of frequencies, starts to tune the impedance of the high-Q coil, and the high-Q coil powers the Bionode and eventually the tuning circuit itself.

#### 3.3 Measured Results

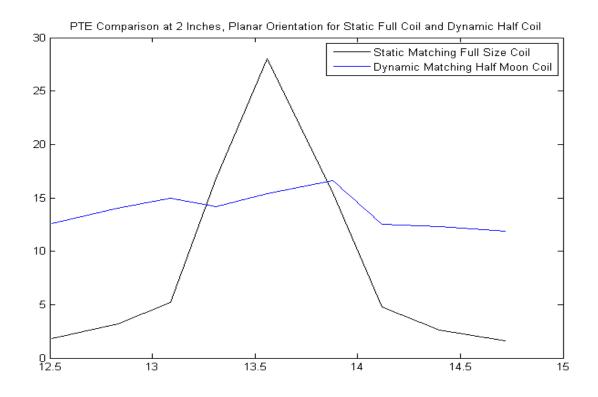

We measure the PTE of the high Q half-moon coil and single pancake coil shown in Fig. 3.1e and Fig. 3.1d using a two port VNA measurement in the same fashion as the PTE measurements in the cavity-based work above. Additionally, we measure the PTE of the single full size coil and single pancake coil shown in Fig. 3.1c and Fig 3.1d. By statically tuning the full

size coil for the center frequency of 13.56 MHz and leaving the impedance the same for all different frequency measurements, we simulate what the static impedance case will be. This comparison is done to show the sacrifice of having half the flux area in the half-moon coil with dynamic impedance matching compared to the standard static case of having a single full size circular coil with no dynamic impedance matching. In addition, we allow the high-Q half-moon coil to be tuned for every frequency measurement by the FPGA on-board to simulate the dynamic impedance case. The transmit and receive coils are separated by 5.08 cm with the orientation of each lined up to maximize coupling. Fig. 3.4 demonstrates the PTE of the halfmoon proposed coil compared to that of the single full size coil whose area is the same as the combined two half-moon coils. By inspection, the dynamically tuned half-moon coil sacrifices PTE at and near the center frequency of 13.56 MHz by reducing from 28% at max to only 16.6% at max. However, the dynamic impedance matching pays dividends on average by increasing the mean PTE from 8.83% for the static full coil up to a mean PTE of 14.83% for the dynamic halfmoon coil over the displayed and measured frequency range of 12.51 MHz to 14.72 MHz. Thus, so long as the low-Q coil properly powers up the impedance matching hardware and algorithm on the FPGA, the two half-moon dynamic system is more robust and sufficient to provide power to an implant like the Bionode at safe input power levels. The low-Q coil's static impedance matching can be tuned to however wide of a band is required as long as power within that band of frequencies is sufficient to provide sufficient power to the ADC, DAC, and FPGA providing the high-Q tuning.

Figure 3.4. A plot of the dynamic impedance matching PTE for the high Q half-moon coil in Fig 3.1e versus the static impedance matching PTE for a coil in Fig 3.1c that is the full area of the low Q and high Q half-moon coils combined. Peak PTE drops as expected, but average PTE over a wide frequency range is much higher.

### 3.4 Summary

In this work, I address the shortcomings of the transient turn-on requirements of the cavity based dynamic impedance matching Powernode from the first section of this thesis. I propose and fabricate a two-coil receive solution for lower frequency coil-to-coil systems that increases the average PTE by 5% (additively) over the displayed frequency range at the cost of max PTE reduction of 11.4% (additively) at the center frequency of 13.56MHz.

# 4. ASIC FOR FLEXIBLE IMPLANTABLE DEVICES WITH BATTERY AND WIRELESS POWER

In implantable devices requiring the use of just one of battery or wireless powering, the power supply design of the device is rather straightforward. However, in the case of combining both power sources together in an efficient and enabling manner, more complicated and elegant solutions are required to gain more efficiency and allow for the device to operate a larger percentage of the time desired. In the following section, the various types of power supply and power conversion are discussed, as well as their end-use applications. Towards the end of the discussion, a suitable power converter for this power supply is selected and developed.

#### 4.1 Power Conversion Topology Selection

In power supplies where voltages rails are slightly above the desired regulated level, a standard LDO can be used with great efficiency and minimal complexity. The efficiency of the regulator directly decreases as the input voltage rises further above the desired regulated output level. This relationship is expressed as:

$$Efficiency = \frac{V_{out}}{V_{in}}$$

where  $V_{in}$  is the input voltage, and  $V_{out}$  is the output regulated voltage. Because of this efficiency decrease at large input voltages compared to the output voltage, a different topology is necessary.

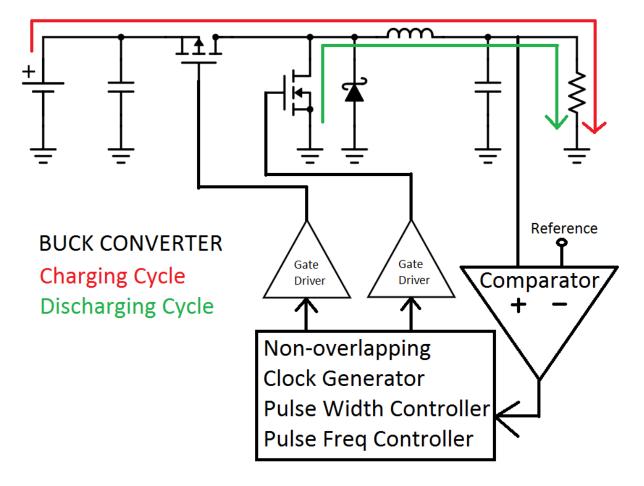

When voltage rails greatly exceed the output regulated voltage needed, a buck converter is useful in stepping down the input voltage to the output voltage seen in Fig 4.1. This is achieved through charging an inductor whilst increasing the output voltage of the converter and charging its output capacitor. Then, after charging the inductor, the input voltage source is switched out of the circuit, and the inductor discharges its charge to the output load. As the inductor and output capacitor discharge, the output voltage decreases. The cycle repeats, causing the output voltage to cyclically increase and decrease periodically. This ripple voltage generated generally must be held below a certain level to maintain proper noise reduction in the loading circuits of the implant. The output voltage of the buck converter is directly set by the ratio of the time spent charging the inductor to the time spent discharging the inductor expressed as:

$$D = \frac{V_{out}}{V_{in}}$$

where D is the duty cycle of the time charging the inductor to the time discharging the inductor,  $V_{out}$  is the output voltage, and  $V_{in}$  is the input voltage. This relationship is physically demonstrated in the amount of time that the pass PMOS device is on, which is the inverse of the amount of time per period that the shunt NMOS device is on. Taking a more practical view, the voltage drop across the non-ideal pass PMOS, the voltage drop across the non-ideal shunt NMOS, and the resistance of the inductor must be accounted for in the calculation of the duty cycle required, expressed as:

$$D = \frac{V_{out} + V_n}{V_{in} - V_p + V_n}$$

where  $V_p$  is the PMOS voltage drop in saturation,  $V_n$  is the NMOS voltage drop in saturation, and  $V_{ind}$  is the drop across the resistive portion of the inductor.

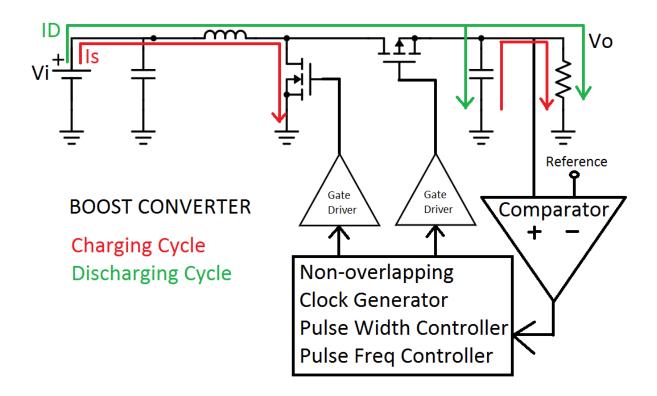

Figure 4.1. A standard synchronous buck conversion topology.

While the buck converter topology solves the step-down part of the problem, the cases where the battery is discharged, and the wireless powering is producing lower voltages than the desired regulated voltages must be addressed. This step-up conversion can be achieved through a boost converter topology seen in Fig 4.2. A boost converter operates similarly to a buck converter by charging and discharging an inductor periodically. Initially, the inductor is charged while the output voltage and capacitor are switched out of the circuit and isolated. After charging the inductor, the input voltage source and inductor are switched into a series configuration, pushing current forward into the output capacitor, which in turn increases the output voltage as the inductor discharges. Because the inductor and input voltage are in series, the two voltages add, resulting in a voltage presented to the output that is larger than the input. Next, the inductor is charged again by the input voltage source, and the output voltage and capacitor are switched out of the circuit and isolated. During this charging state, the output capacitor discharges into the output load while the output voltages decreases. This repeated charging and discharging cycle lead to a periodic decreasing and increasing output voltage, respectively. Similar to the buck converter, the output voltage is a function of the time spent charging compared to discharging, expressed as:

$$D = (\frac{V_{out} - V_{in}}{V_{out}})$$

where D is the duty cycle of the on time of the shunt charging NMOS. The relationship is physically demonstrated in the amount of time that the shunt NMOS device is on, which is the inverse of the amount of time per period that the pass PMOS device is on. Taking a more practical view, the voltage drop across the non-ideal components must be considered again, expressed as:

$$D = \left(\frac{V_{out} - V_{in} + V_p}{V_{out} - V_n + V_p}\right)$$

where the variables are the same as in the buck converter case.

Figure 4.2. A standard synchronous boost conversion topology

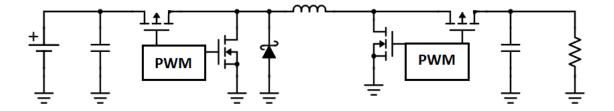

To combine both of the functions of the boost and buck converters in an efficient way, there have been multiple topologies created, which include the single-ended primary-inductor converter (SEPIC), split-pi converter, buck-boost converter, switched capacitor converter, cúk converter, and non-inverting buck-boost converter (NIBBC). When selecting from these topologies, trade-offs include output polarity, number of inductors, number of capacitors, a need for bidirectional current, continuous or discontinuous output current, and efficiency at various stepping ratios. In implantable devices, space is limited to create less intrusive devices in the body, thus fewer inductors and capacitors is paramount. This eliminates the cúk, SEPIC, and split-pi converters as they require two inductors and multiple capacitors. Additionally, in this application, the output voltage polarity should be the same as the input voltage, which makes the buck-boost converter not applicable. Finally, the output voltage must be efficient at multiple voltages to maintain flexibility, which rules out the use of a switched-capacitor converter. Thus, the remaining converter is the NIBBC. This converter uses one capacitor and one inductor to provide step-up and step-down capabilities. Drawbacks of the converter include reduced

efficiency due to two pass PMOS elements, complexity of the control scheme, and additional power consumption of the controls for the converter compared to other similar topologies. The basic NIBBC is demonstrated by Fig 4.3. The duty cycle of the converter is mode dependent, and the buck duty cycle is expressed as:

$$D_{buck} = \frac{V_{out} + V_n}{V_{in} - 2V_p + V_n}$$

where the variables are the same as in the buck converter equation. The duty cycle of the boost mode is expressed as:

$$D_{boost} = \left(\frac{V_{out} - V_{in} + 2V_p}{V_{out} - V_n + 2V_p}\right)$$

By inspection of the two duty cycles, the converter must contend with two pass power PMOS compared to the buck converter or boost converter topologies. As a result, the duty cycles are slightly different if designed well, and the power consumption of the converter overall is traditionally lower by default than the individual converters due to the extra PMOS power switch voltage drop, without mentioning the additional power required by the more complicated controller required for a NIBB converter.

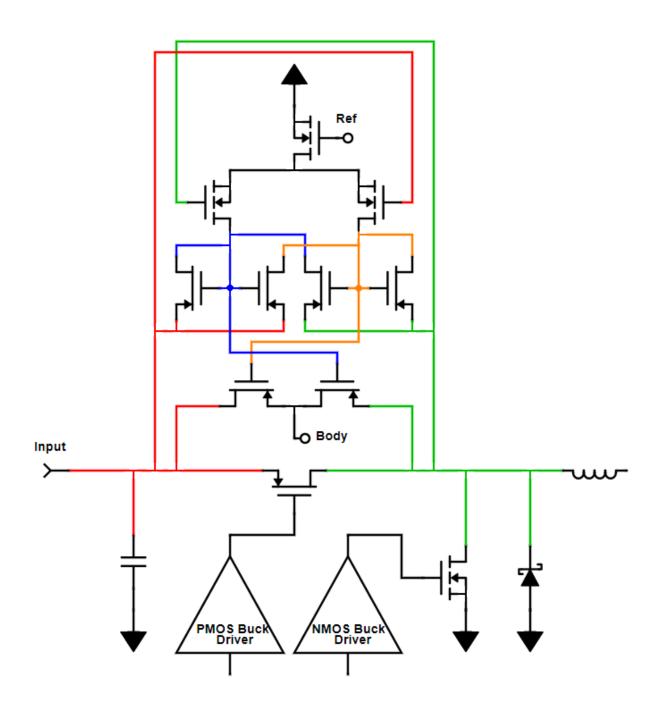

Figure 4.3. A standard PWM-based NIBBC topology.

# 4.2 General NIBB Converter Concerns