# ENABLING LOGIC-MEMORY SYNERGY USING INTEGRATED NON-VOLATILE TRANSISTOR TECHNOLOGIES FOR ENERGY-EFFICIENT COMPUTING

by

Sandeep Krishna Thirumala

**A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical and Computer Engineering West Lafayette, Indiana December 2020

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

### Dr. Sumeet Kumar Gupta, Chair

School of Electrical and Computer Engineering

## Dr. Anand Raghunathan

School of Electrical and Computer Engineering

## Dr. Zhihong Chen

School of Electrical and Computer Engineering

### Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

## Dr. Kaushik Roy

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

To my family for their unconditional love and support.

### ACKNOWLEDGMENTS

It is a bitter-sweet moment to write this part of my dissertation. Looking back, my PhD chapter of life has been nothing but an incredible voyage. Phenomenal learning curve, overcoming taxing hurdles and amazing collaborations is what has pushed me to achieve my dream and grow me into the person I am today.

First and foremost, I would like to wholeheartedly extend my sincere gratitude to my academic advisor, Professor Sumeet Kumar Gupta, for his excellent guidance and mentorship at every step of my doctoral studies. I am grateful to him for challenging me and providing me with an excellent research environment. I have always been motivated by his immense energy for research and strive for excellence, which enabled me to overcome numerous obstacles throughout my PhD. His strong emphasis on hard-plus-smart work ethics, flawless research presentations, and high-quality publications has helped me evolve as a researcher. I will be forever indebted to him for letting me steer the course of my PhD during the final years, which has made me learn to be an independent researcher, discover my strengths and gain skills to face the unpredictable challenges of academic problem-solving. I cannot thank him enough for being an outstanding mentor, critic, and companion throughout the course of my PhD. Working under his supervision has been a privilege for me, and this dissertation would certainly not have been possible without him.

Besides my advisor, I would like to thank my dissertation committee members, Prof. Anand Raghunathan, Prof. Zhihong Chen, Prof. Vijay Raghunathan and Prof. Kaushik Roy for their continuous collaboration and support with experiments and analysis. I consider myself extremely fortunate to have constant interaction and guidance from them, who are simply 'worldclass' researchers and teachers. Their insightful thoughts and constructive discussions have helped me steer my research towards the right direction. I thank them for their valuable feedback on refining my research proposals in this dissertation.

Next, I would like to thank my fellow lab mates and alumni of the Integrated Circuits and Device Laboratory (ICDL) – Prof. Ahmedullah Aziz (University of Tennessee), Atanu Kumar Saha, Niharika Thakuria, Karam Cho, Chunguang Wang and Xinkang Chen. It was a great experience having everyone around. I truly enjoyed and cherish all our conversations over a broad range of topics including heated research debates and fun, non-academic jabbers. In the process, I have learned so much from each one of them. I will forever remember all the memories of the lab.

Special mention to Dr. Arnab Raha (Intel), Dr. Shubham Jain (IBM) and Dr. Terry Hung (TSMC) with whom I have had numerous discussions, which led me to explore a wide range of topics and gain more comprehensive research perspectives. Their constant support and valuable insights have shaped my dissertation significantly. They have played a very important role in my PhD journey and I sincerely thank them for all their contributions.

I am also grateful to Dr. Hongmei Wang and Dr. Fabio Pellizzer for mentoring me and introducing me to the real-world industrial projects, during my internship at Micron Technologies, USA. I had to opportunity to learn several insights and concepts, along with the experience to face challenges which come along the way while bringing an emerging concept to reality.

I would also like to acknowledge the sponsors of my doctoral research, which was supported in part by the New Materials for Logic, Memory and Interconnects (NEWLIMITS), a center in nCORE, a Semiconductor Research Corporation (SRC) program sponsored by National Institute of Standards and Technology (NIST) and in part by the Defense Advanced Research Projects Agency (DARPA) Young Faculty Award (YFA) Grant. I am also extremely grateful for the Bilsland Dissertation Fellowship awarded to me by the Purdue University during the final year of my PhD.

Finally, I would like to thank to all my friends who gave me good advice and made this journey extremely enjoyable. In particular, I would also like to thank Sujata Khandare, for all her motivation and support during my entire graduate studies at the Purdue University. A special thanks goes to my sister Lalenthika Krishna, for constantly supporting me during this chapter of life and for being my loving stress-busters. Also, a shout-out to my four-legged sister Zoey Krishna (Labrador), for being a faithful virtual companion during the course of my studies. I would like to thank my grandparents, for always believing in me achieving greater heights. My deepest gratitude goes to my parents, Shanthy Madhusudan and Madhusudan Thirumala for their guidance, patience and unconditional love throughout, that provided the foundation for this work. This dissertation is a token of my respect and appreciation to all of them.

## **TABLE OF CONTENTS**

| LIST OF 7  | TABLES       12                                                                      |

|------------|--------------------------------------------------------------------------------------|

| LIST OF I  | FIGURES                                                                              |

| List of Ab | breviations                                                                          |

| ABSTRA     | CT                                                                                   |

| 1. INTR    | ODUCTION                                                                             |

| 1.1 Da     | ta Intensive Computing: Memory Bottleneck and Climate Burden                         |

| 1.2 Em     | nerging Memories to the Rescue                                                       |

| 1.3 Mo     | oving Logic Closer to Memory                                                         |

| 1.4 Mo     | otivation for this Work                                                              |

| 1.5 Or     | ganization of the Dissertation                                                       |

| 2. BACH    | GROUND TO FERROELECTRIC TRANSISTORS                                                  |

| 2.1 Int    | roduction                                                                            |

| 2.2 Fei    | roelectric Field Effect Transistors - FEFETs                                         |

| 2.2.1      | Device design                                                                        |

| 2.2.2      | Device operation                                                                     |

| 2.3 FE     | FET based Circuits and Systems                                                       |

| 2.3.1      | Non-volatile memory (NVM) design                                                     |

| 2.3.2      | Non-volatile flip-flop (NVFF) design                                                 |

| 2.3.3      | Artificial intelligence hardware / compute-in-memory (CiM) fabric for brain-inspired |

| comp       | uting                                                                                |

| 2.4 Dra    | awbacks of Existing Approaches                                                       |

| 2.4.1      | Requirement of negative voltages for polarization switching                          |

| 2.4.2      | Retention and endurance tradeoffs                                                    |

| 2.4.3      | Write voltage Scalability                                                            |

| 2.4.4      | Gate leakage                                                                         |

| 2.5 Su     | nmary                                                                                |

| 3. RECO    | ONFIGURABLE FERROELECTRIC TRANSISTOR R-FEFET: A NON-                                 |

| VOLATIL    | E MEMORY DEVICE WITH DYNAMICALLY TUNABLE HYSTERESIS                                  |

| 3.1  | Intr  | oduction                                                                            | . 52 |

|------|-------|-------------------------------------------------------------------------------------|------|

| 3.2  | R-F   | EFET Device Structure                                                               | . 52 |

| 3    | 3.2.1 | FinFET technologies                                                                 | . 53 |

| 3    | 3.2.2 | Planar technologies                                                                 | . 54 |

| 3.3  | Sin   | nulation Methodology                                                                | . 55 |

| 3.4  | Dyı   | namic Reconfigurability in R-FEFETs                                                 | . 56 |

| 3    | 3.4.1 | Non-volatile ('NV') mode                                                            | . 57 |

| 3    | 3.4.2 | Volatile ('V') mode                                                                 | . 60 |

| 3    | 3.4.3 | Effect of drain-to-source voltage                                                   | . 61 |

| 3.5  | Dev   | vice Design and Analysis                                                            | . 62 |

| 3    | 3.5.1 | Thickness of ferroelectric (T <sub>FE</sub> )                                       | . 63 |

| 3    | 3.5.2 | Control terminal voltage (V <sub>CS</sub> )                                         | . 63 |

| 3    | 3.5.3 | Area of control stack (A <sub>CS</sub> )                                            | . 64 |

| 3    | 3.5.4 | Current-voltage characteristics                                                     | . 65 |

| 3.6  | Ana   | alysis Considering Gate Leakage                                                     | . 66 |

| 3    | 3.6.1 | Gate leakage in standard FEFETs                                                     | . 67 |

| 3    | 3.6.2 | Impact of GL in R-FEFETs                                                            | . 68 |

| 3    | 3.6.3 | Impact on current-voltage characteristics                                           | . 70 |

| 3    | 3.6.4 | Comparison with standard FEFETs                                                     | . 70 |

| 3.7  | Tra   | nsition between different Modes during Circuit Operation                            | . 71 |

| 3.8  | Syr   | nmetric R-FEFET (R-FEFET $_{SYM}$ ) Design to Mitigate the Influence of Gate Leakag | e75  |

| 3    | 3.8.1 | Device design and operation                                                         | . 75 |

| 3    | 3.8.2 | Advantages of R-FEFET <sub>SYM</sub> vs R-FEFET <sub>ASYM</sub>                     | . 79 |

| 3.9  | Sur   | nmary                                                                               | . 80 |

| 4. I | R-FEF | ET BASED NON-VOLATILE MEMORIES                                                      | . 82 |

| 4.1  | Intr  | oduction                                                                            | . 82 |

| 4.2  | 3T-   | R NVM Design and Operation                                                          | . 83 |

| Z    | 4.2.1 | Memory operation                                                                    | . 83 |

| Z    | 4.2.2 | Probability of failures                                                             | . 88 |

| Z    | 4.2.3 | Endurance and retention                                                             | . 90 |

| 2    | 1.2.4 | Advantages over standard FEFET based memories                                       | . 90 |

| 4.2   | 2.5  | Memory array analysis                                          | 91    |

|-------|------|----------------------------------------------------------------|-------|

| 4.3   | 2T-  | R NVM Design and Operation                                     | 93    |

| 4.3   | 3.1  | Memory design                                                  | 93    |

| 4.3   | 3.2  | Memory operation                                               | 94    |

| 4.3   | 3.3  | Comparison with previous FE(M)FET/R-FEFET NVMs                 | 97    |

| 4.3   | 3.4  | Memory array analysis                                          | 97    |

| 4.4   | Var  | iation Analysis of R-FEFET based NVMs                          | 99    |

| 4.5   | Sun  | nmary                                                          | . 102 |

| 5. R- | FEF  | ET BASED NON-VOLATILE FLIP-FLOPS                               | . 103 |

| 5.1   | Intr | oduction                                                       | . 103 |

| 5.2   | Inte | ermittently Powered Systems                                    | . 104 |

| 5.3   | NV   | FF with Auto-Backup: RNVFF-1                                   | . 106 |

| 5.3   | 3.1  | Circuit design                                                 | . 106 |

| 5.3   | 3.2  | Circuit operation                                              | . 107 |

| 5.4   | NV   | FF with Gated Backup: RNVFF-2                                  | . 108 |

| 5.4   | 4.1  | Circuit design                                                 | . 108 |

| 5.4   | 4.2  | Circuit operation                                              | . 108 |

| 5.5   | Cire | cuit-Level Analysis                                            | . 110 |

| 5.6   | Imp  | plementation in Intermittently Powered Systems                 | . 111 |

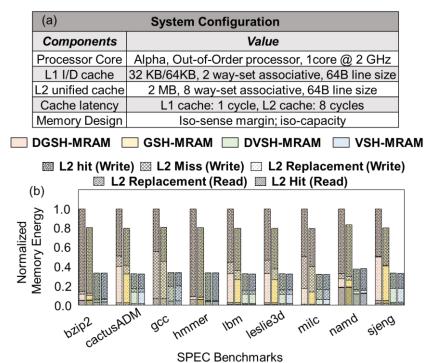

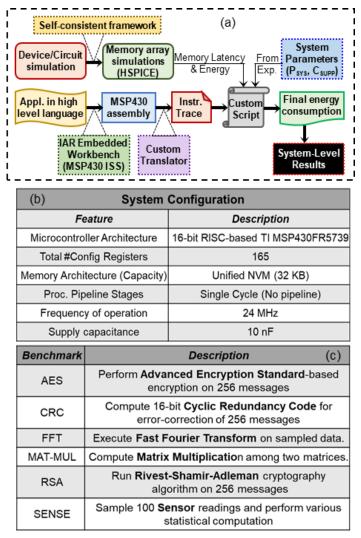

| 5.0   | 6.1  | System-level simulation methodology                            | . 111 |

| 5.0   | 6.2  | System-level simulation results                                | . 113 |

| 5.7   | Sun  | nmary                                                          | . 121 |

| 6. R- | FEF  | TET/FEFET BASED ARCHITECTURES FOR BOOLEAN/ARITHM               | ETIC  |

| COMP  | UTI  | ING-IN-MEMORY                                                  | . 122 |

| 6.1   | Intr | oduction                                                       | . 122 |

| 6.2   | R-F  | FEFET based Energy-Efficient CiM Engine using Differential NVM | . 124 |

| 6.2   | 2.1  | Differential 4T-R NVM                                          | . 124 |

| 6.2   | 2.2  | Memory operations                                              | . 125 |

| 6.2   | 2.3  | Variation analysis                                             | . 128 |

| 6.2   | 2.4  | Computation-in-memory using 4T-R NVM                           | . 129 |

| 6.2   | 2.5  | Array-level results                                            | 132   |

| 6.    | 2.6  | System-level results                                        |           |

|-------|------|-------------------------------------------------------------|-----------|

| 6.3   | IPS  | -CiM: FEFET based CiM Hardware for Performing IPS Workloads |           |

| 6.    | 3.1  | Need for energy-efficiency in IPS                           |           |

| 6.    | 3.2  | Transient computing workloads                               |           |

| 6.    | 3.3  | Proposed FEFET based compute enabled memory                 |           |

| 6.    | 3.4  | Enabling transient computing workloads in-memory            | 147       |

| 6.    | 3.5  | Evaluation                                                  |           |

| 6.4   | Sun  | nmary                                                       | 159       |

| 7. FI | EFEI | BASED ARTIFICIAL INTELLIGENCE HARDWARE FOR                  | TERNARY   |

| PERIC | CION | COMPUTING-IN-MEMORY TO ACCELERATE DEEP NEURAL NE            | TWORKS    |

|       |      |                                                             |           |

| 7.1   | Intr | oduction                                                    |           |

| 7.2   | Ter  | nary Precision Networks                                     |           |

| 7.3   | FEF  | FET based Ternary Compute Enabled Memory                    |           |

| 7.    | 3.1  | Memory Design                                               |           |

| 7.    | 3.2  | Ternary read-write operation                                | 164       |

| 7.    | 3.3  | In-memory ternary scalar multiplication using TeC-Cell      |           |

| 7.    | 3.4  | Ternary dot-product computation                             | 166       |

| 7.    | 3.5  | Variation analysis                                          |           |

| 7.4   | TeC  | C-Array Design                                              | 169       |

| 7.5   | Res  | ults                                                        | 170       |

| 7.    | 5.1  | Array-level                                                 | 170       |

| 7.    | 5.2  | System evaluation                                           |           |

| 7.6   | Sun  | nmary                                                       |           |

| 8. 21 | ) TR | ANSITION METAL DICHALCOGENIDE BASED SPIN-DEVICES E          | XHIBITING |

| LOGI  | C-MI | EMORY SYNERGY                                               | 176       |

| 8.1   | Intr | oduction                                                    | 176       |

| 8.2   | Bac  | kground                                                     | 178       |

| 8.    | 2.1  | Giant spin hall (GSH) effect                                | 178       |

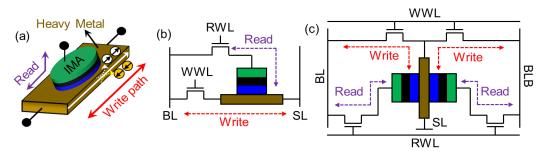

| 8.    | 2.2  | GSH effect based non-volatile memories                      | 178       |

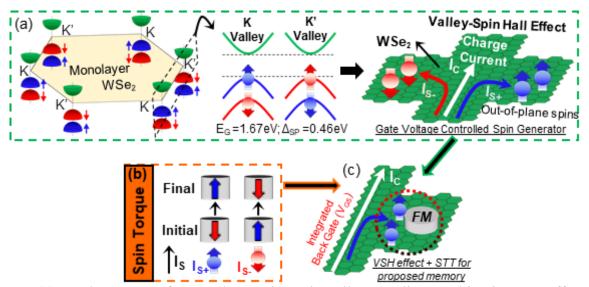

| 8.    | 2.3  | Valley-coupled-spin hall (VSH) effect                       |           |

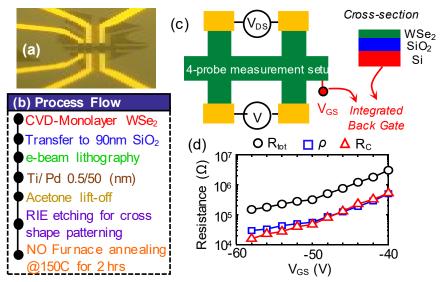

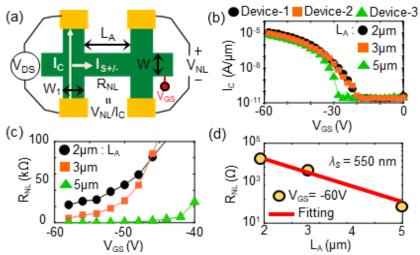

| 8.2   | 2.4 Fabrication and experimental results                                      |               |

|-------|-------------------------------------------------------------------------------|---------------|

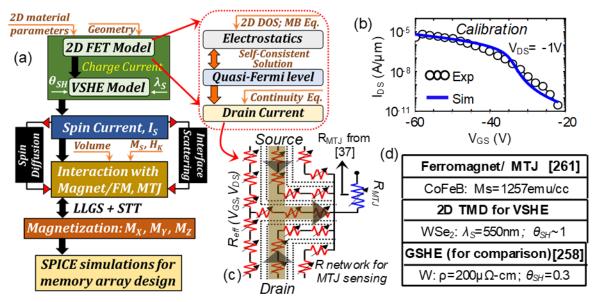

| 8.3   | Simulation Framework                                                          |               |

| 8.4   | VSH Effect based Non-Volatile Memories                                        |               |

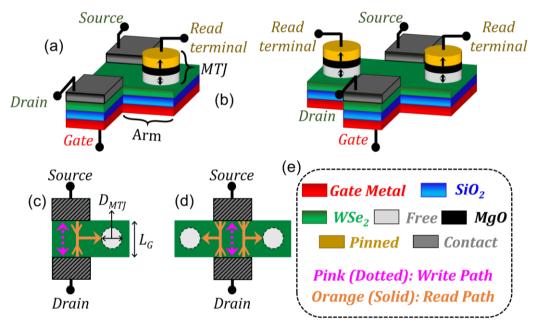

| 8.4   | 1.1 Structure and operation of VSH memory devices                             |               |

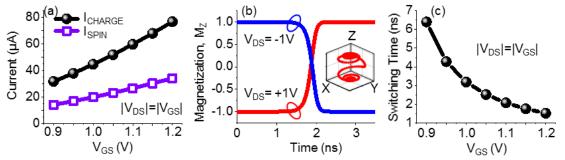

| 8.4   | 1.2 Memory device characteristics                                             |               |

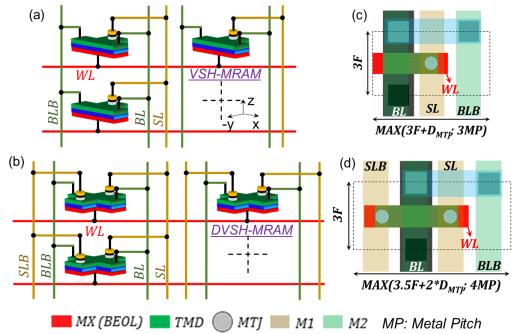

| 8.4   | A.3 Memory array design and operation                                         |               |

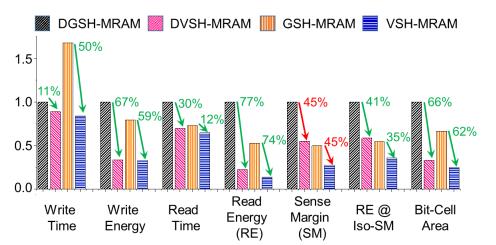

| 8.4   | 1.4 Results                                                                   |               |

| 8.5   | Boolean/Arithmetic Computation-in-Memory                                      |               |

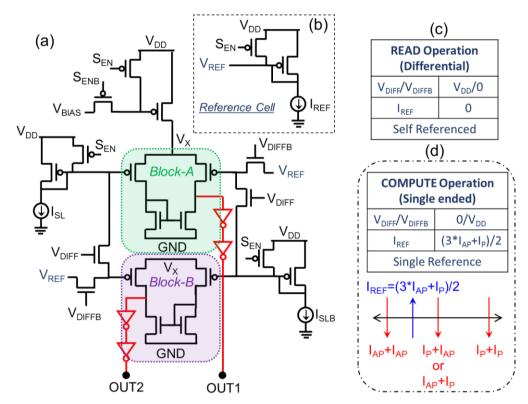

| 8.5   | 5.1 Reconfigurable current sense amplifier                                    |               |

| 8.5   | 5.2 Bit-wise AND and NOR logics                                               |               |

| 8.5   | 5.3 Compute model integrated with RCSA                                        |               |

| 8.5   | 5.4 Results                                                                   |               |

| 8.5   | 5.5 Other CiM architectures using (D)VSH-MRAMs                                |               |

| 8.6   | Ternary Precision Non-Boolean Computation-in-Memory                           |               |

| 8.6   | 5.1 Ternary compute-enabled VSH Cell (TVC)                                    |               |

| 8.6   | 5.2 In-memory ternary multiplication using TeC-Cell                           |               |

| 8.6   | 5.3 Ternary dot product computation                                           |               |

| 8.6   | 5.4 Results                                                                   |               |

| 8.7   | Summary                                                                       |               |

| 9. CC | DNCLUSION                                                                     |               |

| 9.1   | Synopsis                                                                      |               |

| 9.2   | Dissertation Summary                                                          |               |

| 9.2   | 2.1 Integrated non-volatile transistor technologies                           |               |

| 9.2   | 2.2 Non-volatile circuits and their system implications                       |               |

| 9.2   | 2.3 Exploration of the proposed devices and circuits for advanced computing a | architectures |

|       |                                                                               |               |

| 9.3   | Future Outlook                                                                |               |

| 9.3   | 3.1 Development of low-precision AI specific hardware                         |               |

| 9.3   | 8.2 Neural network fabric for approximate edge computing in intermitten       | tly powered   |

| sys   | stems                                                                         |               |

| REFER | RENCES                                                                        |               |

| VITA         |  |

|--------------|--|

| PUBLICATIONS |  |

## LIST OF TABLES

| Table. 4.1 Operating Bias Conditions for 3T-R NVM                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table. 4.2 Hold and Read stability margins for various TFE89                                                                                                                                                            |

| Table. 4.3 Performance metrics of 2T, 3T, 4T and 3T-R memories                                                                                                                                                          |

| Table. 4.4 Operating bias conditions for 2T-R NVM94                                                                                                                                                                     |

| Table. 4.5 Array-level comparison of 2T-R vs 4T NVM                                                                                                                                                                     |

| Table. 5.1 Comparison of energy-delay metrics for flip-flop designs                                                                                                                                                     |

| Table. 6.1 Cyclic Redundancy Code: CiM-based Algorithm147                                                                                                                                                               |

| Table. 6.2 (a) Description of terms used in Table (b). (b): Instr. feature-type energy breakdown from MPS430 synthesis at 45 nm. Note, FEFET-NVM atomic read/write energies are excluded and are to be added separately |

| Table.  7.1  Related work exploring the synergy between in-memory and low-precision computing                                                                                                                           |

| Table. 7.2 Comparison of TeC-Cell DNN with other state-of-the-art DNN architectures175                                                                                                                                  |

| Table. 8.1 Operating bias conditions of VSH-MRAMs and DVSH-MRAMs.     189                                                                                                                                               |

| Table. 8.2 MTJ parameters for (D)VSH-MRAMs and (D)GSH-MRAMs190                                                                                                                                                          |

## LIST OF FIGURES

| Fig. 1.1 Memory and storage system in a computing system showcasing the hierarchy of elements involved with a wide spectrum of performance, cost and density24                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2 Processor and Memory speed over time illustrating the memory wall problem25                                                                                                                                                                                                          |

| Fig. 1.3 (a) Estimated ICT CO <sub>2</sub> emissions (b) Energy consumption distribution of data centers26                                                                                                                                                                                    |

| Fig. 1.4 (a) Phase Change Memory cell (b) Magnetic Tunnel Junction used in STT-MRAMs and (c) Resistive RAM cell. Figure adapted from [50]                                                                                                                                                     |

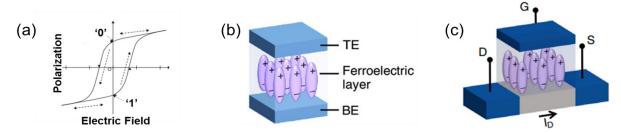

| Fig. 1.5 (a) Polarization vs voltage hysteresis loop of FE illustrating the bi-stable states (b) FE capacitor structure used in FeRAMs and (c) FEFET device structure with FE integrated in the gate stack if a transistor. Figure adapted from [50]                                          |

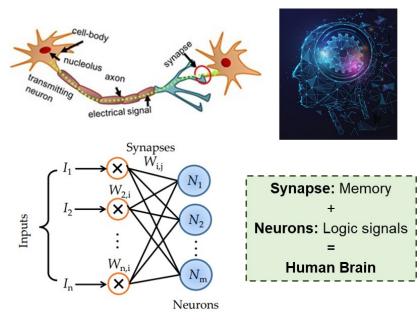

| Fig. 1.6 Brain-inspired computing involving closer integration of logic and memory31                                                                                                                                                                                                          |

| Fig. 2.1 Three generations of ferroelectric memory technologies                                                                                                                                                                                                                               |

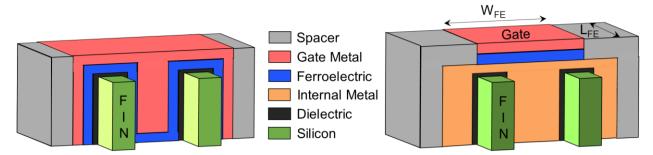

| Fig. 2.2 FEFET devices based on FinFET architecture: (a) without an internal metal layer (IML) between FE and DE, (b) with IML between FE and DE                                                                                                                                              |

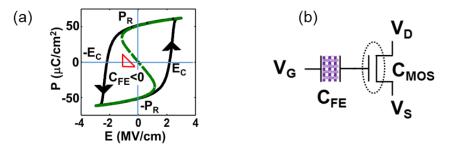

| Fig. 2.3 (a) Polarization vs applied electric field of FE capacitor illustrating the negative capacitance region used for steep-switching applications; figure from [108]. (b) Schematic of FE capacitor connected to the MOS capacitance of the underlying transistor                        |

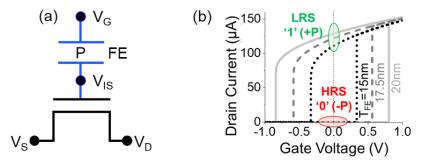

| Fig. 2.4 (a) Schematic of FEFET showing the internal potential and (b) Current-Voltage characteristics of an FEFET illustrating the sensed currents, resistance states for the two bi-stable states; Drain-to-source voltage, $V_{DS}=0.2V$ . $V_{IS} for -P and V_{IS}>V_{TH} for +P40$      |

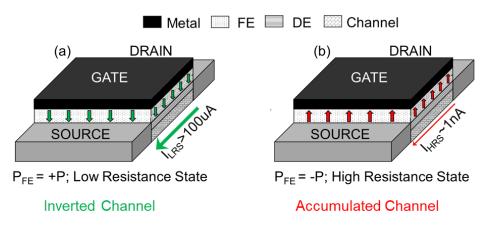

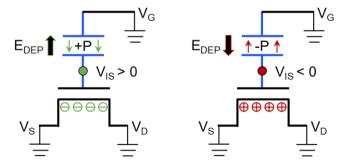

| Fig. 2.5 Planar FEFET device structure showing (a) inversion caused in the channel due to positive polarization (+P) and (b) accumulation due to negative polarization (-P)41                                                                                                                 |

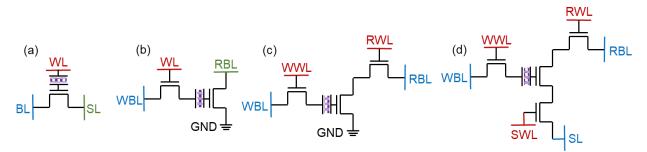

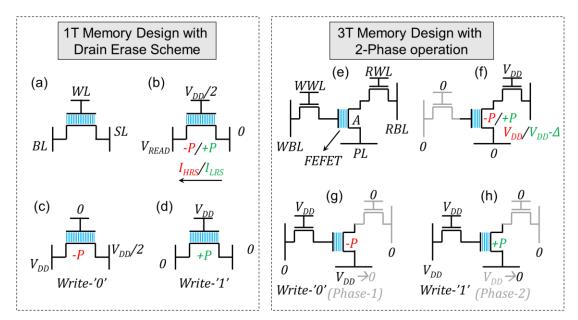

| Fig. 2.6 (a) 1T, (b) 2T, (c) 3T and (d) 4T memory designs based on standard FEFETs42                                                                                                                                                                                                          |

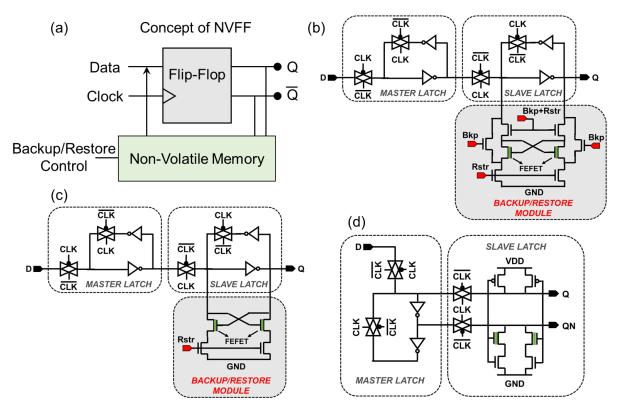

| Fig. 2.7 (a) Concept with in situ NVM as the state backup storage; (b) nvDFF1 [146]; (c) nvDFF2 [145]; (d) nvDFF3 [147]44                                                                                                                                                                     |

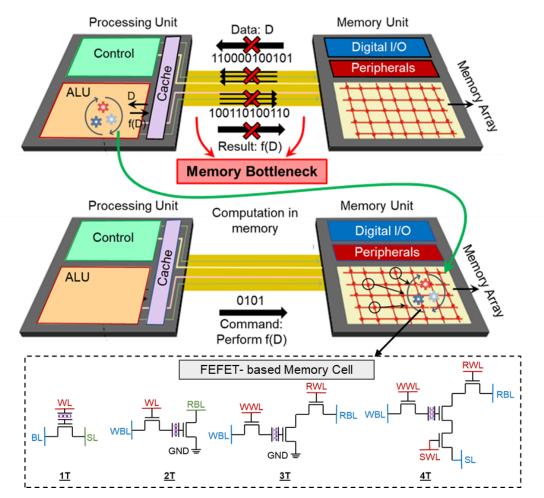

| Fig. 2.8 Concept of computing-in-memory using ferroelectric memory technologies. Adapted from [156]45                                                                                                                                                                                         |

| Fig. 2.9 Techniques to mitigate the use of negative bias for polarization switching: (a-d) Drain-<br>erase bias scheme used for 1T memory cells placed in a cross-point fashion and (e-h) example of<br>2-phase scheme used in a 3T memory cell to write bit- '0' and '1' in different phases |

| Fig. 2.10 Depolarization issues in FEFET/FEMFET due to $V_{IS} \neq 0V$                                                                                                                                                                                                                       |

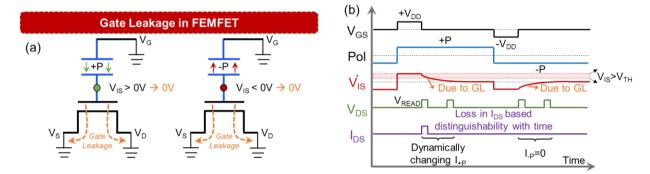

| Fig. 2.11 (a) Gate leakage in FEMFET due to floating IML resulting in (d) loss in resistance-based drain current based distinguishability                                                                                                                                                     |

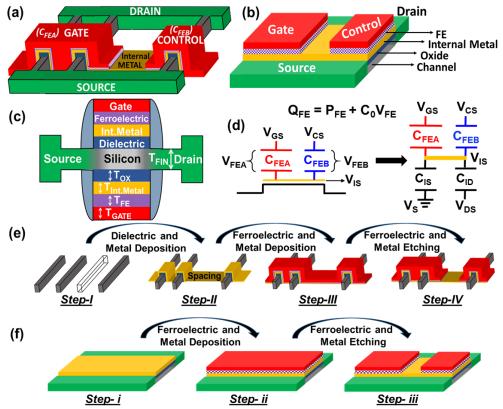

| Fig. 3.1 (a) Proposed R-FEFET with 3 fins (b) R-FEFET realized using planar FET (c) Cross Section of (a). (d) Schematic and capacitance network of R-FEFET. Process flow for R-FEFET                                                                                                          |

| based on (e) FinFET and (f) planar structures. Note, spacing between FE <sub>A</sub> and FE <sub>B</sub> can be changed according to design rules of technology node                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

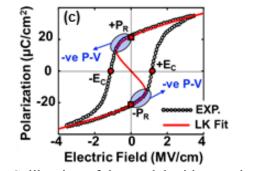

| Fig. 3.2 Calibration of the model with experiments from [113]56                                                                                                                                                                                                                                        |

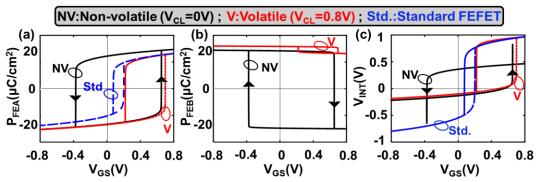

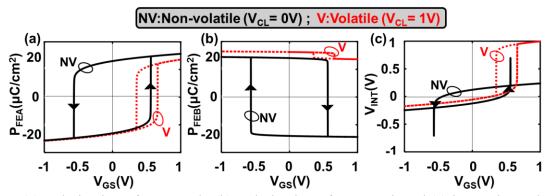

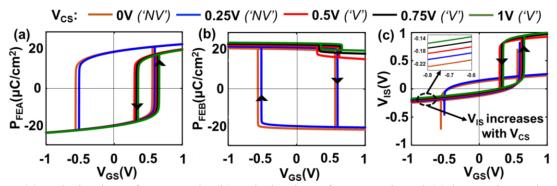

| Fig. 3.3 (a) Polarization of FE <sub>A</sub> stack, (b) Polarization of FE <sub>B</sub> stack and (c) internal metal voltage versus gate voltage. $V_{DS}$ =0V and $T_{FE}$ =8nm                                                                                                                       |

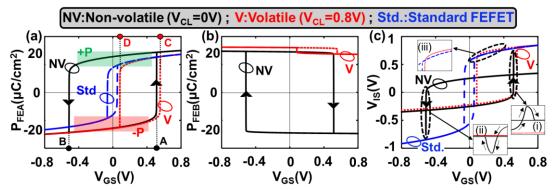

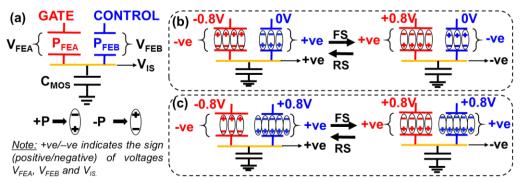

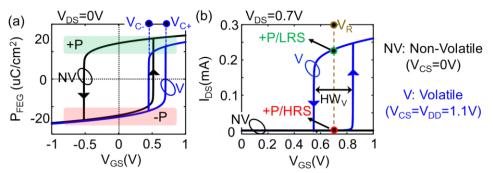

| Fig. 3.4 (a) Schematic of R-FEFET. Device operation in (b) non-volatile mode and (c) volatile mode. FS: Forward Sweep, RS: Reverse sweep                                                                                                                                                               |

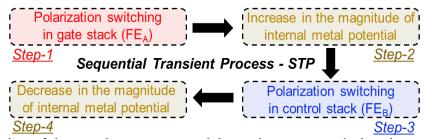

| Fig. 3.5 Illustration of the step-by-step sequential transient process during the non-volatile mode of operation in the proposed R-FEFETs                                                                                                                                                              |

| Fig. 3.6 (a) Polarization of $FE_A$ stack, (b) Polarization of $FE_B$ stack and (c) internal metal voltage versus gate voltage. $V_{DS}=0.3V$ ; $T_{FE}=8nm$                                                                                                                                           |

| Fig. 3.7 (a) Polarization of FE <sub>A</sub> stack, (b) Polarization of FE <sub>B</sub> stack and (c) internal metal voltage versus gate voltage for planar R-FEFETs                                                                                                                                   |

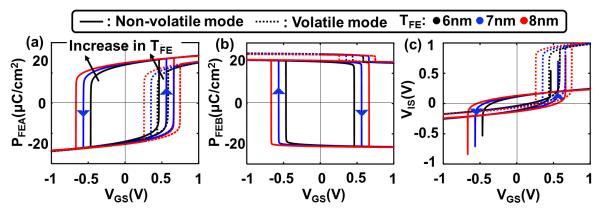

| Fig. 3.8 (a) Polarization of FE <sub>A</sub> stack, (b) Polarization of FE <sub>B</sub> stack and (c) internal metal voltage versus gate voltage for planar R-FEFETs for $T_{FE} = 6, 7, 8$ nm. $V_{DS}=0$ V; $W_{FEA}=44$ nm; $W_{FEB}=33$ nm                                                         |

|                                                                                                                                                                                                                                                                                                        |

| Fig. 3.9 (a) Polarization of FE <sub>A</sub> stack, (b) Polarization of FE <sub>B</sub> stack and (c) internal metal voltage versus gate voltage for V <sub>CS</sub> varying from $0V \rightarrow 1V$ . V <sub>DS</sub> = $0V$ ; T <sub>FE</sub> =7nm; W <sub>FEA</sub> =44nm; W <sub>FEB</sub> =33nm. |

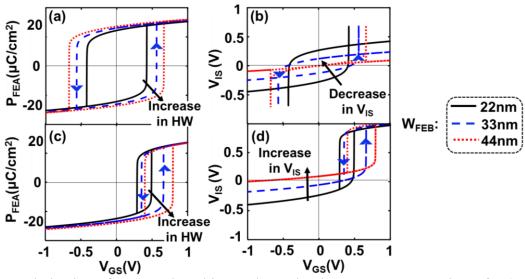

| Fig. 3.10 Polarization of FE <sub>A</sub> stack and internal metal voltage versus gate voltage for (a, b) 'NV' and (c, d) 'V' mode for $W_{FEB} = 22$ , 33, 44nm. $V_{DS}=0V$ ; $W_{FEA}=44nm$ ; $T_{FE}=7nm$ ; HW: Hysteresis Width                                                                   |

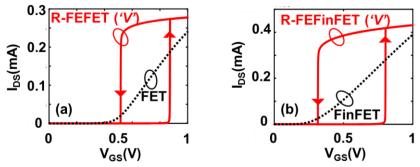

| Fig. 3.11 Transfer characteristics of (a) planar and (b) FinFET based R-FEFET with $V_{DS}$ =0.5V66                                                                                                                                                                                                    |

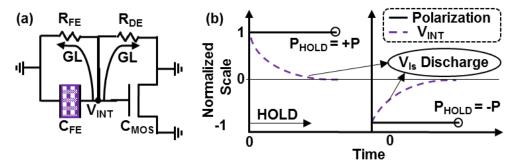

| Fig. 3.12 (a) Equivalent circuit representation of the FEFET, showing gate leakage (GL). (b) Transient simulations showing polarization retention with $V_{IS}$ discharge due to GL. $P_{HOLD}$ = Retained Polarization                                                                                |

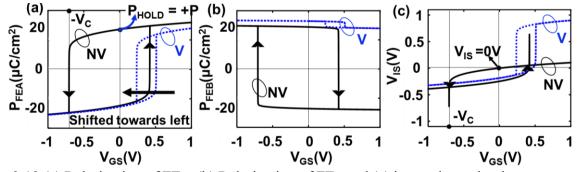

| Fig. 3.13 (a) Polarization of $FE_A$ stack, (b) Polarization of $FE_B$ stack and (c) internal metal voltage versus gate voltage when $P_{HOLD} = +P$ . $V_{DS}=0V$ ; $T_{FE}=7nm$ ; $W_{FEA}=44nm$ ; $W_{FEB}=33nm$ ; HM: Hold Margin                                                                  |

| Fig. 3.14 (a) Polarization of $FE_A$ stack, (b) Polarization of $FE_B$ stack and (c) internal metal voltage versus gate voltage when $P_{HOLD} = -P$ . $V_{DS}=0V$ ; $T_{FE}=7nm$ ; $W_{FEA}=44nm$ ; $W_{FEB}=33nm$ ; HM: Hold Margin                                                                  |

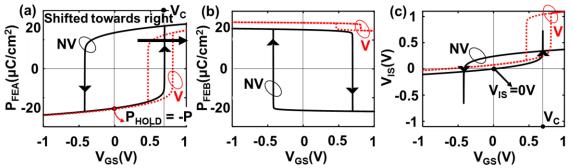

| Fig. 3.15 Transfer characteristics of (a) planar and (b) FinFET based R-FEFET in the presence of gate leakage with $V_{DS}=0.5V$ 70                                                                                                                                                                    |

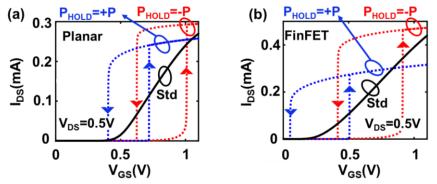

| Fig. 3.16 R-FEFET device characteristics (a) without GL, with GL for (b, c) $P_{HOLD} = +P$ and (d, e) $P_{HOLD} = -P$ . Modes A and B are non-volatile (NV; $V_{CS}=0V$ ); modes C and D are volatile (V; $V_{CS}=V_{DD}$ )                                                                           |

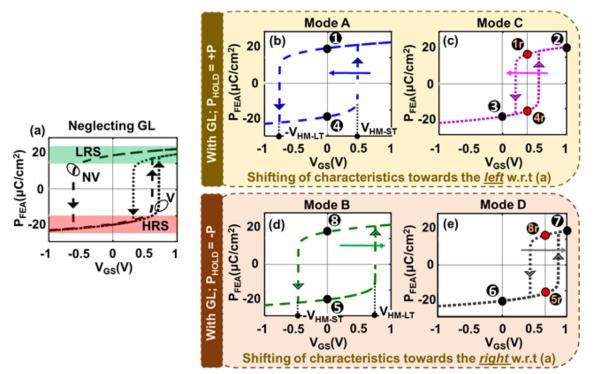

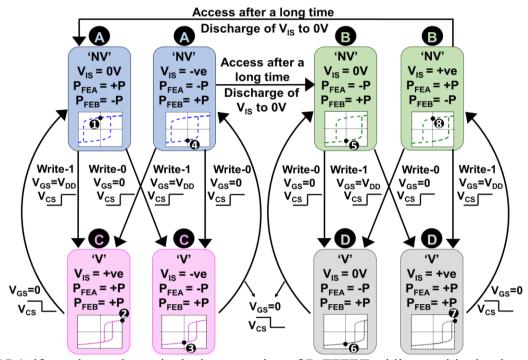

| Fig. 3.17 Self-consistent dynamic device operation of R-FEFET while transitioning between the 'V' and 'NV' modes (A, B, C and D)                                                                                                                                                                       |

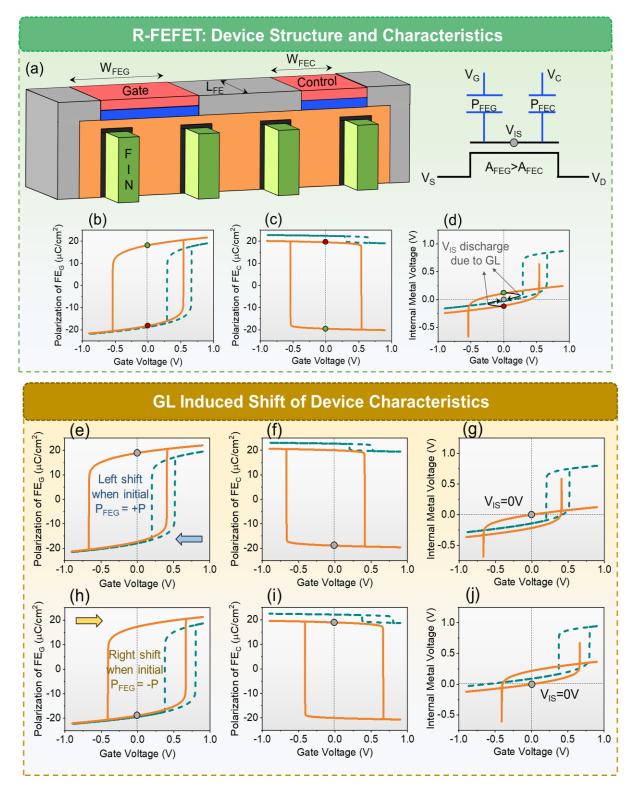

| Fig. 3.18 R-FEFET device design and schematic proposed with $A_{FEG}$ ( $W_{FEG}*L_{FE}$ ) : $A_{FEC}$ ( $W_{FEC}*L_{FE}$ ) >1. $P_{FEG}$ , $P_{FEC}$ and $V_{IS}$ vs $V_{GS}$ (b, c, d) without GL consideration, (e, f, g) with GL and initial $P_{FEG}=+P$ and (h, i, j) with GL and initial $P_{FEG}=-P$ , respectively                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

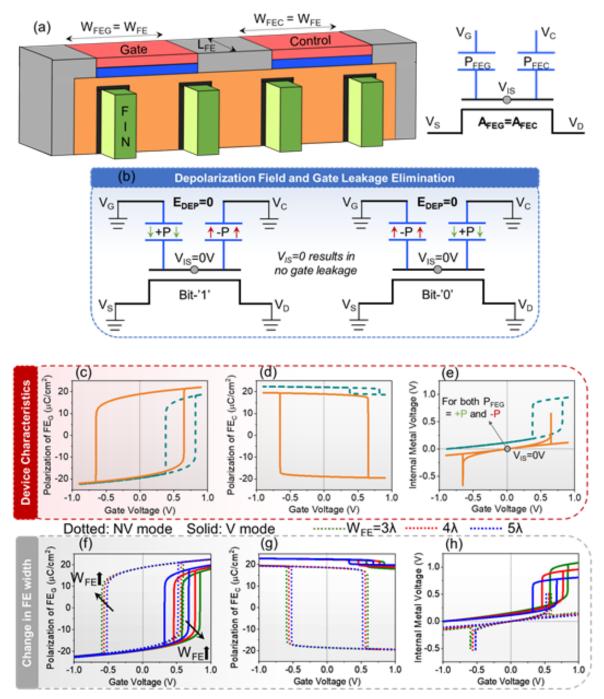

| Fig. 3.19 (a) R-FEFET <sub>SYM</sub> device design and schematic with $A_{FEG}$ : $A_{FEC} = 1$ . (b) Elimination of depolarization fields in 'NV' mode at $V_{GS}=0V$ . (c) $P_{FEG}$ , (d) $P_{FEC}$ , and (e) $V_{IS}$ vs $V_{GS}$ irrespective of initial $P_{FEG}$ . (f) $P_{FEG}$ , (g) $P_{FEC}$ , and (h) $V_{IS}$ vs $V_{GS}$ for varying $W_{FE}$ |

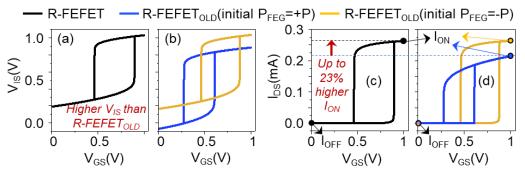

| Fig. 3.20 (a, b) V <sub>IS</sub> vs V <sub>GS</sub> and (c, d) I <sub>DS</sub> vs V <sub>GS</sub> for R-FEFET <sub>SYM</sub> and R-FEFET, considering initial P <sub>FEG</sub> dependent shifts. V <sub>DS</sub> =0.2V                                                                                                                                      |

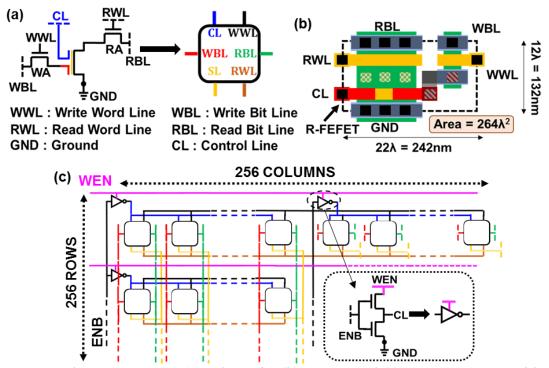

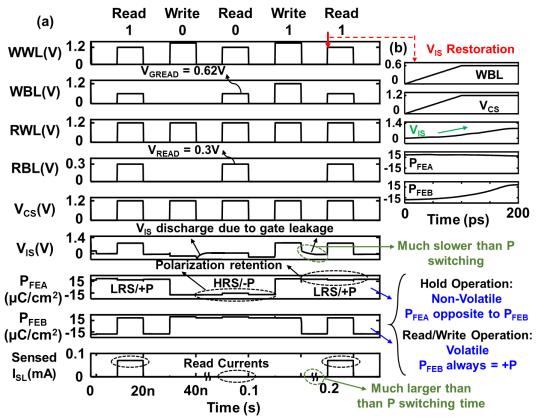

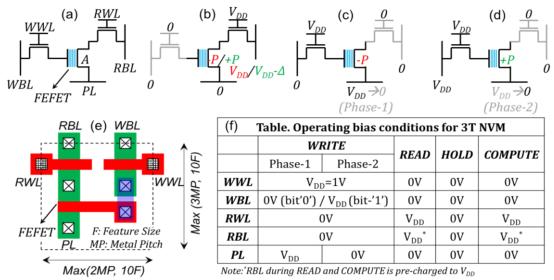

| Fig. 4.1 Proposed 3T-R memory: (a) Schematic, (b) Layout and (c) 256X256 Array with 64-bit word.                                                                                                                                                                                                                                                            |

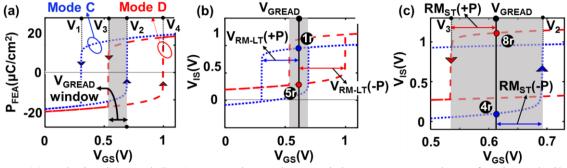

| Fig. 4.2 (a) Polarization and (b, c) Internal metal potential versus gate voltage for the volatile mode of operation with P <sub>HOLD</sub> =+P and -P                                                                                                                                                                                                      |

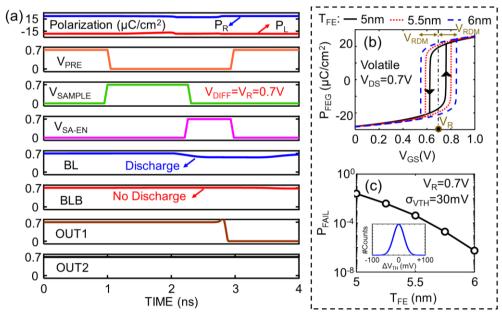

| Fig. 4.3 (a) Transient waveforms of the proposed 3T-R memory design (b) $V_{IS}$ restoration transient when $P_{FEA}=+P$ and initial $V_{IS}=0V$                                                                                                                                                                                                            |

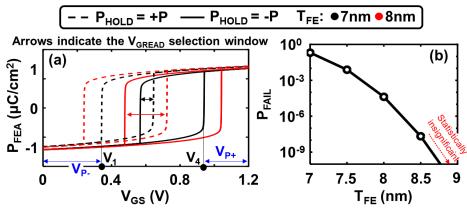

| Fig. 4.4 (a) Polarization of $FE_A$ for varying $T_{FE}$ considering $P_{HOLD}=+P$ and $-P$ (b) Probability of failure during memory access considering $T_{FE}$ and $V_{TH}$ variations                                                                                                                                                                    |

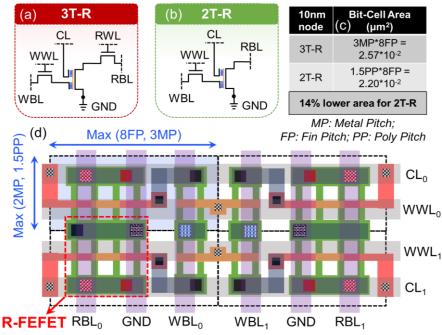

| Fig. 4.5 Schematic of proposed (a) 3T-R and (b) 2T-R NVMs. (c) Bit-cell area comparison of 3T-R and 2T-R. (d) 2X2 layout of the 2T-R array                                                                                                                                                                                                                  |

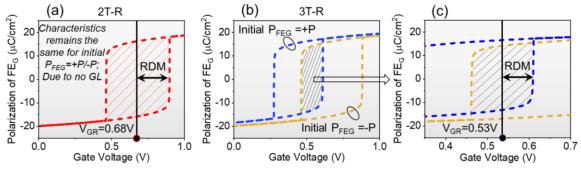

| Fig. 4.6 $P_{FEG}$ vs $V_{GS}$ in the volatile mode for R-FEFET in (a) 2T-R and (b, c) 3T-R NVMs (for both initial $P_{FEG} = +P$ and $-P$ ). Shaded region is the $V_{GR}$ selection window. $V_{READ}=0.2V$                                                                                                                                               |

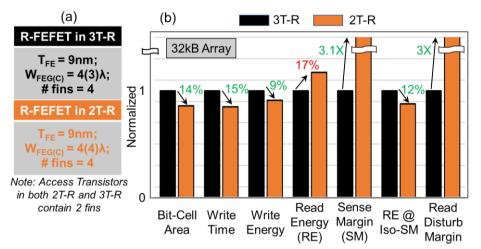

| Fig. 4.7 (a) Device parameters used for 3T-R and 2T-R NVMs. (b) Array-level results of 3T-R and 2T-R for various metrics                                                                                                                                                                                                                                    |

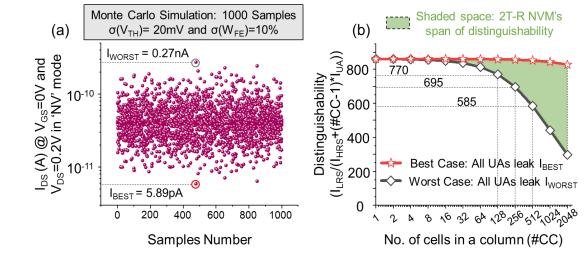

| Fig. 4.8 Monte Carlo simulation result of $I_{DS}$ for 1000 R-FEFET <sub>SYM</sub> device samples with $\sigma(V_{TH})=20mV$ and $\sigma(W_{FE})=15\%$ (b) Plot of distinguishability vs #CC depicting the proposed 2T-R NVM's span of distinguishability100                                                                                                |

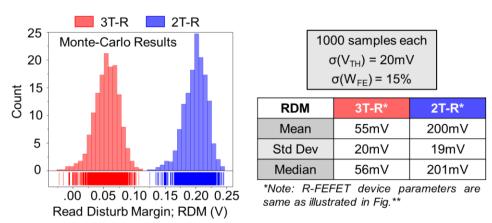

| Fig. 4.9 Monte Carlo simulation results of RDM for 1000 samples of each 2T-R and 3T-R NVMs with $\sigma(V_{TH})=20$ mV and $\sigma(W_{FE})=15\%$                                                                                                                                                                                                            |

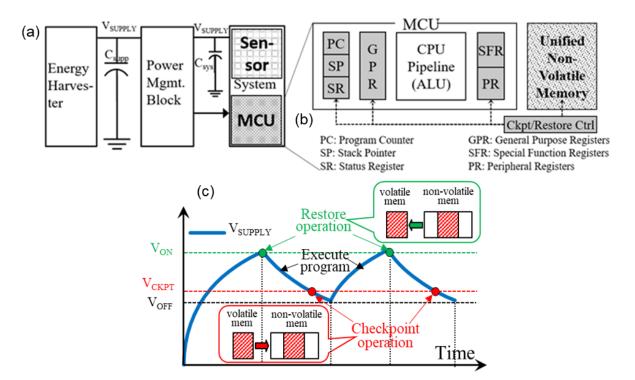

| Fig. 5.1 (a) Conceptual diagram of an intermittently powered system (IPS) (b) MCU core registers and unified NVM mapped to R-FEFET-based NVFFs (RNVFF-1 and RNVFF-2) and NVM (3T-R) respectively (c) Energy profile from an energy harvesting source                                                                                                        |

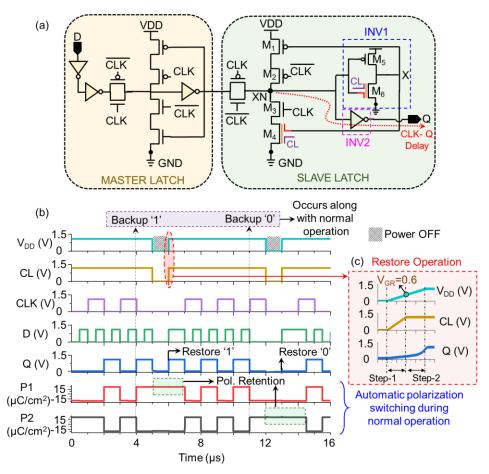

| Fig. 5.2 (a) Schematic of RNVFF-1 (b) Transient waveforms showcasing auto-backup operation with polarization switching along with normal operation, (c) two-step restore operation106                                                                                                                                                                       |

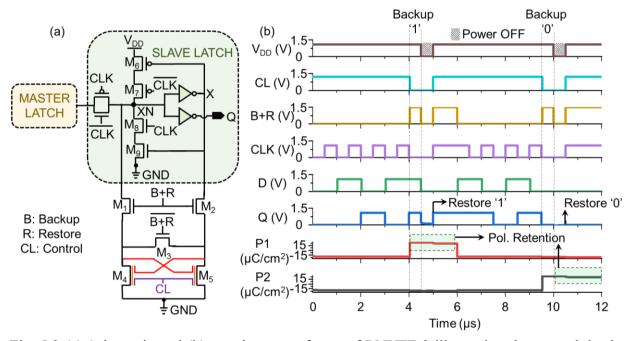

| Fig. 5.3 (a) Schematic and (b) transient waveforms of RNVFF-2 illustrating the normal, backup and restore operations                                                                                                                                                                                                                                        |

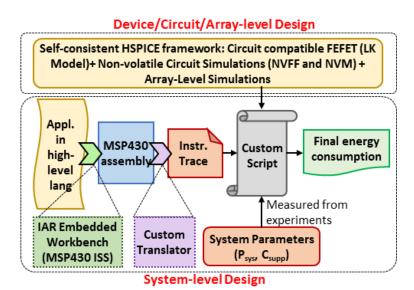

| Fig. 5.4 Experimental Methodology for IPS evaluation112                                                                                                                                                                                                                                                                                                     |

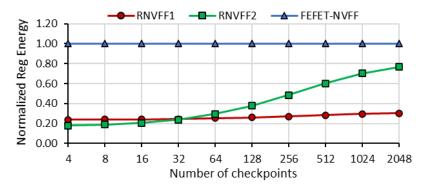

| Fig. 5.5 Normalized core register energy consumption of the different NVFF designs for synthetic benchmarks generated by varying the number of checkpoints                                                                                                                                                                                                  |

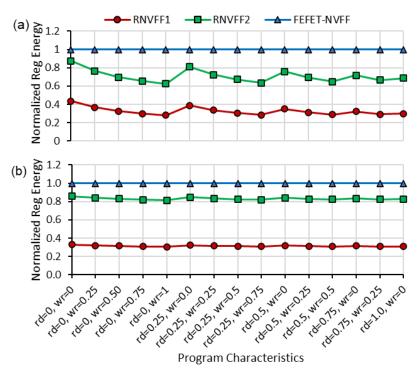

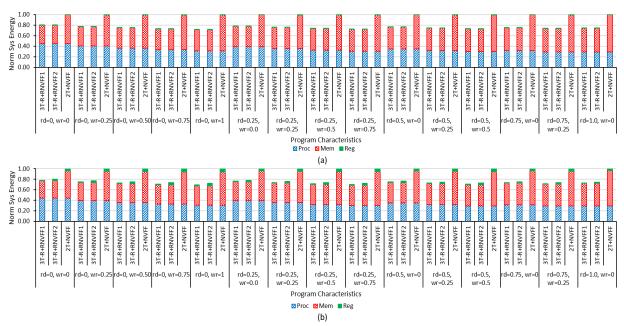

| Fig. 5.6 Normalized core register energy consumption of different NVFF designs for synthetic benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

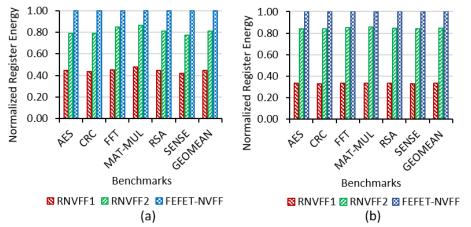

| Fig. 5.7 Normalized core register energy consumption of different NVFF designs for real benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$                                                                              |

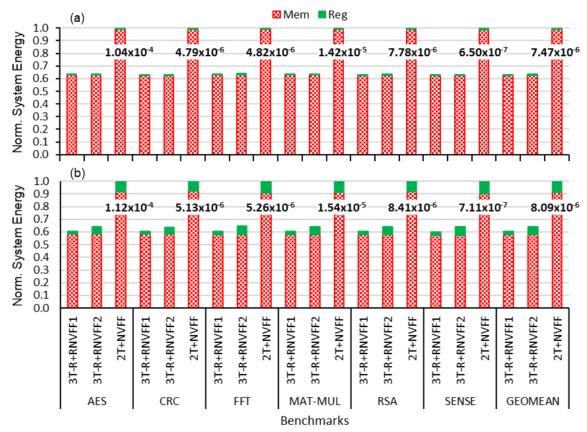

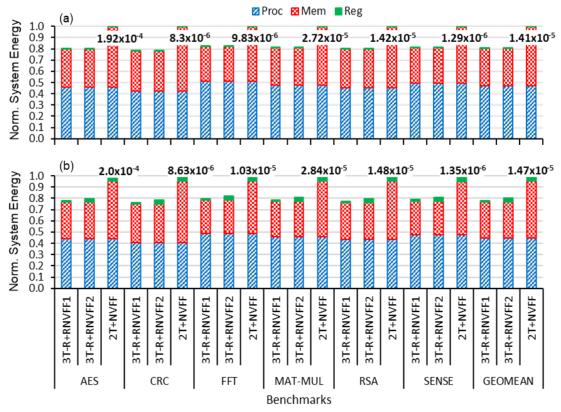

| Fig. 5.8 Normalized total memory (tot mem) energy consumption of different NVFF+NVM designs for real benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$ 117                                                             |

| Fig. 5.9 Normalized system energy (tot sys) consumption of different NVFF+NVM designs for real benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$                                                                       |

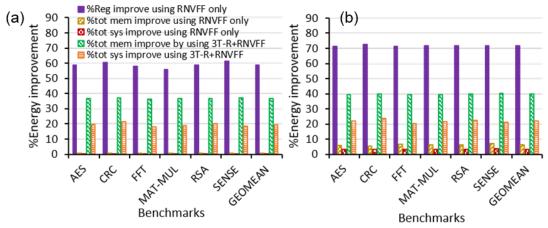

| Fig. 5.10 Register, memory and system-level energy improvements of different NVFF+NVM designs for real benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$                                                               |

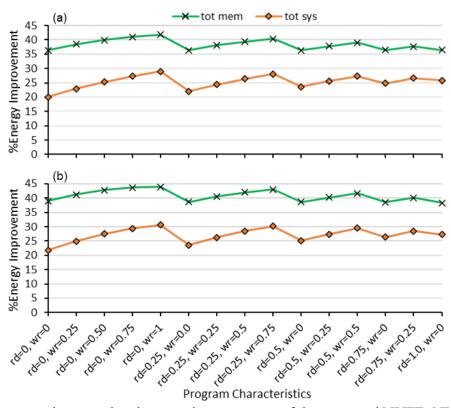

| Fig. 5.11 Memory and system-level energy improvement of the proposed NVFF+NVM design for synthetic benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$                                                                   |

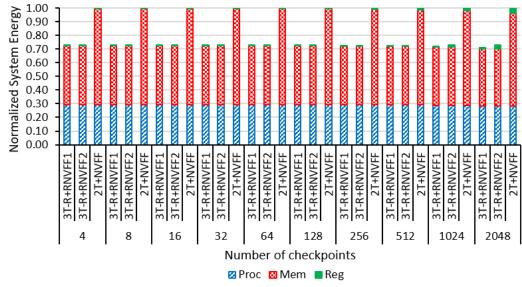

| Fig. 5.12 Normalized system energy consumption of different NVFF+NVM designs for synthetic benchmarks using (a) $C_{SUPP} = 10 \text{ nF}$ and (b) $C_{SUPP} = 1 \text{ nF}$                                                                           |

| Fig. 5.13 Normalized system energy consumption of different NVFF+NVM designs for synthetic benchmarks generated by varying the number of checkpoints                                                                                                   |

| Fig. 6.1 (a) Memory bottleneck in tradition von-Neumann computing systems (b) Memory wall problem                                                                                                                                                      |

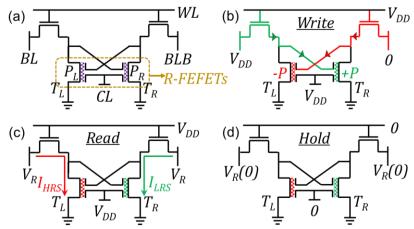

| Fig. 6.2 (a) Proposed 4T-R memory cell schematic with cross-coupled R-FEFETs. Schematic with biasing for (b) Write, (c) Read and (d) Hold operations of the proposed R-FEFET based 4T-R memory                                                         |

| Fig. 6.3 (a) Layout and (b) Bias conditions for the proposed 4T-R memory                                                                                                                                                                               |

| Fig. 6.4 (a) Polarization of $FE_G$ (P <sub>FEG</sub> ) and (b) Drain Current (I <sub>DS</sub> ) vs Gate voltage (V <sub>GS</sub> ) for Non-volatile and Volatile modes of operation                                                                   |

| Fig. 6.5 (a) Transient waveforms during read. (b) $P_{FEG}$ vs $V_{GS}$ in the 'V' mode for various $T_{FE}$ . (c) Probability of failure for the 4T-R memory, considering $V_{TH}$ variations (inset shows the $V_{TH}$ variation histogram)          |

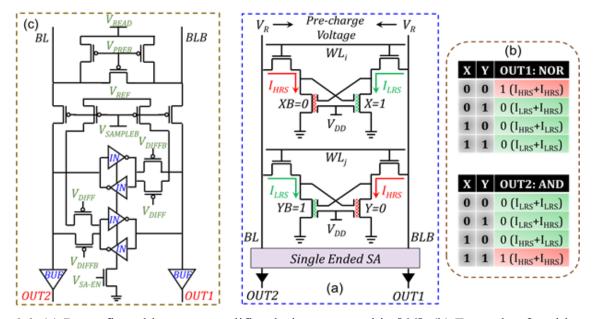

| Fig. 6.6 (a) Reconfigurable sense amplifier design proposed in [66]. (b) Example of multi-word line assertion and currents through R-FEFETs during compute operations (c) Truth tables for the naturally generated NOR (OUT1) and AND (OUT2) functions |

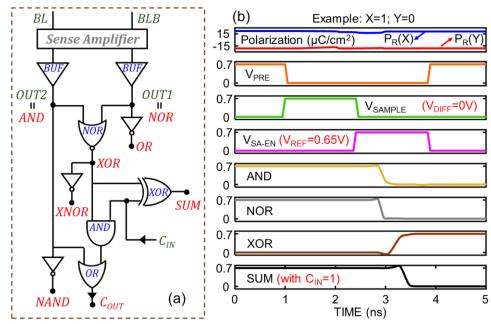

| Fig. 6.7 (a) Proposed compute module/CM which is integrated with RSA. (b) Simulation waveforms showing various logic functionalities                                                                                                                   |

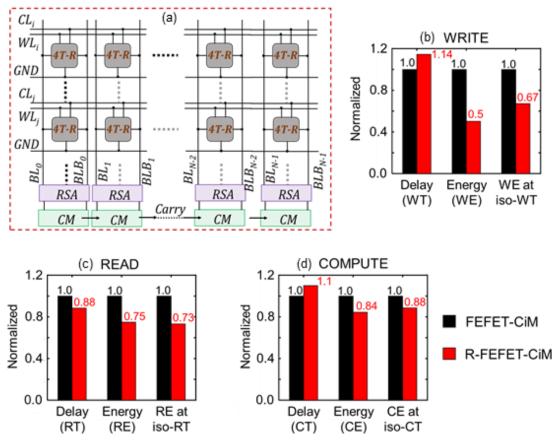

| Fig. 6.8 (a) R-FEFET-CiM array architecture. Array-level comparison of the normalized delay, energy and energy at iso-delay for the (b) write, (c) read and (d) compute operations of the proposed R-FEFET-CiM with respect to FEFET-CiM               |

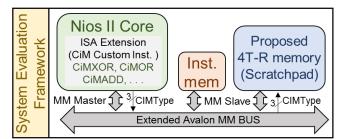

| Fig. 6.9 Simulation framework used for system-level evaluation                                                                                                                                                                                         |

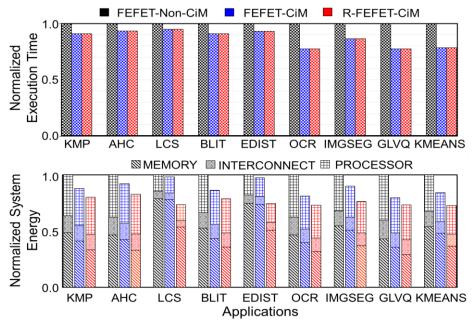

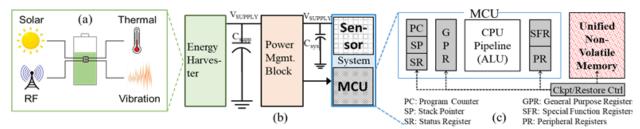

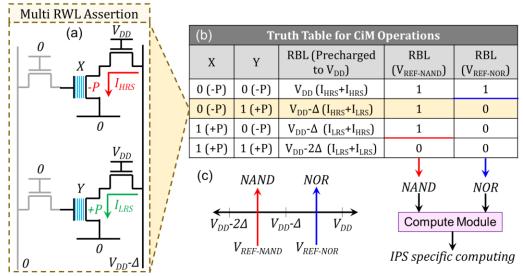

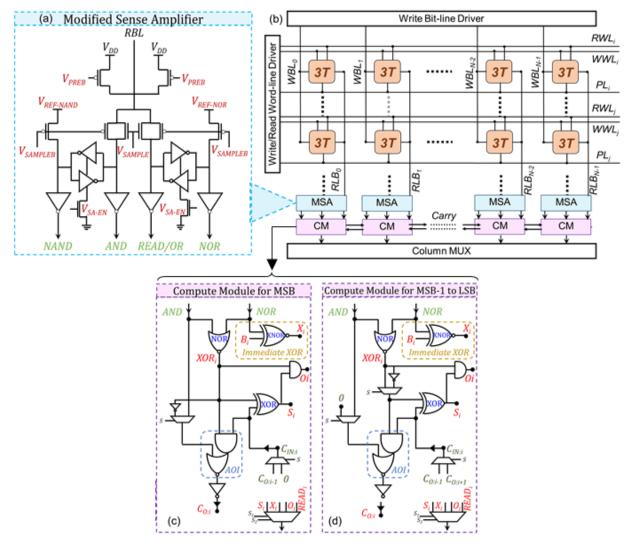

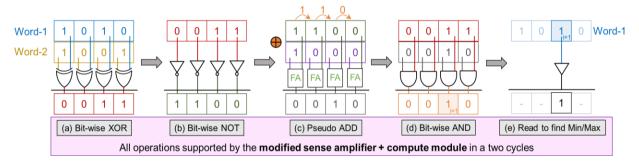

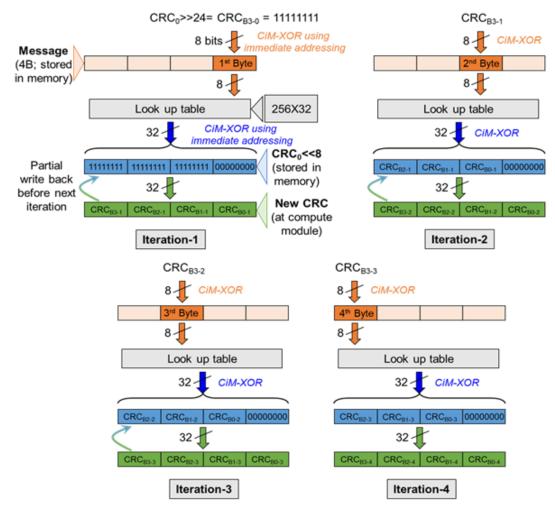

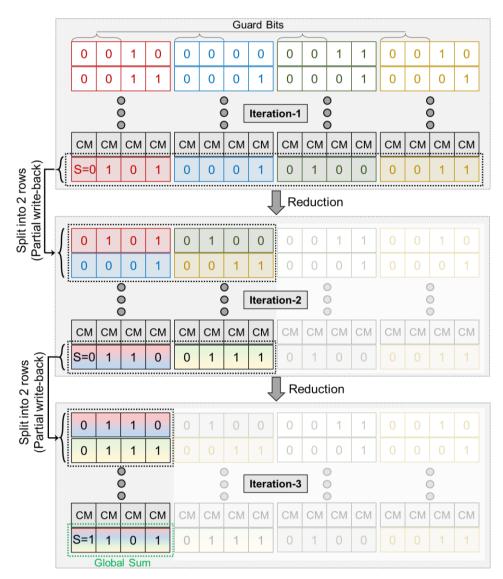

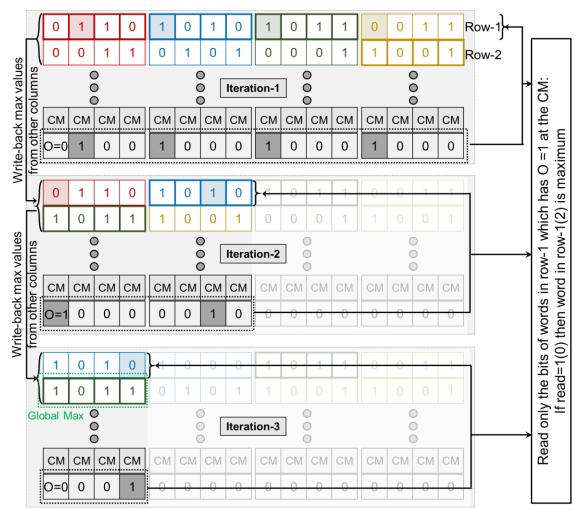

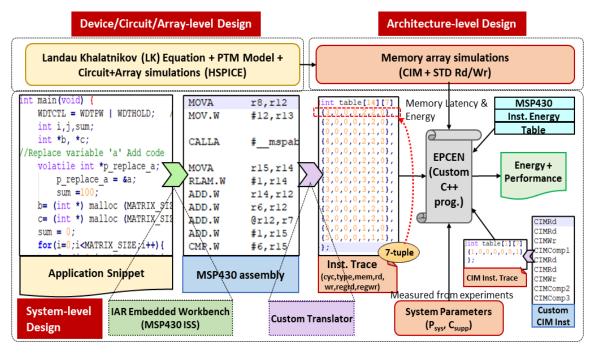

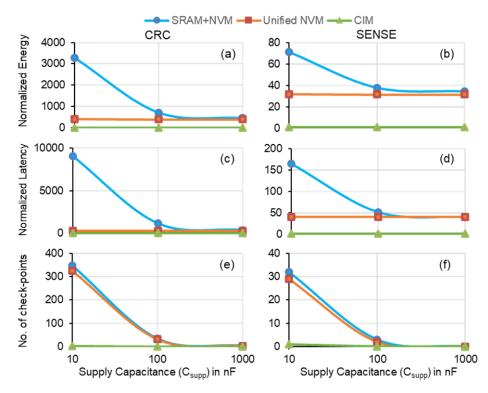

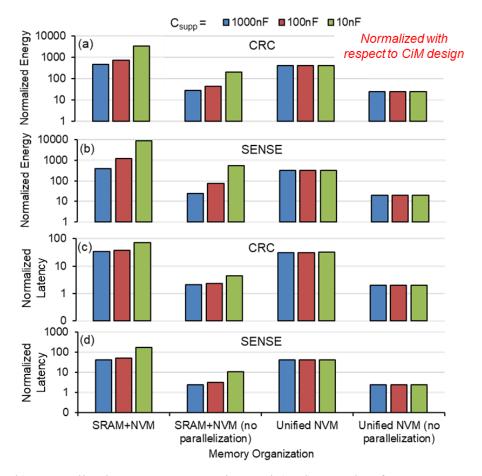

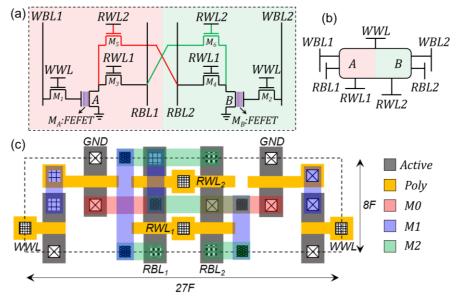

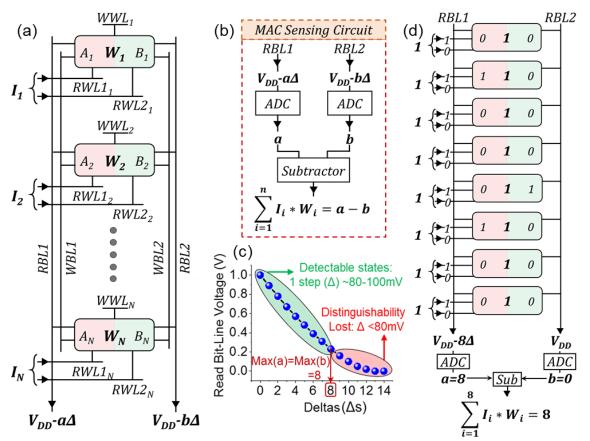

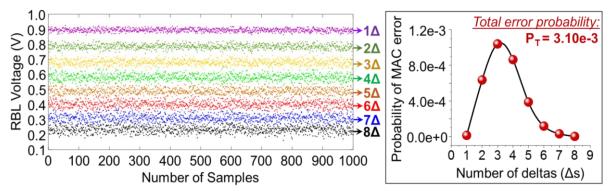

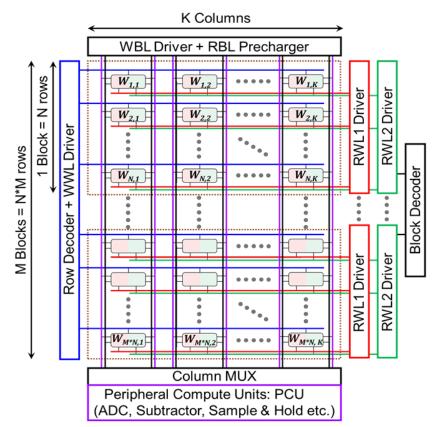

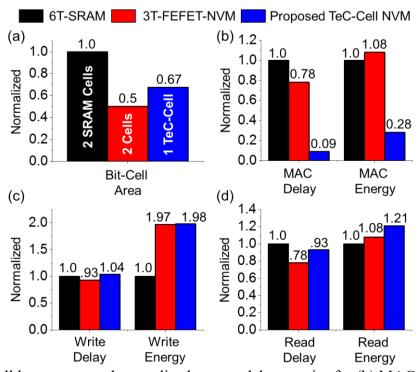

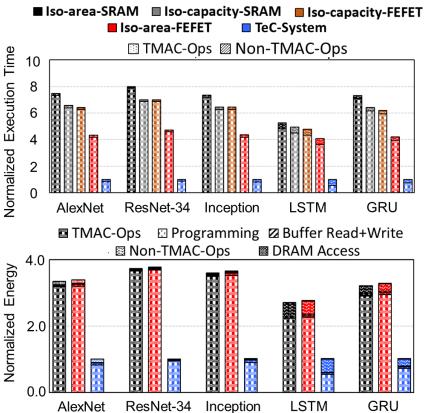

Fig. 6.10 (a) Execution time and (b) total system energy consumption of the proposed R-FEFET-CiM in comparison with FEFET-CiM and FEFET-Non-CiM for various application benchmarks. Iso-performance for FEFET-CiM and R-FEFET-CiM has been achieved by tuning V<sub>DD</sub>......135 Fig. 6.11 (a) Sources for energy harvesting (b) Conceptual diagram of an intermittently powered Fig. 6.12 (a) 3T FEFET memory cell schematic. Schematic with biasing for (b) Read, (c) Write '0' in phase-1 and (d) Write '1' in phase-2. (e) Layout and (f) operating bias conditions of 3T Fig. 6.13 (a) Example of multi RWL assertion for in-memory computation. (b) Truth table for RBL discharge during multi-RWL assertion. (c) Voltage reference location for achieving bit-wise Fig. 6.14 Modified sense amplifier used to simultaneously generate AND and NOR logics. (b) Schematic of the 3T NVM array (c) Compute module used in the column of (c) MSB bit and (d) Fig. 6.15 CiM flow for performing minimum/maximum operations. (a) Bit-wise XOR (b) bit-wise NOT of the XOR result (c) pseudo-ADD operation of the NOT result (d) bit-wise AND of XOR and pseudo-ADD results (e) Read bit of any word corresponding to the set bit location of the AND Fig. 6.16 CiM flow for performing cyclic redundancy check. 32-bit message has 4 iterations, each Fig. 6.17. Example of CiM flow for performing global sum operation which is required for average Fig. 6.18. Example of CiM flow for performing global maximum operation......151 Fig. 6.19 IPS-CiM Energy and Performance Simulation Framework......153 Fig. 6.20. (a and b) Normalized system energy consumption, (c and d) Speedup achieved by IPS-CiM, (e and f) Number of checkpoints for SRAM+NVM, Unified NVM, and IPS-CiM systems Fig. 6.21 (a, b) Normalized energy consumption and (c, d) Speedup for SRAM+NVM, Unified NVM, and their non-parallel versions for (a, c) CRC and (b, d) SENSE applications. All plots are Fig. 7.1. (a) Circuit design, (b) schematic and (c) layout of ternary compute-enabled non-volatile Fig. 7.2 (a) Input, (b) Weight and (c) Output encoding for ternary compute operations. (d) Example of scalar multiplication in TeC-Cell. (e) Truth table for all permutation of I.E and W.E. ......166 Fig. 7.3 (a) Ternary dot-product computation of input vector I and weight vector W (b) MAC sensing unit consisting of ADCs and subtractor. (c) RBL voltage vs number of  $\Delta$  drops. (d) An example of worst-case input-weight scenario for sensing, resulting in a=8. .....167 Fig. 7.4 (a) Variation analysis with 1000 Monte Carlo sample for each state varying from  $1\Delta$  to

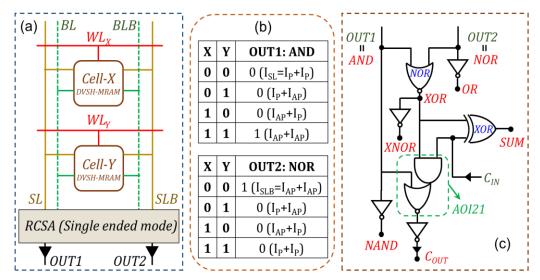

| Fig. 8.13 (a) Reconfigurable current sense amplifier along with (b) reference current generation. (c) Bias conditions for single ended and differential sensing. (d) Reference current used for in-<br>memory compute                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 8.14 (a) Example of multi-word line assertion (b) Truth tables for the natively generated AND (OUT1) and NOR (OUT2) functions (c) compute module attached to RCSA for Boolean logic and ADD                                                                                                                                          |

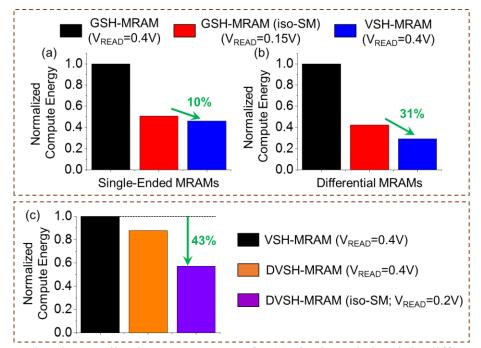

| Fig. 8.15 Array-level normalized compute energy for (a) single-ended and (b) differential memory designs based on VSH and GSH effect. (c) Normalized compute energy consumption of VSH/DVSH-MRAMs                                                                                                                                         |

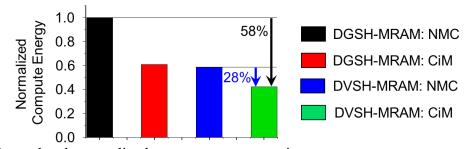

| Fig. 8.16 Array-level normalized compute energy using near-memory compute (NMC) and compute in-memory (CiM) architectures for DGSH-MRAM and DVSH-MRAM                                                                                                                                                                                     |

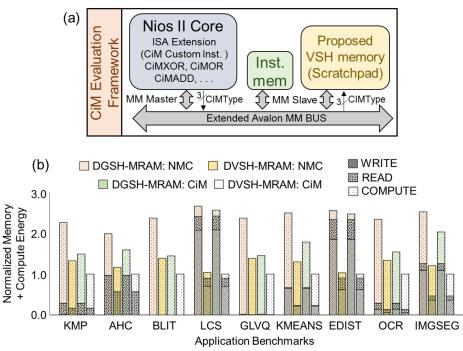

| Fig. 8.17 (a) Simulation framework for system-level evaluation (b) total system energy consumption of the proposed DVSH-MRAM: CiM in comparison with DGSH-MRAM: CiM and DVSH/DGSH-MRAM: NMC for various application benchmarks                                                                                                            |

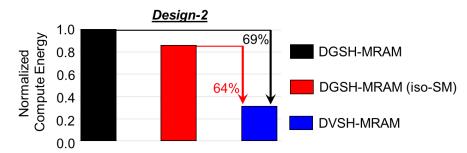

| Fig. 8.18 Array-level normalized compute energy using Design-2 based CiM implementation for DVSH-MRAM and DGSH-MRAM                                                                                                                                                                                                                       |

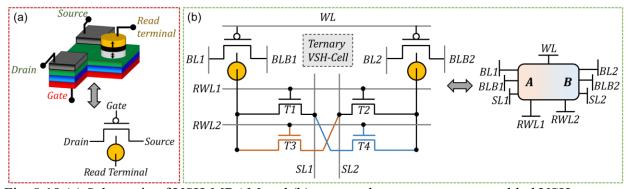

| Fig. 8.19 (a) Schematic of VSH-MRAM and (b) proposed ternary compute-enabled VSH memory cell (TVC)                                                                                                                                                                                                                                        |

| Fig. 8.20 (a) Input, (b) Weight and (c) Output encoding for the proposed TVC. (d) Truth table for all combinations of input and output206                                                                                                                                                                                                 |

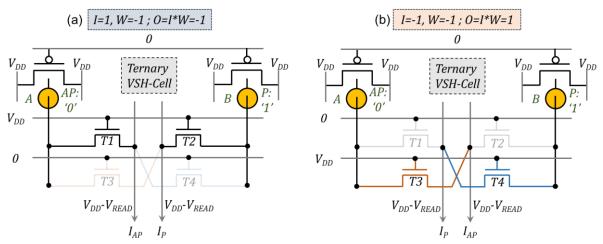

| Fig. 8.21 Examples of scaler ternary precision in-memory multiplication for (a) $I = 1$ , $W = -1$ and (b) $I = -1$ , $W = -1$                                                                                                                                                                                                            |

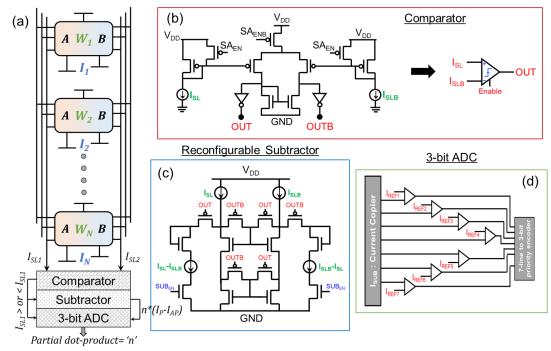

| Fig. 8.22 (a) Schematic of a column in the proposed TVC-Array with peripherals. Schematics of (b) comparator, (b) reconfigurable subtractor and (d) 3-bit ADC designs used in the vector dot-product computation                                                                                                                          |

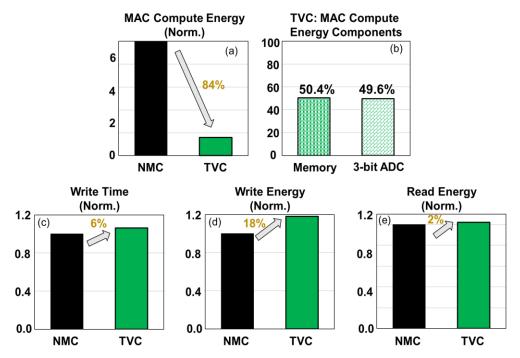

| Fig. 8.23 Array-level results for (a) compute energy of MAC operation vs baseline near-memory computing design (NMC). (b) Split of energy between memory and ADC component for the TVC based design. (c)Write time, (d) write energy and (e) read energy evaluation of the proposed TVC based ternary-in-memory computing vs baseline NMC |

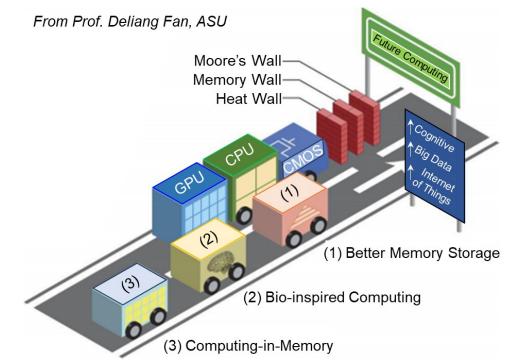

| Fig. 9.1 Illustration of the problem and solution to tackle the challenges of future computing.<br>Adapted from [297]                                                                                                                                                                                                                     |

## LIST OF ABBREVIATIONS

| FEFET                 | Ferroelectric Field Effect Transistor                |

|-----------------------|------------------------------------------------------|

| <b>R-FEFET</b>        | Reconfigurable Ferroelectric Field Effect Transistor |

| NVM                   | Non-Volatile Memory                                  |

| NVFF                  | Non-Volatile Flip-flop                               |

| TMD                   | Transition Metal Dichalcogenides                     |

| IPS                   | Intermittently Powered Systems                       |

| STP                   | Sequential Transient Process                         |

| P <sub>HOLD</sub>     | Hold Polarization                                    |

| GSHE                  | Giant Spin Hall Effect                               |

| VSHE                  | Valley-coupled-Spin Hall Effect                      |

| ML                    | Machine Learning                                     |

| DNN                   | Deep Neural Networks                                 |

| AI                    | Artificial Intelligence                              |

| STT-MRAM              | Spin-Transfer-Torque Magnetic Random-Access Memory   |

| PCM                   | Phase Change Memory                                  |

| RRAM                  | Resistive Ransom Access Memory                       |

| FERAM                 | Ferroelectric Random Access Memory                   |

| CRC                   | Cyclic Redundance Check                              |

| RSA                   | Reconfigurable Sense Amplifier                       |

| RCSA                  | Reconfigurable Current Sense Amplifier               |

| CiM                   | Computation-in-Memory                                |

| GL                    | Gate Leakage                                         |

| RDM                   | Read Disturb Margin                                  |

| MAC                   | Multiply-and-Accumulate                              |

| ADC                   | Analog to Digital Converters                         |

| RFEFET <sub>SYM</sub> | Symmetric R-FEFET                                    |

| RFEFETASYM            | Asymmetric R-FEFET                                   |

| ICT                   | Information and Communication Technology             |

### ABSTRACT

Over the last decade, there has been an immense interest in the quest for emerging memory technologies which possess distinct advantages over the traditional silicon-based memories. The unique opportunities ushered by these technologies such as high integration density, near-zero leakage, non-volatility and, in some cases, excellent CMOS compatibility, has triggered the development of design techniques, enhancing the computation capabilities of various systems. Further, in the era of big data, the emerging memory technologies offer new design opportunities to address a pressing need of achieving close integration of logic and memory sub-systems with an objective to overcome the von-Neumann bottleneck associated with the humungous cost of data transfer between logic and memory. Such a logic-memory coupling not only enables low power computation in standard systems, but also promises high energy efficiency in unconventional compute platforms such as the brain-inspired deep neural networks (DNNs) which have transformed the field of machine learning (ML) in recent years. However, in order to exploit the unique properties of the emerging memory technologies for efficient logic-memory integration, there exists a strong need to explore cross-layer design solutions which can potentially enable efficient computation for current and future generation of systems. Motivated by this, in this dissertation, we harness the benefits offered by the emerging technologies and propose novel devices and circuits which exhibit an amalgamation of logic and memory functionalities. We propose two variants of memory devices: (a) Reconfigurable Ferroelectric transistors (R-FEFET) and (b) Valley-Coupled-Spin Hall (VSH) effect based magnetic random-access memory (VSH-MRAM), which exhibit unique logic-memory unification. Exploiting the intriguing features of the proposed devices, we carry out a cross-layer exploration from device-to-circuits-to-systems for energy efficient computing. We investigate a wide spectrum of applications for the proposed devices including embedded memories, non-volatile logic, compute-in-memory circuits and artificial intelligence (AI) systems.

The first technology of our focus is ferroelectric transistor (FEFET), which is being actively explored for logic and memory applications. Experimental studies have showcased volatile (logic) or non-volatile (memory) characteristics for FEFET by employing static/design time optimizations. However, if run-time tuning of non-volatile and volatile modes can be achieved, several new

avenues for circuit design will open. Inspired by this, we propose Reconfigurable FEFET (R-FEFET), which has the capability to dynamically modulate its operation between volatile and nonvolatile modes, enabling true logic-memory synergy at the device level. Utilizing these unique features of the R-FEFET, we propose an embedded non-volatile flip-flop design (R-NVFF) featuring a fully automatic backup operation (during power shut down) without the need of any external circuitry or signals. Compared to a previously proposed FEFET based NVFF, the proposed R-NVFF exhibits 69% lower check-pointing energy (which includes backup and restore operation). We also propose non-volatile memory (NVM) with highly energy-efficient read and write operations enabled by the dynamic reconfigurability in R-FEFETs. Our proposed NVM exhibits 55% lower write power, 37%-72% lower read power and 33% lower area compared to an FEFET-NVM. Finally, we implement the proposed NVM and R-NVFF in a state-of-the-art intermittently-powered platform and show up to 40% energy savings at the system-level.

Another technology, which has sparked immense interest in spintronic applications, is the Valley-coupled-Spin Hall (VSH) effect in two-dimensional Transition Metal Dichalcogenides (2D TMDs). The unique generation of out-of-plane spin currents in monolayer TMDs can potentially enable efficient switching of nano-magnets. In this dissertation, we propose an emerging spin-based memory device featuring close logic-memory integration utilizing the VSH effect in 2D TMD transistors, where the information is stored in nano-magnets (which are unified with the transistor), for energy efficient computing. We propose two variants of NVM designs, namely single-ended VSH-MRAM and differential DVSH-MRAM. We show that the integrated gate feature exclusive to 2D TMDs, facilitates access transistor-less memory array designs, resulting in ultra-high integration density. We compare the proposed memory designs with the standard Giant Spin Hall (GSH) effect-based memories and showcase 35%-67% lower energy consumption at the circuit-level and up to 3.14X energy efficiency at the system-level in the context of general-purpose computing systems as well as targeted system applications such as energy harvesting platforms.

In addition to traditional computing architectures, the logic-memory synergy in the proposed device technologies, showcase an immense potential for energy-efficient in-memory computation, especially for AI specific hardware running DNN/ML algorithms. We propose R-FEFET and DVSH-MRAM based design of novel compute-enabled memory fabrics. We custom design memory bit-cells which enable massively parallel Boolean and non-Boolean in-memory

computations using minimal array accesses. For example, we propose R-FEFET and DVSH-MRAM based NVM cells which performs natural and simultaneous computation of bit-wise Boolean AND and NOR logics in a single array access. We also propose a compact compute module, attached to the array peripherals, for carrying out other logic and arithmetic operations such as addition. The proposed in-memory computation technique shows up to 71% lower energy consumption compared to existing FEFET and GSH-MRAM based compute-in-memory solutions. Moreover, for targeted energy-autonomous system workloads, we propose application-specific, FEFET inspired CiM fabric, which demonstrate 32X and 40X improvement in energy consumption and performance during edge-sensing, when compared to conventional computing architectures. Lastly, for energy-efficient computing in edge devices, we propose compute-enabled memory cells with ternary-precision, which achieves a sweet spot between accuracy and energyefficiency for DNN workloads. With optimal encoding scheme for the computing elements in synergy with device-circuit co-design, we achieve efficient ternary in-memory dot-product computation with minimal number of transistors per cell. The proposed ternary compute-inmemory arrays show up to 3.4X reduction in energy and 7X improvement in performance when compared to optimized near-memory DNN accelerators. Overall, evaluation results of the proposed CiM techniques in this dissertation, show significant reduction in system energy along with system performance improvement over conventional von-Neumann architecture-based approaches for a wide range of application workloads, thus addressing the critical need for energy efficient logic-memory synergy in future computing platforms.

### **1. INTRODUCTION**

#### 1.1 Data Intensive Computing: Memory Bottleneck and Climate Burden

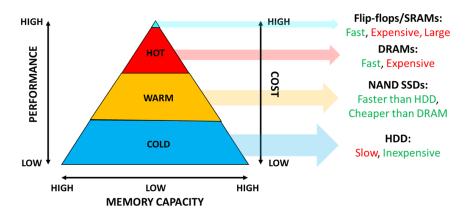

The memory and storage system in modern day computers consists of a hierarchy of devices with various density, speed, and cost (Fig. 1.1) [1]. The hierarchy includes: registers for holding temporary results and variables; caches which act as staging areas for the data and instructions stored in the main memory; main memory to stage data stored in large but slow storage entities, such as hard disk drives (HDDs) or NAND flash. As we enter the era of big data, many emerging data-intensive workloads become pervasive, and mandate very high bandwidth and heavy data movement between the computing units and the memory. Storing and manipulating such a humungous amount of data raises significant challenges in designing high-performance, energy-efficient memory hierarchy. This has been a major concern over the recent years as the systems are expected to be more compact and powerful with data-intensive computing [2], [3].

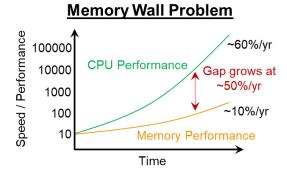

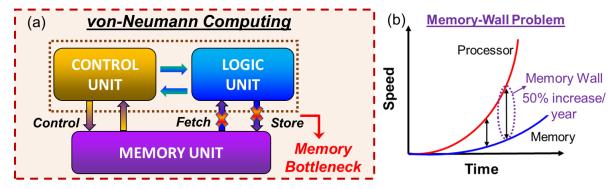

Unfortunately, technology scaling has further aggravated the aforementioned problem of memory and storage systems, significantly slowing the performance improvements of computing systems. Over the years, it has been observed that microprocessor speeds are increasing, but not at the same rate that memory access latencies have decreased. This increasing gap between the pace of processor and the memory has created the "memory wall" problem in which the data movement between the logic and memory component of a system is becoming the bottleneck in present computing architectures (Fig. 1.1-1.2) [4]–[6]. Sources state that the increase in the processing

Fig. 1.1 Memory and storage system in a computing system showcasing the hierarchy of elements involved with a wide spectrum of performance, cost and density.

Fig. 1.2 Processor and Memory speed over time illustrating the memory wall problem.

speed is around 60% every year, while the rate of memory operation has only improved by less than 10% per year, resulting in doubling of the gap between the performance of the processor and memory every 1 to 2 years [6], [7]. Moreover, commodity memory technologies, such as SRAM and DRAM, are facing scalability challenges due to several constraints. Firstly, both SRAM and DRAM are leaky at advanced technology nodes and the leakage power starts dominating for high memory capacity. Results in [8], [9] suggests that 25-40% of total power is attributed to the memory system [8] and the embedded processor caches consume over 40% of the total chip power budget [9]. This can significantly degrade the energy efficiency of systems based on scaled technologies when static leakage power is considered. Secondly, the SRAM/DRAM architectures are facing many difficulties while being scaling down. One challenge is in regard to the large increase in process variations [10], [11]. With the continuous scaling of CMOS devices, variations in key parameters such as threshold voltage ( $V_{TH}$ ), oxide thickness ( $T_{OX}$ ), etc. are growing at an alarming rate [12]. Subsequently, the performance of different die on the same wafer can vary widely, resulting in a significant parametric yield loss, which directly translates into higher manufacturing costs. Another challenge is that its intrinsically hard to scale down. For example, scaling down DRAM below a 20nm process node is extremely challenging due to the difficulty in keeping an adequate amount of cell capacitance [13]. Therefore, the memory and storage systems are becoming a fundamental performance and energy bottleneck in various advanced generation of electronic systems, ranging from cloud servers to end-user devices.

Another harmful aspect of data-intensive computing is their impact on climate change. The current and future generation of computing largely relies on data centers which store and process humungous amounts of data. The data centers themselves consume a lot of power and as per recent reports, nearly 2% of electrical energy utilization in the U.S alone is from the data centers [14]. It

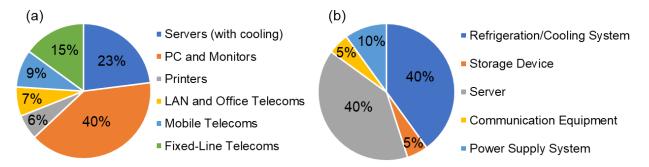

Fig. 1.3 (a) Estimated ICT CO<sub>2</sub> emissions (b) Energy consumption distribution of data centers

is expected that the  $CO_2$  emissions from information and communication technology (ICT) will account for 12% of world-wide emissions by the end of 2020 [15]. These numbers are alarming, especially while considering the explosion in the data demands observed over the recent years.

The energy consumption of data centers may be divided into two categories: computing resources and physical resources (Fig. 1.3). The statistics show that the energy consumption of computing resources accounts for about 50% of the total energy consumption [15]. On the other part, the energy consumption of refrigeration/cooling systems is a major part of energy consumption by physical resources, which accounts for about 40% of the total energy consumption. Scientists believe that this number would vastly increase in the very near future considering the estimate of the 175 zettabytes (175 trillion gigabytes) of data generated by 2025 across the globe [16]. Therefore, we can conclude that servers with the processing elements (which fetch, compute and store data in the memory) and cooling systems are the most substantial energy draining facilities in the data centers. They account for a dominant portion of the total operating costs. Therefore, reducing energy consumption for servers and cooling systems is a key issue to address the sustainable development of data centers.

There are two ways to tackle this problem of carbon emissions from the data centers. The first approach is by efficiently controlling the heat generated as a result of the high computing demands in modern workloads. For example, innovating cooling strategies which consume less energy or re-utilization of the thermal energy generated in partially powering towns and cities would reduce the carbon footprint of data centers [17]. Another possibility is to build data centers in eco-friendly locations (cold regions), thereby partially or completely eliminating the requirements of cooling systems [18]–[20]. However, with the increasing demand and stringent federal constraints on the privacy of data, which requires it to be stored in the home country of the

institution managing the data center, setting up data centers in remote/distant locations such as, Iceland, or even Antarctica, for the entirety of world population, might not be feasible. The second approach to overcome the energy inefficiency of the data centers is to intrinsically develop materials, devices, circuits and systems which are intrinsically energy-efficient. Several researchers across the globe are constantly innovating novel design architectures in this aspect. Such an approach can help solve the root cause of the problem and drastically reduce the power consumption of the data centers, which in turn will reduce the impact on climate change. One of the major constituents of a data center is the memory, which stores the data. Accessing data to-and-fro, the memory consumes significant component of the server energy. Therefore, in the following section, we discuss the importance of exploring emerging memories for future generation of electronic systems.

#### **1.2 Emerging Memories to the Rescue**

With technology scaling the traditional CMOS memories (SRAM/DRAM) exhibit a fundamental limitation for high performance, energy-efficient computing as detailed in the previous section. To overcome this drawback, various emerging non-volatile memory (NVM) technologies have been proposed to replace/complement SRAMs and/or DRAMs because of their appealing advantages such as high density, zero standby power, fast access speed, non-volatility, etc., [21]. They showcase the potential to efficiently overcome the drawbacks of the traditional memory hierarchy design which makes them important technology enablers for high-performance and intelligent hardware systems in the near future [22], [23].

Both prototypical and emerging non-volatile memories are based on novel materials and mechanisms which are drastically different from the traditional CMOS counterparts [24]. In the following, we briefly describe the advantages and drawbacks of some of the widely explored emerging memories:

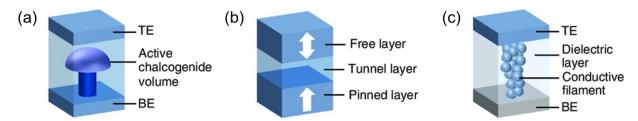

Phase Change Memories (PCMs) are based on reversible transition between the amorphous phase (high resistance) and the crystalline phase (low resistance) of chalcogenides (Fig. 1.4(a)) [21]. PCMs use special alloys, including Germanium Antimony Tellurium (GST), which have innovative characteristics that enable the non-volatile storage of their material phase by manipulating the heat inside the material. Micron's X100 NVMe SSD [25] and Intel's Optane

Fig. 1.4 (a) Phase Change Memory cell (b) Magnetic Tunnel Junction used in STT-MRAMs and (c) Resistive RAM cell. Figure adapted from [50].

technology [26] are few examples of well-established and mass-produced products using PCM. They demonstrate desirable characteristics such as longer retention and improved endurance compared to NAND Flash and also showcase functionality at scaled dimensions. However, the large latency of transition between the two phases (~100ns) and their high write power consumption hinder their direct implementation in circuit design [27]. Moreover, the ability of Flash to store and detect multiple bits per cell still gives flash a memory capacity advantage over PCMs. Although, multi-level storage is a possibility in PCMs, it is yet to be demonstrated in the industry products.

- Spin-Transfer Torque Magnetic RAM (STT-MRAM) is based on a magnetic tunnel junction (MTJ) cell with the most popular architecture composed of one transistor and one MTJ-based resistor (1T-1R; Fig. 1.4(b)) [23]. The resistance of the MTJ depends on the relative magnetization of the free layer (FL) with respect to the pinned layer (PL). They showcase faster read/write latencies (~10ns) and very high endurance (~10<sup>15</sup>) when compared to PCMs, and also smaller device footprint for high integration densities, close to that of DRAMs [21]. Samsung's STT-MRAM in 28nm FDSOI platform [28] and Intel's FinFET based MRAM technology [29] are some industrial efforts on the implementation of spintronic memory. However, the major disadvantage appears to be the high write current which increases the power consumption [21]. Moreover, the resistance-based distinguishability between the two logic states is low when compared to other emerging technologies (~orders of magnitude), leading to challenges associated with data sensing [30]–[32].

- *Resistive RAMs (RRAMs)* are another class of NVM technologies built on the resistance changing mechanisms. An example of RRAM is conductive bridge RRAM where the switching is generally attributed to the formation and rupture of conductive filaments in insulating oxides (Fig. 1.4(c)) [33]. It involves a simple 3-layer memory cell: metallic top

Fig. 1.5 (a) Polarization vs voltage hysteresis loop of FE illustrating the bi-stable states (b) FE capacitor structure used in FeRAMs and (c) FEFET device structure with FE integrated in the gate stack if a transistor. Figure adapted from [50].

electrode, resistive switching medium and metallic/non-metallic bottom electrode. Both unipolar and bi-polar variants of RRAM have been explored in the past. 1T-1R array architectures have also been built and explored to demonstrate CMOS compatible, high density memory arrays. The P-series from Crossbar Inc. [34], TSMC's 22nm ReRAM technology [35] and Fujitsu's world's largest density and mass produced, 8Mb ReRAM product- MB85AS8MT [36] are some of the leading industrial endeavor on this technology. However, tradeoffs exist among key RRAM parameters, e.g., speed-retention, power-speed, endurance, retention, etc. A major challenge of RRAM is reliability and variability [37]. The switching process is not controlled microscopically and is intrinsically stochastic, which is reflected in the large variation of device resistance and switching voltage from cycle to cycle and from device to device [21]. Also, the memory cells might require large forming voltage which might not be supported by scaled access transistors.

• *Ferroelectric RAMs (FERAMs)* are ferroelectric (FE) capacitor-based memories which have been proposed and industrially implemented using the unique property of FE's polarization retention in the absence of an external electric field Fig. 1.5(a) [38]. The memory follows a 1T-1C architecture, where the binary states are encoded in the polarization state of the ferroelectric as shown in Fig. 1.5 (b). They offer high endurance along with high integration densities close to DRAMs. Texas Instrument's FRAM microcontrollers [39] and Cypress's ExcelonTM FRAM [40] are examples of state-of-the-art efforts to leverage the FE properties for memory applications. However, their read operation is destructive and requires a write back operation, leading to large energy overheads [41]. Also, they employ voltage-based sensing, whose speed is limited by the bit line/ plate line capacitance and the low capacitance distinguishability between their bi-stable states [31]

• *Ferroelectric Transistors (FEFETs)* are field-effect transistor that can serve as a form of nonvolatile memory (Fig. 1.5(c)) [42], [43]. The device includes a FE layer being integrated in the gate stack of a transistor. The resistance state of the device is defined based on the polarization stored in the FE, which can be sensed by applying a drain-to-source voltage. Due to the polarization retention in the absence of electric field, even the resistance state of the transistor is retained. Such a device offers separation of read and write paths unlike many of the above mentioned emerging NVMs, which relaxes several design constraints. They offer a more robust sensing compared to FERAMs [31] and come with excellent CMOS compatibility and scalability (particularly those based on hafnium zirconium oxide of HZO) [44]. However, gate leakage in certain device architectures and interface variability can severely degrade the device and memory functionalities [45]. Moreover, large scale realization of this technology in memory products is yet to be achieved.