# EVALUATION OF STOCHASTIC MAGNETIC TUNNEL JUNCTIONS AS BUILDING BLOCKS FOR PROBABILISTIC COMPUTING

by

Orchi Hassan

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

Electrical and Computer Engineering West Lafayette, Indiana December 2020

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Surpiyo Datta, Chair

School of Electrical and Computer Engineering

Dr. Joerg Appenzeller School of Electrical and Computer Engineering

## Dr. Zhihong Chen

School of Electrical and Computer Engineering

## Dr. Ernesto E. Marinero

School of Materials Engineering

### Approved by:

Dr. Dimitrios Peroulis

This thesis is dedicated to *my family*.

## ACKNOWLEDGMENTS

Looking back, I am happy to say this has been a rewarding journey of self-growth. I would like to take this opportunity to acknowledge the people who had guided, inspired, and supported me throughout this journey.

It has been an honor and privilege to work with Professor Supriyo Datta, whose guidance and research philosophy have not only shaped this work but have also shaped me as a researcher and a person in the process. Being in touch with an inspiring educator and original-thinker like Professor Datta has been an invaluable experience. Above all, he has taught me the importance of diligence and perseverance and the art of elucidating complex concepts. His incredible patience, understanding, and kindness have been nothing short of a blessing throughout this time.

I also had the good fortune to be guided by a team of expert experimentalists who made up my thesis committee. I would like to thank Professor Joerg Appenzeller and Professor Zhihong Chen for shaping my thoughts on the realities of experimental realizations. They generously gave their time and offered insightful feedback toward improving my work. I would like to thank Professor Ernesto E. Marinero for building my knowledge on magnetism.

I gratefully acknowledge Dr. Jonathan Z. Sun's (IBM) contributions to understanding the fascinating physics of low-barrier magnets. Discussions with him gave life to some of the key contents of this thesis. I would also like to thank Professor Muhammad Ashraful Alam, for guiding me in my early days at Purdue and inspiring me to constantly learn from every aspect of life.

I am thankful to my brilliant set of colleagues: Kerem Y. Camsari, Shehrin Sayed, Rafatul Faria, Ahmed Zeeshan Pervaiz, Brian M. Sutton, Jan Kaiser, Shuvro Chowdhury, Lakshmi Anirudh Ghastasala, Risi Jaiswal, and others for the support, advice, collaborations, and most importantly the stimulating group discussions over the years. I want to especially thank Kerem for being a mentor in every sense of the word.

I am *ever grateful* to my incredible friends at Purdue, who have been a major source of support in everyday life and hope we remain *ever true*. Despite living by myself, I never felt

lonely here. Purdue was home, thanks to you guys. Finally, I am grateful to my family for their unconditional love, support, and encouragement. I am forever indebted to my parents for giving me the opportunities and experiences that have made me who I am today. I am thankful to my aunt, who has done everything she can to make my life easier in the US. One of the hardest parts of grad school was living apart from my sister and my husband. The two 'Missourians' were my greatest confidants, critics, and also my biggest cheerleaders throughout. I dedicate this milestone to all of them, who believed in me and made this journey possible.

## TABLE OF CONTENTS

| LI | ST O | F FIGU  | JRES                                            | 9  |

|----|------|---------|-------------------------------------------------|----|

| Ał | BRE  | VIATIO  | ONS                                             | 17 |

| AI | BSTR | ACT .   |                                                 | 18 |

| 1  | INTI | RODUC   | CTION                                           | 19 |

|    | 1.1  | Probal  | bilistic Spin Logic                             | 21 |

|    | 1.2  | Realiza | ation of Probabilistic Hardware                 | 23 |

|    | 1.3  | Organi  | ization of Thesis                               | 25 |

| 2  | LOW  | / BARI  | RIER MAGNET DESIGN                              |    |

|    | FOR  | HARD    | OWARE PROBABILISTIC BITS                        | 28 |

|    | 2.1  | Hardw   | vare p-bit realizations                         | 28 |

|    | 2.2  | Low B   | Parrier Magnet ( $\Delta \leq k_B T$ ) Dynamics | 30 |

|    |      | 2.2.1   | Correlation Time                                | 30 |

|    |      | 2.2.2   | Biasing Current                                 | 33 |

|    | 2.3  | Perform | mance Evaluation of p-bits                      | 34 |

|    |      | 2.3.1   | Steady-State Response                           | 35 |

|    |      | 2.3.2   | Time Response                                   | 36 |

|    |      | 2.3.3   | Power Consumption                               | 37 |

|    | 2.4  | Summ    | ary                                             | 39 |

| 3 | EVA | ALUATION OF PROBABILISTIC BITS FOR                       |                   |

|---|-----|----------------------------------------------------------|-------------------|

|   | ACC | CELERATING ISING MACHINES                                | 0                 |

|   | 3.1 | General Approach to Design of BSN 42                     | 2                 |

|   |     | 3.1.1 Types of fluctuating resistances                   | 3                 |

|   |     | 3.1.2 Performing the BSN function                        | 5                 |

|   |     | 3.1.3 Parameter Dependence and Design Choices            | 6                 |

|   | 3.2 | Realization of fluctuating resistances with sMTJs        | 0                 |

|   | 3.3 | Performance Evaluation of sMTJ based BSN                 | 4                 |

|   |     | 3.3.1 Device-Level Performance Evaluation                | 4                 |

|   |     | 3.3.2 Hardware Projections:                              | 7                 |

|   | 3.4 | Summary                                                  | 9                 |

| 4 | REA | ALIZATION OF WEIGHTED p-BIT                              | 0                 |

|   | 4.1 | Weighted p-bit Building Block                            | 0                 |

|   | 4.2 | Invertible full adder                                    | 4                 |

|   | 4.3 | 3SUM Problem                                             | 6                 |

|   | 4.4 | Subset-sum Problem (SSP) 68                              | 8                 |

|   | 4.5 | Summary                                                  | 0                 |

| 5 | MAG | GNETOELECTRIC MEMORY DEVICE BASED ON PSEUDO-MAGNETIZATIO | <mark>N</mark> 71 |

|   | 5.1 | Equivalent Circuit Model for Magnetoelectric Effect      | 1                 |

|   | 5.2 | Pseudomagnetization - New Order Parameter                | 5                 |

|              | 5.3   | Magnetoelectric Memory Cell                      | 78  |

|--------------|-------|--------------------------------------------------|-----|

|              | 5.4   | Extraction of $v_m$ from FMR Results             | 80  |

|              | 5.5   | Summary                                          | 82  |

| 6            | SUM   | MARY                                             | 83  |

|              | 6.1   | Realization of Naturally Stochastic Hardware     | 83  |

|              | 6.2   | Physics of Low-barrier Magnets                   | 84  |

|              | 6.3   | Benchmarking Metrics for Probabilistic Computing | 85  |

| RI           | EFER  | ENCES                                            | 87  |

| A            | DER   | IVATION OF PINNING FIELD OF LBM                  | 102 |

|              | A.1   | Perpendicular Magnetic Anisotropy (PMA)          | 102 |

|              | A.2   | In-plane Magnetic Anisotropy (IMA)               | 103 |

| В            | P-BI  | T DESIGN CRITERIA FROM BEHAVIORAL MODEL          | 104 |

| $\mathbf{C}$ | COE   | ES                                               | 106 |

| ΡĮ           | JBLIC | CATIONS                                          | 107 |

| VI           | TA    |                                                  | 108 |

## LIST OF FIGURES

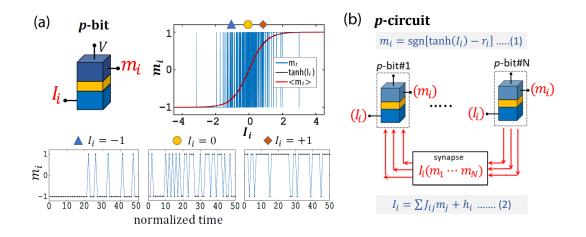

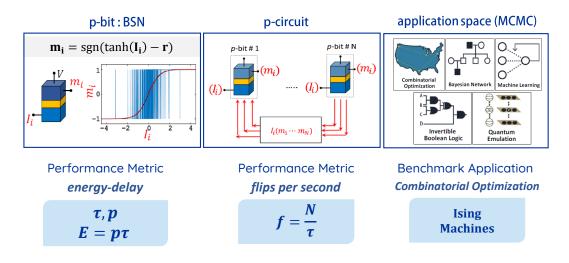

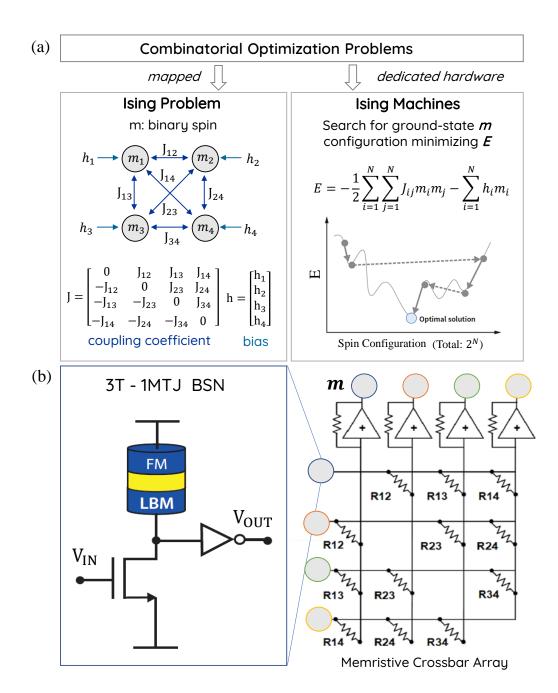

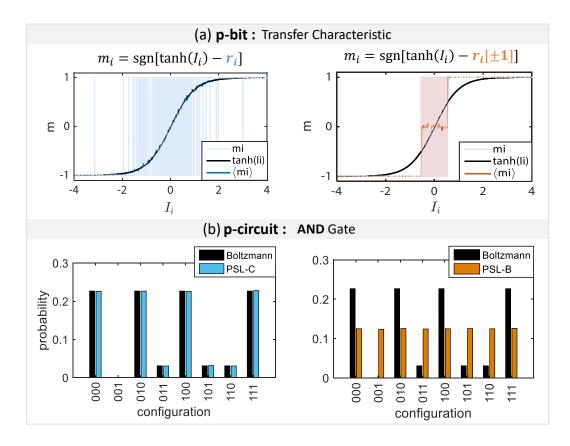

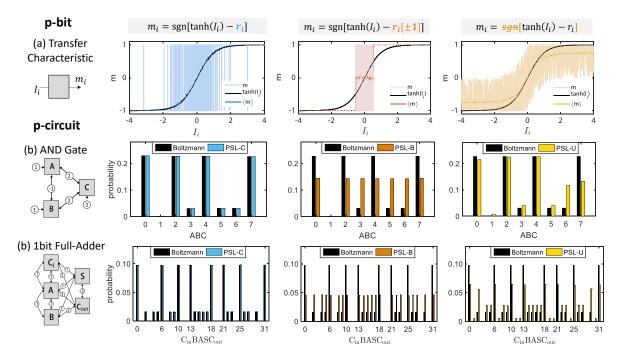

| 1.1 | <b>PSL framework:</b> (a) <i>p</i> -bit: The p-bit is a classical quantity that fluctuate rapidly between $+1$ and $-1$ and its fluctuations can be tuned through an input bias $I_i$ . (b) <i>p</i> -circuit: multiple p-bits can be connected through synaptic connections to form p-circuits to perform useful functions.                                                                                                                                                                                                                                                                                                                                                                                                                | 22 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | <b>Basic Design Principle:</b> The random thermal fluctuations in low barrier magnet's magnetization can be utilized to realize a stochastic resistor (SR) through the tunnel magnetoresistance (TMR) effect in an MTJ structure. The stochastic MTJ (s-MTJ) acts as the source of randomness $(r_i)$ in hardware realizations of p-bits.                                                                                                                                                                                                                                                                                                                                                                                                   | 23 |

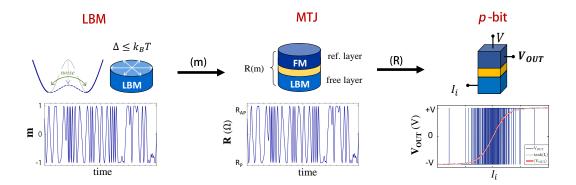

| 1.3 | <b>p-bit realizations with stochastic MTJ:</b> In each design the LBM MTJs act like a stochastic fluctuating resistance. The fluctuations are tuned to behave like a p-bit. In (a) Design 1, the tunability is achieved through spin current manipulation of magnetic state. The structure and operation principle is similar to the spin-orbit-torque (SOT) controlled MRAM. In (b) Design 2, the structure looks like a spin-transfer torque (STT) MRAM, but it achieves tunability mostly through the NMOS transistor. (c) shows the realization of a compact building block - the weighted p-bit (wpbit) using design (b) coupled to a capacitive voltage adder to perform the weight logic. We demonstrate fully hardware realization. | 24 |

| 1.4 | <b>Evaluation of PSL framework:</b> We define a set of performance metrics to benchmark the performance of PSL hardware. We evaluate the p-bit performance in terms of the average time and energy it takes to flip to a new random state. We emphasise the evaluation of hardware performance in terms of a problem independent metric - flips per second. It has been shown that PSL can be realized as a hardware accelerator for a wide spectrum of applications, in this thesis we benchmark our hardware performance against the digital implementations of Ising Machines.                                                                                                                                                           | 25 |

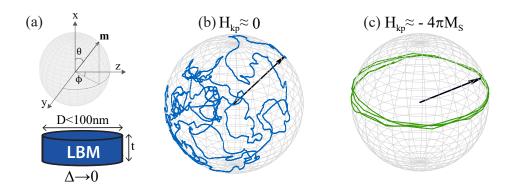

| 2.1 | Fluctuation Dynamics of LBM: (a) Schematic illustration of circular<br>LBM with saturation magnetization $M_s$ and volume $\Omega = \pi (D/2)^2 t$ and the<br>magnetization $\mathbf{m} = \mathbf{M}/M_s = (m_x, m_y, m_z) \equiv (\cos \theta, \sin \theta \sin \phi, \sin \theta \cos \phi)$ .<br>SPICE simulation shows $m(t)$ dynamics on Bloch sphere of a low barrier circu-<br>lar magnet with ( $\Delta \approx 0$ ) for magnet with (b) $H_{kp} \approx 0$ and (c) $H_{kp} \approx -4\pi M_s \approx$<br>$-13.8$ kOe, where $H_{kp} = 2K_s/t - 4\pi M_s$ is the perpendicular anisotropy along<br>x-axis and the in-plane anisotropy $H_{ki} \approx 0$ due to circular shape.                                                     | 29 |

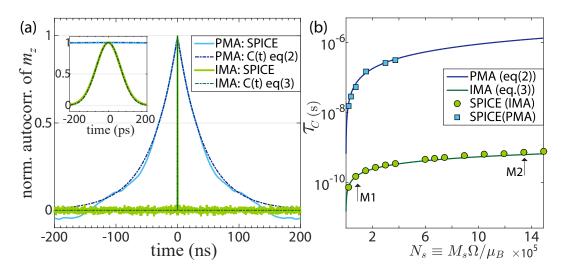

| 2.2 | Correlation Time of PMA and IMA magnets (a) The normalized auto-<br>correlation of magnetic fluctuations taken in the z direction, (b) Comparison<br>of $\tau_c$ as a function of number of spins $N_s \equiv M_s \Omega/\mu_B$ where $M_s = 1100$ emu/cc<br>and the volume $\Omega$ is varied. Damping coefficient $\alpha$ is assumed to be 0.01:<br>Results from numerical simulations agree well with the equations cited in the                                                                                                                            |          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

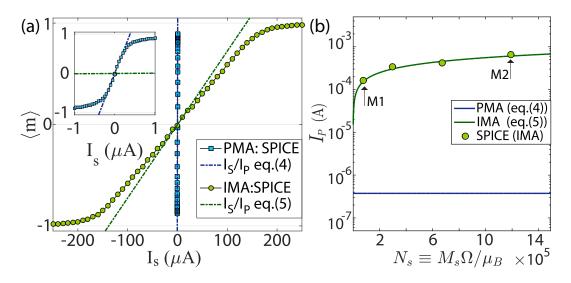

| 2.3 | <b>Pittning current of PMA and IMA magnets</b> (a) PMA and IMA magnet's long time averaged magnetization $\langle m \rangle$ as a function of applied spin current $I_S$ , (b) Comparison of PMA/IMA $I_P$ as a function of number of spins $N_s \equiv M_s \Omega/\mu_B$ where $M_s = 1100$ emu/cc and the volume $\Omega$ is varied. Damping coefficient $\alpha$ is assumed to be 0.01: Results from numerical simulations agree well with the equations cited in the text.                                                                                  | 31<br>32 |

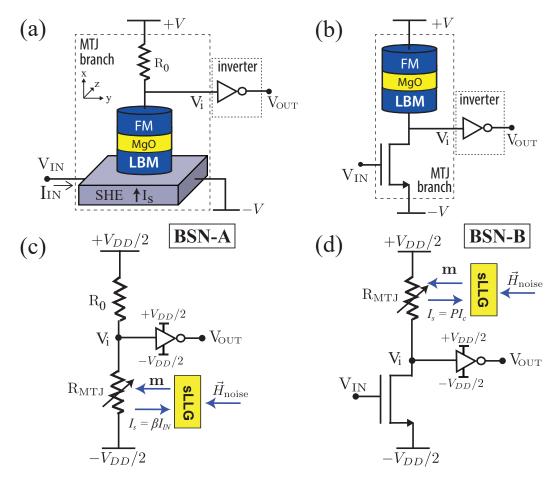

| 2.4 | Two BSN designs using stochastic MTJ with fluctuating resistance:<br>(a) BSN-A uses an input spin current to pin the fluctuating resistance [31].<br>Structurally it looks similar to spin-orbit torque magnetoresistive random<br>access memory (SOT-MRAM). (b) BSN-B looks similar to spin transfer<br>torque MRAM (STT-MRAM) but it makes no use of spin torque. The input<br>voltage controls the resistance of a field effect transistor (FET) which is in<br>series with the MTJ [77]. (c) and (d) show the circuit models used for SPICE<br>simulations. | 34       |

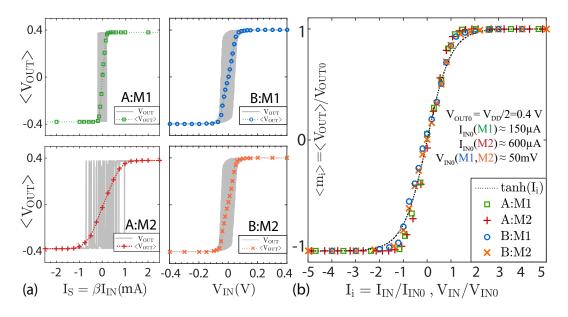

| 2.5 | <b>Steady-state Response:</b> (a) Plot of $\langle V_{OUT} \rangle$ (averaged over a time window $\gg \tau_c$ ) vs $V_{IN}$ for designs A, B using magnets M1, M2. The grey lines indicate $V_{OUT}$ without time averaging. (b) All four plots in (a) collapse onto a single curve using appropriate scaling parameters $V_{OUT0}$ , $I_{IN0}$ , $V_{IN0}$ . The resulting curve approximately follows the time averaged $\langle m_i \rangle$ of eq. 2.1.                                                                                                     | 36       |

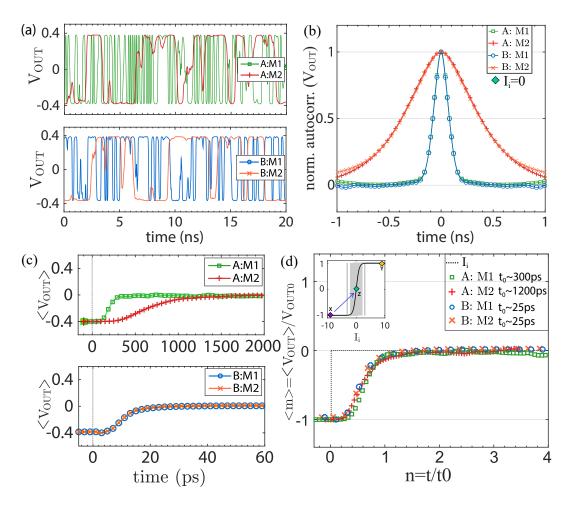

| 2.6 | Two relevant time-scales for BSN Operation: (a), (b) show correlation<br>time and (c),(d) show response time. (a) Output voltage fluctuations with<br>$I_i = 0$ for designs A, B using magnets M1, M2. (b) Corresponding normalized<br>autocorrelation functions. (c) Response to a step function $I_i : -10 \rightarrow 0$ at<br>t=0 averaged over 1000 ensembles for all four cases.(d) All four curves in (c)<br>collapse onto a single curve using appropriate scaling parameter $t_0$ .                                                                    | 37       |

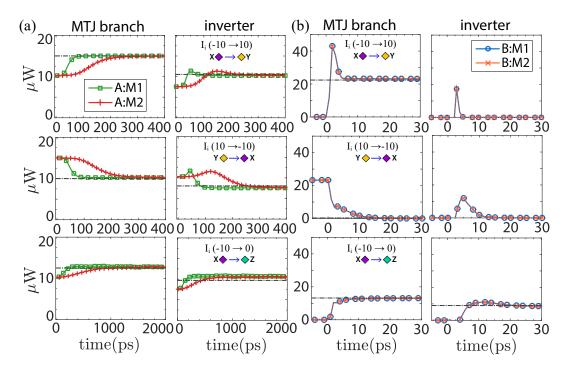

| 2.7 | <b>Power Consumption</b> for (a) BSN-A and (b) BSN-B when the input is stepped at t=0 as indicated                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 38       |

| 3.1 | 1MTJ-3T compact BSN hardware which utilizes the natural physics of low-<br>barrier nanomagnets holds the promise to accelerate the simulated annealing<br>processors.                                                                                                                                                                                                                                                                                                                                                                                           | 41       |

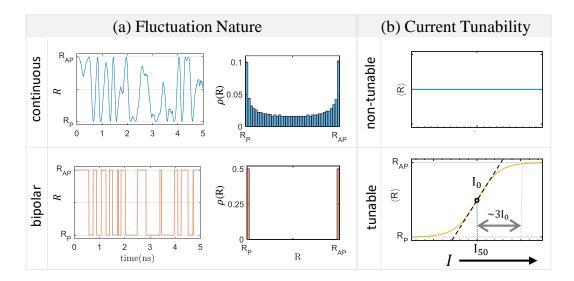

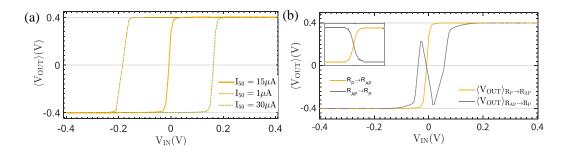

3.2 **Categorizing Resistances:** (a) Fluctuating nature: they can be continuous or bipolar. The time dynamics and distribution are shown for each category. (b) Current-Tunability: The fluctuations could be unaffected by I or it could be a function of I as indicated by their transfer characteristics.  $I_{50}$  is the current at the 50:50 point where the resistance spends equal time in  $R_P$  and  $R_{AP}$  states.  $I_0$  is the biasing current defined as the slope of the (R vs I) curve at 50:50 point. The pinning current is typically  $\sim 3 - 5 I_0$ .

44

45

46

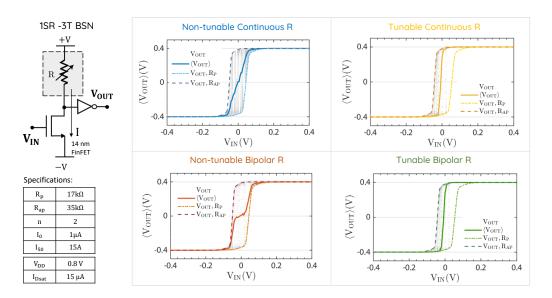

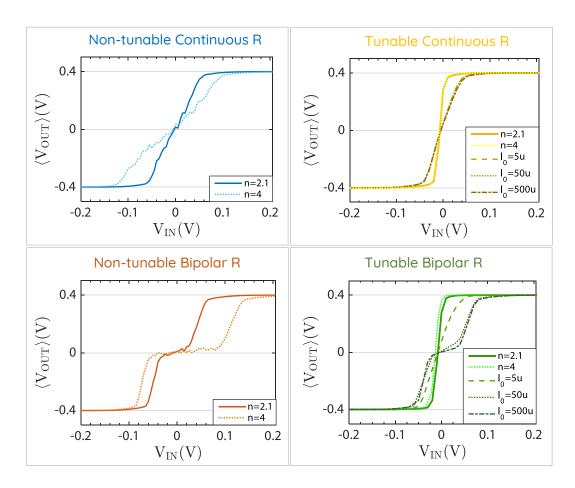

- 3.3 **Transfer Characteristics :** The BSN circuit is realized by coupling the fluctuating resistor which is the physical realization of the random variable  $r_i$  in the BSN equation to an NMOS which provides the tunability, and then to an inverter which thresholds the output. The four types of resistances are coupled to a 14nm FinFET and the resistance parameters (based on experimental demonstrations of MTJs [110]) are chosen to match the transistor characteristics. All resistance types except for the bipolar non-tunable were able to achieve BSN operation following eq. 3.2. To function as a BSN the bipolar resistances need some means of tuning their probability distribution.

- 3.4 Non-tunable Continuous vs Bipolar Resistance: (a) Transfer Characteristics shows that while the continuous resistor results in a sigmoidal output, the bipolar gives a stair-case like function. (b) The bipolar R is unable to follow the Boltzmann distribution of the invertible AND gate (description in ref.[31]). All states remain equally probable.

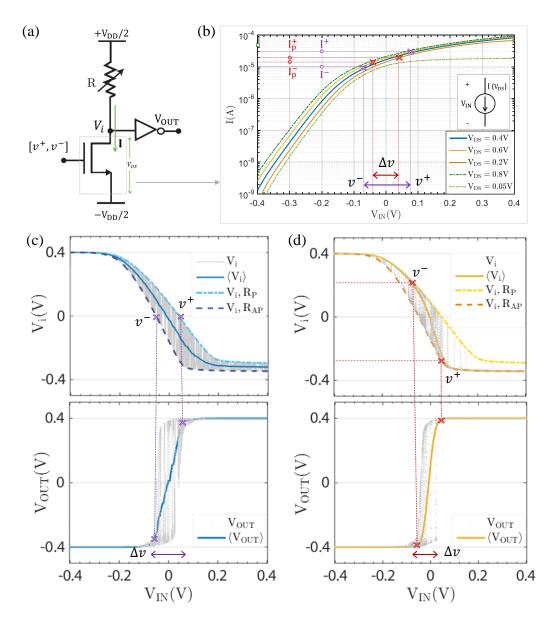

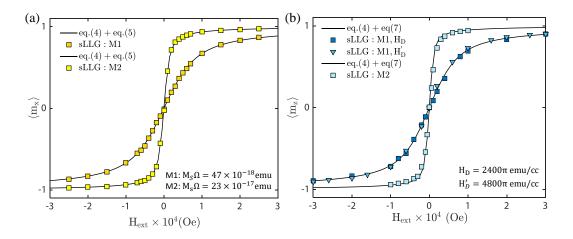

| 3.8  | Low-barrier magnet fluctuation dynamics: We use the benchmarked stochastic LLG module to simulate LBM dynamics. Each simulation is carried out with a time-step at least $\times 100$ smaller for a time-duration $\times 1000$ than characteristic timescales to avoid any simulation time dependencies, the exact parameters are indicated. $\Delta < k_{\rm B}T$ magnets have more continuous fluctuations with (b) having a more uniform distribution than (a) while slightly higher barrier magnets have a more telegraphic fluctuation. In both cases, the presence of high demagnetization fields cause faster fluctuations in IMA magnets. | 51 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

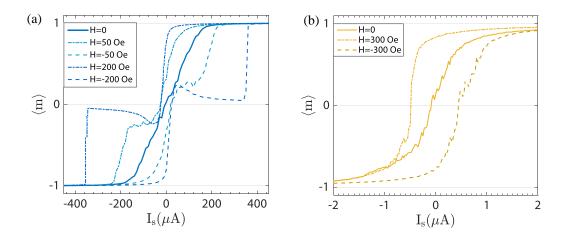

| 3.9  | <b>Current Response of LBM:</b> LBM response to spin-current with and with-<br>out external-fields for (a) circular IMA magnet ( $H_{ki} \sim 0, H_{kp} \sim -H_D$ ) and (b)<br>isotropic anisotropy magnet ( $H_{kp} \sim 0$ ). Each point on the curve is a long-time<br>( $T = 1\mu s, \Delta t = 1ps$ ) average magnetization from our benchmarked sLLG<br>module. The critical field for IMA magnet was ~ 130Oe and for isotropic<br>magnet ~ 200Oe.                                                                                                                                                                                          | 53 |

| 3.10 | <b>Characterization Table:</b> MTJ Free layer and its corresponding R type along with corresponding characteristic parameters and their analytical expression. The numbers in bracket indicates an approximate range of values for each parameter. The proportionality constant for correlation time of magnets with $\Delta > k_BT$ is $\tau_0 \sim 0.1 - 1$ ns, exact equation can be found in [82]                                                                                                                                                                                                                                              | 54 |

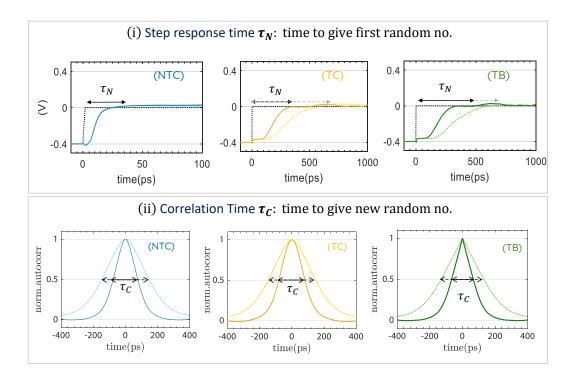

| 3.11 | <b>Timescale of Operation</b> for each resistor type with two fluctuation rates $\tau_{\rm C} \sim [160 \text{ ps}, 320 \text{ ps}]$ . The resistances are engineered to have similar characteristic timescales but different fluctuation behavior (tunable, non-tunable and continuous and bipolar fluctuation) for comparison purposes.                                                                                                                                                                                                                                                                                                          | 55 |

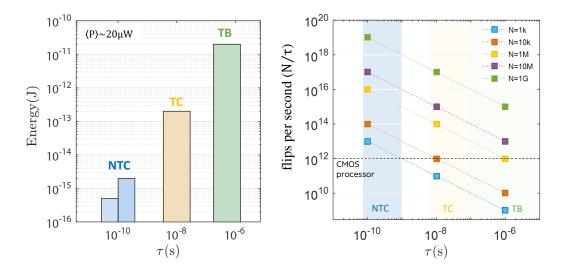

| 3.12 | (a) Energy-Delay of each type of MTJ based BSN assuming an average power of 20 $\mu$ W and timescales in fig. 3.9. (b) Plots the fps for different no. of neurons for each type of MTJs. For the projections only BSN performance numbers are used, synapse would add to the power and thus energy per flip number.                                                                                                                                                                                                                                                                                                                                | 56 |

| 3.13 | flips per second (fps) is a substrate and algorithm independent perfor-<br>mance metric for simulated annealing processors much like the flops per sec-<br>ond metric used for general purpose computers. It is a measure of how many<br>flips, and hence spin configurations the system can cycle through in a second.<br>fps can be derived from the reported performance metrics of the processors<br>following ref. [48]. The reported and derived quantities as indicated. Current<br>CMOS based annealing processors perform at $\sim 10^{12}$ fps. We project that<br>MTJ based hardware can increase by a few orders of magnitude.         | 58 |

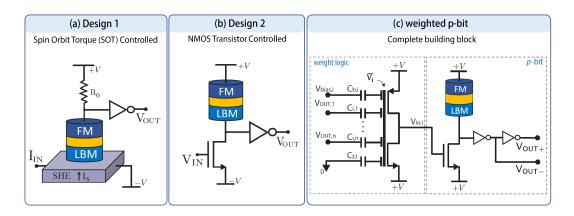

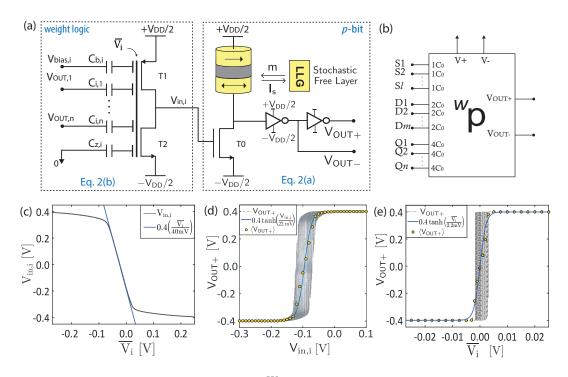

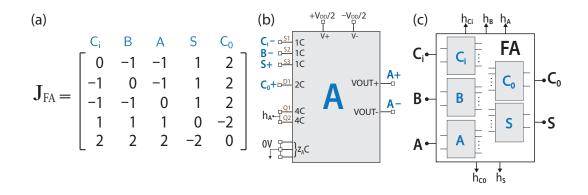

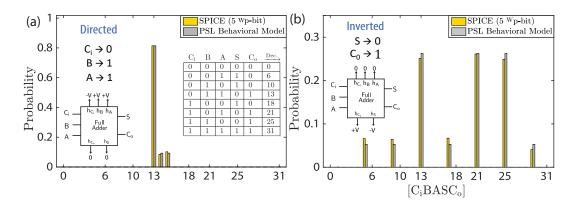

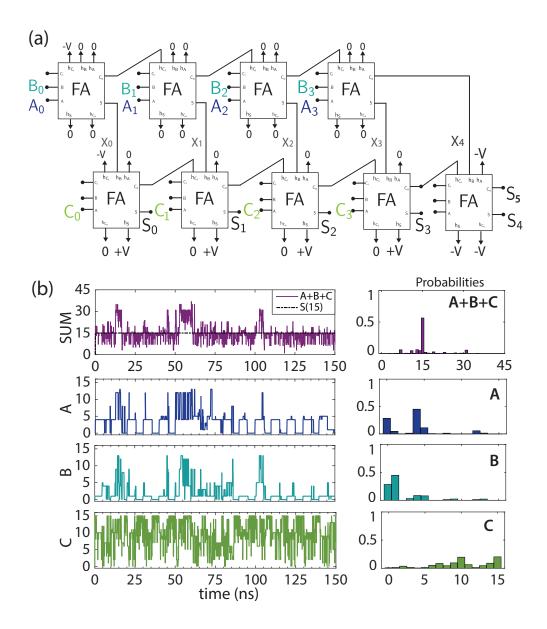

(a) Weighted p-bit ( $^{W}p$ -bit) has two components. The first is the p-bit 4.1implemented through an embedded s-MTJ with two inverters added to give positive and negative outputs. The second is the capacitive voltage adder with an inverter structure on the left similar to floating gate MOS transistors. (b)Shows the block diagram of  $^{W}p$ -bit. (c) Shows how an inverter helps amplify the input  $(V_i)$  of the capacitive network to give  $V_{in,i}$  at the gate of the p-bit's NMOS transistor T0. (d) Shows the relation of the input gate voltage of the NMOS  $(V_{in,i})$  to output  $(V_{OUT}^+)$ . (e) Shows the transfer characteristics of the <sup>W</sup>p-bit as a whole. The inputs in each case is swept from -0.4V to +0.4V in 1  $\mu$ s. The vellow dots are time averaged values at each point over 300 ns and the solid blue lines are numerical fits. 61 **Invertible Full Adder with**  ${}^{W}p$ **-bit**: (a)[J] matrix for implementing a Full 4.2Adder. (b) Explicitly shows the hardware connections made to one of the inputs (A) from the other p-bits where 1C, 2C, and 4C represent capacitors in units of  $C = C_0 = 100 a F$ . (c) Shows the subcircuit representation of the Full Adder with its input/output terminals.  $C_i, B, A$  input and  $S, C_o$  output read terminals and separate corresponding clamping terminals  $h_{C_i}, h_B, h_A, h_S, h_{C_0}$ . We used 8C for the clamping terminals to ensure input / outputs follow what is dictated by the external signals. 64Full SPICE implementation of an Invertible Full Adder(5 <sup>W</sup>p-bit): 4.3 The 5  ${}^{W}\!p$ -bit invertible Full Adder circuit is simulated in (a) Directed and (b) Inverted modes. The clamping values are indicated. All biasing terminals that are not clamped to 1 or 0 are grounded. The histogram of  $[C_iBASC_0]$ is obtained after thresholding voltages  $((V < 0) \equiv -1, (V > 0) \equiv +1)$ . The SPICE model is run for  $1\mu$ s and compared with the PSL equations where each p-bit is updated in random but sequential order [31]. In this example  $I_0 \simeq 1$  is chosen to emphasize how the models are in good agreement even in the magnitudes of the minor peaks of the histogram. 65SPICE simulation of a 4bit 3-SUM Problem (9  $\times$  5 = 45 <sup>W</sup><sub>p</sub>-bit 4.4**network**): (a) The circuit is constructed by interconnecting two rows of invertible Full-Adders (FA) to construct a 3 number, 4-bit adder. The sum S is clamped to the desired value and A, B, C resolves themselves to create all the possible 3 number subsets out of all positive numbers 0 to  $2^4 - 1$  that satisfy A + B + C = S. (b) Shows the results when S is clamped to 15. A, B and C get correlated to satisfy the sum with different combinations. In this example, the inputs A, B, C are unconstrained and can take on any value between 0-15. 67

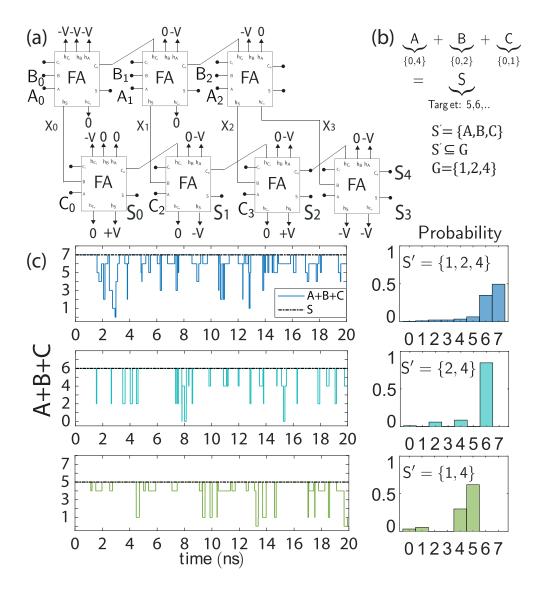

- 4.5 SPICE simulation of a 3 input, 3-bit Subset Sum Problem  $(7 \times 5)$ = 35 <sup>W</sup>p-bit network): (a) A 3-input 3-bit binary adder that adds three numbers A,B,C. Unlike the 3SUM, in this case inputs are constrained to a given value specified by the set G ={1,2,4} in this example. A target S is selected and the output of the adders are clamped to the target value as shown in (b). (c) Shows three different instances of a target where the inputs find a consistent combination (the correct subset of G) to satisfy the target. Histograms show that the highest probable state is the correct subset. An important difference from the 3SUM circuit is that the information flow is directed from the target (second layer of adders) to the first layer of adders.

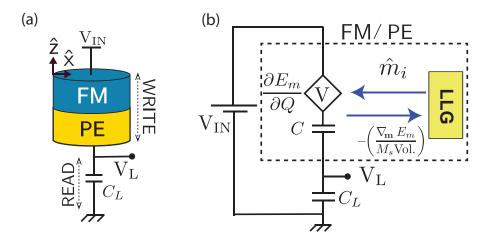

- 5.1 Equivalent circuit for magnetoelectric (ME) read and write operations (a) The charge on the piezoelectric (PE) capacitor changes the easy-axis of the ferromagnet (FM) and this causes a change in the output voltage V<sub>L</sub> through the inverse effect. (b) Equivalent circuit model obtained from (5.1). Write operation is through the effective field  $\vec{H}_{me} = -\nabla_{\mathbf{m}} E_m/(M_s \text{Vol.})$  that enters the stochastic Landau-Lifshitz-Gilbert (s-LLG) equation. Read operation is through the dependent voltage source V that is proportional to  $\partial E_m/\partial Q$ , where  $E_m$  is the magnetic energy.

69

73

74

**Experiment vs circuit model**: (a) The results of the self-consistent circuit 5.2model for the structure in (b) are in good agreement with the experimental results in [156].  $V_{\rm ME}$  is the mathematical difference of two measurements of  $V_R$ with and without the external magnetic field,  $V_{\rm ME} = V_R(H \neq 0) - V_R(H = 0)$ . (b) Experimental structure reported in [156] where the piezeoelectric (PE) is (011)-cut PMN-PT and the ferromagnet (FM) is N layers of TbCo<sub>2</sub>/FeCo. The back-voltage is  $V=v_M\mu$  where  $\mu=m_x^2-m_y^2$  and the magnetic energy is  $E_m = Q_{PE} v_M \mu$  where  $Q_{PE}$  is the charge on the capacitor  $C_{PE}$ . The following parameters are used: Coercivity for FM ( $H_K=200$  Oe), saturation magnetization  $M_s=1100 \text{ emu/cc}$ , FM thickness,  $t_{\rm FM}=200 \text{ nm}$ , PE thickness  $t_{\rm PE}=30$  $\mu m$ , Area=520 × 520 nm<sup>2</sup>, Magnetoelastic constant B = -7 MPa, a net PE constant,  $d = d_{31} - d_{32} = 2500 \text{ pC/N}$ , permittivity  $\epsilon = 4033 \epsilon_0$ , resistance  $R = 2 \text{ M}\Omega$ , back voltage  $v_M = B dt_{\rm FM}/2\epsilon$ . In the experiment, magneto-optic Kerr effect (M.O.K.E) is used to show the variation of magnetization, which is compared to the pseudo-magnetization in our simulation. Experimental panel is reproduced with permission of AIP Publishing LLC, from Reference 156.....

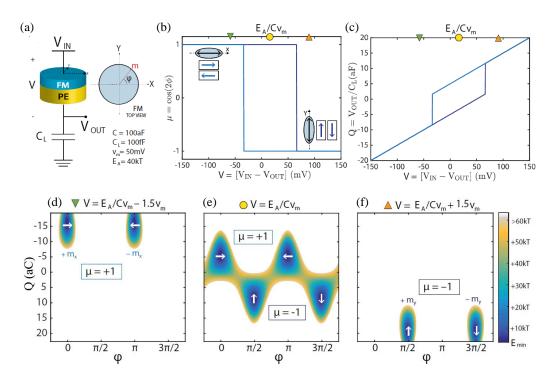

- 5.3 **Pseudomagnetization** (a) Basic electrical circuit for characterization of PE/FM structure. Information on the device is stored in the magnetic easy axis direction  $(\pm x \text{ or } \pm y)$  which we term pseudomagnetization,  $\mu$ . (b) Shows the change of  $\mu$  due to the applied voltage, V across the PE/FM structure and (c) shows the resulting charge versus voltage characteristics in the circuit which is similar to standard ferroelectrics. (d)-(f) shows the stable states at different voltages across the structure on a heatmap. Unlike conventional magnetic memory there are multiple states associated with each voltage indicating preferred easy axis. The states are separated by a large barrier, so which allows for non-volatile memory application.

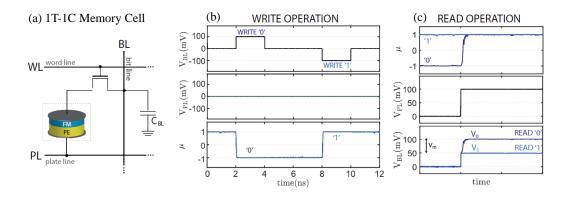

- 5.4 (a) Magnetoelectric 1T-1C memory cell. The READ/WRITE Operation of the cell mimics the scheme of FeRAM operation. (b) WRITE pulse is applied to the bit-line keeping plate line grounded. (c) READ pulse is applied to the PL and voltage at BL is detected. The read process is destructive as in FeRAM, but unlike DRAM is μ non-voltaile so does not require periodic refresh. . . . 79

76

80

81

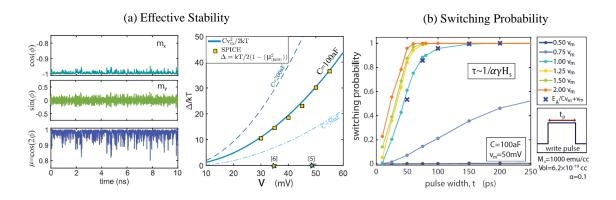

- 5.5 (a) The stability of pseudomagnetization states can be measured from equilibrium fluctuations. The effective stability ( $\Delta$ ) of  $\mu$  can be attributed to an effective stress anisotropy field ( $H_s$ ) it feels which depends on the back-voltage  $v_m$  and the capacitance value C. (b) Switching probability of pseudomagnetization is calculated from 1500 samples for different amplitudes and pulse widths. Sub-ns switching speeds ( $\tau$ ) can be attained due high stress fields ( $H_s = CV_{IN}v_m/M_sVol$ ) in nanomagnets.

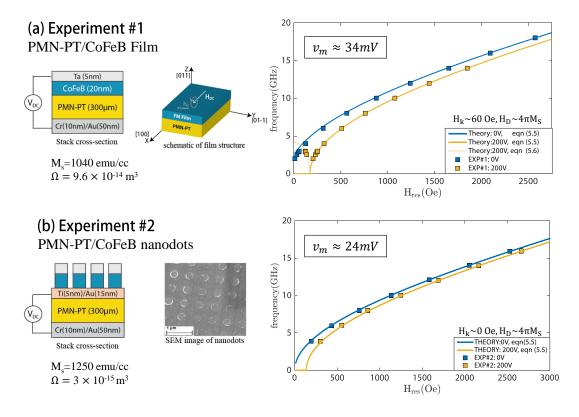

- 5.6 Characterizing FMR Measurements Ferromagnetic resonance (FMR) measurements performed on two samples (a) Film and (b) nanodot array show modification of magnetic anisotropy of CoFeB by applying voltage across the PMN-PT layer. The modified Kittle equations (eq. 5.5 and 5.6) including the voltage-induced stress term  $H_s$  are used to fit the measurements. The reported experimental parameters for the piezoelectric are relative permittivity  $\epsilon_r = 600$ , piezoelectric co-efficient d = 4500 pC/N, and for the magnet the magnetoelastic constant B = 4 MPa. For the film the theoretically expected ME back-voltage ( $v_m = Bdt_{FM}/2\epsilon$ ) of 34 mV fits the data while a slightly lower value of 34 mV fits the nanodots which has a Ti/Au layer inbetween the PE and FM layer.

- A.1 **Pinning Field of low-barrier magnets** The numerical evaluations of equations are compared to SPICE simulation for (a) Isotropic magnets and (b) circular IMA magnets which have  $\Delta \leq k_{\rm B}T$ . The pinning fields are shown to be a function of  $M_S\Omega$  only where  $M_{\rm S} = 600$  emu/cc and the volume of magnet  $\Omega$  is varied, The pinning field values for IMA magnets indicate that it is independent of the large demagnetization field, H<sub>D</sub>. The precise correspondence between the analytical formulas and the numerical simulation also constitutes as a benchmark to our finite temperature (stochastic) LLG formulation. . . 103

## ABBREVIATIONS

| BSN                 | binary stochastic neuron                            |

|---------------------|-----------------------------------------------------|

| $\mathbf{FM}$       | ferromagnet(ic)                                     |

| fps                 | flips per second                                    |

| GSHE                | giant spin hall effect                              |

| IMA                 | in-plane magnetic anisotropy                        |

| LBM                 | low barrier magnet                                  |

| LLG                 | Landau-Lifshitz-Gilbert (equation)                  |

| MCMC                | markov chain monte carlo                            |

| ME                  | magnetoelectric                                     |

| MRAM                | magnetic random access memory                       |

| MTJ                 | magnetic tunnel junction                            |

| p-bit               | probabilistic bit                                   |

| PE                  | piezoelectric                                       |

| PMA                 | perpendicular magnetic anisotropy                   |

| PSL                 | probabilistic spin logic                            |

| RNG                 | random number generator                             |

| SA                  | simulated annealing                                 |

| sLLG                | stochastic LLG                                      |

| s-MTJ               | stochastic magnetic tunnel junction                 |

| SOT                 | spin-orbit torque                                   |

| SPICE               | simulation program with integrated circuit emphasis |

| $\operatorname{SR}$ | stochastic resistance                               |

| STT                 | spin-transfer torque                                |

| TMR                 | tunnel magnetoresistance                            |

| TDNC                | true renders number generator                       |

${\rm TRNG} \quad {\rm true\ random\ number\ generator}$

## ABSTRACT

Probabilistic computing has been proposed as an attractive alternative for bridging the computational gap between the classical computers of today and the quantum computers of tomorrow. It offers to accelerate the solution to many combinatorial optimization and machine learning problems of interest today, motivating the development of dedicated hardware. Similar to the 'bit' of classical computing or 'q-bit' of quantum computing, probabilistic bit or 'p-bit' serve as a fundamental building-block for probabilistic hardware. p-bits are robust classical quantities, fluctuating rapidly between its two states, envisioned as three-terminal devices with a stochastic output controlled by its input. It is possible to implement fast and efficient hardware p-bits by modifying the present day magnetic random access memory (MRAM) technology. In this dissertation, we evaluate the design and performance of low-barrier magnet (LBM) based p-bit realizations.

LBMs can be realized from perpendicular magnets designed to be close to the in-plane transition or from circular in-plane magnets. Magnetic tunnel junctions (MTJs) built using these LBMs as free layers can be integrated with standard transistors to implement the three-terminal p-bit units. A crucial parameter that determines the response of these devices is the correlation-time of magnetization. We show that for magnets with low energy barriers  $(\Delta \leq k_B T)$  the circular disk magnets with in-plane magnetic anisotropy (IMA) can lead to correlation-times in *sub-ns* timescales; two orders of magnitude smaller compared to magnets having perpendicular magnetic anisotropy (PMA). We show that this striking difference is due to a novel precession-like fluctuation mechanism that is enabled by the large demagnetization field in mono-domain circular disk magnets. Our predictions on fast fluctuations in LBM magnets have recently received experimental confirmation as well.

We provide a detailed energy-delay performance evaluation of the stochastic MTJ (s-MTJ) based p-bit hardware. We analyze the hardware using benchmarked SPICE multiphysics modules and classify the necessary and sufficient conditions for designing them. We connect our device performance analysis to systems-level metrics by emphasizing problem and substrate independent figures-of-merit such as flips per second and dissipated energy per flip that can be used to classify probabilistic hardware.

### 1. INTRODUCTION

The future of computing beyond Moore's Law is in building heterogeneous computing platforms that can handle diverse workloads. This entails introducing new computing paradigms and architectures tailored for addressing specific applications [1] complementary to the general-purpose computing architecture. Conventional computing has been dominating the computing paradigm for decades fueled by the continuous improvements in computing performance following the observation made by Gordon Moore over 50 years ago [2]. This observation that the number of components (semiconductor transistors) in an integrated circuit doubles every two years, dubbed Moore's Law by Carver Mead [3], underpinned by Dennard scaling [4] had come to shape the modern-society itself. Even after the end of Dennard scaling in 2004, new device-physics and changes in computer architecture enabled conventional computing performance to continue to increase exponentially. However, as semiconductor device scaling reaches its physical limits the exponential growth rate is finally tapering. But on the other hand, thanks to the internet of things and our own digital footprint the amount of data available to analyze is increasing at unprecedented rates everyday [5]. As the demand to capitalize from this plethora of data increases, technological and economic forces are propelling the computing paradigm to shift from general purpose to specialized. The algorithmic success of neuro-inspired and quantum computing models in dealing with large data sets have now opened up exciting new possibilities, but demands computing performance even beyond exa-scale [6]. Moving to specialized architecture and dedicated hardware for such compute-expensive applications is likely to provide substantial performance advantage leading to significant breakthroughs [7].

A lot of progress are being made in this front. Machine Learning (ML) a decades old concept has now set to become a ubiquitous part of life [8] as its computational load is accelerated by specialized hardware like the highly parallel graphic processor units (GPUs)[9], [10]. Quantum computing, also a decades old concept has become a billion dollar industry [11] as big companies like Google, IBM, Intel, and Microsoft are taking on the grand challenge of developing commercial quantum computers demonstrating quantum supremacy [12]. Although significant progress has been made, the difficulty of scaling quantum bits for building large-scale, error-corrected quantum computer to carry out relevant calculations that a classical computer cannot is perhaps decades away from complete [13].

In recent years, probabilistic computing has emerged as an attractive alternative for bridging the computational gap between the classical computers of today and the quantum computers of tomorrow. Most real-problems that quantum computers are aiming to solve can be formulated as combinatorial optimization problems. A way to solve these computationally complex problems efficiently is to map them onto an Ising model [14], [15] and use its intrinsic convergence properties to search for the ground state of the system and reach the solution [16]. Companies like Hitachi, Fujitsu, Toshiba, NTT, D-Wave, and others have invested in building dedicated hardware accelerators based on the Ising Model broadly termed Ising Machines. The various approaches range from quantum computers based on quantum annealing (QA) or adiabatic quantum optimization (AQC) implemented with superconducting circuits [17], coherent Ising machines (CIMs) implemented with laser pulses [18], phase-change oscillators [19], or CMOS oscillators [20]–[23] to digital annealers based on simulated annealing (SA) [16] implemented with digital circuits [24]–[30]. Digital annealers are at the forefront of the race offering scalable, room-temperature mm sized chips. However, these deterministic digital hardware only emulates the probabilistic nature of the algorithms. Infact, the random number generators (RNGs) occupy a major portion of the annealing processors today [28]. A substantial performance advantage could be achieved if probabilistic algorithms ran directly on probabilistic hardware with naturally probabilistic constituents. The probabilistic spin logic (PSL) framework based on the concept of using probabilistic bits or 'p-bits', is an embodiment of this idea [31]-[33]. p-bits are classical quantities intermediate between the stable bits of digital electronics and the q-bits of quantum computing. In this work, we analyze the physical implementations of p-bits using naturally stochastic elements to serve as building-blocks for realization of compact, scalable, energy-efficient PSL hardware.

#### 1.1 Probabilistic Spin Logic

The idea of a probabilistic computer to prelude quantum computers can be found in the seminal keynote address by Richard Feynman on simulating physics with computers [34]. Feynman articulated that the only efficient means to simulate a phenomenon was with a system governed by its same fundamental constituents. A wide range of practical problems of great interest today, like machine learning and combinatorial optimization, essentially involve probabilities. So, an efficient way to solve these problems would be by using a probabilistic computer whose fundamental constituents are probabilistic bits.

In 2016, Behin-Aein et. al. [33] proposed the idea of interconnecting transistor like three terminal stochastic devices, subsequently dubbed the 'p-bit' by Camsari et. al. [31] to serve as a building block for probabilistic networks. Probabilistic spin logic (PSL) is the name given to the study of these networks of p-bits. The 'spin' in PSL is originally motivated by its strong ties to magnetic-devices and efficient realizations of hardware p-bits using low-barrier magnets which we document in this thesis.

A wide variety of problems encompassing two active but disjoint fields of research, stochastic machine learning [35], [36], and quantum computing [37]–[41] can be mapped onto the p-computer through proper design of the interconnections between the p-bits. Basically, what we propose is a naturally stochastic hardware that can implement probabilistic alogrithms that are based on Markov chain Monte Carlo (MCMC) efficiently.

A p-circuit solves a problem by naturally converging to the ground state of the system described by its energy:

$$E = I_0 \left( -\frac{1}{2} \sum_{i,j=1}^N J_{ij} m_i m_j - \sum_{i=1}^N h_i m_i \right)$$

(1.1)

where, m denotes the p-bit, J is the coupling co-efficient or interconnection strength between the p-bits, h is the external bias applied to a p-bit and  $I_0$  is a dimensionless quantity representative of the system's temperature. For machine learning applications  $I_0$  is typically kept constant, while for optimization problems involving simulated annealing  $I_0$  is varied.

Figure 1.1. PSL framework: (a) *p*-bit: The p-bit is a classical quantity that fluctuate rapidly between +1 and -1 and its fluctuations can be tuned through an input bias  $I_i$ . (b) *p*-circuit: multiple p-bits can be connected through synaptic connections to form p-circuits to perform useful functions.

The p-bits are essentially tunable random number generators (RNGs), analogous to the binary stochastic neurons (BSNs) [42] of stochastic neural networks and can be described mathematically by

$$m_{\rm i} = \rm{sgn}(tanh(I_{\rm i}) - r_{\rm i}) \tag{1.2}$$

where,  $r_i$  is a random number between  $\pm 1$  and  $I_i$  is the input to the p-bit. Here, we use bipolar variable  $m_i = \pm 1$  to represent the two states '1' and '0' of the system. The output fluctuation probability of the p-bits are controlled by their individual input  $I_i$  generated from the weighted sum of the states of other p-bits according to:

$$I_{\rm i} = I_0 \left( \frac{1}{2} \sum_{\rm j=1}^{\rm N} J_{\rm ij} m_{\rm j} + h_{\rm i} \right)$$

(1.3)

Eq. 1.2 and 1.3 together describes the PSL framework. Problems can be mapped onto PSL through appropriate J and h [15]. The same framework accompanied by a learning rule can also be used to calculate the J and h themselves [36], [43]. Infact, eq. 1.2 and 1.3 are widely used in many modern algorithms, but they are commonly implemented in software whose performance could be accelerated by building dedicated hardware. So, how do we build a scalable energy-efficient hardware for implementing PSL? Much work has gone into developing accelerators for performing the matrix multiplication and addition of eq. 1.3 which the PSL hardware can directly benefit from [44]–[47]. Our primary focus in this thesis is on the design of a hardware accelerator for implementing eq. 1.2, the p-bit.

### 1.2 Realization of Probabilistic Hardware

Any random signal generator whose randomness can be tuned with a third terminal could serve as a suitable physical realization of p-bit, but *what is the most efficient way to do it?* Completely digital implementations using conventional CMOS technology are possible [48]–[50], but getting true randomness from deterministic circuits require elaborate circuits with unfavorable size, power-consumption, and latency [19], [51]. Also, it beats our original motivation of leveraging from nature's innate stochasticity. In this thesis, we show that hardware p-bits can be efficiently and compactly realized using low-barrier magnets (LBMs) in structures similar to those in conventional magnetic random access memory (MRAM) technologies [52], [53].

Figure 1.2. Basic Design Principle: The random thermal fluctuations in low barrier magnet's magnetization can be utilized to realize a stochastic resistor (SR) through the tunnel magnetoresistance (TMR) effect in an MTJ structure. The stochastic MTJ (s-MTJ) acts as the source of randomness  $(r_i)$ in hardware realizations of p-bits.

The key element in the designs is the stochastic magnetic tunnel junction (s-MTJ) which has been shown to be well-suited for the physical implementation of random number generators [54]–[56]. LBMs whose magnetization fluctuates randomly under thermal perturbations can be built from perpendicular magnetic anisotropy (PMA) magnets designed to be close to the in-plane transition or from circular in-plane magnetic anisotropy (IMA) magnets [57]. MTJs utilizing these unstable LBMs as free layers present themselves as fluctuating stochastic resistances (SR). The basic design principle for p-bit hardware realization involves using the resulting fluctuating resistance (R) of such stochastic MTJ structures in conjunction with necessary electrical components to realize a tunable random number generator as shown in fig. 1.2.

We apply magnet and circuit physics to comprehensively evaluate and characterize lowbarrier magnet (LBM) based p-bit implementations shown in fig. 1.3. The fundamental design principle of these devices is actually independent of the magnetic realizations, it applies to any stochastic resistor (SR). So, we also classifying necessary and sufficient conditions for designing p-bits from this general perspective and hope these design rules stimulate discussion in the realization of different stochastic resistors.

Figure 1.3. p-bit realizations with stochastic MTJ: In each design the LBM MTJs act like a stochastic fluctuating resistance. The fluctuations are tuned to behave like a p-bit. In (a) Design 1, the tunability is achieved through spin current manipulation of magnetic state. The structure and operation principle is similar to the spin-orbit-torque (SOT) controlled MRAM. In (b) Design 2, the structure looks like a spin-transfer torque (STT) MRAM, but it achieves tunability mostly through the NMOS transistor. (c) shows the realization of a compact building block - the weighted p-bit (wpbit) using design (b) coupled to a capacitive voltage adder to perform the weight logic. We demonstrate fully hardware realization of p-circuit operation using this building block through SPICE simulation.

We evaluate the performance of the proposed designs using SPICE compatible multiphysics modules, where benchmarked spintronic device models [58] are coupled with stateof-the art transistor models [59]. We project the overall performance of LBM based PSL hardware based on the individual p-bit performance characteristics. The LBM implementations of p-bits enable autonomous or clock-less operation of p-circuits and are thus not limited by clock-frequencies like digital circuits. We benchmark PSL hardware performance against digital implementation of Ising Machines by focusing on problem and substrateindependent performance metrics - flips per second (fps) and energy per flip. These metrics could serve as key figures of merit in the benchmarking test suits for the emerging class of specialized probabilistic hardware.

Figure 1.4. Evaluation of PSL framework: We define a set of performance metrics to benchmark the performance of PSL hardware. We evaluate the p-bit performance in terms of the average time and energy it takes to flip to a new random state. We emphasise the evaluation of hardware performance in terms of a problem independent metric - flips per second. It has been shown that PSL can be realized as a hardware accelerator for a wide spectrum of applications, in this thesis we benchmark our hardware performance against the digital implementations of Ising Machines.

## 1.3 Organization of Thesis

This thesis is aimed to present a comprehensive evaluation of probabilistic spin logic hardware for compact and efficient implementation of probabilistic algorithms. Our primary focus is on sprintronic devices realized with low-barrier magnets (LBMs). We discuss the interesting physics of mono-domain low-barrier ( $\Delta \leq k_B T$ ) magnets which is typically ignored and provide analytical expressions to characterize its fluctuation dynamics and predict current and magnetic-field response. The thesis is organized as follows:

**Chapter 2** presents a detailed performance analysis of p-bit realizations using low-barrier magnet (LBM) based magnetic tunnel junctions (MTJ). We define the energy and delay for these class of devices and identify the magnet and transistor properties that contribute to them. Our analysis identifies the correlation time of magnetization be a crucial parameter that determines the response of such devices. We show that this correlation time can be in sub-ns timescales for circular disk magnets with in-plane magnetic anisotropy (IMA) having low energy barriers ( $\leq k_BT$ ). These fast fluctuations and the compact realization leads to energy requirements of only ~ a few fJ to evaluate the BSN function, orders of magnitude lower than the digital CMOS implementations.

A key result we highlight in this chapter is difference between the fluctuation dynamics of mono-domain LBM with in-plane magnetic anisotropy (IMA) and perpendicular magnetic anisotropy (PMA). The presence of large out-of-plane demagnetization fields enable an almost two-orders of magnitude faster precession-like fluctuation dynamics in the circular-IMA magnets compared to its PMA counterpart. The striking numerical observation is backed by physical understanding and analytical expressions in this chapter. Following the theoretical predictions,  $\sim$  GHz fluctuations have been observed in circular IMA LBM MTJ structures recently.

Chapter 3 presents a structured design guideline for realization of p-bit hardware using stochastic MTJs for designers. We identify necessary conditions for successful realization of p-bits and define a systematic approach to matching the magnetic and circuit parameters for the embedded MTJ hardware.

We also evaluate the performance of autonomous probabilistic computing hardware realized using s-MTJs against the clocked digital implementations of Ising Machines in this chapter. We connect our device-level analysis to problem independent hardware figures-ofmerits: *flips per second* and dissipated *energy per flip* that can be used to benchmark such probabilistic hardware. The naturally stochastic hardware can overcome the technological difficulties of producing random numbers with deterministic hardware and also eliminate the need for a global clock and sequencers. The compact unit can drastically reduce the area footprint while promising massive scalability by leveraging the existing Magnetic RAM (MRAM) technology.

**Chapter 4** presents the design of a complete building block for PSL by augmenting the p-bits with a floating-gate MOS-based capacitive adder to provided the weighted-sum input locally. p-bit interconnections can be implemented off-chip either in software or with a hardware matrix multiplier unit, but that requires data to be transferred back and forth. So instead we present a low-level compact hardware implementation where each p-bits come with its own local capacitive adder network to provide inputs is proposed. We call these buildingblocks weighted p-bits. We demonstrate that such weighted p-bits can interconnected like gates and scale from 1-bit invertible full-adder to small instances of more complex problems like the subset-sum problem. This type of building blocks are suited for realizing p-circuits with sparse and discrete weights.

**Chapter 5** departs a little from probabilistic hardware and proposes a new type of magnetoelectric memory device that stores information on magnetic easy-axis or pseudo-magnetization, in piezoelectric/ferromagnetic (PE/FM) heterostructures. We present an equivalent circuit model of the magnetoelectric (ME) phenomena and use SPICE simulations to benchmark this model against experimental data that demonstrate the read and write operation through the ME effect. We show how the magnetoelectric coupling between the PE/FM combination can lead to non-volatility in pseudo-magnetization even when the magnet is designed as a low-barrier nanomagnet.

Chapter 6 provides a summary of this work and a future outlook.

# 2. LOW BARRIER MAGNET DESIGN FOR HARDWARE PROBABILISTIC BITS

Most of the materials in this chapter have been extracted verbatim from the paper: "Low Barrier Magnet Design for Efficient Hardware Binary Stochastic Neurons", O. Hassan, R. Faria, K. Y. Camsari, J. Z. Sun, and S. Datta, published in IEEE Magnetic Letters, vol. 10, 2019 [60].

In this chapter we evaluate stochastic magnetic tunnel junction (s-MTJ) based realizations of the fundamental building block of probabilistic spin logic (PSL) - the probabilistic bit (p-bit). Low barrier magnets (LBMs) built either from perpendicular magnets designed to be close to the in-plane transition or from circular in-plane magnets can provide a natural physical source of randomness for the realization of p-bits [37], [57], [61]. MTJs utilizing such LBMs have been shown to be well-suited for the implementation of random number generators (RNGs) [55], [56], [62]. The p-bits, which are essentially three terminal tunable RNGs can be realized by combining s-MTJs with standard CMOS transistors, similar to spin-orbit torque (SOT) and spin-transfer torque (STT) magnetoresistive random access memory (MRAM) devices [31], [63]. We discuss the physics of low-barrier magnets and evaluate the performance of two such p-bit designs in this chapter.

Asp-bits are analogous to the binary stochastic neurons (BSNs) in stochastic neural networks, we use the word BSN and p-bit interchangeably throughout this thesis.

#### 2.1 Hardware p-bit realizations

Many inference and machine learning algorithms are based on networks of binary stochastic neurons [42], [64]–[68] each of whose response  $m_i$  at time step (n+1) is determined by the input  $I_i$  at time n ( $r_i$ : random number between -1 and +1):

$$m_{\rm i}(n+1) = \operatorname{sgn}[\tanh I_{\rm i}(n) - r_{\rm i}]$$

(2.1)

In the absence of an input  $I_i$  the output  $m_i$  fluctuates randomly between two values -1 and +1. A positive  $I_i(n)$  makes +1 more likely, while a negative  $I_i(n)$  makes -1 more likely [69]. Each BSN described by eq. 2.1 receives its input from a weighted sum of other BSNs obtained

Figure 2.1. Fluctuation Dynamics of LBM: (a) Schematic illustration of circular LBM with saturation magnetization  $M_s$  and volume  $\Omega = \pi (D/2)^2 t$  and the magnetization  $\mathbf{m} = \mathbf{M}/M_s = (m_x, m_y, m_z) \equiv (\cos \theta, \sin \theta \sin \phi, \sin \theta \cos \phi)$ . SPICE simulation shows m(t) dynamics on Bloch sphere of a low barrier circular magnet with  $(\Delta \approx 0)$  for magnet with (b)  $H_{kp} \approx 0$  and (c)  $H_{kp} \approx -4\pi M_s \approx -13.8$  kOe, where  $H_{kp} = 2K_s/t - 4\pi M_s$  is the perpendicular anisotropy along x-axis and the in-plane anisotropy  $H_{ki} \approx 0$  due to circular shape.

from a "synapse"  $I_i(n) = \sum_j W_{ij} m_j(n)$ . A wide variety of functions can be implemented by properly designing or learning the weights  $W_{ij}$  [39], [70], [71].

The BSN function (eq. 2.1) is evaluated repeatedly in modern algorithms but they are typically implemented in software. Efforts have been put into developing a suitable hardware for accelerating evaluation of this function, many of which are based on magnetoresistive random access memory (MRAM) technology which is a major contender in the field of nonvolatile memory using stable magnets to store information in the form of 0's and 1's. By contrast, BSNs can be built out of nanomagnets designed to have low energy barriers [37], [61], [62], [72]–[76]. The performance of such BSN designs are largely dependent on the magnetization fluctuation rates of the LBM's, making it important to design the low barrier magnet to have a high fluctuation rate.

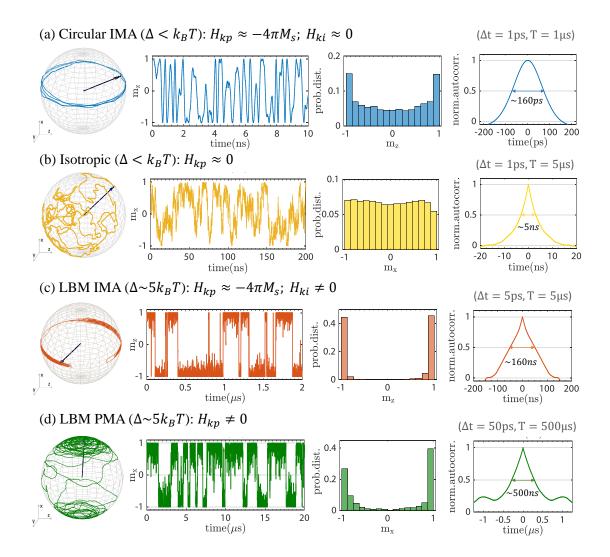

The time scale of fluctuations can be very different for the two categories of low barrier magnets as shown in fig. 2.1b and c. In PMA with vanishing perpendicular anisotropy field making  $\Delta \rightarrow 0$ , the thermal noise makes the magnetization fluctuate randomly anywhere on the Bloch sphere, while in circular IMA with no preferred easy axis and a large effective demagnetization field ( $H_D = 4\pi M_s$ ) restricts the fluctuations to to a compressed region near the equator (i.e. in-plane moment), making more rapid fluctuations possible.

In this chapter, we present a distinction between fluctuation dynamics of low barrier PMA and IMA magnets providing analytical expressions for two very important parameters for performance evaluation of hardware BSNs: the correlation time  $\tau_c$  and pinning current  $I_p$  for  $\Delta \approx k_B T$  and below. Circular IMA magnets have a correlation time two orders of magnitude smaller compared to PMA and a pinning current that is much higher. We also present a device level performance evaluation on two previously proposed compact BSN designs [31], [77] using circular IMA magnet and show that the sub-ns operation results in only ~ a few fJ of energy requirement for evaluating the BSN function which is orders of magnitude lower than its CMOS implementation [78], [79].

## 2.2 Low Barrier Magnet ( $\Delta \leq k_BT$ ) Dynamics

#### 2.2.1 Correlation Time

A key parameter defining the BSNs performance would be the rate at which it produces the random numbers. For an LBM BSN, this rate is related to the magnetization fluctuation rate of the low barrier magnet. The time it takes for the magnet to lose its memory, the *correlation time*  $\tau_c$  is defined by the full-width-half-maxima of the temporal auto-correlation function C(t) of magnetization and could be used to characterize the relevant time-scale of operation of BSN.

In low barrier magnets where the energy barrier is well below the thermal energy ( $\Delta \ll k_B T$ ) its magnetization becomes a continuous variable. The Arrhenius law which describes the thermal fluctuations of high barrier magnets ( $\Delta \gg k_B T$ ) with two distinct magnetic states thus does not hold for LBM [61], [80]. Instead, thermal fluctuations in monodomain low barrier magnets could be characterized starting from Fokker-Planck equation (FPE)[81], [82] or the Landau-Lifshitz-Gilbert (LLG) equation including a Langevin term describing thermal fluctuation [80], [83].

Coffey et. al. [82] analyzes the magnetic fluctuations in a PMA magnet due to thermal noise in detail by using the Fokker-Planck equation (FPE) derived by W. F. Brown [81]. The

analysis presented in these references focused on high-barrier magnets but are not limited to it and thus can be evaluated for  $\Delta \rightarrow 0$  to describe the low barrier magnet dynamics of PMA magnets which agree well with numerical results.

PMA:

$$C(t) = \exp\left(-2\alpha\gamma \frac{k_B T}{M_S \Omega}|t|\right)$$

$\tau_c = \frac{M_S \Omega}{\alpha\gamma k_B T} \ln(2)$

(2.2)

In low barrier circular IMA magnets when thermal noise kicks the magnetization out-ofplane, due to absence of an easy axis and the presence of large orthogonal demagnetization field  $H_D$  the in-plane magnetization starts precessing. If we consider an ensemble of such magnets each with a different precession frequency due to thermal noise, the average magnetization vector would quickly dissipate. The auto-correlation function of the in-plane magnetization  $m_z = \cos(\phi(t))$  could be expressed as:

$$C(t) = \int_{-1}^{1} dm_x \cos(\gamma H_D m_x t) \rho(m_x) / \int_{-1}^{1} dm_x \rho(m_x)$$

Figure 2.2. Correlation Time of PMA and IMA magnets (a) The normalized auto-correlation of magnetic fluctuations taken in the z direction, (b) Comparison of  $\tau_c$  as a function of number of spins  $N_s \equiv M_s \Omega/\mu_B$  where  $M_s = 1100 \text{ emu/cc}$  and the volume  $\Omega$  is varied. Damping coefficient  $\alpha$  is assumed to be 0.01: Results from numerical simulations agree well with the equations cited in the text.

where the in-plane precession dynamics is described by  $\phi(t) \approx \gamma H_D m_x t$  [83] for low damping  $\alpha$ . The perpendicular magnetization  $m_x$  follows a Boltzmann distribution with  $\rho(m_x) \approx \exp(-H_D M_S \Omega m_x^2/2k_B T)$ . For large values of  $H_D$  the integral could be extended to  $\pm \infty$  and evaluated to give an expression for the auto-correlation function and correlation time as follows:

IMA:

$$C(t) = \exp\left(-\gamma^2 \left(\frac{H_D k_B T}{M_S \Omega}\right) \frac{t^2}{2}\right)$$

$\tau_c = \sqrt{8 \ln(2)} \frac{1}{\gamma} \sqrt{\frac{M_S \Omega}{H_D k_B T}}$

(2.3)

In numerical simulations, we observe essentially the same auto-correlation behavior, even when the correlation function is obtained from the time-dependent fluctuations of a single magnet fluctuating for long time periods as shown in fig. 2.2a. In PMA no such precessional fluctuation mechanism exists as the internal fields are compensated.

Figure 2.3. Pinning current of PMA and IMA magnets (a) PMA and IMA magnet's long time averaged magnetization  $\langle m \rangle$  as a function of applied spin current  $I_S$ , (b) Comparison of PMA/IMA  $I_P$  as a function of number of spins  $N_s \equiv M_s \Omega/\mu_B$  where  $M_s = 1100$  emu/cc and the volume  $\Omega$  is varied. Damping coefficient  $\alpha$  is assumed to be 0.01: Results from numerical simulations agree well with the equations cited in the text.

#### 2.2.2 Biasing Current

Another important parameter for evaluating an LBM based stochastic device performance is itds sensitivity to spin current. To maintain stochasticity in MRAM type devices, they should be immune to read current, and the amount of current required to bias BSN devices is also relevant for power considerations. In high barrier magnets the concept of switching current is presented [84], for low barrier magnets we refer to *pinning currents* as the relevant quantity which can be mathematically defined as:  $I_P = (\langle m \rangle / I_S)^{-1}$  as shown in fig. 2.3. The pinning currents for PMA can be derived from steady-state Fokker-Planck equation as described in Ref. [85], while for IMA magnets with  $\Delta \to 0$  and low damping, the pinning current can be approximated from the relation  $I_P \equiv qN_S C(0) / \int_0^\infty dt C(t)$ . fig. 2.3 shows that the numerical results are well described by the obtained expressions:

PMA:

$$I_P = \frac{6q}{\hbar} \alpha k_B T$$

(2.4)

IMA:

$$I_P = \frac{2q}{\hbar} \sqrt{\frac{2}{\pi}} \sqrt{H_D M_S \Omega k_B T}$$

(2.5)

The derivation of eq. 2.4 and eq. 2.5 assume zero energy barriers, but numerically we observe that these equations are approximately valid for barriers up to  $\Delta \approx k_B T$ . In practice obtaining near-zero barrier circular magnets could be challenging due to process variation. For interconnected networks of p-bits, a distribution of correlation times for each p-bit needs to be considered as shown in Ref.[86].

Note that IMA-based designs can achieve sub-nanosecond correlation times even with fairly large volumes, provided that monodomain behavior can be preserved with a small enough diameter, while PMA-based designs tend to be much slower making IMA magnets more suitable for BSN applications. This is accompanied by fairly large pinning currents for IMA compared to PMA which minimizes read disturb effects.

In the following section we used circular IMA magnets M1 and M2 with volumes  $800\pi$  and  $20480\pi$  nm<sup>3</sup>, respectively for evaluating the performance of two LBM based hardware BSN designs.

#### 2.3 Performance Evaluation of p-bits

In this section we evaluate the steady-state and time response of two hardware BSN designs proposed in the past [31], [77] shown in fig. 2.4 and measure the energy and delay associated with each.

Figure 2.4. Two BSN designs using stochastic MTJ with fluctuating resistance: (a) BSN-A uses an input spin current to pin the fluctuating resistance [31]. Structurally it looks similar to spin-orbit torque magnetoresistive random access memory (SOT-MRAM). (b) BSN-B looks similar to spin transfer torque MRAM (STT-MRAM) but it makes no use of spin torque. The input voltage controls the resistance of a field effect transistor (FET) which is in series with the MTJ [77]. (c) and (d) show the circuit models used for SPICE simulations.

The designs makes use of a magnetic tunnel junction (MTJ) whose free layer is a low barrier magnet with a fluctuating magnetization  $m_z(t)$ , resulting in a fluctuating resistance,  $R_{\rm MTJ}(t)^{-1} = G_0[1 + m_{zi}(t) \text{TMR}/(2 + \text{TMR})]$  where  $G_0$  is the average conductance and TMR is the tunneling magnetoresistance. The fluctuating resistance  $R_{MTJ}(t)$  is converted to a fluctuating voltage  $V_i(t)$  by the potential divider:

$$\frac{V_{\rm i}(t)}{V_{DD}/2} = (\pm) \frac{R_{\rm MTJ}(t) - R_0}{R_{\rm MTJ}(t) + R_0}$$

(2.6)

The fluctuations are controlled by two different mechanisms in the two designs. BSN-A is a spin-orbit-torque controlled device [31] which uses the input spin current (in y direction) from the GSHE layer to pin the free layer magnetization (in z direction) of the MTJ thereby pinning  $R_{MTJ}$  and implements (+) configuration of eq. 2.6. BSN-B is a series resistance controlled device [77] which uses the input voltage to control the transistor resistance  $R_0$ and implements the (-) configuration of eq. 2.6. Ideally  $R_{MTJ}$  remains unchanged, though in actual designs it may be important to consider unintended pinning effects of the current. Both designs use a minimum sized CMOS inverter to convert the fulctuating  $V_i$  into a railto-rail output  $V_{OUT}$ . In each case we will use SPICE simulations based on state-of-the-art stochastic Landau-Lifshitz-Gilbert (s-LLG) models for LBM's [87] free layer of the MTJ having  $G_0 \simeq (25K\Omega)^{-1}$  and TMR =  $2P^2/(1 - P^2) = 110\%$  with polarization  $P \simeq 0.6$ coupled with 14 nm HP FinFET's [88] to show that the output voltage  $V_{OUT}$  from a specific BSN is approximately related to its input  $V_{IN}$  by an equation that minics eq. 2.1 :

$$\frac{V_{OUT}(t+t_0)}{V_{OUT0}} \approx \operatorname{sgn}\left[\tanh\frac{V_{IN}(t)}{V_{IN0}} - r(t)\right]$$

(2.7)

with scaling factors  $V_{OUT0}$ ,  $V_{IN0}$ ,  $t_0$  characterizing the specific hardware design.

#### 2.3.1 Steady-State Response

Fig. 2.5 shows the individual steady state response of design A,B using magnet M1 and M2, which can all collapse onto the same curve using appropriate scaling parameters. The output scaling quantity  $V_{OUT0} \simeq V_{DD}/2 = 0.4V$  is the same for all cases as this quantity is defined entirely by CMOS inverter output voltage swing. On the other hand, the input scaling parameters are very design dependent. For BSN-A I<sub>IN0</sub> is determined by pinning currents of magnets M1 and M2. Indeed, the scaling parameters in fig. 2.5b were obtained

from eq. 2.5. For BSN-B  $V_{IN0} \sim 50 \text{mV}$  for both magnets, determined by transistor characteristics. Note that the SPICE simulations include the read disturb current, but its effect is minimal due to the high pinning currents of low barrier IMA compared to PMA as can be seen from eq. 2.4 and eq. 2.5.

Figure 2.5. Steady-state Response: (a) Plot of  $\langle V_{OUT} \rangle$  (averaged over a time window  $\gg \tau_c$ ) vs  $V_{IN}$  for designs A, B using magnets M1, M2. The grey lines indicate  $V_{OUT}$  without time averaging. (b) All four plots in (a) collapse onto a single curve using appropriate scaling parameters  $V_{OUT0}$ ,  $I_{IN0}$ ,  $V_{IN0}$ . The resulting curve approximately follows the time averaged  $\langle m_i \rangle$  of eq. 2.1.

#### 2.3.2 Time Response

Fig. 2.6 shows the two relevant timescales associated with BSN operation. First is the correlation time of the output voltage which is determined by the magnet parameters. Indeed, the FWHM of the autocorrelation function corresponds well to eq. 2.3, which is expected since circuit related times are much shorter in this case. Second is the response time which is very design dependent. For BSN-A it is determined by magnet physics while for BSN-B it is determined by transistor physics [89]. Our analysis shows that the response time  $t_0$  of a single BSN-B neuron is independent of magnet parameters. However, the response of an interconnected network of such neurons would also involve the magnet correlation time  $\tau_c$ .

Figure 2.6. Two relevant time-scales for BSN Operation: (a), (b) show correlation time and (c),(d) show response time. (a) Output voltage fluctuations with  $I_i = 0$  for designs A, B using magnets M1, M2. (b) Corresponding normalized autocorrelation functions. (c) Response to a step function  $I_i : -10 \rightarrow 0$  at t=0 averaged over 1000 ensembles for all four cases.(d) All four curves in (c) collapse onto a single curve using appropriate scaling parameter  $t_0$ .

# 2.3.3 Power Consumption

Fig. 2.7 shows the power drawn from the sources  $\pm V_{DD}/2$  individually by the MTJ branch and the inverter branch as  $V_{IN}$  is stepped at t = 0 from different initial to final values as indicated. The steady-state values of the power dissipated in both the MTJ and inverter branches agree quantitatively with the simple estimate (see dashed line in figures) from  $V_{DD}^2/R$ , where R is the appropriate resistance, namely  $R_{MTJ} + R_0$  for the MTJ branch, and  $R_{\rm NMOS} + R_{\rm PMOS}$  for the inverter branch. For the MTJ branch, the power dissipated is

Figure 2.7. Power Consumption for (a) BSN-A and (b) BSN-B when the input is stepped at t=0 as indicated.

~10-20  $\mu W$  for all cases except in the middle panel for BSN-B. In this case the final state involves a large negative input voltage  $V_{IN}$  for which the series transistor is turned OFF, making the resistance R extremely large, so that  $V_{DD}^2/R \rightarrow 0$ . In all other cases, the total R is of the order of the MTJ resistance ~  $25K\Omega$ , so that  $V_{DD}^2/R \sim 25\mu W$ . For the inverter branch, BSN-A dissipates ~10  $\mu W$  since the voltage at the inverter input in all cases remains close to the threshold value making both NMOS and PMOS branches fairly conducting. On the other hand, for BSN-B, PMOS and NMOS get turned off for large positive and for large negative input  $V_{IN}$  respectively, making the effective R very large. Only for input voltages ~ 0, both PMOS and NMOS branches are conducting, giving rise to a steady-state power ~  $10\mu W$  like BSN-A. This number could be lowered if we can engineer larger voltage fluctuations at the inverter input,  $|\delta V_i| \sim P^2 V_{DD}/(4 - P^4)$ . Our assumed TMR of 110% corresponds to  $P \sim 0.6$ , giving a  $|\delta V_i| \sim 75 \ mV$ .

Note that in this analysis the power drawn from  $V_{IN}$  is not considered which is expected to be very different for a low input impedance design (BSN-A) compared to a high input impedance design (BSN-B) and will depend on the driving mechanism and circuitry. Overall, both designs suffer from significant steady-state power losses and would need to be turned off when not in use. This can be done straightforwardly for BSN-B using a large negative input voltage  $V_{IN}$ . The key point to note is that the energy dissipated during the evaluation of the BSN function is ~ 20  $\mu W \times 50 \ ps =1$  fJ which is orders of magnitude smaller than CMOS implementations of the same function [78], [79] as noted earlier from system level simulations in [90].

### 2.4 Summary

The device level analysis presented here elucidates the role of proper magnet design for achieving the subnanosecond response times that is crucial for fast and low energy operation. The analysis also suggests low barrier IMA magnets maybe a more suitable candidate for pbit type applications due to its fast fluctuation dynamics, while modern non-volatile MRAM technology is largely based on PMA magnets [52].

# 3. EVALUATION OF PROBABILISTIC BITS FOR ACCELERATING ISING MACHINES

Most of the materials in this chapter have been extracted verbatim from the paper: "Quantitative Evaluation of Hardware Binary Stochastic Neurons", O. Hassan, S. Datta, and K. Y. Camsari. (to be submitted)

In the era of internet of things (IoT), combinatorial optimization problems are ubiquitous [25]. Infact, most of the real-problems that quantum computers are aiming to solve can be formulated as combinatorial optimization problems.From directing traffic flow [91], to routing interconnections in integrated circuit design [92], [93], to making financial decisions [94], drug discoveries [95], etc. - all involve solving a form of combinatorial optimization problems. The demand for solving these problems faster and more efficiently is ever-increasing. But such problems typically fall into the category of NP-hard or NP-complete class in computational complexity theory [14], with no known polynomial time solution, making them notoriously difficult to solve in digital computers using traditional computing. Ising computing maps combinatorial optimization problems to an Ising model, and solves it by searching for the ground state of the system described by [15], [37]:

$$E = -\frac{1}{2} \sum_{i,j=1}^{N} J_{ij} m_i m_j - \sum_{i=1}^{N} h_i m_i$$

(3.1)

where, m denotes the Ising spin, J is the coupling co-efficient and h is the external bias. In the machine learning field, the same underlying principle is used to for Boltzmann Machines. The binary stochastic neurons (BSNs) [65] of stochastic neural networks are well suited to function as a 'spin' is such systems, described mathematically by:

$$m_{\rm i} = \operatorname{sgn}[\tanh(I_{\rm i}) - r_{\rm i}] \tag{3.2}$$

where  $r_i$  is a random number between +1 and -1, and  $I_i = -\partial E/\partial m_i$  is the input to the neuron.

Figure 3.1. 1MTJ-3T compact BSN hardware which utilizes the natural physics of low-barrier nanomagnets holds the promise to accelerate the simulated annealing processors.

Given the importance of optimization problems, a lot of research has gone into developing algorithms and identifying appropriate hardware for Ising computing. Various approaches including quantum computers based on quantum annealing (QA) or adiabatic quantum optimization (AQC) implemented with superconducting circuits [17], coherent Ising machines (CIMs) implemented with laser pulses [18], phase-change oscillators [19], or CMOS oscillators [20]–[23] and digital annealers based on simulated annealing (SA) [16] implemented with digital circuits [24]–[30] are being explored.

In this chapter, we comprehensively evaluate and characterize a stochastic magnetic tunnel junction (sMTJ) based realization of the Ising spin (eq. 3.2) where random numbers are generated using the natural physics of low barrier nanomagnets [77] in a compact design. A network of these BSN units can be coupled with a memristive crossbar array [96]–[98] to perform the synaptic operation as shown in fig. 3.1 can drastically improve the area requirements and accelerate computation speed of Ising Machines. We evaluate the performance of the BSN device in terms of its energy and delay metrics and connect these to the problem and substrate-independent metric of *flips per second* that the probabilistic system makes [48].