# APPROXIMATE COMPUTING: FROM CIRCUITS TO SOFTWARE

by

### Younghoon Kim

### A Dissertation

Submitted to the Faculty of Purdue University

In Partial Fulfillment of the Requirements for the degree of

### **Doctor of Philosophy**

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

### Dr. Anand Raghunathan, Chair

School of Electrical and Computer Engineering

### Dr. Cheng-Kok Koh

School of Electrical and Computer Engineering

### Dr. Kaushik Roy

School of Electrical and Computer Engineering

### Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

### Approved by:

Dr. Dimitri Peroulis

### ACKNOWLEDGMENTS

My long journey for a Ph.D. degree would have not been possible without the help of great people around me. Firstly, I'd like to express my sincerest gratitude to my advisor, Prof. Anand Raghunathan, for all the support and guidance on my research. I could learn all aspects of research from him — defining the right problem, setting up technically sound experiments, and writing the paper with a fresh angle. On the personal side, he has helped me endure physical and mental hardships by showing benevolence as well as providing motivation. It was such an honor being able to work with him.

Besides my advisor, I would like to thank my committee members — Prof. Cheng-Kok Koh, Prof. Kaushik Roy, and Prof. Vijay Raghunathan — for their valuable comments that helped my thesis to be in a better shape.

Special thanks to Dr. Swagath Venkataramani, who has been involved in all my research projects and always revised the paper to perfection. I admire his relentless enthusiasm for research and his positive attitude.

I thank all ISL colleagues whom I shared my on-campus life with. A wide range of discussions from research to culture and politics made my days in MSEE337 enjoyable. Thanks to Ashish, Shubham, Younghyun, Sanchari, Jacob, Manik, Sarada, Shrihari, Sourjya, Reena, Soumendu, Christin, Sanjay, Vinod, and Abinand. I wish all the best to everyone in their future endeavors.

Thanks to all my friends in the three main groups that I have actively participated in: ECE, PKTC, and SNUPU. May our paths cross again in the future.

Last but not the least, I'd like to thank my family: My parents and my sister for supporting me both financially and spiritually. Suyeon, my dear wife, for staying by my side through the endless Ph.D. study. Jiseob and Jiin, my lovely children, for being a better creation than any of my thesis chapters.

## TABLE OF CONTENTS

| LI | ST O | F TABI  | LES                                                                                 | 9  |

|----|------|---------|-------------------------------------------------------------------------------------|----|

| LI | ST O | F FIGU  | JRES                                                                                | 10 |

| AH | BBRE | VIATIO  | ONS                                                                                 | 12 |

| AI | BSTR | ACT .   |                                                                                     | 13 |

| 1  | INT  | RODUC   | CTION                                                                               | 16 |

|    | 1.1  | Approx  | ximate Computing                                                                    | 17 |

|    | 1.2  | Thesis  | Contributions                                                                       | 19 |

|    |      | 1.2.1   | Approximate Circuit Design using Clock Overgating                                   | 19 |

|    |      | 1.2.2   | Value Similarity Extensions for Approximate Computing in General-Purpose Processors | 20 |

|    |      | 1.2.3   | Data Subsetting: A Data-Centric Approach to Approximate Computing                   | 21 |

|    | 1.3  | Thesis  | Organization                                                                        | 22 |

| 2  | REL  | ATED    | WORK                                                                                | 23 |

|    | 2.1  | Circuit | Design Techniques for Approximate Computing                                         | 23 |

|    | 2.2  | Archit  | ectures for Approximate Computing                                                   | 23 |

|    | 2.3  | Softwa  | re Techniques for Approximate Computing                                             | 24 |

| 3  | APP  | ROXIM   | MATE CIRCUIT DESIGN USING CLOCK OVERGATING                                          | 25 |

|    | 3.1  | Introd  | uction                                                                              | 25 |

|    | 3.2  | Compa   | arison to Related Work                                                              | 27 |

| 3.3 | Backg  | round                                            | 28 |

|-----|--------|--------------------------------------------------|----|

|     | 3.3.1  | Power Dissipation in Sequential Circuits         | 28 |

|     | 3.3.2  | Clock Gating                                     | 29 |

| 3.4 | Design | n Approach                                       | 30 |

|     | 3.4.1  | Clock Overgating: Concept                        | 30 |

|     | 3.4.2  | Clock Overgating: Design Space                   | 31 |

| 3.5 | Design | n Methodology                                    | 35 |

|     | 3.5.1  | Approximate Design using Clock Overgating        | 35 |

|     | 3.5.2  | Identifying Clock Overgating Candidates          | 37 |

| 3.6 | Exper  | imental Setup                                    | 38 |

|     | 3.6.1  | Benchmarks                                       | 38 |

|     | 3.6.2  | Quality and Power Evaluation                     | 38 |

| 3.7 | Exper  | imental Results                                  | 39 |

|     | 3.7.1  | Energy-Quality Tradeoff                          | 39 |

|     | 3.7.2  | Comparison with Precision Scaling                | 41 |

|     | 3.7.3  | Effectiveness of FF Grouping                     | 41 |

|     | 3.7.4  | Illustration of Clock Overgating in Action       | 43 |

| 3.8 | Summ   | ary                                              | 43 |

| VAL | UE SIN | MILARITY EXTENSIONS FOR APPROXIMATE COMPUTING IN |    |

| GEN | IERAL- | -PURPOSE PROCESSORS                              | 45 |

| 4.1 | Introd | luction                                                     | 45 |

|-----|--------|-------------------------------------------------------------|----|

| 4.2 | Comp   | arison to Related Work                                      | 47 |

| 4.3 | Value  | Similarity: Sources, Opportunities and Challenges           | 48 |

| 4.4 | VSX:   | Value Similarity Extensions for General-Purpose Processors  | 49 |

|     | 4.4.1  | VSX: Overview                                               | 50 |

|     | 4.4.2  | Program Annotations and Compiler Techniques for VSX         | 51 |

|     | 4.4.3  | Instruction Skipping & Result Reuse                         | 52 |

|     | 4.4.4  | VSX: Microarchitecture                                      | 53 |

|     | 4.4.5  | Iteration Fast-Forwarding                                   | 55 |

| 4.5 | Exper  | imental Setup                                               | 56 |

| 4.6 | Result | 58                                                          | 58 |

|     | 4.6.1  | Speedup-Accuracy Tradeoff                                   | 58 |

|     | 4.6.2  | Skip Rate Analysis                                          | 59 |

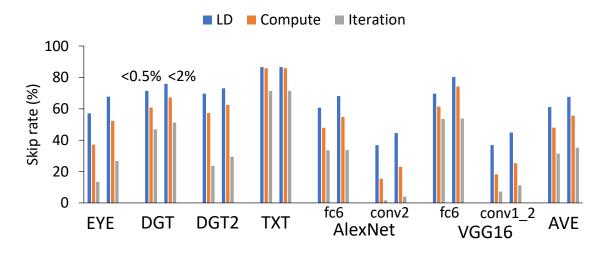

|     | 4.6.3  | Speedup Across Different Spatial Distribution of Similarity | 59 |

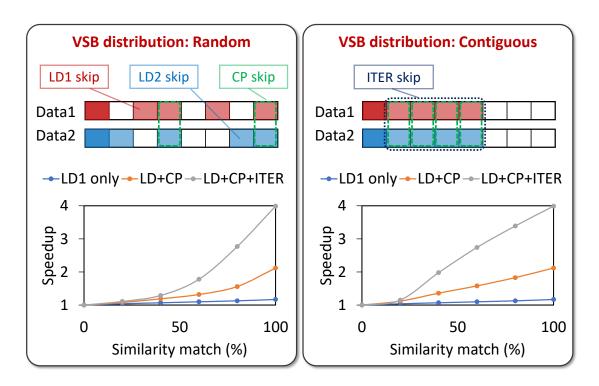

|     | 4.6.4  | VSX vs. Load Value Approximation                            | 60 |

| 4.7 | Summ   | nary                                                        | 61 |

| DAT | A SUE  | SETTING: A DATA-CENTRIC APPROACH TO APPROXIMATE             |    |

| CON | MPUTI  | NG                                                          | 63 |

| 5.1 | Introd | luction                                                     | 63 |

| 5.2 | Comp   | arison to Related Work                                      | 65 |

| 5.3 | Data S | Subsetting                               | 66 |

|-----|--------|------------------------------------------|----|

|     | 5.3.1  | Data Subsetting: Concept                 | 66 |

|     | 5.3.2  | Data Subsetting: Challenges              | 67 |

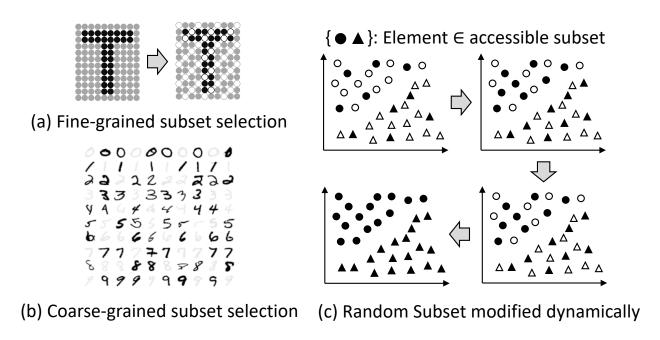

|     |        | Subset Selection                         | 67 |

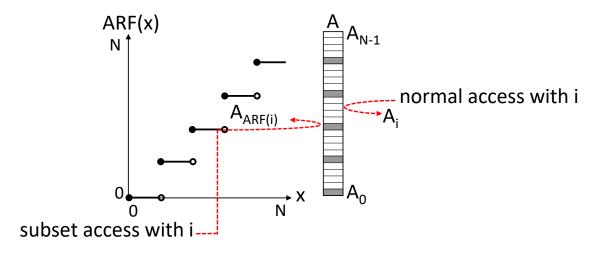

|     |        | Access Approximation through Redirection | 68 |

|     | 5.3.3  | Data Subsetting: Optimizations           | 69 |

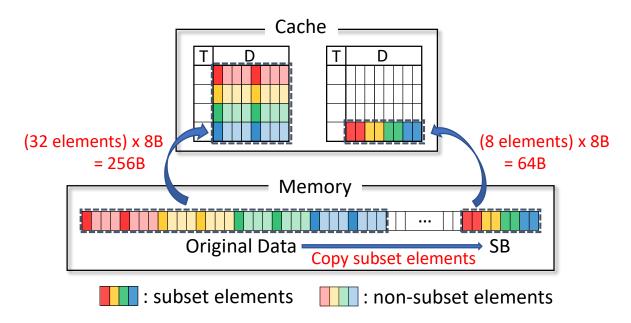

|     |        | Subset Buffer                            | 70 |

|     |        | Eliminating Redundant Computations       | 71 |

| 5.4 | Realiz | ing Data Subsetting in Software          | 72 |

|     | 5.4.1  | SubsettableTensor Data Structure         | 72 |

|     | 5.4.2  | Illustration: K-means Clustering         | 73 |

| 5.5 | Exper  | imental Setup                            | 74 |

|     | 5.5.1  | Benchmarks                               | 74 |

|     | 5.5.2  | Performance Evaluation                   | 75 |

| 5.6 | Result | 58                                       | 75 |

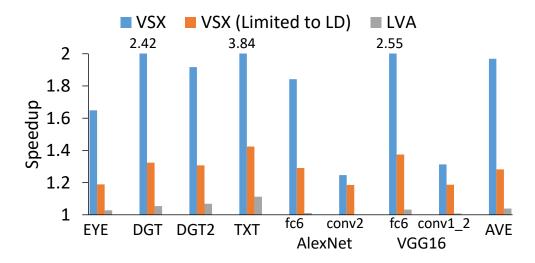

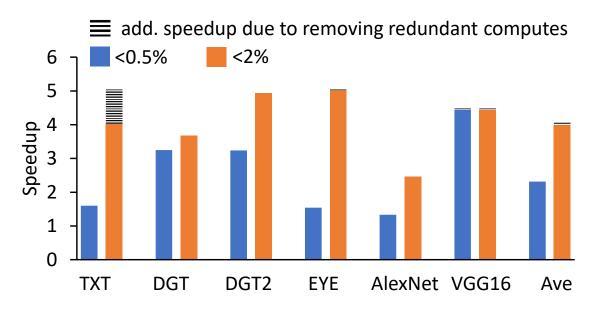

|     | 5.6.1  | Performance Benefits                     | 75 |

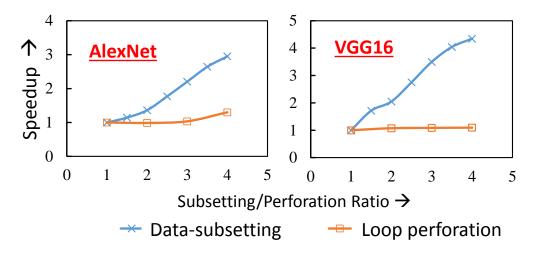

|     | 5.6.2  | Comparison with Loop Perforation         | 76 |

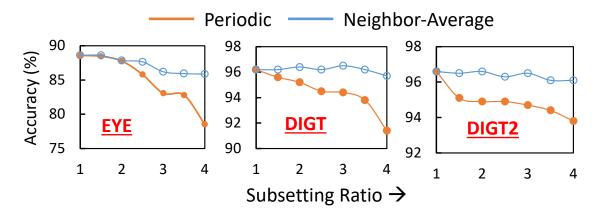

|     | 5.6.3  | Choice of Access Redirection Function    | 77 |

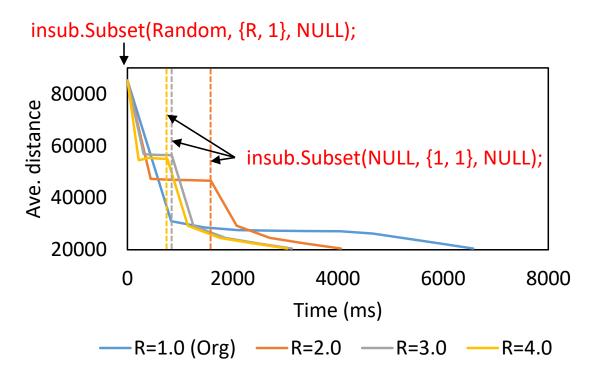

|     | 5.6.4  | Dynamic Modulation of Subset Size        | 78 |

| 5 7 | Summ   | arv                                      | 79 |

| 6 CONCLUSION | 81 |

|--------------|----|

| REFERENCES   | 83 |

| VITA         | 93 |

## LIST OF TABLES

| 3.1 | Benchmark applications                   |  |  | • |  | • |  |  |  |  | 39 |

|-----|------------------------------------------|--|--|---|--|---|--|--|--|--|----|

| 4.1 | Benchmark applications                   |  |  |   |  |   |  |  |  |  | 57 |

| 4.2 | Gem5 system configuration                |  |  |   |  |   |  |  |  |  | 57 |

| 5.1 | Machine learning benchmark applications  |  |  |   |  |   |  |  |  |  | 75 |

| 5.2 | System configuration used in experiments |  |  |   |  |   |  |  |  |  | 75 |

## LIST OF FIGURES

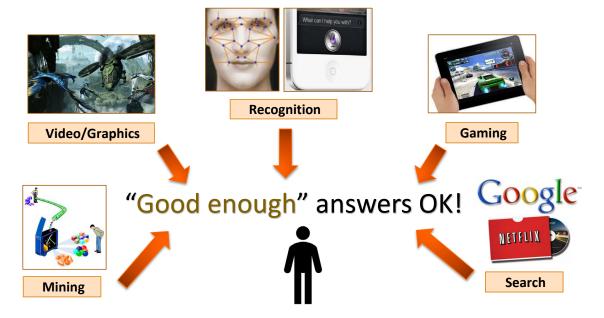

| 1.1 | Modern applications producing good-enough answers                                                               | 17 |

|-----|-----------------------------------------------------------------------------------------------------------------|----|

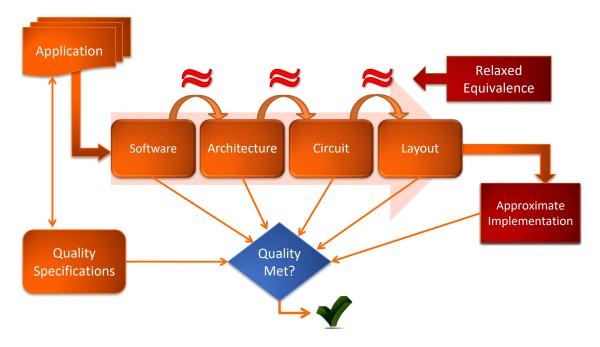

| 1.2 | Approximate computing across the layers of abstraction [3]                                                      | 18 |

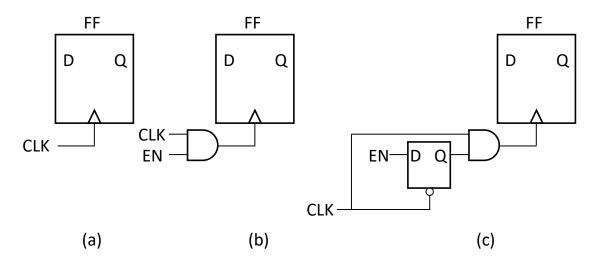

| 3.1 | Different types of clock gating logic                                                                           | 29 |

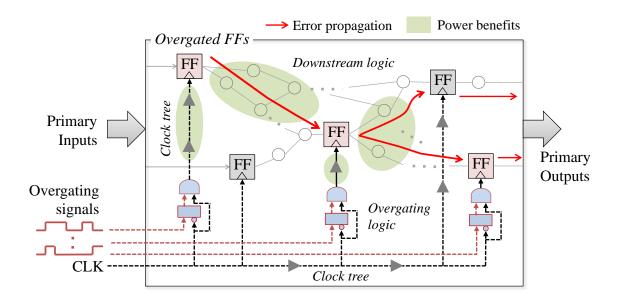

| 3.2 | Clock overgating concept                                                                                        | 31 |

| 3.3 | Design space of clock overgating configurations                                                                 | 32 |

| 3.4 | Functional grouping of FFs                                                                                      | 33 |

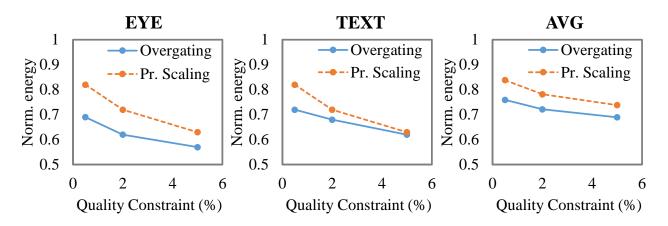

| 3.5 | Energy improvements for various quality constraints                                                             | 40 |

| 3.6 | Energy breakdown analysis                                                                                       | 41 |

| 3.7 | Energy benefits using clock overgating vs. precision scaling                                                    | 42 |

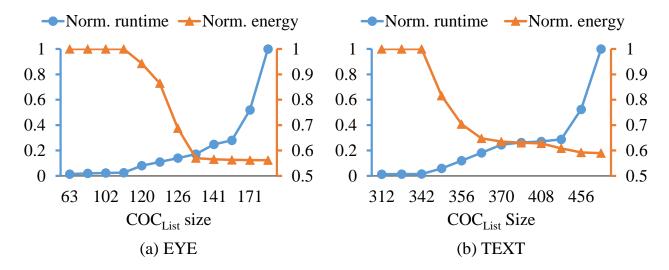

| 3.8 | Runtime vs. optimality tradeoff analysis                                                                        | 43 |

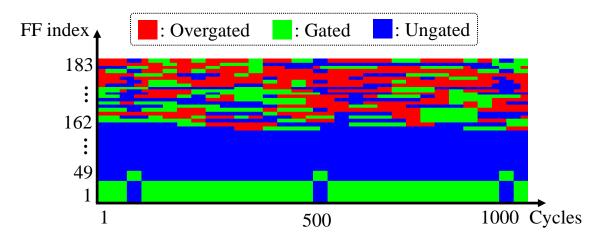

| 3.9 | Clock overgating status over time                                                                               | 44 |

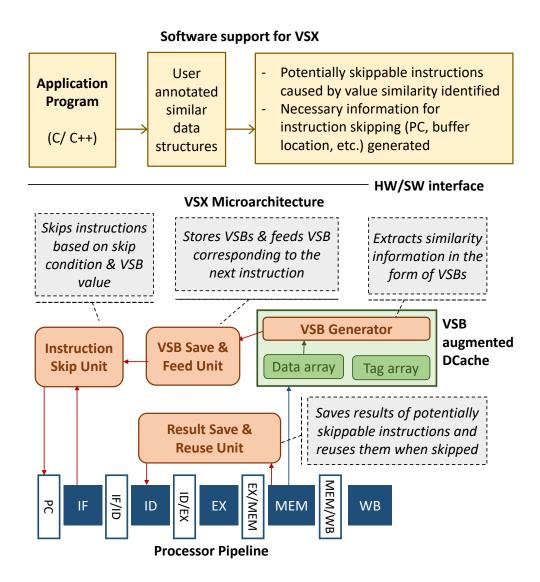

| 4.1 | VSX overview                                                                                                    | 50 |

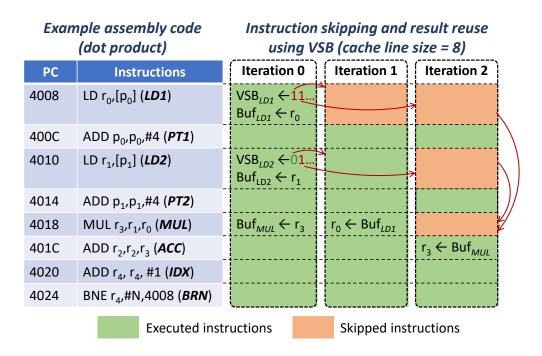

| 4.2 | Instruction skip & result reuse example                                                                         | 52 |

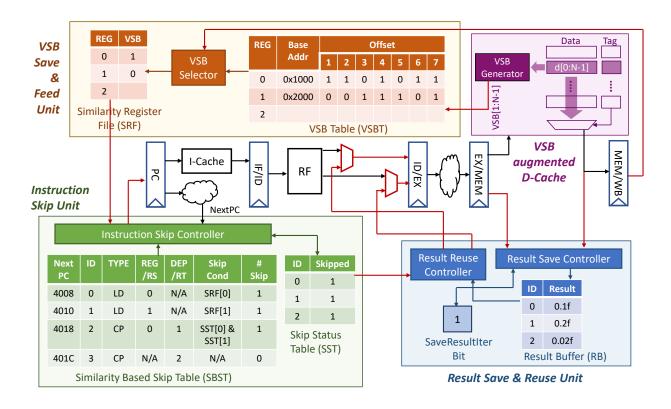

| 4.3 | VSX microarchitecture                                                                                           | 53 |

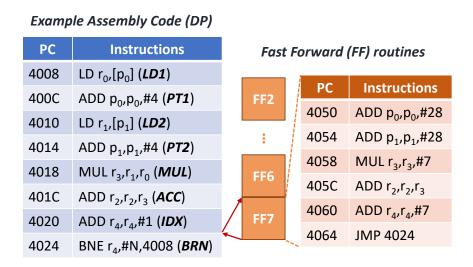

| 4.4 | Iteration skipping example                                                                                      | 55 |

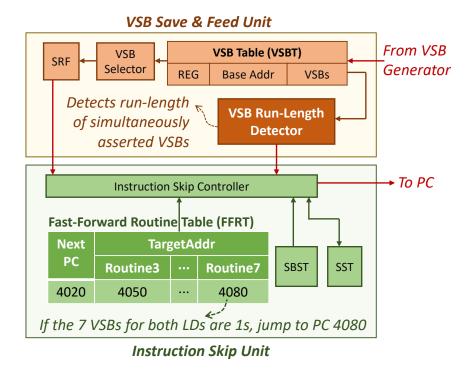

| 4.5 | Modified Instruction Skip Unit and VSB Save $\ensuremath{\mathfrak{C}}$ Feed Unit for iteration fast-forwarding | 56 |

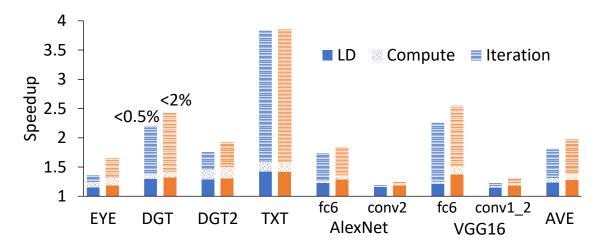

| 4.6 | Speedup-accuracy tradeoff                                                                                       | 58 |

| 4.7 | Skip rates for instructions & iterations                                                                        | 59 |

| 4.8 | Speedup vs. similarity analysis                                                                                 | 60 |

| 4.9 | Iso-accuracy speedup comparison for VSX vs. LVA                                                                 | 61 |

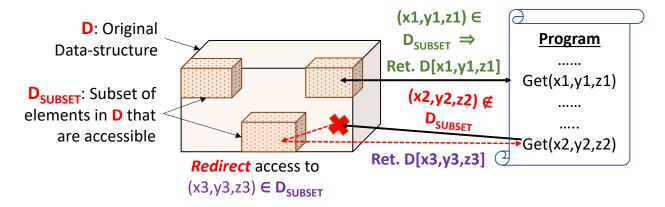

| 5.1 | Data subsetting: Concept                                                                                        | 66 |

| 5.2 | Different forms of subset selection                                                                             | 68 |

| 5.3 | Access Redirection Functions                                                                                    | 69 |

| 5.4 | Memory bandwidth reduction by using subset buffer                                                               | 71 |

| 5.5 | Speedup obtained within different quality constraints                                                           | 76 |

| 5.6 | Data subsetting vs. loop perforation                                                                            | 77 |

| 5.7 | Impact of ARF choice on accuracy                                                                                | 78 |

| 5.8 - | Data subsetting | g applied to | K-Means | clustering. |       | <br> |   |   |   |   |  | <br> |   | 79 |

|-------|-----------------|--------------|---------|-------------|-------|------|---|---|---|---|--|------|---|----|

|       |                 | 5            |         |             | <br>- | <br> | - | - | - | - |  | <br> | - |    |

### **ABBREVIATIONS**

AxC Approximate Computing

RTL Register Transfer Level

FF Flip-Flop

COT Clock Overgating Target

COE Clock Overgating Enable

MSB Most Significant Bit

LSB Least Significant Bit

VSX Value Similarity eXtensions

IF Instruction Fetch

SB Subset Buffer

ARF Access Redirection Function

FLOP Floating-Point OPeration

ML Machine Learning

DNN Deep Neural Network

GPP General Purpose Processor

VSX Value Similarity eXtensions

### ABSTRACT

Many modern workloads such as multimedia, recognition, mining, search, vision, etc. possess the characteristic of intrinsic application resilience — the ability to produce acceptable-quality outputs despite their underlying computations being performed in an approximate manner. Approximate computing has emerged as a paradigm that exploits intrinsic application resilience to design systems that produce outputs of acceptable quality with significant performance/energy improvement. The research community has proposed a range of approximate computing techniques spanning across circuits, architecture, and software over the last decade. Nevertheless, approximate computing is yet to be incorporated into mainstream HW/SW design processes largely due to the deviation from the conventional design flow and the lack of runtime approximation controllability by the user.

The primary objective of this thesis is to provide approximate computing techniques across different layers of abstraction that possess the two following characteristics: (i) They can be applied with minimal change to the conventional design flow, and (ii) the approximation is controllable at runtime by the user with minimal overhead. To this end, this thesis proposes three novel approximate computing techniques — *clock overgating* which targets HW design at the Register Transfer Level (RTL), *value similarity extensions* which enhance general-purpose processors with a set of microarchitectural and ISA extensions, and *data subsetting* which targets SW executing for commodity platforms.

Clock Overgating. The thesis first explores clock overgating, which extends the concept of clock gating — a conventional low-power technique that turns off the clock to a Flip-Flop (FF) when the value remains unchanged. In contrast to traditional clock gating, in clock overgating the clock signals to selected FFs in the circuit are gated even when the circuit functionality is sensitive to their state. This saves additional power in the clock tree, the gated FFs and in their downstream logic, while a quality loss occurs if the erroneous FF states propagate to the circuit outputs. This thesis develops a systematic methodology to identify an energy-efficient clock overgating configuration for any given circuit and quality constraint. Towards this end, three key strategies for efficiently pruning the large space of possible overgating configurations are proposed — significance-based overgating, grouping FFs into

overgating islands, and utilizing internal signals of the circuit as triggers for overgating. Across a suite of 6 machine learning accelerators, energy benefits of  $1.36\times$  on average are achieved at the cost of a very small (<0.5%) loss in classification accuracy.

Value Similarity Extensions. The thesis also explores value similarity extensions, a set of lightweight micro-architectural and ISA extensions for general-purpose processors that provide performance improvements for computations on data structures with value similarity. The key idea is that programs often contain repeated instructions that are performed on very similar inputs (e.g., neighboring pixels within a homogeneous region of an image). In such cases, it may be possible to skip an instruction that operates on data similar to a previously executed instruction, and approximate the skipped instruction's result with the saved result of the previous one. The thesis provides three key strategies for realizing this approach—identifying potentially skippable instructions from user annotations in SW, obtaining similarity information for future load values from the data cache line currently being accessed, and a mechanism for saving & reusing results of potentially skippable instructions. As a further optimization, the thesis proposes to replace multiple loop iterations that produce similar results with a specialized instruction sequence. The proposed extensions are modeled on the gem5 architectural simulator, achieving speedup of 1.81× on average across 6 machine-learning benchmarks running on a microcontroller-class in-order processor.

Data Subsetting. Finally, the thesis explores a data-centric approach to approximate computing called data subsetting that shifts the focus of approximation from computations to data. The key idea is to restrict the application's data accesses to a subset of its elements so that the overall memory footprint becomes smaller. Constraining the accesses to lie within a smaller memory footprint renders the memory accesses more cache-friendly, thereby improving performance. This thesis presents a C++ data structure template called SubsettableTensor — which embodies mechanisms to define an accessible subset of data and redirect accesses away from non-subset elements — for realizing data subsetting in SW. The proposed concept is evaluated on parallel SW implementations of 7 machine learning applications on a 48-core AMD Opteron server. Experimental results indicate that  $1.33 \times -4.44 \times$  performance improvement can be achieved within a <0.5% loss in classification accuracy.

In summary, the proposed approximation techniques have shown significant efficiency improvements for various machine learning applications in circuits, architecture and SW, underscoring their promise as designer-friendly approaches to approximate computing.

### 1. INTRODUCTION

The development and wide-spread adoption of various computing devices that generate data, from mobile phones to Internet-of-Things (IoT) devices, have led to the emergence of applications that analyze and process large amounts of data to produce human-interpretable outputs. These emerging applications which include multimedia processing, machine learning, search and data analytics among others pervade into our everyday lives. While the evolution of these emerging applications demands more and more computing power to produce better-quality outputs within a reasonable time, the efficiency improvement due to technology scaling has been diminishing [1]. The challenge of this efficiency gap has forced both academia and industry to explore new directions for computing system performance and energy efficiency improvement.

Meanwhile, these prevalent emerging workloads possess a unique characteristic called *intrinsic application resilience* which enables them to produce an acceptable-quality output — a degradation in output quality which the user doesn't notice or can tolerate — despite their underlying computations being performed in an approximate manner. Intrinsic application resilience is associated with certain attributes of these applications, such as:

- A golden output doesn't exist, as is often the case in web search.

- Self-healing nature of iterative algorithms where an error introduced in one iteration eventually gets cancelled out during subsequent iterations.

- The fact that these applications including Deep Neural Networks (DNNs) are built to be robust to noisy and redundant real-world inputs.

- Limited capabilities of human perception, which allows some quality degradation without the user noticing it.

From the user's perspective, the expected result of these applications is not a unique golden numerical answer. Rather, the user expects a result of sufficient quality — in other words, an output that is "good-enough" — as depicted in Fig. 1.1. The fact that the users of these applications are satisfied with good-enough results, along with the intrinsic application

resilience possessed by these applications, has led to an emerging design paradigm called approximate computing.

Figure 1.1. Modern applications producing good-enough answers

### 1.1 Approximate Computing

Approximate computing has risen as a new design paradigm that seeks the source of efficiency from designing SW/HW computing platforms in a way that they require just the minimum amount of effort (in terms of time, energy, or area) in order to produce "good enough" results. Approximate computing exploits intrinsic application resilience [2] by intentionally relaxing the notion of "exactness" or "correctness" on selected computations so that they are executed in a more efficient manner. Fig. 1.2 shows how approximate computing can be integrated into the traditional design process, which maps the functional specification of an application into software and the underlying hardware across multiple layers of design abstraction (e.g., architecture, circuit and layout). While the traditional design process requires exact Boolean equivalence between the implementations in different layers of abstraction, approximate computing allows relaxation of the exactness requirement

so that a more efficient implementation is possible as long as the final output quality meets the given quality specification.

Figure 1.2. Approximate computing across the layers of abstraction [3]

Over the last decade, approximate computing has gained a significant interest among the research community due to the ample opportunity for efficiency improvement it provides. As a result, a large volume of approximate computing techniques spanning circuits, architecture, and software have been proposed. Despite the surge of approximation techniques, approximate computing is yet to be incorporated into mainstream HW/SW design practices. This thesis finds two main disadvantages of most existing approximate computing techniques that hinder them from being widely adopted:

Deviation from the conventional design flow. In case of HW design, most prior efforts have focused on approximation at the circuit or logic level of abstraction [4]–[15]. However, Register Transfer Level (RTL) is the most common layer of abstraction at which HW designs are specified and application-level output quality is addressed. In case of architecture design, many previous efforts have targeted specialized architectures such as domain-specific processors [16], GPUs [17], or custom accelerators [18], [19]. However, from the SW designer's point of view, utilizing specialized architectures itself requires a significant transformation

of the existing code with architectural knowledge. In case of SW design, many existing techniques require specialized HW and custom compilers making them difficult to adopt in practice [20]–[23].

Lack of runtime approximation controllability by the user. The user may often require the ability to take control over the degree or extent of approximation during runtime. However, most HW techniques hardwire approximations to the circuit implementation so that the degree of approximation is fixed [4]–[14]. SW techniques that rely on this type of underlying approximate HW also lack runtime controllability [20]–[23].

### 1.2 Thesis Contributions

The contribution of this thesis lies in exploring approximate computing techniques across different layers of abstraction that overcome the aforementioned limitations of prior works. Specifically, this thesis focuses on developing techniques that can be applied with minimal change to the conventional design flow, and are runtime configurable by the user with minimal overhead. This thesis suggests that re-thinking approximate computing from this perspective has a potential to take it closer to the mainstream. Towards this end, the thesis proposes three novel approximate computing techniques — clock overgating, which targets HW design at the Register Transfer Level (RTL), value similarity extensions, which enhances general-purpose processors with a set of microarchitectural and ISA extensions, and data subsetting, which targets SW design for commodity platforms.

### 1.2.1 Approximate Circuit Design using Clock Overgating

Clock overgating extends the concept of conventional clock gating into an approximate computing context. Clock gating is a low-power technique that turns off the clock to a Flip-Flop (FF) when the FF state remains unchanged. It is widely used in industry design practices and supported by most EDA tools which detect clock-enable conditions from the RTL code. While the traditional clock gating condition is confined in order to ensure the identical circuit functionality, clock overgating relaxes the gating condition to the point where the circuit functionality can be affected by the erroneous FF state. This saves switching

power in the clock tree, the target FF, and its downstream combinational logic at the cost of a possible quality loss in case the erroneous FF state propagates to the circuit output. The proposed technique enables approximation by modifying the clock gating conditions in the circuit's RTL description. This allows seamless integration into the existing design flow which typically starts from the RTL. In addition, approximation can be controlled in runtime by selecting the gating condition from multiple candidates. This thesis provides a systematic methodology to identify an energy-efficient clock overgating configuration for any given circuit and quality constraint is developed. The main challenge in identifying an optimal clock overgating configuration is that the number of candidate configurations to be evaluated grow exponentially with respect to the circuit size. In order to address this challenge, 3 key strategies for efficiently pruning the large space of possible overgating configurations are proposed — significance-based overgating, grouping FFs into overgating islands, and utilizing internal signals of the circuit as triggers for overgating. For a suite of 6 machine learning accelerators, energy benefits of 1.36× on average is achieved at the cost of a negligible (<0.5%) loss in classification accuracy.

## 1.2.2 Value Similarity Extensions for Approximate Computing in General-Purpose Processors

VSX (Value Similarity eXtensions for general-purpose processors) provides a set of microarchitectural and ISA extensions that exploits value similarity present in data structures for performance improvement. The key idea behind VSX is to dynamically detect and skip instructions that produce similar results to a previous one. In order to realize this approach, VSX must be able to identify potentially skippable instructions, dynamically detect an instruction result's similarity before execution, and approximate skipped instruction's result with a previous one. Towards this end, this thesis develops 3 key strategies for VSX — identifying potentially skippable instructions from user annotation in SW, obtaining similarity information for future load values from the data cache line currently being accessed, and providing a mechanism for saving & reusing results of potentially skippable instructions. As a further optimization, this thesis proposes iteration fast-forwarding, wherein multiple loop iterations producing similar results are substituted by a specialized sequence of instructions.

This thesis models VSX microarchitectural extensions on the gem5 simulator and runs 6 machine-learning benchmarks with real-word datasets on a low-end in-order processor platform. Speedups of  $1.19\times-3.84\times$  ( $1.81\times$  on average) are achieved across the benchmarks within a tight output quality constraint (<0.5%) while incurring a small HW area overhead (2.13%).

### 1.2.3 Data Subsetting: A Data-Centric Approach to Approximate Computing

The third body of work in this thesis shifts the focus of approximation from computations to data, and proposes a data-centric approach to approximate computing called data subsetting. The key idea is to modulate the application's data accesses in a manner that reduces off-chip traffic. Specifically, all accesses to data elements outside the selected subset are redirected to a subset element so that the overall memory footprint is reduced. Constraining the accesses to lie within a smaller memory footprint renders the memory accesses more cache-friendly, thereby improving performance. This approach allows approximations (access redirections) to be applied to the target SW code which eliminates the need for an approximate HW and a custom compiler. In addition, the degree of approximation can be dynamically reconfigured by adjusting the size and the redirection policy. This thesis presents a C++ data structure template called SubsettableTensor which can be used for realizing data subsetting in SW design. SubsettableTensor embodies mechanisms to define an accessible subset of data and redirect accesses to non-subset elements. As a further optimization, the thesis observes that data subsetting may cause some computations to become redundant and propose a mechanism for application software to identify and eliminate such computations. The proposed technique is evaluated by applying SubsettableTensor to parallel SW implementations of 7 machine learning applications on a 48-core AMD Opteron server. Experimental results indicate that  $1.33 \times -4.44 \times$  performance improvement can be achieved within a <0.5% loss in classification accuracy.

### 1.3 Thesis Organization

The rest of this thesis is organized as follows. Chapter 2 presents a brief overview of the prior efforts in approximate computing classified into their target layers of abstraction. Chapter 3 describes the concept of clock overgating and the proposed systematic methodology for design approximate circuits using clock overgating. Chapter 4 describes how VSX exploits value similarity for performance improvement and the details of the micro-architectural and ISA extensions. Chapter 5 describes the concept of data subsetting and how it is applied to existing SW code for real-world applications. Finally, Chapter 6 concludes this thesis.

### 2. RELATED WORK

Approximating computing is a vibrant area of research and prior efforts have proposed approximation techniques spanning the different layers of the computing stack [1], [24], [25]. This chapter presents an overview of such efforts and highlight the key distinguishing features of the thesis.

### 2.1 Circuit Design Techniques for Approximate Computing

Research on approximate circuits began with manual designs of basic arithmetic components such as adders [4]–[8], [26]–[31] and multipliers [8], [9]. Approximate design techniques such as voltage overscaling [10], [11], [32]–[34], truncating carry chains [6], and input operand partitioning [7] were proposed in this context. Modifying the Boolean function realized by the circuit to reduce logic complexity was proposed as an approach to approximate circuit design in [12]. Subsequent efforts broadened this concept to the approximate design of arbitrary circuits using techniques such as redundancy propagation [13], path pruning [14], and don't care based simplification [15], substitution [35], logic isolation [36] among others. [37] provides error modeling and analysis on the approximate circuits. All of the above efforts operate at the logic level of abstraction, and target the design of approximate combinational circuits. How such approximate circuit blocks should be composed to form larger designs remains an open challenge. Chapter 3 proposes an approximate circuit design methodology at RTL, which is a higher level of abstraction targeting larger circuits with both combinational and sequential logic.

### 2.2 Architectures for Approximate Computing

At the architecture level, research efforts build approximate architectures both in the context of application-specific designs and programmable processors. Means of approximation came from various sources as operating at sub-threshold voltage [38], stochastic processing [39], underlying approximate HW [20], [22], [40]–[60] or quality-configurable vector processing unit [16] where compiler support is provided for mapping variables/operations in

SW to their corresponding approximate HW storage/computation components. While the majority of existing techniques target only the execution pipeline stage, Chapter 4 proposes a technique which increases the efficiency of instruction fetch and decode as well.

### 2.3 Software Techniques for Approximate Computing

The majority of SW works in approximate computing have focused on providing programming language/compiler support for approximating internal computations/functions, that are categorized as compute-centric approaches. One branch of compute-centric approach maps computations/functions onto approximate HW[20]–[22], [41], [61]–[66], neural network[23], user-defined approximate loops/functions[67], approximate kernels for commonly used data parallel computation patterns[68], piecewise polynomial approximation of the target function[69], or a computational model which increases the output quality over time[70]. Another branch of compute-centric approach judiciously skips loop iterations[71], [72], atomic instructions[73], tasks[74] or critical sections[75]. In contrast to the aforementioned compute-centric approaches, Chapter 5 proposes a data-centric approach to AxC. As opposed to approximating computations, Chapter 5 targets modulating data structure accesses in a manner that reduces memory bandwidth, thereby speeding-up applications executed on memory-bound platforms.

Another category of approximate SW work targets multi-threaded programs and achieve approximation by relaxing dependencies or synchronization constraints. [76] immediately terminates the current phase on all processors when the majority of them are in idle condition. [77] forces the threads in a SIMD execution to take the same control path or read from the same memory block. [75], [78] proposes a parallelizing compiler and runtime which provides control knobs for relaxing inter-loop dependencies and synchronizations. While these works are orthogonal to the approach proposed in Chapter 5, the proposed approach for mitigating memory bottleneck is especially effective in multi-threaded environments, thus can be used in complementary to each other.

# 3. APPROXIMATE CIRCUIT DESIGN USING CLOCK OVERGATING

#### 3.1 Introduction

Many prevalent and emerging application domains such as multimedia, recognition, mining, data analytics, search and vision among others, possess the characteristic of *intrinsic application resilience*, which enables them to produce outputs of acceptable quality, despite approximations to some of their computations. Intrinsic application resilience arises from several factors: algorithms are designed to be robust to noise, input data contains redundancies, applications only need to produce an acceptable output rather than a unique golden result, *etc.* [24], [79]. Approximate computing leverages intrinsic application resilience and relaxes the need for strict correctness in the execution of computations to improve energy and/or performance.

Over the last decade, several research efforts have developed techniques for approximate computing in both software [24], [71] and hardware [4]–[15], [80]–[83]. Approximate hardware may be realized by operating circuits under overscaled conditions [10], [11] (e.g., lowering the voltage to a point where timing errors occur), or by designing hardware that contains fewer transistors or gates but deviates to a limited extent from the specification [4]–[9], [12]–[15], [80], [81]. A vast majority of approximate hardware design techniques are at the circuit or logic levels of abstraction. It is desirable to explore approximate design at the higher levels of abstraction, since from the designer's point of view, quality is most naturally defined and evaluated at the application level. For example, it is much more natural to talk about classification accuracy or image quality than to specify accuracy or error constraints at the outputs of individual adders or multipliers within a circuit.

The Register Transfer Level (RTL) remains the most common level of abstraction at which hardware designs are specified in the industry. In addition to inherent advantages in terms of faster simulation and analysis times, RTL descriptions contain higher-level semantic information (data types, bit positions, operators, etc.) that can be leveraged in the process of approximation.

Very few research efforts have previously investigated approximate computing at the RTL. Notably, Axilog [83] proposes Verilog HDL extensions that designers can use to specify which signals and operations in the RTL code can be subject to approximations. In contrast, this chapter's objective is to develop a new approximate design technique, and hence Axilog [83] is complementary to this chapter's proposal. Another effort, ABACUS [82], generates approximate designs from behavioral/RTL descriptions by applying pre-specified approximation transformations to individual operations or operands. A key drawback of this approach is that the approximations are fixed at design time and hardwired into the circuit implementation. This is an issue in practice, since the same hardware may be used to execute computations that can tolerate different levels of approximation, or the application context may dictate the use of different accuracies for the same computation. These considerations strongly suggest that the approximations employed should be reconfigurable at runtime.

This chapter proposes a new approximation technique called *clock overgating* for the design of approximate hardware. Clock gating is one of the most widely adopted low-power techniques, in which clock signals to sequential elements (flip-flops or latches) in the circuit are suppressed to reduce power, provided that doing so preserves the exact functionality of the circuit. This chapter extends this concept to propose clock overgating, where the clock signal to a Flip-Flop (FF) is gated *even when doing so may affect the circuit outputs*. Clock overgating may result in incorrect outputs when an FF is supposed to change state but incorrectly retains its previous state, and this error propagates to the circuit outputs. In return, switching power is saved in the clock tree, the FF itself, and the fanout logic cone of the FF. Note that these power savings are over-and-above the savings due to conventional clock gating and other low-power techniques.

Clock overgating has the following desirable properties: (i) It is easily reconfigurable, *i.e.*, the clock overgating signal to each FF can be modulated dynamically in a fine-grained manner, (ii) it preserves the structure of the circuit and is hence minimally-intrusive, and (iii) it leverages the wide support for clock gating that is present in commercial EDA tools and design flows.

Given the RTL description of a circuit, an input testbench and an output quality constraint, this chapter proposes a systematic methodology to identify where (in which FFs) and when (in which clock cycles) to perform overgating. The search space for overgating, defined by all possible FFs and all possible execution cycles, is extremely large (e.g., 2<sup>10000</sup> for a circuit with 100 FFs that operates for 100 cycles), and is even more challenging in cases when designs take a variable number of cycles to complete execution. Rather than explicitly search through this prohibitively large space, the proposed methodology utilizes internal signals from the circuit to trigger clock overgating. Doing so restricts the search space, and also has the added benefit of incurring minimal overhead in the logic that realizes the overgating conditions. Further, FFs in a circuit are grouped into clock overgating islands based on their location in the circuit and how they impact the overall application output. FFs in each overgating island are constrained to have the same overgating condition, greatly reducing the search space without significantly affecting the energy savings from overgating. Then a gradient descent search is performed to identify the set of clock overgating island–trigger signal combinations that maximize the improvement in energy for the specified quality constraint.

In summary, the key contributions of this work are as follows:

- This chapter proposes clock overgating, a new technique to design approximate circuits at the RTL, in which sequential elements in the circuit are clock gated even when doing so may affect the circuit outputs.

- This chapter develops a systematic methodology to determine the clock overgating

conditions for sequential elements in any given circuit. The proposed methodology

groups sequential elements into overgating islands and uses internal circuit signals as

overgating triggers to efficiently prune the space of possible overgating configurations.

- This chapter applies clock overgating to develop approximate versions of accelerators for 6 machine learning applications, and demonstrate 1.36× average improvement in energy for <0.5% loss in quality at the application-level.

### 3.2 Comparison to Related Work

Section 2.1 presented various research efforts on approximate circuit design and emphasized their limitations where the approximation target is restricted to combinational circuits

and performs approximation at the logic level of abstraction. In contrast to the aforementioned efforts, this chapter focuses on a higher level of abstraction, viz. RTL, where very few efforts have explored approximate computing. Axilog [83] provides Verilog HDL extensions, which can be used to specify and identify portions of the design that are safe to approximate. Axilog is complementary to this work as this work's objective is to develop new approximate design techniques that can be applied to the identified parts. ABACUS [82] applies predefined approximate transformations (e.g., scaling bitwidth, strength reduction) to operators in the RTL description. However, a key limitation of [82] is that the approximations are hardwired into the circuit implementation, and cannot be changed at runtime. In practice, hardware needs to be re-used in different application contexts, operate on different inputs, or execute different operations within an application; all these scenarios require the ability to modulate the degree of approximation at runtime. Clock overgating is inherently quality configurable, since one can enable overgating in different subsets of FFs to realize distinct energy vs. quality tradeoffs. Furthermore, it has other desirable attributes such as preserving the overall structure of the circuit and can be easily integrated into existing design flows. Finally, recent work has explored High-Level Synthesis (HLS) of approximate circuits through precision scaling [81]. Notwithstanding significant advances in HLS, it is noted that hardware is often still designed at the RTL in the industry, hence this chapter focuses on the complementary problem of approximating any given RTL design in a quality-configurable manner.

### 3.3 Background

### 3.3.1 Power Dissipation in Sequential Circuits

The average power dissipated in a sequential circuit can be broken down into is major components as:

$$P_{average} = P_{leakage} + P_{dynamic} \tag{3.1}$$

$P_{leakage}$  mainly comes from sub-threshold currents and they contribute to the average power dissipation even when there are no switching activities. The portion of  $P_{leakage}$  with

respect to  $P_{average}$  increases as the transistor size becomes smaller. On the other hand,  $P_{dynamic}$  is caused by switching activities of each node, where the load capacitance needs to be charged.  $P_{dynamic}$  can be represented as:

$$P_{dynamic} = \alpha \cdot C_L \cdot V_{DD}^2 \cdot f \tag{3.2}$$

Where  $\alpha$  being the fraction of the circuit that is switching switching,  $C_L$  being the load capacitance,  $V_{DD}$  being the supply voltage, and f being the operation frequency. The part of a circuit where  $P_{dynamic}$  becomes dominant is the clock tree, where the input clock is constantly switching while the circuit is powered on.

### 3.3.2 Clock Gating

Figure 3.1. Different types of clock gating logic

As mentioned in Section 3.3.1, clock power occupies a significant fraction of the total dynamic power dissipation since the clock is fed to every circuit block where sequential logic elements (e.g., flip-flops) are present. Clock gating is a wide-spread lower-power technique which targets clock power. The key concept of clock gating is to turn off the clock to a Flip-Flop (FF) when the FF state does not change. Gating conditions can be explicitly specified by the user (explicit load-enable condition), or can be derived by comparing the next cycle's input to the current state (XOR-based approach). Fig. 3.1 shows different types

of clock gating logics which are widely used. In contrast to Fig. 3.1(a) where the CLK signal is directly fed to the target FF, Fig. 3.1(b) gates CLK with an EN signal and an AND gate so that the input clock to the FF doesn't switch when EN is low. Fig. 3.1(c) is an advanced type of clock gating logic (latch-based) where glitches to EN does not affect the functionality of the target FF. Clock overgating technique presented in Chapter 3 extends the conventional duration of EN so that the clock remains gated for a longer amount of time while the FF state becomes erroneous. The selection of EN for each FF is judiciously made through a systematic methodology so that each FF is gated longer while minimizing the effect on the final output.

### 3.4 Design Approach

Given a hardware design described at the RTL and a quality constraint specified at its outputs, this chapter's objective is to design an approximate version through clock overgating that is as energy-efficient as possible, while meeting the specified quality constraints. This section describes the basic concepts behind clock overgating, the challenges involved in applying it to the design of approximate circuits, and this chapter's approach to addressing these challenges.

### 3.4.1 Clock Overgating: Concept

Clock gating is a popular low-power design technique that is widely used to reduce dynamic power dissipation. In clock gating, additional logic is embedded in the clock tree of the circuit, which suppresses the clock signal transitions from reaching one or more sequential elements (FFs or latches) in the circuit under certain conditions. Since the clock signal is suppressed, the target FFs cannot switch states and therefore switching power is saved in the clock tree leading to the FFs, the FFs themselves and their fanout logic cones. To preserve functionality, clock gating is performed only when an FF's state is guaranteed not to switch, or if it can be proven that the circuit's outputs are insensitive to the FF's inputs in the gated execution cycles.

Figure 3.2. Clock overgating concept

This chapter proposes clock overgating, whose concept is illustrated in Fig. 3.2. In clock overgating, selected FFs in the circuit are gated even when doing so may result in an incorrect circuit output. In other words, local errors are introduced in the circuit due to incorrect FF states, and they may propagate to the circuit output, potentially causing the output quality to degrade. In return, since FFs are being gated for additional execution cycles beyond conventional clock gating, it results in improved dynamic power and energy. Thus, clock overgating presents designers with a means to tradeoff energy vs. quality. The key question that arises, which will be discussed next, is how to utilize clock overgating to achieve the best energy benefit for a given output quality?

### 3.4.2 Clock Overgating: Design Space

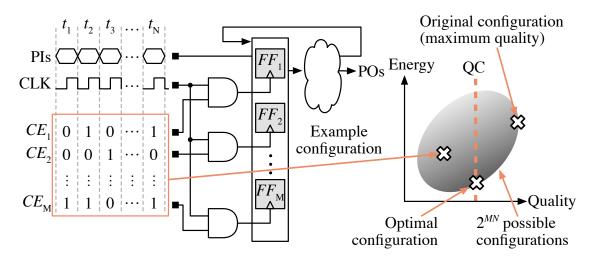

Identifying a *clock overgating configuration* involves defining: (i) which FFs in the circuit should be overgated, and (ii) when (during which clock cycles) the selected FFs should be overgated, or in other words, what conditions should be used to trigger overgating for the selected FFs. This chapter refers to the FFs that are candidates for overgating as Clock Overgating Targets (COTs), and the signals used to trigger clock overgating in them as Clock Overgating Enables (COEs). Fig. 3.3 shows the design space for clock overgating.

If M is the number of FFs in a circuit, which operates for N cycles, then each FF can be either gated or active in each cycle, leading to a total of  $2^{M*N}$  overgating configurations. Clearly, a brute force search of all possible overgating configurations is infeasible for practical designs. Therefore, efficient heuristics are key to exploring this very large design space and to identifying the clock overgating configuration that is most energy-efficient for a given output quality constraint (QC).

Figure 3.3. Design space of clock overgating configurations

To address the above challenge, this chapter adopts 3 strategies that leverage the semantic information available at the RTL to significantly reduce the number of COTs as well as the number of possible COEs for each COT. Although these strategies do not guarantee optimality, *i.e.*, they may result in a suboptimal overgating configuration, this chapter's experimental results demonstrate that they work well in practice and yield significant improvements in energy even for very tight quality constraints.

Significance constrained overgating: In general, each FF in the circuit can be regarded as a COT and overgated independently. However, in practice, multiple FFs are semantically grouped into registers that together store/represent multi-bit data. This chapter extracts this information from the RTL description of the circuit and exploits the bit significance of individual FFs in their respective registers to constrain the sequence in which they are overgated. In typical circuits, errors in the LSBs of registers impact the output quality by

an exponentially smaller amount relative to the MSBs. Further, the LSBs typically have the most switching activity and fan out to larger cones of logic; hence, they can lead to higher energy savings when overgated. Therefore, identification of COEs for FFs in a given register is proceeded in the order of their bit significance, *i.e.*, COEs for the LSBs are identified first before considering the MSBs for overgating. In summary, the first strategy prunes the search space by associating FFs with registers specified at the RTL, and constraining the manner in which they are overgated based on bit-significance.

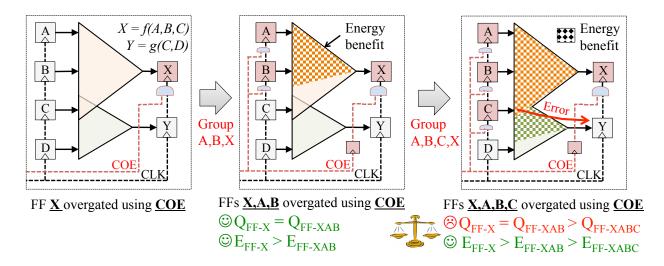

Figure 3.4. Functional grouping of FFs

Functional grouping of FFs: In this strategy, this chapter reduces the number of COTs by grouping multiple FFs into overgating islands, and overgating all FFs in an island together. This is achieved by leveraging the functional relationship between FFs that can be easily identified at the RTL. Fig. 3.4 illustrates the opportunity for FF grouping. Consider a scenario where clock overgating in FF X is triggered by signal COE. This enables energy savings in X and in its downstream logic. Now, as shown in Fig. 3.4, X is functionally related to FFs A, B and C i.e. X changes state only in response to a change in A, B or C. Also, note that FFs A and B exclusively fan out to X, whereas C also fans out to other FFs in the circuit. In this case, the key observation is that when COE is used to clock overgate FFs A and B in the cycle before X is overgated, it results in no additional quality loss at the circuit outputs, as any errors introduced at A and B propagate only to X, which itself

is overgated in the next cycle. However, this results in additional energy savings in the FFs A and B, and in the combinational logic connecting FFs A and B with X. Therefore, this chapter groups FFs X, A and B into a single overgating island, and uses the same signal (COE) to overgate all of them. Note that when grouped, the overgating signal to X is delayed by one clock cycle, as the values in A and B propagate to X only after a cycle.

The above strategy can be extended to include an FF in a group even when some of its fanouts lie outside the group. In this case, grouping may result in additional quality degradation, as errors introduced in the FFs due to overgating can propagate to the circuit outputs through its fanouts that lie outside the island. In the example shown in Fig. 3.4, if C is grouped along with X, A and B, the error introduced in C impacts its fanouts other than X, leading to an additional degradation in quality. This additional quality degradation needs to be compared against the net energy benefits to decide if it is favorable to add an FF to an overgating island. A detailed description of how FFs are grouped into overgating islands is presented in Section 3.5.

Using internal signals as COEs: The final strategy addresses the large space of possible COE candidates that could be used to trigger overgating in each COT. Since logic to generate COEs needs to be added to the circuit, a key constraint in picking COEs is that they should incur low overhead. To reduce the search space, while also minimizing the energy overheads in the logic that generates COEs, this chapter proposes to use internal signals already present within the circuit as COEs. In addition, to ensure that the timing constraints on the gating signal are satisfied, and that no glitches are introduced on the gated clock signals, this chapter further restricts COEs to be the outputs of FFs in the circuit and their complements. While this restriction greatly prunes the design space, this chapter's experiments suggest that it still enables a rich and favorable energy-quality tradeoff. This chapter suggests that in practice, circuits contain control states such as address counters, FSM state variables etc. that naturally predict which registers in the circuit are active and likely to affect the output the most.

In summary, this chapter proposes clock overgating, an RTL approximation technique in which clock signals to FFs in a circuit are gated even when the circuit outputs may be affected, thereby resulting in a tradeoff between energy and output quality. This chapter also proposes three key strategies to prune the space of possible overgating configurations, enabling clock overgating to be applied to any given input circuit while meeting the desired quality constraint.

### 3.5 Design Methodology

This section presents a systematic methodology for clock overgating that realizes the design approach described in Section 3.4.

### 3.5.1 Approximate Design using Clock Overgating

```

Algorithm 1 Approximate design using clock overgating

Input: Original circuit Ckt_{orig},

Application dataset AppData, Quality constraint QC

Output: Approximate circuit Ckt_{app}

1: COT_{List} = \text{form\_COTs}(Ckt_{orig})

2: COT_{subList} = select COTs in LSB position from COT_{List}

3: COE_{List} = FFs and their complements in Ckt_{orig}

4: Ckt_{opt} = Ckt_{orig} with COE=0 \ \forall \ COTs in COT_{List}

5: do

Ckt_{app} = Ckt_{opt}; FOM_{opt} = 0

6:

COT\text{-}COE_{List} = \{ \langle T,E \rangle \mid T \in COT_{subList}, E \in COE_{List} \}

7:

for each \langle COT, COE \rangle in COT-COE_{List} do

8:

Ckt_{tmp}=assign COE as ovg. signal for COT in Ckt_{app}

9:

\Delta E = E_{orig} - get_energy(Ckt_{tmp}, AppData)

10:

11:

\Delta Q = Q_{orig} - get_quality(Ckt_{tmp}, AppData)

FOM = \Delta E/\Delta Q

12:

if (\Delta E > 0 and \Delta Q < QC and FOM > FOM_{opt}) then

13:

COT_{opt} = COT; COE_{opt} = COE

14:

Ckt_{opt} = Ckt_{tmp}; FOM_{opt} = FOM

15:

end if

16:

17:

end for

18:

remove COT_{opt} from COT_{subList}

COT_{subList} = add \ COT \ containing \ next \ significant \ bit

19:

of COT_{opt} from COT_{List}

20: while (Ckt_{app} \neq Ckt_{opt})

21: return Ckt_{app}

```

Algorithm 1 shows the pseudocode of the proposed methodology. Given the original circuit ( $Ckt_{orig}$ ), an input dataset (AppData), and a constraint on the output quality (QC), the algorithm produces an energy-efficient approximate version ( $Ckt_{app}$ ) that is clock overgated and satisfies the specified quality constraint. First, a list of possible clock overgating targets ( $COT_{List}$ ) and clock overgating enables ( $COE_{List}$ ) are formed by employing the different design space pruning strategies described in Section 3.4 (lines 1-3). To this end, the FF grouping strategy is first used to form the  $COT_{List}$  (line 1). The details of this process are explained in Algorithm 2. Next, the significance constrained overgating strategy is used to further reduce the list of COTs (resulting in  $COT_{subList}$ ). In this case, only the COTs that are in the least significant bit positions in their corresponding registers are chosen from  $COT_{List}$ , and added to  $COT_{subList}$  (line 2). Next, since only FF outputs and their complements are considered as possible clock gating enables,  $COE_{List}$  is initialized with all FFs and their complements in the circuit (line 3).

Despite significantly reducing the design space using the various strategies, trying out all possible COT-COE combinations becomes computationally expensive for larger circuits. Therefore, this chapter adopts a gradient descent approach (lines 5-20), where in each iteration the COT-COE pair that yields the best energy vs. quality tradeoff without violating QC is selected. To this end, this chapter first initializes the COE for each COT to logic 0, which corresponds to no overgating (line 4). Then, this chapter forms a list of all possible COT-COE pairs  $(COT\text{-}COE_{List})$  by pairing each COT in  $COT_{subList}$  with each COE in  $COE_{List}$ (line 7). Next, for each COT-COE pair this chapter forms a candidate overgated circuit by assigning the COE under consideration as the overgating signal for the COT (line 9). Subsequently, this chapter evaluates the energy benefits (line 10) and the corresponding quality loss (line 11). Note that COT-COE pairs that cause unacceptable quality degradation are captured during quality evaluation and filtered out from further COT- $COE_{List}$  formations. This chapter then computes a figure of merit (FOM) for each COT-COE pair, which is given by the ratio of energy saved to quality lost (line 12). This chapter identifies the COT-COE pair that has the best FOM (lines 13-16) and updates the approximate circuit by "committing" the COE to the COT (line 15). The committed COT is removed from  $COT_{subList}$  (line 18), and the COT containing the next significant bit position is added to  $COT_{subList}$  (line 19). This process is repeated until no COT-COE pair yields further improvements in energy without violating QC (line 20), at which point the algorithm terminates and returns the approximate circuit (line 21).

## 3.5.2 Identifying Clock Overgating Candidates

#### **Algorithm 2** Identify overgating candidates

```

Input: Original circuit Ckt, Application dataset AppData

Output: Clock overgating candidate list: COT_{List}

1: COT_{List} = FFs \text{ in } Ckt

2: G = \text{create\_FF\_connection\_graph}(Ckt)

3: W = \text{get RTL simulation waveform}(Ckt, AppData)

4: TSC(FF_1,FF_2): temporal correlation between FF_1\&FF_2 in W

5: do

6:

for each COT in COT_{List} do

for each COT_{In} in fan-in(COT,G) do

7:

for each COT_{In-out} in fan-out (COT_{In},G) do

8:

TSC_{tmp} = TSC(COT_{In}, COT_{In-out})

9:

\Delta E_{local} += TSC_{tmp} \times \text{fan-out-size}(COT_{In}, COT_{In-out})

10:

if (COT_{In-out} \neq COT) then \Delta Q_{local} += TSC_{tmp}

11:

end for

12:

13:

if (\Delta E_{local}/\Delta Q_{local} > \eta) then

COT_{List} = merge(COT, COT_{In})

14:

15:

end for

16:

end for

17:

18: while (COT_{List} modified?)

19: return COT_{List}

```

Algorithm 2 presents the methodology used to obtain the list of clock overgating candidates in line 1 of Algorithm 1. Algorithm 2 essentially implements the FF grouping strategy presented in Section 3.4. First,  $COT_{List}$  is initialized to contain all the FFs in Ckt (line 1). Then  $COT_{List}$  is reduced by grouping FFs whose switching activities are highly correlated (lines 2-18). To this end, a FF connection graph (G), whose vertices represent the FFs and whose edges represent a combinational path between two FFs, is constructed from the RTL code (line 2). Then, the circuit RTL is simulated with the given dataset, and the switching

activity of each FF is recorded (line 3). Subsequently, the degree of 1-cycle temporal switching correlation (TSC) between FF pairs that have an edge connecting them in G is computed (line 4). This chapter denotes two FFs to be temporally correlated if they are likely to switch in successive cycles. Next, for each COT and its fan-in ( $COT_{In}$ ), this chapter computes the local energy savings expected in all the fan-outs of  $COT_{In}$  if it is overgated along with COT (line 10). Similarly, this chapter evaluates the local errors expected in the fan-outs of  $COT_{In}$  that are not contained within COT, assuming that  $COT_{In}$  is overgated along with COT (line 11). This chapter merges  $COT_{In}$  with COT if the ratio of the local energy savings to the local error induced is greater than a threshold  $\eta$  (lines 13-15). In this chapter's implementation, the value of  $\eta$  is determined empirically as discussed in Section 3.7.3. This process is repeated until no pair of candidates in  $COT_{List}$  can be merged (line 18), and the final  $COT_{List}$  is produced (line 19).

## 3.6 Experimental Setup

This section describes the experimental setup used to evaluate clock overgating.

#### 3.6.1 Benchmarks

The benchmark circuits consist of algorithm-specific hardware accelerators for 6 popular machine learning applications listed in Table 5.1. Classification accuracy, or the fraction of application inputs correctly classified, was used as the measure of output quality for all the benchmarks. Separate datasets were used for training and testing/validation, and the same testing dataset was used to evaluate the original and approximate circuits.

## 3.6.2 Quality and Power Evaluation

The design methodology and heuristics described in Section 3.5 were implemented as a custom script that executes the following design flow. First, a custom RTL parser extracts necessary information from the input RTL code and produces an approximate version. The output quality (classification accuracy) of the approximate circuit is obtained by RTL simulation with the testing dataset using Mentor Graphics ModelSim. RTL simulation also

Table 3.1. Benchmark applications

| Algorithm | Application                        | Dataset        | FFs/Gates   |

|-----------|------------------------------------|----------------|-------------|

| GLVQ      | Eye detection (EYE)                | Image set from | 183 / 3100  |

|           |                                    | NEC labs       |             |

| KNN       | Optical digit classification (OPT) | OCR digits     | 344 / 4128  |

|           | Webpage classification (W5A)       | LIBSVM         | 422 / 7348  |

| SVM       | Text classification (TEXT)         | Reuters        | 480 / 27760 |

| ANN       | Digit classification (DIGT)        | MNIST          | 398 / 29833 |

|           | Face detection (FACE)              | YUV faces      | 394 / 31428 |

produces the switching activity information that is used for power estimation. Power is estimated by synthesizing the approximate circuit to IBM 45nm technology using Synopsys Design Compiler, and estimating the circuit power including the clock tree power using Synopsys PrimeTime. This chapter notes that the most aggressive optimization options available by Synopsys Design Compiler (conventional clock gating, gate sizing, use of low leakage cells, etc.) were applied to create well-optimized baselines for comparison.

## 3.7 Experimental Results

This section presents the results of various experiments that demonstrate the benefits of clock overgating and underscores the effectiveness of the proposed strategies in exploring the large design space of overgating configurations.

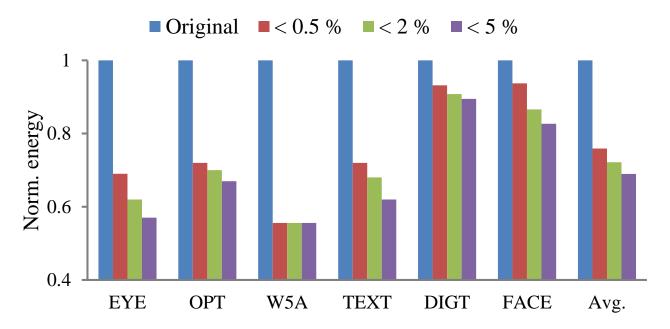

#### 3.7.1 Energy-Quality Tradeoff

Fig. 3.5 shows the energy reduction obtained using clock overgating for various output quality constraints. Note that output quality constraints are expressed in terms of classification accuracy degradation with reference to the baseline, and the energy consumption of each approximate circuit is normalized to the energy consumption of its baseline implementation. As shown in Fig. 3.5, clock overgating provides significant energy benefits between  $1.07 \times -1.80 \times (1.36 \times \text{ on average})$  at the application level with virtually no loss (<0.5%) in classification accuracy. When the quality constraints are relaxed to <2% and <5%, the

energy benefits increase to  $1.10 \times -1.80 \times (1.43 \times \text{ on average})$  and  $1.12 \times -1.80 \times (1.50 \times \text{ on average})$ , respectively.

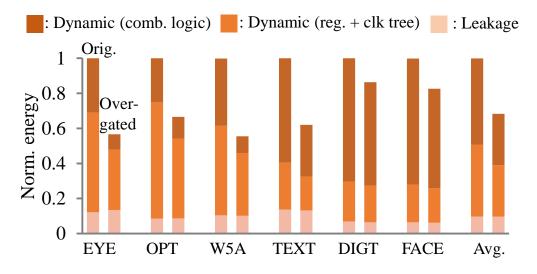

Figure 3.5. Energy improvements for various quality constraints

The graph shown in Fig. 3.6 breaks down the energy from Fig. 3.5 into 3 key components: (i) leakage (static) power, (ii) dynamic power in the registers and the clock tree, and (iii) dynamic power in the combinational logic. This section only presents the <5% quality constraint case here, but the observations hold for other cases as well. Again, all the energy components are normalized to the baseline implementation. First, this chapter finds that the overhead due to the increase in leakage power is negligible (0.21% on average). This suggests that the overhead for clock overgating was kept minimal (cell area increased by 0.28% on average) by using the internal signals as COEs. Next, it is observed that clock overgating reduces the power dissipated in the clock tree, the FFs' internal power, as well as the dynamic power consumed by the combinational logic. A general trend shown in Fig. 3.6 is that the power improvements are more pronounced in the combinational logic than in the clock tree and the FFs. This is due to the fact that only a small fraction (16.9% on average) of the total FFs are clock overgated in the design, and further, these overgated FFs are dominated by LSBs. The parts of the combinational logic that process LSBs typically

exhibit higher switching activity and therefore overgating the corresponding FFs results in considerable dynamic power savings without a significant impact on output quality.

Figure 3.6. Energy breakdown analysis

## 3.7.2 Comparison with Precision Scaling

The graph shown in Fig. 3.7 compares the energy benefits achieved by clock overgating and precision scaling for various target quality constraints. In the case of precision scaling, different numbers of LSBs were clock gated in all data path registers, throughout the evaluation of the circuit. It can be clearly seen that clock overgating outperforms precision scaling in terms of energy benefits; for example,  $1.36 \times vs$ .  $1.19 \times$  on average for a quality constraint of <0.5%. This is due to the fact that clock overgating allows for a more fine-grained control over which FFs should be gated in which execution cycles.

### 3.7.3 Effectiveness of FF Grouping

As described in Section 3.4, this chapter groups multiple FFs into overgating islands, which significantly cuts down the search space of overgating configurations. However, this renders clock overgating to be more coarse grained, potentially impacting the energy efficiency of the overgated circuit. Fig. 3.8 quantifies this tradeoff for 2 benchmarks by varying the number of COTs into which the FFs of the circuit are grouped, and observing the runtime

Figure 3.7. Energy benefits using clock overgating vs. precision scaling

of the methodology as well as the energy efficiency of the resulting overgated circuit. Note that, in Fig. 3.8, energy is normalized to that of the baseline circuit. A quality constraint of <5% classification accuracy was used in these experiments; however, the conclusions hold for other quality constraints as well. It is observed that the runtime increases with an increase in the number of COTs. In the case of energy, the benefits of clock overgating are very small when FFs are aggressively grouped. The energy efficiency of the overgated circuit improves drastically once the number of COTs crosses a threshold. However, beyond a point, the benefits saturate and very fine grained overgating does not yield additional improvements. Thus, if carried out to the right extent, FF grouping can achieve significant improvements in overall runtime, without a significant loss in the energy benefits. For instance, in the case of EYE, when its 183 FFs are grouped to form 129 COTs (using  $\eta$ =3.5 in Algorithm 2), the runtime reduces by 5.8× at the cost of a mere 1.8% decrease in energy savings. The result of this experiment shows that  $\eta$  values of 3.2–3.5 work well for all circuits. Note that by combining the strategies described in Section 3.4, the total runtime was reduced substantially to <4 hours for a circuit size of ~30K gates. While this chapter argues that this is a reasonable runtime for this chapter's proof-of-concept implementation, it can be considerably reduced by utilizing static techniques (vs. simulation) for switching activity estimation, and parallelizing across multi-cores (for example, the loop over COT-COE combinations in Algorithm 1 can be parallelized) to ensure scalability for larger circuits.

Figure 3.8. Runtime vs. optimality tradeoff analysis

## 3.7.4 Illustration of Clock Overgating in Action

Fig. 3.9 visually illustrates clock overgating in action by plotting the activity of FFs during around 1000 cycles of execution of the EYE application. In Fig. 3.9, each point on the Y axis corresponds to a distinct FF, while the X axis represents execution cycles. The color at each (x, y) coordinate indicates the status of FF y at cycle x. In a given cycle, an FF can be either active, clock gated or clock overgated, marked by blue, green and red colors respectively. Also, the length of the segment in the Y axis corresponding to each FF is proportional to the energy benefits possible by gating the FF. Therefore, the area in Fig. 3.9 occupied by the overgated regions roughly corresponds to the overall energy benefits. It is observed that only 12% of the FFs (FF index 162–183) are overgated in the circuit, but since they and the combinational logic that they feed contribute up to 50% of the total energy,  $\sim$ 40% improvement in energy is achieved.

## 3.8 Summary

The intrinsic resilience in emerging applications provides new opportunities for optimizing hardware through approximate computing. This chapter proposes clock overgating, an RTL approximation technique. The key idea behind clock overgating is to suppress the clock signal to selected FFs in the circuit even when the circuit functionality is affected as

Figure 3.9. Clock overgating status over time

a result, thereby creating a trade-off between energy and quality. A systematic methodology is developed which identifies an energy-efficient clock overgating configuration given any arbitrary circuit and output quality constraint. The methodology employs three key strategies that leverage the semantic information available at the RTL to efficiently explore the large space of overgating configurations. The results across hardware implementations for a range of machine learning algorithms suggest that clock overgating is a promising approach to approximate hardware design and that it enables favorable tradeoffs between energy and output quality.

# 4. VALUE SIMILARITY EXTENSIONS FOR APPROXIMATE COMPUTING IN GENERAL-PURPOSE PROCESSORS

#### 4.1 Introduction

In the previous decade, Approximate Computing (AxC) has emerged as a popular design paradigm that leverages the intrinsic ability of applications to tolerate approximations in some of their computations to boost compute efficiency [24], [84]. A significant fraction of prior efforts in AxC have focused on specialized architectures such as domain-specific processors [16], GPUs [17], or custom accelerators [84]–[86], while relatively limited effort has been devoted towards General-Purpose Processors (GPPs). However, modern applications that benefit from AxC are still widely executed on GPPs for various reasons, ranging from their easy programmability to stringent cost/area budgets precluding the use of custom accelerators. For example, the majority of Facebook's inference workloads run on CPUs within edge devices [87]. Hence, leveraging AxC to improve the efficiency of GPPs is of significant interest.

AxC in GPPs. A key challenge in approximating GPPs is that their execution units contribute only a small fraction of total energy. Hence, AxC in GPPs has been predominately achieved through software-level approximations such as function approximation, loop skipping, and relaxed synchronization [24], [71], [84]. The few efforts that propose hardware approximations for GPPs employ approximations either within the execution units through memoization [88], [89] and voltage scaling [39], [90], or in the memory sub-system through load value prediction [91]. The benefits from these approaches are limited by the energy expended in the parts that are not approximated, such as instruction fetch, decode, control, etc.

AxC through Value Similarity. This chapter proposes a holistic approach to AxC in GPPs that encompasses compute, memory and control front-ends. This chapter leverages the application property of value similarity, i.e., input operands to computations that occur close-in-time take similar values, thereby producing results that are similar. An analysis on six representative Machine Learning (ML) workloads indicates that value similarity is

broadly prevalent, impacting as much as 80% of the computations executed. This provides an opportunity to pre-detect similar computations and skip fetch-decode-execute of entire instruction sequences, while substituting their results with those of previously executed computations, benefiting both performance and energy. To this end, this chapter proposes VSX, a set of lightweight micro-architectural and ISA extensions to leverage value similarity in GPPs. This chapter also presents compiler techniques that leverage user annotations to benefit from VSX in the context of common ML kernels.

A key trade-off in the design of VSX is balancing the window-of-opportunity *i.e.*, the span of computations across which similarity is exploited vs. the complexity of the implementation and overheads incurred. To ease the pressure on the memory-subsystem, GPP applications are structured to maximize access locality to elements within a cache-line. This chapter leverages this observation in VSX and pre-detect similar values among elements of a cache-line when performing a load (the similarity threshold is defined by software). The pre-detected similarity information is passed to the instruction fetch unit, which skips instructions even before they enter the pipeline by appropriately controlling the program counter.

VSX provides maximum flexibility to the compiler to define which instructions are skippable under what conditions. This is critical as the impact of approximations on the overall

quality cannot be solely ascertained in hardware. To this end, the micro-architecture contains a programmable Similarity Based Skip Table that is configured before entering a code

region where value similarity can be exploited. Based on programmer annotations in the

code, the compiler generates the skip information for common ML kernels such as GEMM,

Conv2D etc. As a further optimization, VSX also supports iteration fast-forwarding, i.e.,