# FEEDBACK DRIVEN MATCHING NETWORKS FOR RADIO FREQUENCY POWER AMPLIFIERS

by

**Henry Alexander**

### A Thesis

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Master of Science**

School of Engineering Technology West Lafayette, Indiana May, 2021

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## John Denton, Chair

Electrical and Computer Engineering Technology

# **Dr. Grant Richards**

Electrical and Computer Engineering Technology

# Dr. Mark French

Mechanical Engineering Technology

# Approved by:

Dr. Duane D. Dunlap

I would like to dedicate this work to my wife.

## ACKNOWLEDGMENTS

I would like to acknowledge everyone who played a crucial role in my academic success. First of all, I would like to thank my committee chair, John Denton, for supporting me and my research endeavors. Without his instruction and trust in me, I would not be where I am today. Secondly, I would like to acknowledge the rest of my committee, Dr. Grant Richards and Dr. Mark French, for standing by me throughout the work and my academic career.

I would also like to acknowledge the fantastic people at Indiana Microelectronics LLC. for their financial help in my education and for lending me the use of their lab for my research. Specifically, I would like to thank Eric Rice, Eric Hoppenjans, and Warren Getlin for their technical support.

Without all the people and organizations listed, I could not have completed this work. Their contributions are greatly appreciated.

# TABLE OF CONTENTS

| LIST OF TABLES                                 | . 9 |

|------------------------------------------------|-----|

| LIST OF FIGURES                                | 10  |

| ABSTRACT                                       | 15  |

| CHAPTER 1. INTRODUCTION                        | 16  |

| CHAPTER 2. REVIEW OF LITERATURE                | 19  |

| 2.1 Literature Review Introduction             | 19  |

| 2.2 System and Device Impedance                | 19  |

| 2.3 Static Matching Networks                   | 20  |

| 2.3.1 Why a Matching Network                   | 21  |

| 2.3.2 What is a Matching Network               | 23  |

| 2.3.3 L Matching Network Topology and Analysis | 23  |

| 2.3.4 Cascaded L Matching Networks             | 25  |

| 2.3.5 Pi and Tee Matching Networks             | 27  |

| 2.3.6 Correcting for Complex Loads             | 32  |

| 2.3.7 Summary of Matching Networks             | 32  |

| 2.4 Power Amplifier Classification and Designs | 33  |

| 2.4.1 Parameters of a Power Amplifier          | 34  |

| 2.4.1.1 Gain                                   | 34  |

| 2.4.1.2 1dB Compression Point                  | 34  |

| 2.4.1.3 Efficiency                             | 35  |

| 2.4.1.4 Transistor Types                       | 36  |

| 2.4.1.5 Transistor Impedances                  | 38  |

| 2.4.2 Amplifier Classes                        | 38  |

| 2.4.2.1 Class A Amplifier                      | 38  |

| 2.4.2.2 Class B Amplifier                      | 40  |

| 2.4.2.3 Class AB amplifier                     | 42  |

| 2.4.2.4 Class C Amplifier                      | 44  |

| 2.4.2.5 Class D Amplifier                      | 46  |

| 2.4.2.6 Class E Amplifier                      | 48  |

| 2.4.2.7 Class F Amplifier                                                         | . 51 |

|-----------------------------------------------------------------------------------|------|

| 2.4.3 Power Amplifier Summary                                                     | . 54 |

| 2.5 Tunable Elements                                                              | . 55 |

| 2.5.1 Tunable Capacitors                                                          | . 55 |

| 2.5.1.1 Micro Electro-Mechanical System (MEMS) Capacitor                          | . 55 |

| 2.5.1.2 Varactor Diodes                                                           | . 56 |

| 2.5.1.3 Digitally Tunable Capacitor (DTC)                                         | . 58 |

| 2.5.2 Tunable Inductors                                                           | . 59 |

| 2.5.2.1 Capacitively Tuned Inductor                                               | . 59 |

| 2.5.3 Switched Bank Components                                                    | . 60 |

| 2.5.4 Summary of Tunable Components                                               | . 63 |

| 2.6 Feedback Topologies and Control Methods                                       | . 64 |

| 2.6.1 Measurement of Reflection Coefficients Using A Directional Coupler          | . 64 |

| 2.6.2 Iterative Search Methods Based on the Measurement of Reflection Coefficient | . 68 |

| 2.6.3 Direct Impedance Measurement                                                | . 68 |

| 2.7 Summary                                                                       | . 70 |

| CHAPTER 3. RESEARCH METHODOLOGY                                                   | . 71 |

| 3.1 Overview                                                                      | . 71 |

| 3.2 Specifications                                                                | . 71 |

| 3.3 System Modeling                                                               | . 72 |

| 3.4 Block Diagram                                                                 | . 72 |

| 3.5 Power Amplifier                                                               | . 73 |

| 3.5.1 Power Amplifier Design                                                      | . 73 |

| 3.5.2 Amplifier Biasing and Operating Procedures                                  | . 77 |

| 3.5.3 Power Amplifier Testing                                                     | . 78 |

| 3.5.3.1 Power Amplifier Spectrum Analyzer Test                                    | . 78 |

| 3.5.3.2 Power Amplifier Network Analyzer Test                                     | . 81 |

| 3.5.4 Amplifier Test Results Summary                                              | . 87 |

| 3.6 Summary                                                                       | . 87 |

| CHAPTER 4. RESULTS                                                                | . 88 |

| 4.1 Overview                                                                      | . 88 |

| 4.2  | Ma    | tching Network                               | 88  |

|------|-------|----------------------------------------------|-----|

| 4.   | 2.1   | Matching Network Design                      |     |

| 4    | 4.2.1 | .1 Input Matching Network Design             | 89  |

| 4    | 4.2.1 | .2 Output Matching Network Design            |     |

| 4.   | 2.2   | Matching Network Test Setup                  | 96  |

| 4.   | 2.3   | Matching Network Results                     |     |

| 4.   | 2.4   | Matching Network Test Results Summary        | 107 |

| 4.3  | Sen   | sing Method                                  |     |

| 4.   | 3.1   | Sensing Method Design                        |     |

| 4.   | 3.2   | Sensing Method Test Setup                    | 113 |

| 4.   | 3.3   | Sensing Method Test Results                  | 114 |

| 4.   | 3.4   | Sensing Method Test Summary                  | 115 |

| 4.4  | Sys   | tem Integration                              | 115 |

| 4.5  | Coi   | ntrol System                                 |     |

| 4.   | 5.1   | Control System Design                        | 120 |

| 4.   | 5.2   | Control System Test Setup                    |     |

| 4.   | 5.3   | Control System Test Results                  |     |

| 4.   | 5.4   | Control System Test Results Summary          |     |

| 4.6  | Sys   | tem Power Added Efficiency                   |     |

| 4.   | 6.1   | Power Added Efficiency Test Setup            |     |

| 4.   | 6.2   | Power Added Efficiency Test Results          |     |

| 4.   | 6.3   | Power Added Efficiency Test Results Summary  |     |

| 4.7  | Coi   | nplete System Summary                        |     |

| 4.8  | Ass   | sumptions, Limitations, Delimitations        | 141 |

| 4.   | 8.1   | Assumptions                                  | 141 |

| 4.   | 8.2   | Delimitations                                | 141 |

| 4.   | 8.3   | Limitations                                  | 141 |

| 4.9  | Sur   | nmary                                        |     |

| CHAP | TER   | 5. SUMMARY, CONCLUSIONS, AND RECOMMENDATIONS |     |

| 5.1  | Sur   | nmary of Work Completed                      |     |

| 5.2  | Rec   | commendations for Improvement                |     |

| LIST OF REFERENCES                | 145 |

|-----------------------------------|-----|

| APPENDIX A. CONTROLLER CODE       | 150 |

| APPENDIX B. EQUATION CALCULATIONS | 168 |

# LIST OF TABLES

| Table 2.1: L Matching Network Options                               |    |

|---------------------------------------------------------------------|----|

| Table 2.2: Performance Characteristics of Transistors (Pozar, 2011) |    |

| Table 2.3: Power Amplifier Summary                                  |    |

| Table 2.4: Tunable Capacitance Component Summary                    |    |

| Table 3.1: Amplifier Test Circuit BOM                               | 76 |

| Table 3.2: Power Amplifier Power Measurements                       |    |

| Table 3.3: Unmatched Power Amplifier Characteristics 10dBm Input    |    |

| Table 3.4: Amplifier Test Results Summary                           |    |

| Table 4.1: Input Matching Network BOM                               |    |

| Table 4.2: Output Matching Network BOM                              |    |

| Table 4.3: Theoretical Match to Amplifier Capability                |    |

| Table 4.4: Output Matching Network Power Loss                       |    |

| Table 4.5: Redesigned Output Matching Network Power Loss            |    |

| Table 4.6: Matching Network Test Results Summary                    |    |

| Table 4.7: Sensing BOM                                              |    |

| Table 4.8: Sensing Method Specification Summary                     |    |

| Table 4.9: Complete System BOM                                      |    |

| Table 4.10: Low Band Controller Results                             |    |

| Table 4.11: High Band Controller Test Results                       |    |

| Table 4.12: Control System Specification Summary                    |    |

| Table 4.13: Unmatched Amplifier PAE                                 |    |

| Table 4.14: Full System Low Band Configuration PAE                  |    |

| Table 4.15: Full System High Band Configuration PAE                 |    |

| Table 4.16: Power Added Efficiency Test Results                     |    |

| Table 4.17: Summary of Subsystem Results                            |    |

| Table 4.18: Summary of System Results                               |    |

# LIST OF FIGURES

| Figure 2.1: Basic Network Diagram                                           |    |

|-----------------------------------------------------------------------------|----|

| Figure 2.2: Output Characteristics vs. Normalized Load Impedance            |    |

| <i>Figure 2.3:</i> L Matching Network $Z_s < Z_L$                           |    |

| <i>Figure 2.4:</i> L Matching Network $Z_s > Z_L$                           |    |

| Figure 2.5: Series Shunt Cascaded L Matching Network                        |    |

| Figure 2.6: Shunt Series Cascaded L Matching Network                        |    |

| Figure 2.7: Theoretical Resistance for Cascaded L Network Design            |    |

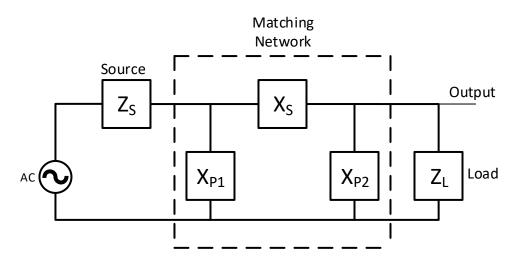

| Figure 2.8: Generic Model of Pi Matching Network                            |    |

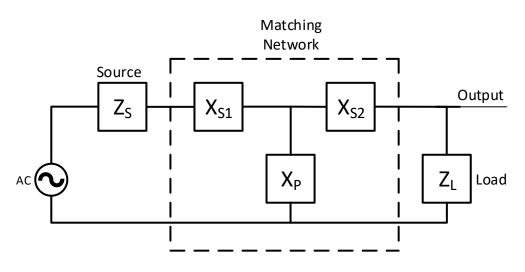

| Figure 2.9: Generic Model of Tee Matching Network                           |    |

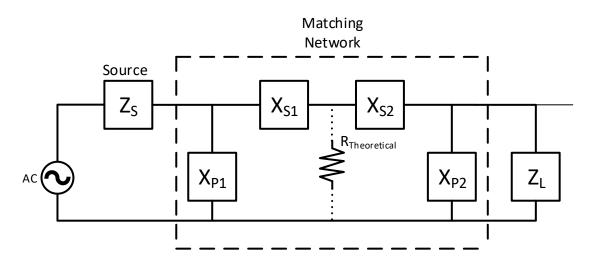

| Figure 2.10: Pi Network With Theoretical Resistance                         |    |

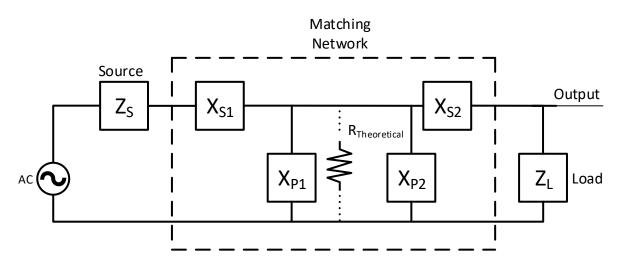

| Figure 2.11: Tee Network with Theoretical Resistance                        |    |

| Figure 2.12: Lumped Element Pi Network Configurations                       |    |

| Figure 2.13: Lumped Element Tee Network Configurations                      |    |

| Figure 2.14: Series Circuit for Realization of Resistive Load (Breed, 2008) |    |

| Figure 2.15: Shunt Circuit for Realization of Resistive Load (Breed, 2008)  |    |

| Figure 2.16: 1dB Compression Point (Mini-Circuit, 2015)                     |    |

| <i>Figure 2.17:</i> Simplified Hybrid $\pi$ Equivalent Circuit of Junction  |    |

| Figure 2.18: Small-signal Equivalent Circuit for FET in                     |    |

| Figure 2.19: Class A Amplifier Basic Design                                 |    |

| Figure 2.20: Class A Amplifier Output Waveform                              |    |

| Figure 2.21: Class B Complementary Amplifier Basic Design                   |    |

| Figure 2.22: Class B Amplifier Waveforms                                    |    |

| Figure 2.23: Class AB Complementary Amplifier Basic Design                  |    |

| Figure 2.24: Class AB Amplifier Waveforms                                   |    |

| Figure 2.25: Class C Complementary Amplifier Basic Design                   |    |

| Figure 2.26: Class C Amplifier Waveforms                                    |    |

| Figure 2.27: Class D Amplifier Basic Design                                 | 47 |

| Figure 2.28: Class D Amplifier Waveforms                                                                                                                          | . 48 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.29: Class E Zero Voltage Crossing Amplifier                                                                                                              | . 49 |

| <i>Figure 2.30:</i> Waveforms for a Zero Voltage Crossing Amplifier. A) Optimum Operation. B) Below 50% Duty Cycle. C) Above 50% Duty Cycle. (Kazimierczuk, 2015) | . 49 |

| Figure 2.31: Class E Zero Current Crossing Amplifier                                                                                                              | . 50 |

| <i>Figure 2.32:</i> Zero Current Crossing Class E Amplifier Waveforms: A) Optimum Operation. B Suboptimum Operation (Kazimierczuk, 2015)                          |      |

| Figure 2.33: Class F Amplifier                                                                                                                                    | . 51 |

| Figure 2.34: Inverse Class F Amplifier                                                                                                                            | . 52 |

| Figure 2.35: Class F Amplifier Typical Waveforms (Kazimierczuk, 2015)                                                                                             | . 52 |

| Figure 2.36: Inverse Class F Amplifier Typical Waveforms (Kazimierczuk, 2015)                                                                                     | . 53 |

| Figure 2.37: MEMS Capacitor (Pozar, 2011)                                                                                                                         | . 56 |

| Figure 2.38: Varactor Model                                                                                                                                       | . 57 |

| Figure 2.39: Varactor Array (Nemati, Fager, Gustavsson, Jos, & Zirath, 2009)                                                                                      | . 57 |

| Figure 2.40: Improved Power Handling Varactor Design (Buisman, et al., 2007)                                                                                      | . 57 |

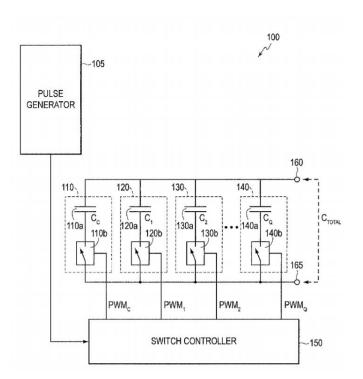

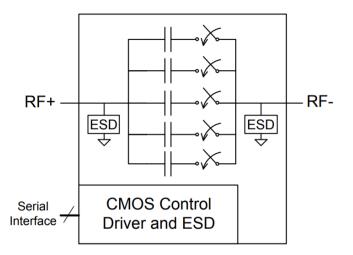

| Figure 2.41: Patent Diagram for a Digitally Tunable Capacitor                                                                                                     | . 58 |

| Figure 2.42: Block Diagram of Peregrine Semiconductor Corp. DTC                                                                                                   | . 59 |

| Figure 2.43: Capacitive Variable Inductor Options                                                                                                                 | . 60 |

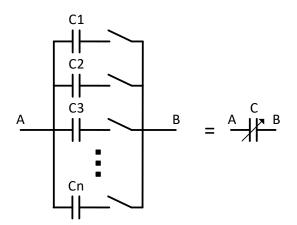

| Figure 2.44: Switched Capacitor                                                                                                                                   | . 61 |

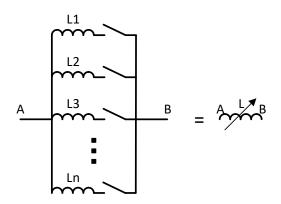

| Figure 2.45: Switched Inductor                                                                                                                                    | . 61 |

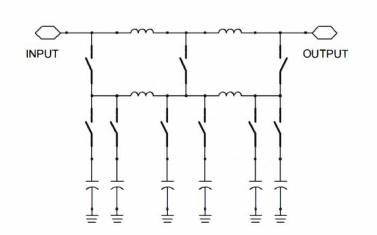

| Figure 2.46: Schematic of Switched Component Tunable Matching Network                                                                                             | . 61 |

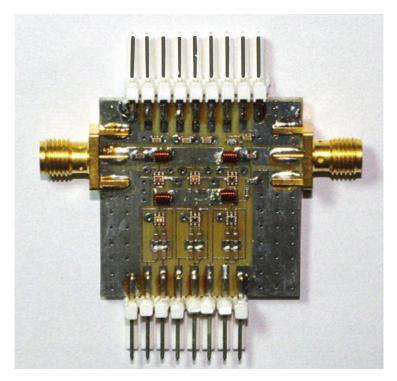

| Figure 2.47: Realization of Switched Component Tunable Matching Network                                                                                           | . 62 |

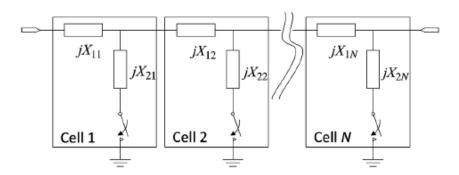

| Figure 2.48: Cell Based Switch Bank (Sanchez-Perez, de Mingo, Carro, & Garcia-Ducar, 201                                                                          | ,    |

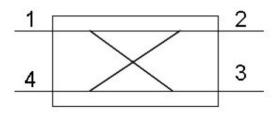

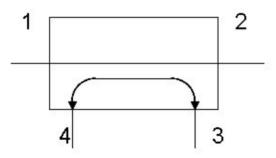

| Figure 2.49: Generic Directional Coupler Schematic Symbol (Directional Couplers, 2013)                                                                            |      |

| Figure 2.50: Bidirectional Coupler (Directional Couplers, 2013)                                                                                                   | . 65 |

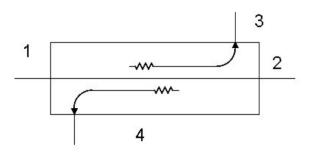

| Figure 2.51: Dual Directional Coupler (Directional Couplers, 2013)                                                                                                | . 66 |

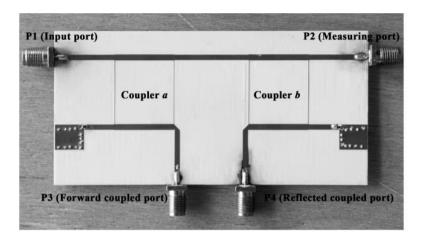

| Figure 2.52: Directional Coupler Implemented (Le & Zimmer, 2015)                                                                                                  | . 66 |

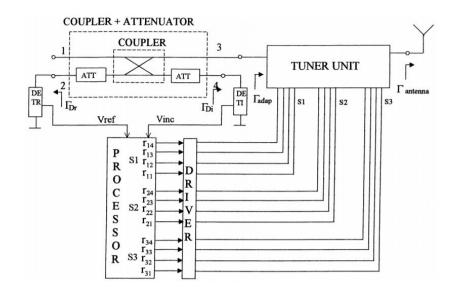

| <i>Figure 2.53:</i> Basic Diagram of Coupler Driver Feedback for Processor Control of a Tunable Matching Network. (de Mingo, et al., 2004)                        | . 67 |

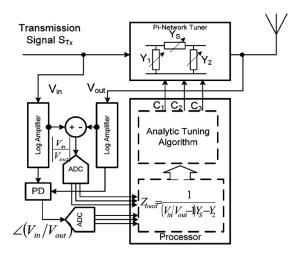

| <i>Figure 2.54:</i> Block Diagram of an Analytical Based Adaptive Matching Network Control (Gu & Morris, 2013) |

|----------------------------------------------------------------------------------------------------------------|

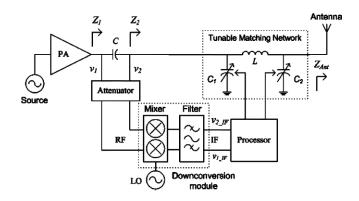

| Figure 2.55: Block Diagram of a Series Capacitance Based Deembedding Approach                                  |

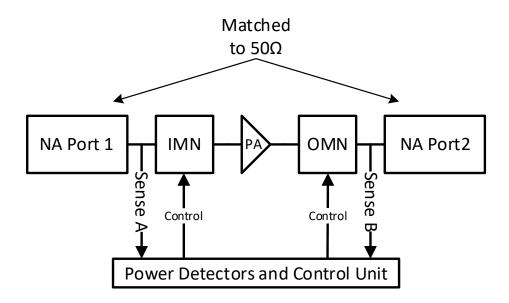

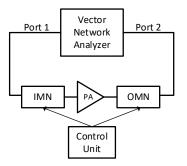

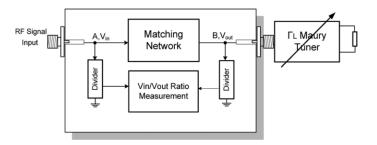

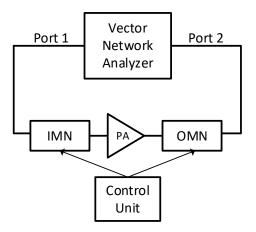

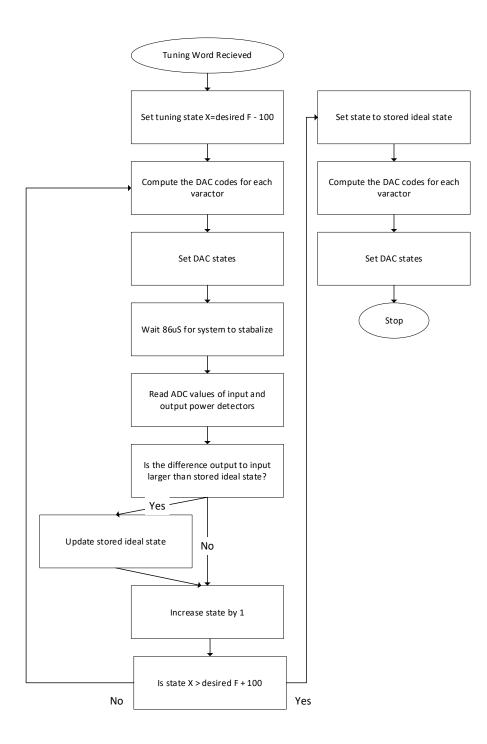

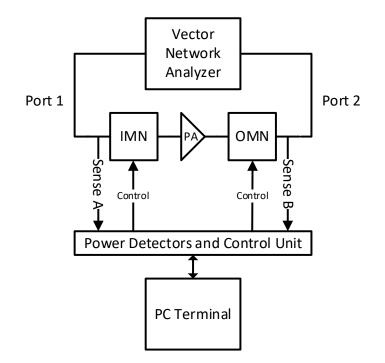

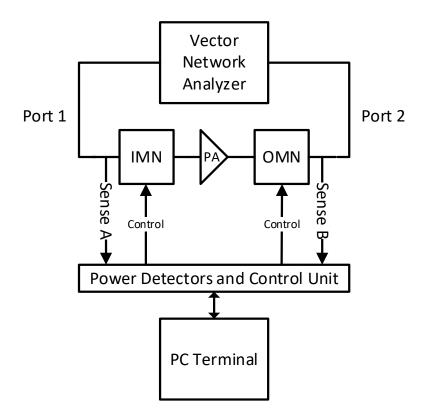

| Figure 3.1: System Block Diagram                                                                               |

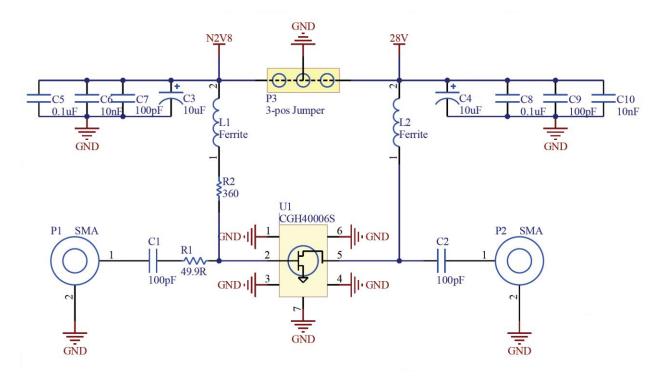

| <i>Figure 3.2:</i> Amplifier Schematic                                                                         |

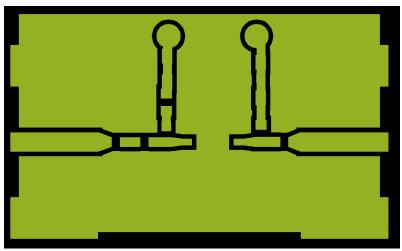

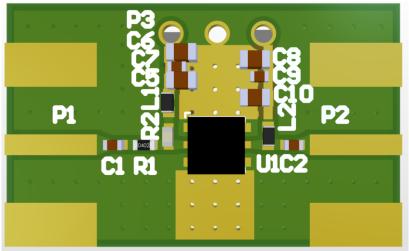

| Figure 3.3: Power Amplifier Test Board Top, Bottom, and 3D Layout                                              |

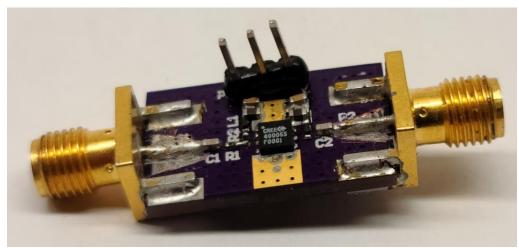

| <i>Figure 3.4:</i> Built Power Amplifier Test Board76                                                          |

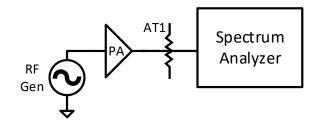

| Figure 3.5: Power Amplifier Spectrum Test Setup                                                                |

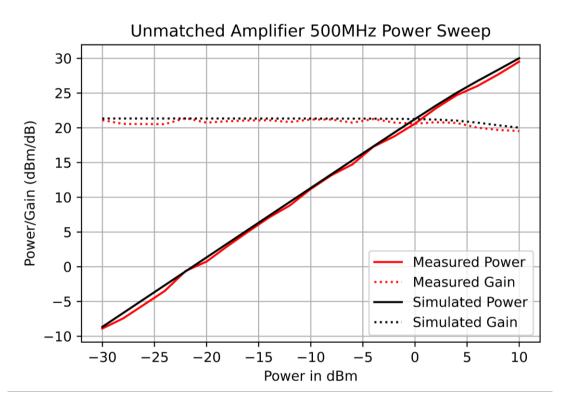

| Figure 3.6: Unmatched Amplifier 500MHz Power Sweep                                                             |

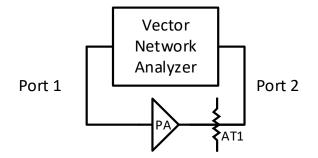

| Figure 3.7: Test Setup for Power Amplifier Measurements                                                        |

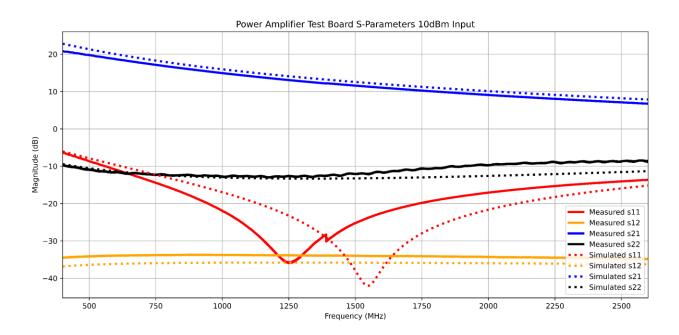

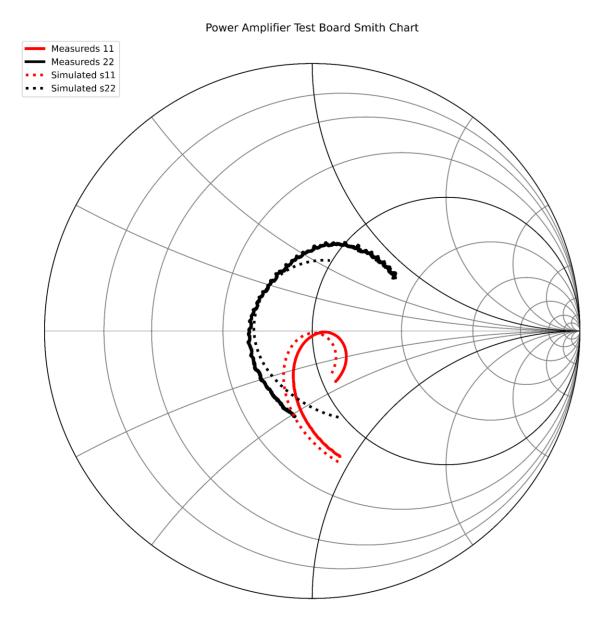

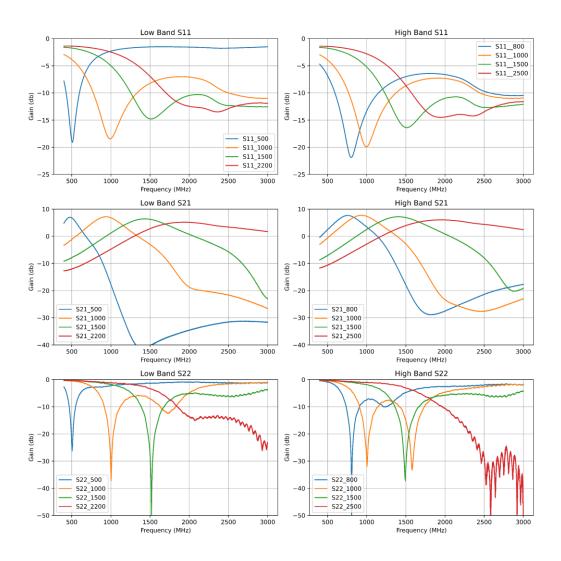

| Figure 3.8: Power Amplifier Test Board S-parameters 10dBm Input                                                |

| Figure 3.9: Unmatched Power Amplifier S-parameters and Smith Chart                                             |

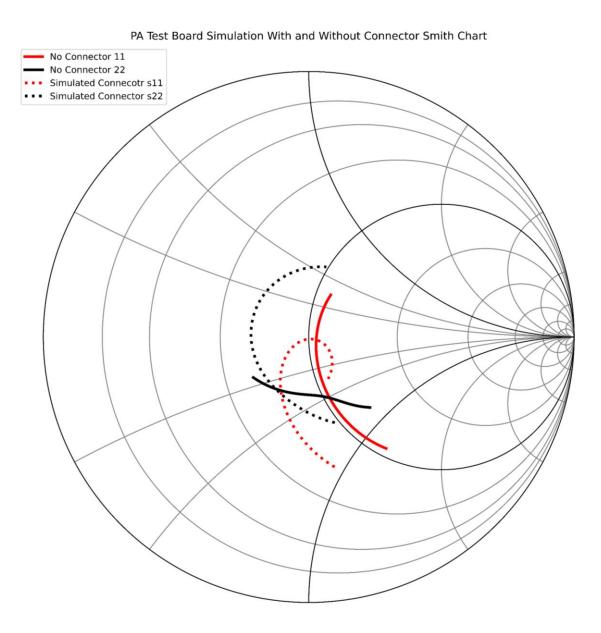

| Figure 3.10: Power Amplifier Simulation With and Without Connector models                                      |

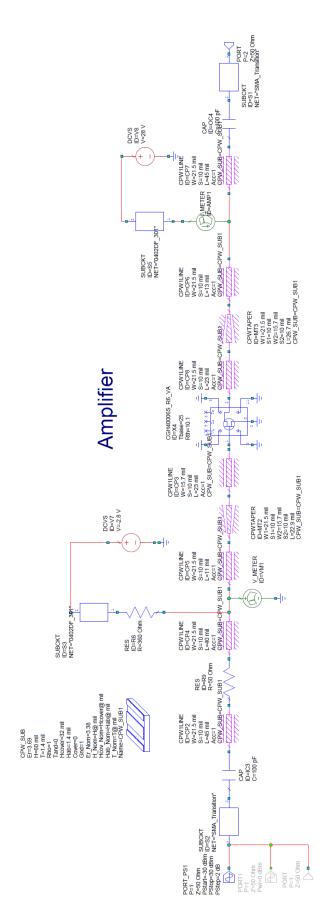

| Figure 3.11: Power Amplifier Test Board Simulation Setup                                                       |

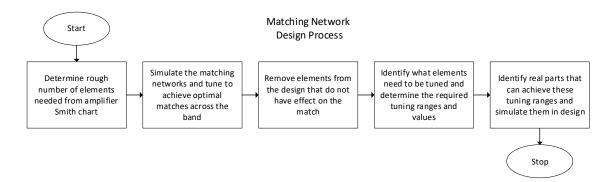

| Figure 4.1: Matching Network Design Process                                                                    |

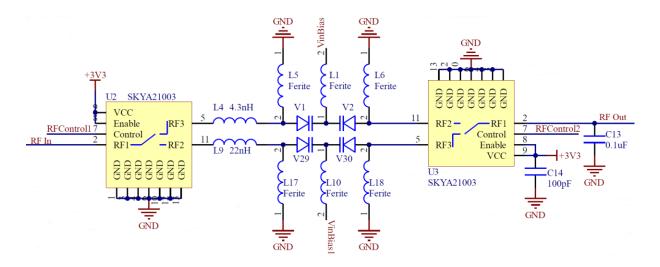

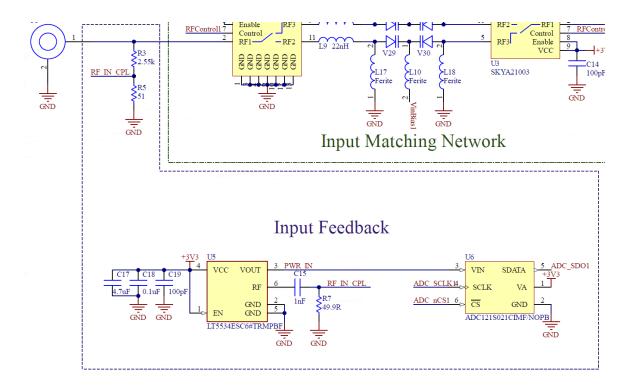

| Figure 4.2: Input Matching Network Schematic                                                                   |

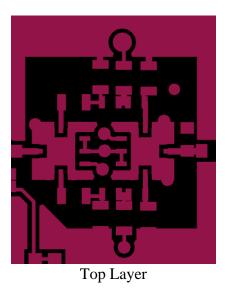

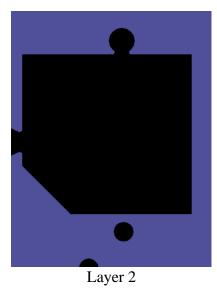

| Figure 4.3: Input Matching Network Gerber Layers and 3D Layout                                                 |

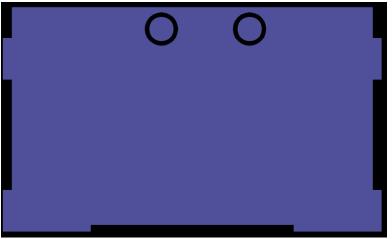

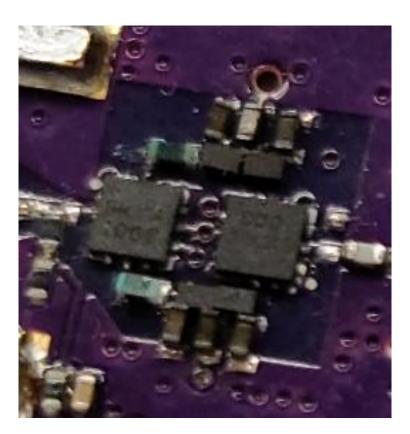

| Figure 4.4: Assembled Input Matching Network                                                                   |

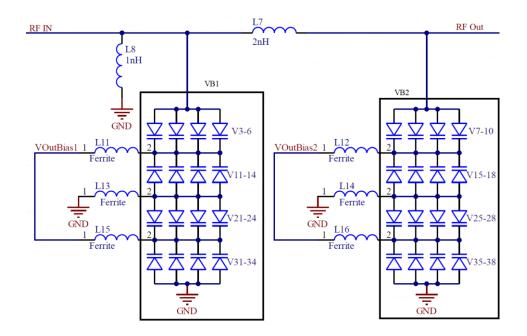

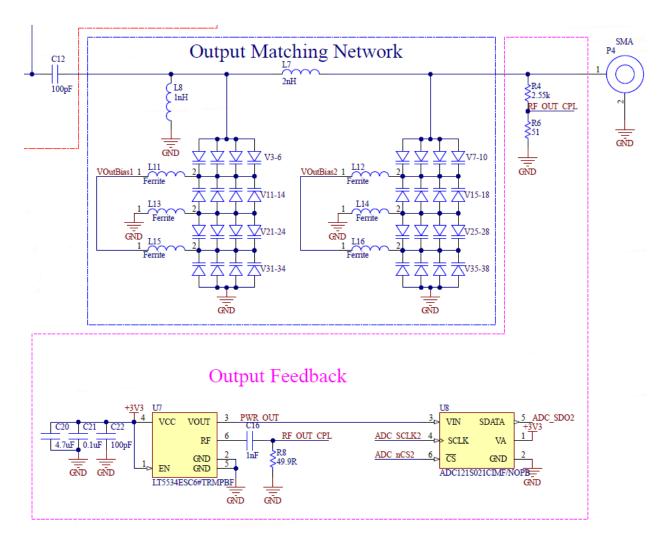

| Figure 4.5: OutputMatching Network Schematic                                                                   |

| Figure 4.6: Output Matching Network Layout                                                                     |

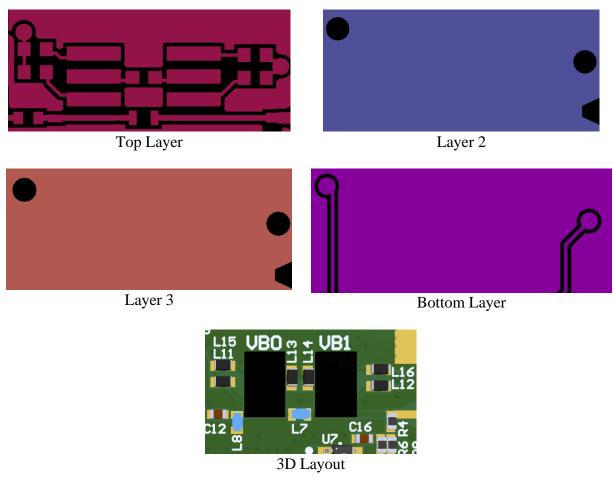

| <i>Figure 4.7:</i> Built Output Matching Network                                                               |

| Figure 4.8: Test Setup for Matching Network Measurements                                                       |

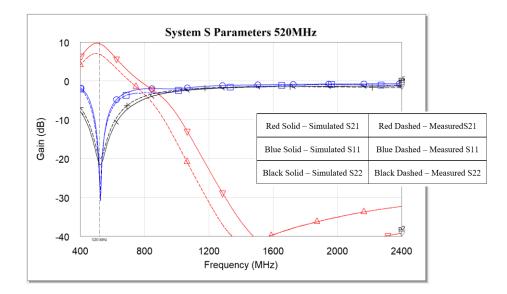

| Figure 4.9: Simulated vs. Measured System S-parameters at 520MHz                                               |

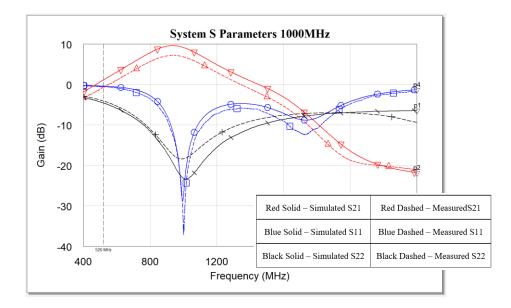

| Figure 4.10: Simulated vs. Measured System S-parameters at 1000MHz                                             |

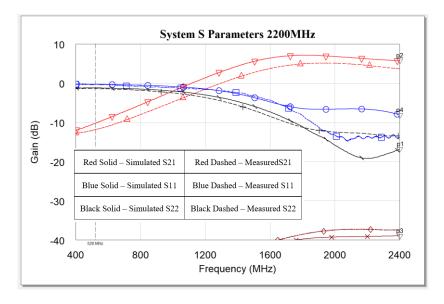

| Figure 4.11: Simulated vs. Measured System S-parameters at 2200MHz                                             |

| Figure 4.12: System Matching Network Swept S-parameters 100                                                    |

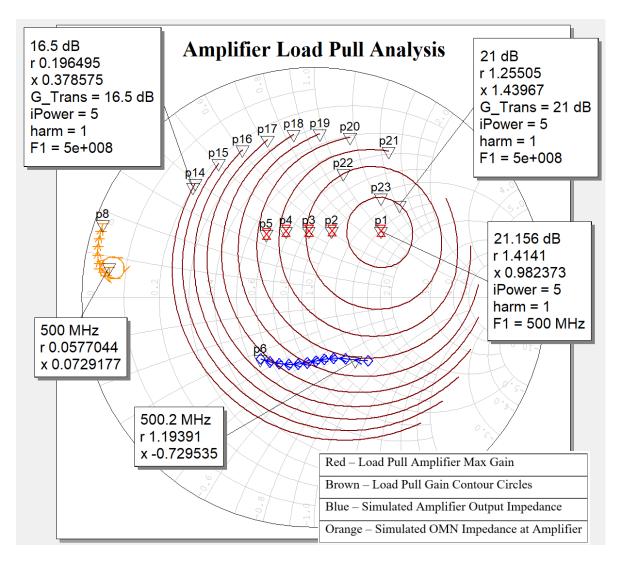

| Figure 4.13: Amplifier Load Pull Analysis                                                                      |

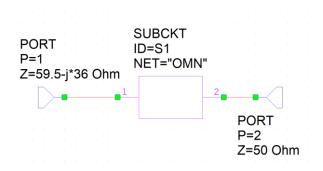

| Figure 4.14: Output Matching Network Amplifier Replacement 103                                                 |

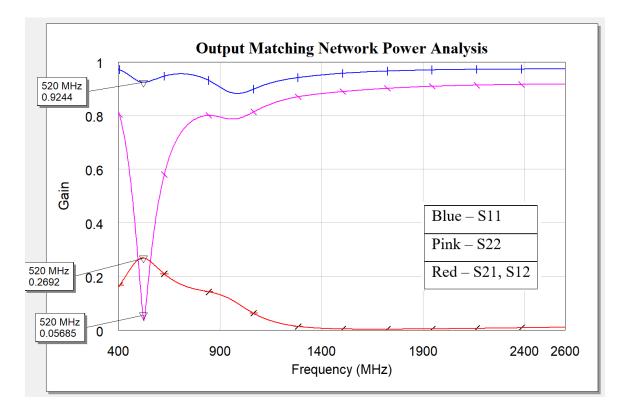

| Figure 4.15: Output Matching Network Power Analysis 103                                                        |

| Figure 4.16: Redesigned Static Matching Circuit                                                                |

| Figure 4.17: Redesigned OMN and Load Pull Analysis                      | 105 |

|-------------------------------------------------------------------------|-----|

| Figure 4.18: Redesigned OMN S-parameters                                | 106 |

| Figure 4.19: Comparison of OMN Power Analysis                           | 107 |

| Figure 4.20: Reference Design for Sensing Method                        | 108 |

| Figure 4.21: Input Feedback Schematic                                   | 109 |

| Figure 4.22: Output Feedback Schematic                                  | 110 |

| Figure 4.23: Input and Output Sensing Layouts                           |     |

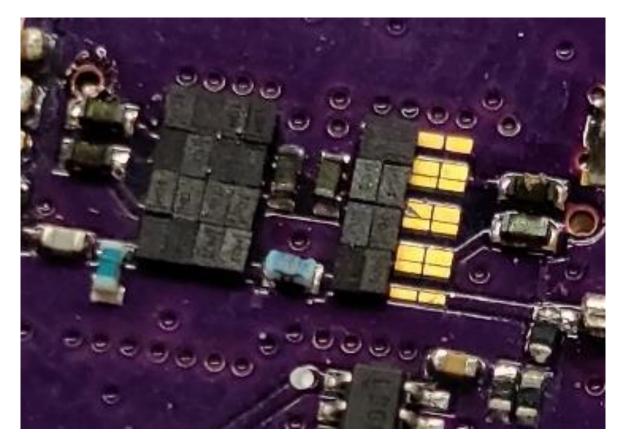

| Figure 4.24: Built Feedback Networks                                    | 113 |

| Figure 4.25: Sensing Method Physical Setup                              |     |

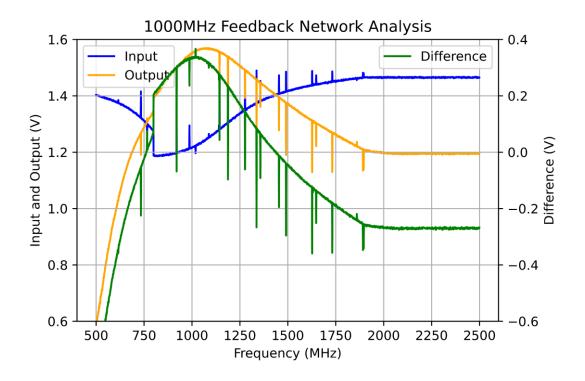

| Figure 4.26: Feedback Analysis 1000MHz                                  |     |

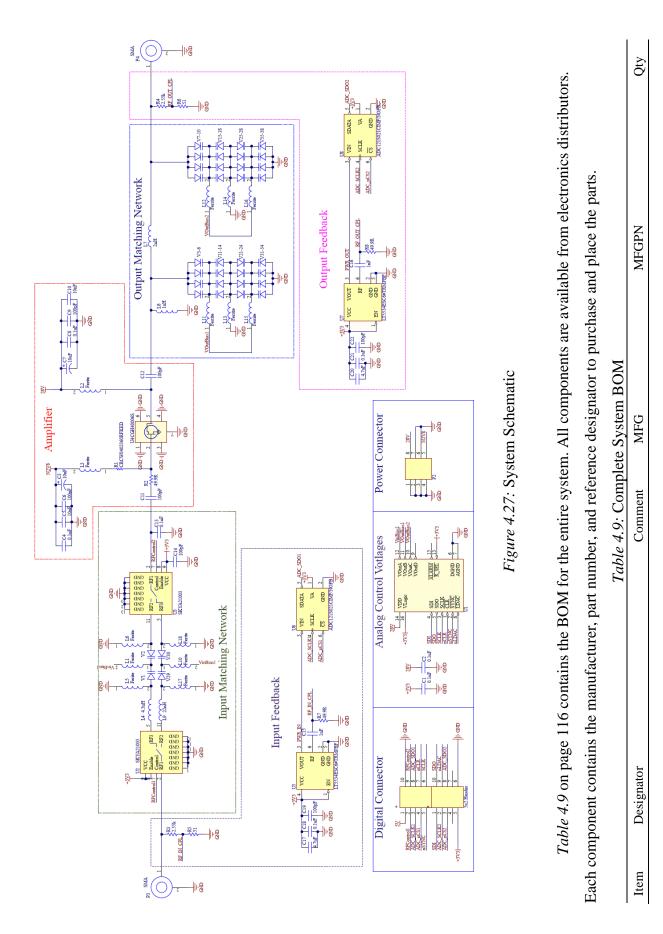

| Figure 4.27: System Schematic                                           | 116 |

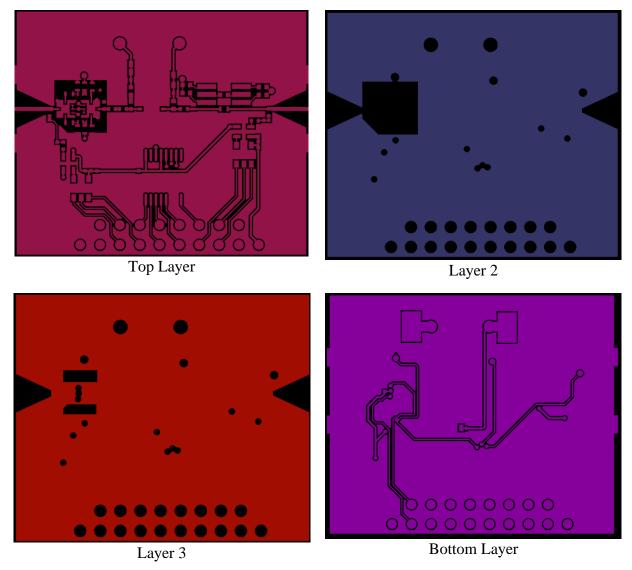

| Figure 4.28: System Layout                                              |     |

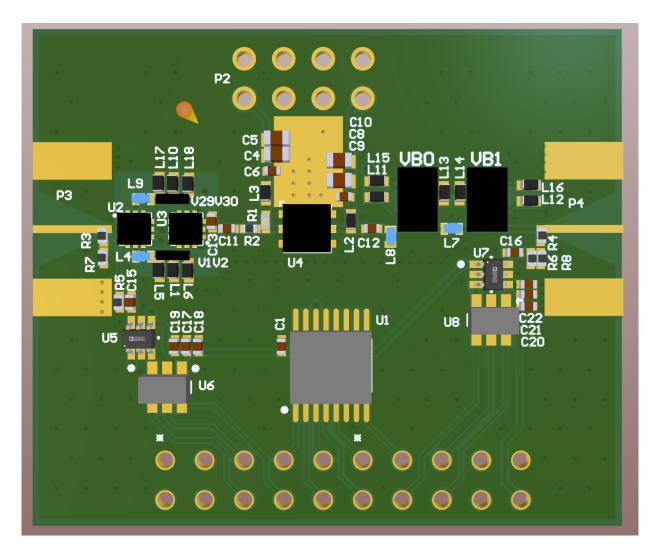

| Figure 4.29: System 3D Model                                            | 119 |

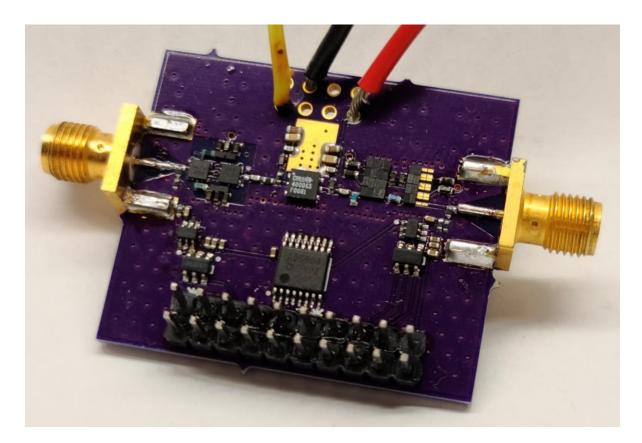

| Figure 4.30: Built System                                               | 120 |

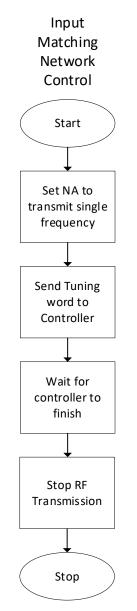

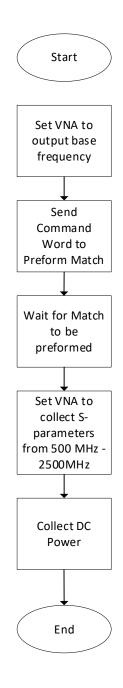

| Figure 4.31: Test Bench Flow Chart                                      | 122 |

| Figure 4.32: Control Algorithm Flow Chart                               | 123 |

| Figure 4.33: Control System Test Setup                                  |     |

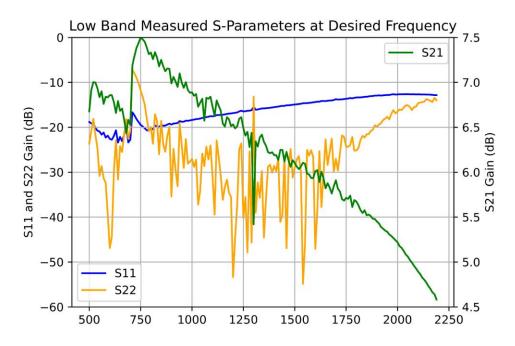

| Figure 4.34: Low Band Measured S-parameters at Desired Frequency        | 126 |

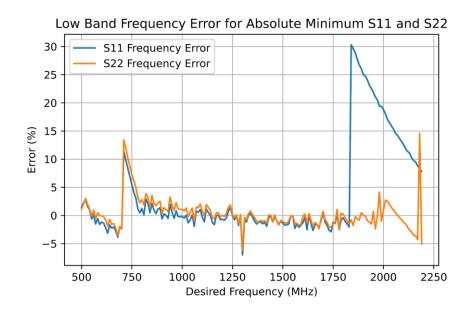

| Figure 4.35: Low Band Frequency Error for Absolute Minimum S11 and S22  | 126 |

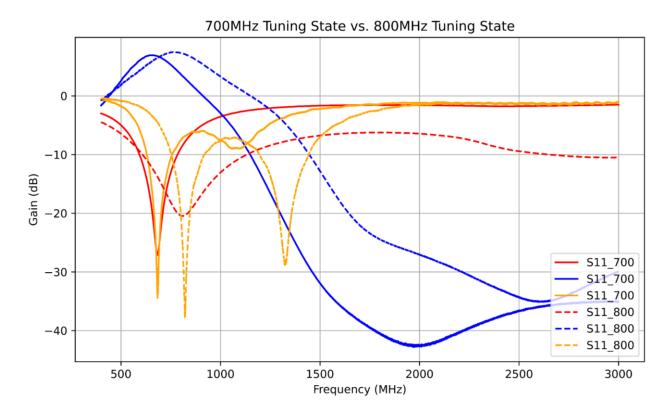

| Figure 4.36: 700MHz vs. 800MHz Tuning State                             | 127 |

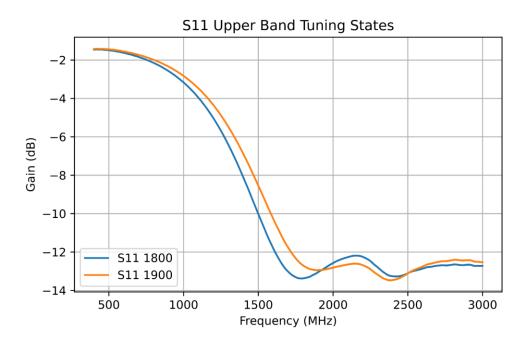

| Figure 4.37: S11 Upper Band Tuning States                               | 128 |

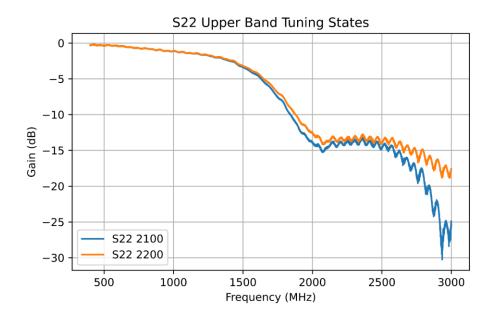

| Figure 4.38: S22 Upper Band Tuning States                               | 128 |

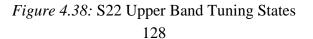

| Figure 4.39: High Band Measured S-parameters at Desired Frequency       | 130 |

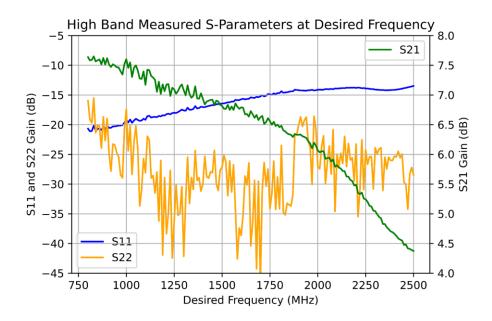

| Figure 4.40: High Band Frequency Error for Absolute Minimum S11 and S22 | 130 |

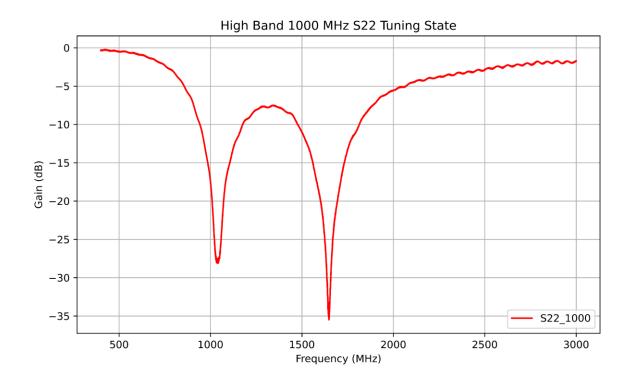

| Figure 4.41: High Band 1000MHz S22 Tuning State                         |     |

| Figure 4.42: Power Added Efficiency Test Setup                          |     |

| Figure 4.43: Power Added Efficiency Testing Procedures                  |     |

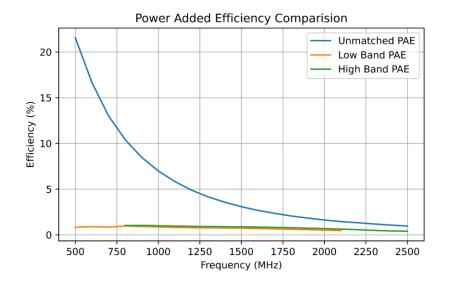

| Figure 4.44: Power Added Efficiency Comparison                          |     |

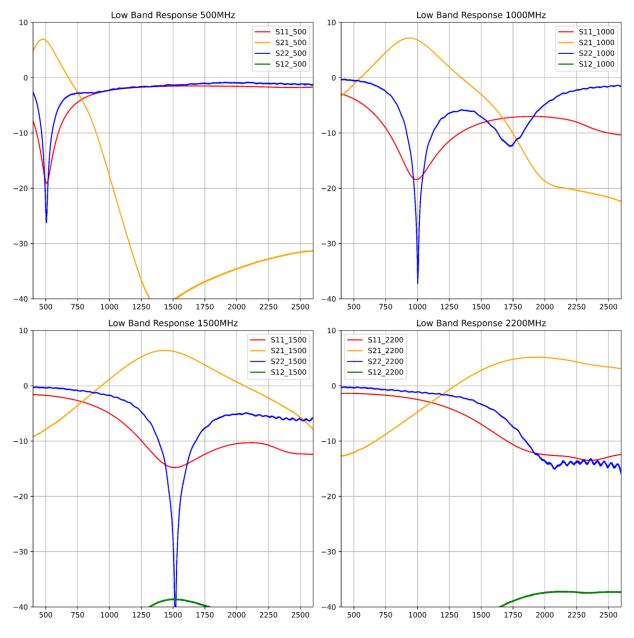

| Figure 4.45: Low Band Frequency Responses                               |     |

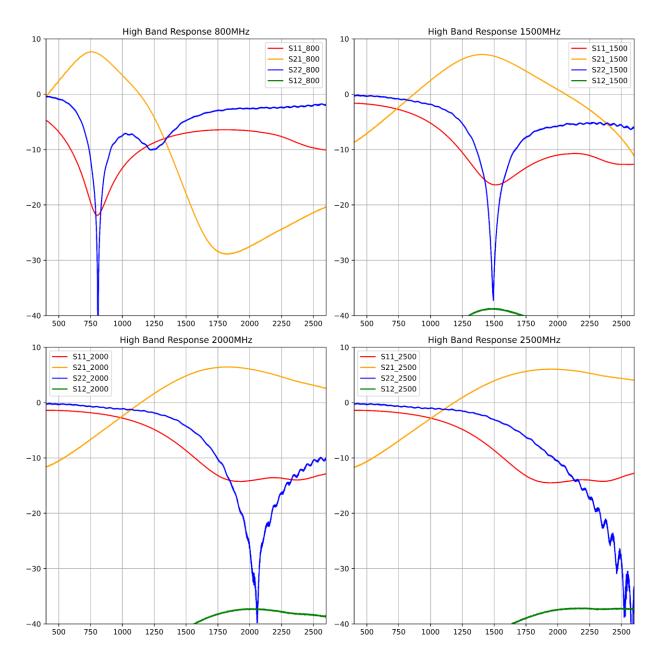

| Figure 4.46: High Band Frequency Responses                              | 139 |

# GLOSSARY, ABBREVIATIONS, AND SYMBOLS

## **Abbreviations**

| ADC: Analog to Digital Converter         | Γ: Reflection                                         |

|------------------------------------------|-------------------------------------------------------|

| BJT: Bipolar Junction Transistor         | $V_0^+$ : Incident                                    |

| C: Capacitor                             | X: Reactance                                          |

| DAC: Digital to Analog Converter         | X <sub>C</sub> : Capacitiv                            |

| dB: Decibel                              | X <sub>L</sub> Inductive                              |

| DSP: Digital Signal Processor            | X <sub>P</sub> : Parallel (                           |

| FET: Field Effect Transistor             | X <sub>S</sub> : Series Re                            |

| FPGA: Field Programmable Gate Array      | Z <sub>L</sub> : Load (Ou                             |

| G: Gain                                  | Z <sub>S</sub> : Source (In                           |

| HBT: Heterojunction Transistor           |                                                       |

| HEMT: High Electron Mobility Transistor  |                                                       |

| L: Inductor                              |                                                       |

| MEMS: Micro Electro-Mechanical System    | $\pi$ : standard de                                   |

| MESFET: Metal Semiconductor Field Effect |                                                       |

| Transistor                               | <ul><li>ω: angular ve</li><li>Ω: resistance</li></ul> |

| MOSFET: Metal Oxide Semiconductor Field  |                                                       |

| Effect Transistor                        | °: angle in de                                        |

| PA: Power Amplifier                      |                                                       |

| PAE: Power Added Efficiency              |                                                       |

| R: Resistor                              |                                                       |

| RF: Radio Frequency                      |                                                       |

| RFPA: Radio Frequency Power Amplifier    |                                                       |

| VNA: Vector Network Analyzer             |                                                       |

| VSWR: Voltage Standing Wave Ratio        |                                                       |

| Vt: Threshold Voltage                    |                                                       |

| $V_0^-$ : Reflected Wave Voltage         |                                                       |

|                                          |                                                       |

$\Gamma$ : Reflection Coefficient  $V_0^+$ : Incident Wave Voltage X: Reactance X<sub>C</sub>: Capacitive Reactance X<sub>L</sub> Inductive Reactance X<sub>P</sub>: Parallel (Shunt) Reactance X<sub>S</sub>: Series Reactance Z<sub>L</sub>: Load (Output) Impedance Z<sub>S</sub>: Source (Input) Impedance

### **Symbols**

π: standard definition of pi (3.14159)

ω: angular velocity in radian/second

Ω: resistance in Ohms

°: angle in degrees

## ABSTRACT

The research presented covers the theory and design of feedback-driven matching networks for radio frequency power amplifiers. The study examines amplifier classifications, types of tunable components, feedback topologies, and control systems to achieve the desired operation. The work centers on designing and implementing a tunable matching network for an amplifier's input and output. The tunable systems provide the amplifier with a wide range of operational frequencies at reasonable power levels comparable to today's modern communication systems and produce millisecond-based tuning times. Simulated results are verified against a fabricated system prototype and tweaked to provide further insight into the design's operation.

## CHAPTER 1. INTRODUCTION

The wireless communication industry is ever-expanding, driven by the need for faster speeds, more substantial data transfer, and reduced power consumption. The incorporation of these features presents an interesting problem for engineers. Engineers are turning to wideband operations as the way of the future to accomplish these goals. The concept is that each user has more stake in the Radio Frequency (RF) spectrum for their data transmission, analogous to larger pipelines for data to flow through (Rodriguez, 2008). To achieve this, high-efficiency electronic systems and devices that can handle the wide bandwidth are required.

Power amplifiers (PA) are among the most critical aspects of the Radio Frequency (RF) transmit chain. Radio Frequency Power Amplifiers (RFPAs) are typically the final stage before the antenna and thus provide the actual power for transmission. A Typical RFPA converts DC voltage into RF power employing an N channel transistor. The change of the voltage on the transistor gate and the device's constant gain amplifies the signal. RFPAs are not like other high-efficiency amplifiers, such as class D amplifiers. Device and circuit parasitics in these high-efficiency amplifiers cause problems at higher switching frequencies, unlike low-frequency audio amplifiers (Raab, et al., 2002). For these reasons, RFPAs need to be linear in design. A standard example of an RFPA topology is a Class A amplifier. Linear amplifiers are notorious for their lack of efficiency. Removal of inefficiencies in the surrounding system compensates for the RFPA's already high losses (Zannas & Vafiadis, 2016).

One of the challenges to power transmission from an RFPA is the impedance mismatch at different frequencies. An impedance mismatch can cause reflections on the input and output of the power amplifier. The system loses the reflected power instead of transmitting it and can even incur noise on the output. In traditional narrowband applications, matching the antenna and amplifier together is done using a lumped element matching network allowing optimal power transfer. RFPA's can be statically matched because over a narrow band of operation, the devices' impedance remains constant. For narrowband applications, static matching networks work well due to the design's simplicity but fall short in wideband applications (Thompson, Richardson, Davis, & White, 2005). In wideband configurations, an RFPA and antenna's impedance changes significantly enough that the static matching network no longer provides a high power

16

transmission level. For very wide bandwidths, this requires lots of networks and an increase in cost in printed circuit board (PCB) space and parts, which is not practical.

One technology currently being implemented around the country is 5G ultra-wideband. One of the many advances that this technology bolsters is the concept of wide bandwidths for data transfer on handheld devices. Many of the systems that will support 5G are handheld and thus run on batteries. The RF transmit chain's high efficiency is crucial to successful deployment and general adoption by the community. Since the power amplifier consumes the most energy in the RF chain for these devices, it is desirable to minimize its losses.

This thesis's research addresses the impedance mismatch that occurs as power amplifiers impedance change over the frequency spectrum and how best to control the match using feedback. Power amplifiers offer a complex impedance (resistance and reactance) on their inputs and outputs. The matching networks on the inputs and outputs of the RFPA can be adjusted to provide optimal power transmission (maximizing forward power and minimizing reflections) using tunable elements (Leuzzi & Micheli, 2003). A tuned matching network can provide a gain performance increase of 32% over untuned networks (Thompson, Richardson, Davis, & White, 2005). The increase in efficiency would allow for energy to be conserved and help prolong the system's battery life. Implementation of adaptive feedback loops to control the tunable matching network provide enhanced performance over calibrated responses. There are several methods possible, and some are faster or more power-efficient than others (Po, de Foucauld, Morche, Vincent, & Kerherve, 2011)

Based on the problem presented, the purpose of this thesis is to design and analyze a working prototype of wideband tunable matching networks with feedback control for use with a power amplifier. The outcome of this research should yield a functional system that can answer the following hypothesis. Maximum forward power transmission into and out of the RFPA, conservation of energy, and dynamic optimization of a wideband RFPA is achievable using feedback-controlled tunable matching networks.

The system should tune the matching networks based on the RF transmission chain feedback within 100 milliseconds (ms). The system should also cover a tuning range of 500 MegaHertz (MHz) to 2.5 GigaHertz (GHz). The power output of RFPA should be between 27dBm and 30dBm after the matching network. These goals will be met using standard RF

17

design processes and maintain a low budget and physical footprint. These, however, are not constraints of the design but considerations to keep in mind throughout the process.

The significance of this work lies in its ability to configure the system appropriately. Proper configurations save energy, keep high transmission levels, allow for reconfigurability, and provide constant updates (Po, de Foucauld, Morche, Vincent, & Kerherve, 2011) (Gu & Morris, 2013). This type of system could exist in first responder and military-grade electronics, where battery power is a limiting factor, consistent transmission power is critical, and reconfigurability provides extensive communication techniques (Nesimoglu, Aydın, Atilla, Köprü, & Yarman, 2013). Loss of communication due to battery depletion or because the transmission power levels drop drastically is at least inconvenient and even potentially lifethreatening in specific applications.

There is a definitive need for controlled tunable elements in the vast RF space. Providing any efficiency upgrade and control over a system will enable future technologies to utilize the RF spectrum better.

### CHAPTER 2. REVIEW OF LITERATURE

#### 2.1 Literature Review Introduction

The following chapter provides an overview of matching networks, power amplifiers, tunable elements, RF feedback topologies, detection methodologies, and control systems. The chapter explains how each element works individually, along with potential design considerations and challenges. Along with the considerations, each section gives theoretical calculations where applicable.

#### 2.2 System and Device Impedance

Oliver Heaviside used the term Impedance for the first time in the nineteenth century to describe the complex voltage and current ratio of alternating current (AC) circuits (Pozar, 2011). Impedance is the inherent resistance to an alternating current that consists of resistance and reactance. Impedance (Z) is a complex number with a "Real" and "Imaginary" part, denoted by  $(\Omega)$ . Resistance (R) is the real value and has the same effect on direct current (DC) as AC. Power loss occurs through resistance. A typical example of a resistive element is a resistor. Reactance (X) is the imaginary part of the impedance and does not contribute to power loss. Reactive components are capacitors and inductors. In a circuit implementation, inductors do have internal resistance and thus produce a signal loss even though inductors are considered purely reactive. In its Cartesian form, impedance is expressed as follows in EQN(2.1). Note that the "j" in the equation denotes the imaginary term.

$$Z = R + jX EQN(2.1)$$

Resistors, capacitors, and inductors whose units are typical Ohms, Farads, and Henry's, respectively, can be transformed into their impedance equivalent. The impedance transformation for a resistor is simple. The nature of a resistor is frequency independent, so the resistance's value is the same as the impedance. EQN(2.2) shows the impedance transformation for a resistor. For capacitors and inductors, due to their reactive nature, the impedance for these devices is frequency-dependent. The definition of the term angular velocity ( $\omega$ ) is double the frequency (*f*)

multiplied by pi ( $\pi$ ) EQN(2.3). The unit for  $\omega$  is radians per second. EQN(2.4) and EQN(2.5) show the impedance calculations for a capacitor and inductor, respectively.

$$Z_R = R EQN(2.2)$$

$$\omega = 2\pi f \qquad \qquad \text{EQN}(2.3)$$

$$Z_L = j\omega L$$

EQN(2.5)

All devices in an RF signal chain will have impedance, either purely resistive, purely reactive, or complex. Even though the term impedance existed for many years prior, it was not until the 1930's that S. A. Schelkunoff recognized that the concept of impedance could be applied in a distributed manner to describe a system characteristic (Pozar, 2011). The system will also have an overall impedance as defined by its inputs and outputs. There are several standard system impedances, including  $50\Omega$  and  $75\Omega$ . For RF applications, the preference is a purely resistive  $50\Omega$  system. The reason dates to the development of coax cables for high power systems in the 1930s. Through examination,  $77\Omega$  provided the least amount of loss while  $30\Omega$  offered the best power handling. The geometric mean between these two,  $50\Omega$ , is used to compromise between power handling and loss. From here, many devices, cables, and connectors use the standard  $50\Omega$  impedance (Why Fifty Ohms?, 2020).

#### 2.3 <u>Static Matching Networks</u>

The following sections outline the purpose and design of several different matching network topologies. The structure is as follows: why is a matching network important, what is a matching network, and the different network designs.

#### 2.3.1 Why a Matching Network

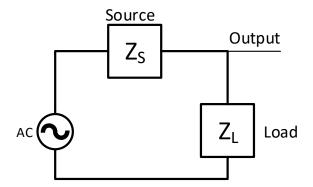

When cascading devices in an RF signal chain, the device's input impedance must match the previous device's output. A system with a perfect match will have the source and load be equal impedances. When this occurs, the maximum amount of power transfers to the load (Pozar, 2011). Take *Figure 2.1*, for example, which shows a network consisting of a source and load impedance. The load will be adjusted and show how an impedance mismatch will affect the output voltage, current, and power.

*Figure 2.1:* Basic Network Diagram

Normalization is a widely accepted form for generalizing impedances of an RF signal chain. In this case, the system source impedance sets the normalization. To normalize the system, divide the source and load impedances by the source impedance. Doing so means that the source's impedance will be 1, and the output will be scaled accordingly. EQN(2.6) and EQN(2.7) demonstrate this. Once the load impedance is normal, it is then used along with the input voltage to calculate the output voltage EQN(2.8), output current EQN(2.9), and output power EQN(2.10).

$$Z_{SNorm} = \frac{Z_S}{Z_S} = 1$$

$$EQN(2.6)$$

$$EQN(2.7)$$

$$V_{out} = V_{in} * \frac{Z_{LNorm}}{Z_{LNorm} + Z_{SNorm}}$$

EQN(2.8)

$$I_{out} = \frac{V_{out}}{Z_{LNorm}}$$

EQN(2.9)

$$P_{out} = V_{out} * I_{out}$$

EON(2.10)

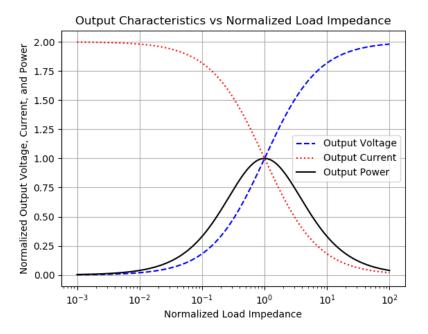

To demonstrate how the mismatch affects the output, apply a 2 volt (V) signal onto the network's input. Adjust the load impedance from a normalized value of 0 to 100. As this change occurs, the voltage and current at the load also change. When the source and load are the same value, 1 in this case, the maximum amount of power is transferred to the load even though the current and voltage are only half their starting values. *Figure 2.2* shows the voltage, current, and power present at the load due to the change in load impedance compared to the input impedance. From the graph, the maximum power transfer of an RF system is when  $Z_{LNorm}$  is equal to  $Z_{SNorm}$  which in this case is 1. The phenomenon is the Maximum Power Transfer Theorem (Maximum Power Transfer Theorem, 2020). RF communications rely on power transfer, so having a system with matched impedances is crucial to its functionality.

*Figure 2.2:* Output Characteristics vs. Normalized Load Impedance Based on EQN(2.8), EQN(2.9), and EQN(2.10)

#### 2.3.2 What is a Matching Network

As mentioned earlier, some aspects of an RF system such as connectors, transmission lines, cables, and even individual IC's are pre-matched to a specific impedance making designs simple. When these parts are not available, the designer takes measures to fix the impedance mismatch by implementing a matching network. These are purely reactive circuits that transform one impedance into another, so all system components are matched accordingly. It is important to note that all the elements in a matching network be reactive to minimize losses. Reactive components are capacitors and inductors. These components theoretically will not dissipate power. If using a resistive element, the energy loss occurs due to the resistance.

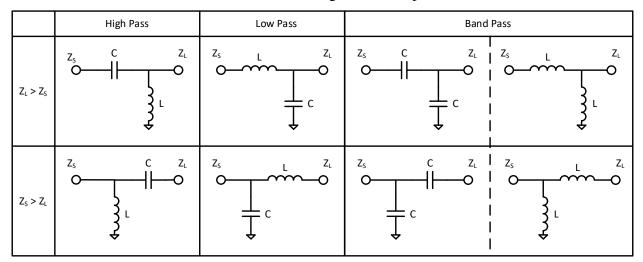

Matching networks come in several different topologies and bandwidths. These are L, Tee, and Pi. Each of these also comes in high pass, low pass, and bandpass configurations. Tee and Pi networks also can be configured in a band stop configuration.

#### 2.3.3 L Matching Network Topology and Analysis

L networks are the easiest to implement and get their name from the shape of the circuit. L networks are considered a narrow band matching network. As the operating frequency moves away from the design frequency, the matching network quickly begins to fail. For L networks, there is a series element and a shunt element. Proper configuration requires placing the series element between the shunt element and the lowest impedance, while the shunt element placement is adjacent to the highest impedance. *Figure 2.3* and *Figure 2.4* show the basic designs of L matching networks.

*Figure 2.3:* L Matching Network  $Z_s < Z_L$

Figure 2.4: L Matching Network  $Z_s > Z_L$

L Matching networks implement the two types of reactive elements, inductors and capacitors, producing eight different topologies (Bahl, 2003). *Table 2.1* shows the network configurations, their band properties, and what load to source impedance provides that topology. Note that matching networks are versions of highpass, lowpass, and bandpass LC filters.

Table 2.1: L Matching Network Options

For purely resistive sources and loads, the calculation of the components in the matching network is straightforward. The quality factor (Q) first needs to be determined. The quality factor is a unitless ratio that compares the input and output impedances. The equation for calculating Q is expressed in EQN(2.11) (Bahl, 2003).

if

$$Z_S > Z_L$$

then  $Q = \sqrt{\frac{Z_S}{Z_L} - 1}$  EQN(2.11)

if

$$Z_L > Z_S$$

then  $Q = \sqrt{\frac{Z_L}{Z_S} - 1}$  EQN(2.12)

After calculating Q, calculate the reactance of the series and shunt components. EQN(2.13) and EQN(2.14) show the calculations for these, respectively (Bahl, 2003),  $Z_{Nearest}$  is the impedance to be matched closest to the series or shunt matching component.

$$X_s = Q * Z_{Nearest}$$

EQN(2.13)

The final step for calculating the series and shunt components is taking the reactances and plugging them back into the respective components' impedance definition. The reactances derived in the previous step are those of the capacitor and the inductor chosen (Bahl, 2003).

$$L = \frac{X_L}{2\pi f}$$

EQN(2.15)

$$C = \frac{1}{2\pi f X_C}$$

EQN(2.16)

#### 2.3.4 Cascaded L Matching Networks

One of L networks' intriguing parts is their ability to be cascaded to create different impedance matches and at much wider bandwidths. These are typically to create bandpass matching networks. A typical design of an L matching network works for only one frequency, but a bandpass network will better match a wide range of frequencies. The bandpass matching network is just a lowpass matching network cascaded in series with a highpass network. *Figure 2.5* and *Figure 2.6* show the typical cascaded L matching network (Breed, 2008).

Figure 2.5: Series Shunt Cascaded L Matching Network

Figure 2.6: Shunt Series Cascaded L Matching Network

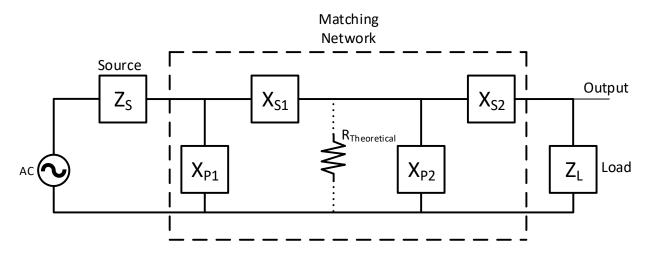

To calculate the network components' values, use a similar design process to simple L matching networks. First, place a theoretical resistance between the two L Networks. Note that this theoretical resistance is not in the final circuit. This resistance is simply a common point to match each half of the network too. When solving for the left L network, this resistance is the load, and when solving for the right side matching network, this is the source. The same equations for quality factor and reactance still apply to this. *Figure 2.7* shows the cascaded L

matching network with theoretical resistance. The theoretical resistance which is the geometric mean of  $Z_L$  and  $Z_s$  can be calculated, as shown in EQN(2.17).

Figure 2.7: Theoretical Resistance for Cascaded L Network Design

$$R_{Theoretical} = \sqrt{Z_s * Z_L} \qquad \qquad \text{EQN}(2.17)$$

After calculating the reactance's, solve for the component values. It is at this point where the increased bandwidths come in. Bandpass matching networks have two break frequencies  $f_{low}$ and  $f_{high}$  at the band edges, which are chosen based on application. One of the L network configurations is for lowpass, and the other is for highpass. The low pass L network uses  $f_{High}$ , and the high pass L network uses the  $f_{Low}$  parameter.

#### 2.3.5 Pi and Tee Matching Networks

Pi and Tee networks are a form of three-element matching. They offer several advantages over L networks; wider bandwidth and adjustable Q. All components have a specific Q based on their physical properties, and this cannot be changed. Recalling EQN(2.11) and EQN(2.12), the required component Q of the L network is fixed based on the source and load impedances. Cascaded L networks Q is also fixed because of the intermediate impedance in EQN(2.17), based on the source and load impedances. The Q of the component must be higher than the required Q of the network, or the system will not function properly. Pi and Tee networks have an adjustable Q because the designer can pick the intermediate impedance. The only criteria for the

intermediate impedance for Pi networks are that it must be lower than both the source and load impedances. For Tee networks, the intermediate impedance must be higher than the source and load. The larger the impedance mismatch, the higher the required Q. Therefore, it will be in the best interest of the designer to pick a topology that has the smallest impedance transformation to keep the network Q sufficiently low compared to components. For these networks, it does not matter if the source or load impedance is higher like it does for L networks (Bowick, 2008).

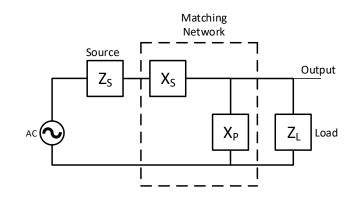

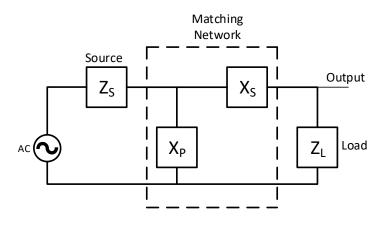

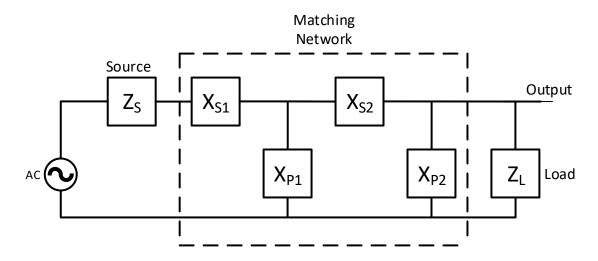

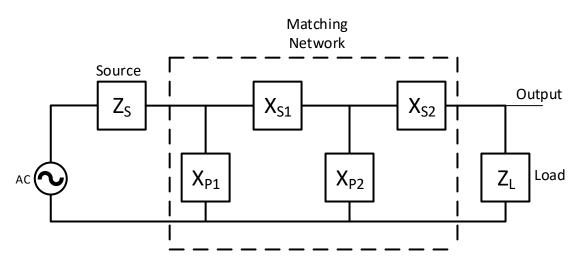

Pi and Tee Matching networks are very similar to the cascaded L matching network design process. The networks are solved essentially the same way but account for a common part in the last step. Pi and Tee networks get their name the same way that L networks do by their shape. *Figure 2.8* and *Figure 2.9* show the Pi and Tee Network designs, respectively. Pi and Tee networks are considered a more wideband approach to matching networks (Bowick, 2008).

Figure 2.8: Generic Model of Pi Matching Network

Figure 2.9: Generic Model of Tee Matching Network

When designing the networks, the first thing to do is split the network into two back-toback L networks with a theoretical resistance in the middle. From here, solve the networks as cascaded L networks. *Figure 2.10* and *Figure 2.11* show how to split the Pi and Tee networks, respectively (Bowick, 2008).

Figure 2.10: Pi Network With Theoretical Resistance

Figure 2.11: Tee Network with Theoretical Resistance

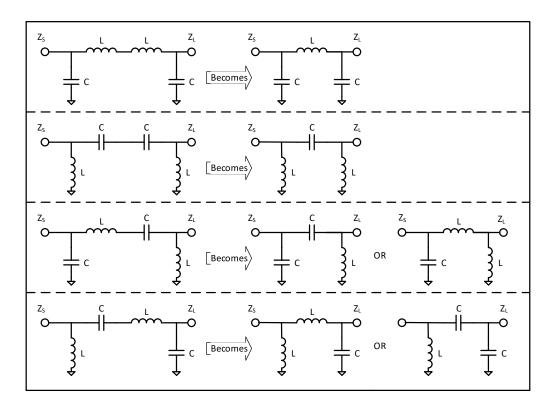

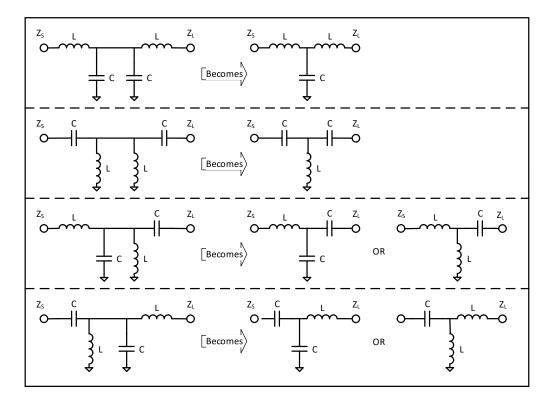

After solving the split network reactances, the center's reactances need to be combined. Combining reactances before converting to components is the easiest way to combine the components. Combining the reactances starts with one of the four topology options in *Figure* 2.12 for Pi Networks or *Figure 2.13* for Tee Networks.

For Pi Networks, combine the center reactances in series by adding the two series reactances to obtain total reactance. Convert the total reactance back into an equivalent reactive component.

For Tee networks, combine the center components in parallel. Do this by using EQN(2.18) to obtain the total parallel reactance. The last step is to convert the combined reactance back into an equivalent reactive component.

One thing to note is that the individual L networks need to have one capacitor and inductor. Both components on the same half of the L network cannot be the same type. *Figure 2.12* and *Figure 2.13* show the lumped element options for Pi and Tee Networks (Bowick, 2008).

$$\frac{1}{(\frac{1}{X_{P1}} + \frac{1}{X_{P1}})}$$

EQN(2.18)

Figure 2.12: Lumped Element Pi Network Configurations

Figure 2.13: Lumped Element Tee Network Configurations

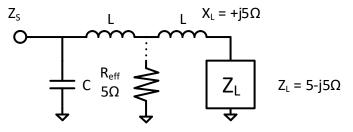

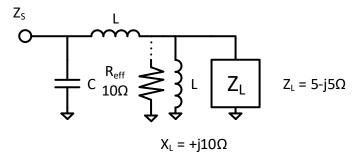

#### **2.3.6** Correcting for Complex Loads

Up to this point, for simplicity, loads have been considered to be purely resistive to make the math simple. As load and source impedances introduce their reactive elements, the mathematics behind the matching network's development becomes increasingly involved. A simple way to solve the problem would be to place a series or shunt component with the complex impedance to achieve a purely resistive impedance (Breed, 2008). *Figure 2.14* and *Figure 2.15* show how adding a reactive element to a load can create a purely resistive load. The same principle applies to source impedances.

Figure 2.14: Series Circuit for Realization of Resistive Load (Breed, 2008)

Figure 2.15: Shunt Circuit for Realization of Resistive Load (Breed, 2008)

#### 2.3.7 Summary of Matching Networks

As can be seen, matching networks play a significant role in the RF signal chain. Ensuring a matched circuit guarantees maximum power transfer to the load and minimizes power loss from reflections. Matching Networks come in many shapes and configurations but are often straightforward to produce. Here is a quick recap of the different types of networks covered.

- L Networks:

- o Consists of two reactive elements in an "L" configuration

- o Narrow bandwidth

- Can be cascaded easily

- Simple to design

- Does not handle complex source and load impedances well

- Pi Networks

- Consist of 3 components in a " $\pi$ " configuration

- o Offers wideband matching

- Is based on back to back L networks

- Medium complexity to design

- Tee Networks

- Consists of 3 components in a "T" configuration

- Offers wideband matching

- Is based on back to back L networks

- Medium complexity to design

- Cascaded Networks

- o Consist of back to back L networks

- o Provides the widest bandpass options compared to the rest of the networks

- o Medium to high level of complexity to design

#### 2.4 Power Amplifier Classification and Designs

Power amplifiers are common components in RF signal chains and are extensively studied. These devices take low power signals and amplify the signal power to drive some load. The most basic options are going to be covered. Amplifiers come in different "classes" these are standard operating topologies, and each comes with benefits and challenges. Along with the different types of amplifiers, there are basic principles of amplifiers that need to be covered.

### 2.4.1 Parameters of a Power Amplifier

RFPA's have several characteristics that are important to understand before discussing the different classifications. These are gain, 1dB compression, efficiency, transistor type, and impedance. The following sections cover these topics before moving on to discussing the different power amplifier classes.

#### 2.4.1.1 <u>Gain</u>

Power amplifiers are designed for one task, provide gain to a signal at its input. Gain is defined as the output power ( $P_{out}$ ) compared to input power ( $P_{in}$ ), both in Watts. Typically gain for a power amplifier is in dB, which is a logarithmic representation. Gains represented linearly, especially at high power, can be vary enough that it is easier to transform everything into a log scale for simplicity. Characterizing an amplifier gain in dB also allows it to be calculated in the system easier since log gains add. To calculate the power gain of an amplifier, use the formula shown in EQN(2.19).

$$G = \frac{P_{out}}{P_{in}} , \qquad G_{dB} = 10 * \log\left(\frac{P_{out}}{P_{in}}\right) \qquad \qquad \text{EQN}(2.19)$$

#### 2.4.1.2 <u>1dB Compression Point</u>

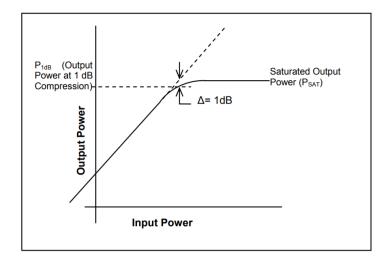

Another critical characteristic of an amplifier is its 1dB compression point. Typically power amplifiers have a set gain. As the input power increases and decreases, so does the output power by the same amount. This phenomenon is known as the linear region of operation. The 1dB compression point is where the amplifier's gain has dropped by 1dB from the amplifier's expected gain. At this point, extra harmonics and unwanted noise, along with the amplifier saturation, begin to occur. When this occurs, the amplifier is in its nonlinear region of operation. RF amplifiers need to operate below the 1dB compression point. *Figure 2.16* shows the principle for the 1dB compression point (Pozar, 2011).

Figure 2.16: 1dB Compression Point (Mini-Circuit, 2015)

#### 2.4.1.3 Efficiency

The power amplifier is typically the largest consumer of DC power ( $P_{DC}$ ) in most handsets. When measuring the power efficiency of a device, compare the output power to the input power. For RFPA's, however, the output power is measured in relation to the DC power. This measurement does not account for any RF power on the input of the device. Instead, power added efficiency can be used instead of traditional efficiency techniques. Power added efficiency (PAE) takes into account the input power ( $P_{in}$ ), output power ( $P_{out}$ ), and DC power ( $P_{DC}$ ) of the device, in Watts, to give a more reasonable approximation to the efficiency of the device. EQN(2.20) shows the calculations for PAE. Note that G is the gain of the amplifier from EQN(2.19) (Pozar, 2011).

$$PAE = \frac{P_{out} - P_{in}}{P_{DC}} = \left(1 - \frac{1}{G}\right) * \frac{P_{out}}{P_{DC}} \qquad EQN(2.20)$$

Along with the amplifier gain and its efficiency, the output type is either linear or switching. Linear amplifiers are inherently lossier than switching amplifiers but create a more accurate output waveform. Switching amplifiers are suitable for constant envelope waveforms, where high distortion is ok, but most applications require as little distortion as possible (Pozar, 2011).

#### 2.4.1.4 <u>Transistor Types</u>

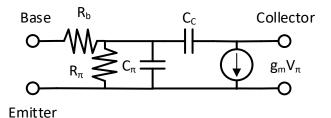

Transistors come in various topologies, which break up into two major categories, Bipolar Junction Transistors (BJT) and Field Effect Transistors (FET). The BJT comes in two configurations, standard BJT and Heterojunction Bipolar Transistor. BJT's are among the oldest types of transistors and still find use in RF applications to this day. The device acts as a currentcontrolled current source. As the base current changes, the collector current changes as well. The BJT offers good operating performance in terms of its frequency range, power efficiency, cost, and ease of biasing. One drawback is a higher noise figure that exists because of the shot noise created in the transistor. *Figure 2.17* shows the equivalent circuit for a Bipolar Junction Transistor. Typically, one ignores the capacitance of  $C_C$  because it is small enough not to have significant effects. A Heterojunction Transistor (HBT) is almost identical to a BJT except in the semiconductor layer layout. The semiconducting layer of an HBT breaks into several different layers, unlike a single layer BJT's. This topology allows for high electron mobility increasing frequency range (Pozar, 2011).

*Figure 2.17:* Simplified Hybrid  $\pi$  Equivalent Circuit of Junction Transistor in Common Emitter Configuration (Pozar, 2011)

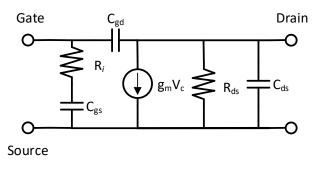

As mentioned, the other type of transistor is the Field Effect Transistor (FET). These devices come in various device types (Metal Semiconductor FET, Metal Oxide Semiconductor FET, and High Electron Mobility Transistor). The device acts as a voltage-controlled voltage source. This principle means that as the gate's input voltage is adjusted, the device changes the source voltage. *Figure 2.18* is the equivalent circuit for a FET in a common source configuration. Metal Semiconductor FET's (MESFET's) are one of the enabling technologies for microwave applications. The GaAs topology allows for excellent electron mobility and, thus, high-frequency operation. Along with the increased frequency range, the device's high electron mobility characteristics eliminate shot noise present in BJT devices (Pozar, 2011).

The Metal Oxide Silicon FET (MOSFET) is one of the most common FET's. The MOSFET is similar to MESFET's but with an additional insulating layer between the gate and channel. This type of device does not have the same frequency range or power handling as other FET's but is simple to bias and very cost-effective for lower-powered applications. The High Electron Mobility Transistor (HEMT) is a heterojunction FET. The principle behind it is the same as an HBT. The semiconducting layer is broken up into different materials to achieve a better frequency response while also having high power handling capabilities (Pozar, 2011).

*Figure 2.18:* Small-signal Equivalent Circuit for FET in Common-source Configuration (Pozar, 2011)

Each transistor has its strengths and weaknesses and must be chosen carefully depending on the application. *Table 2.2* summarizes and compares all the mentioned transistor types.

| Device                 | BJT   | HBT    | CMOS  | MESFET | HEMT   | HEMT   |

|------------------------|-------|--------|-------|--------|--------|--------|

| Semiconductor          | Si    | SiGe   | Si    | GaAs   | GaAs   | GaN    |

| Frequency range (GHz)  | 10    | 30     | 20    | 60     | 100    | 10     |

| Typical gain (dB)      | 10-15 | 10-15  | 10-20 | 5-20   | 10-20  | 10-15  |

| Noise figure (dB)      | 2.0   | 0.6    | 1.0   | 1.0    | 0.5    | 1.6    |

| (frequency, GHz)       | (2)   | (8)    | (4)   | (10)   | (12)   | (6)    |

| Power capacity         | High  | Medium | Low   | Medium | Medium | High   |

| Cost                   | Low   | Medium | Low   | Medium | High   | Medium |

| Single-polarity supply | Yes   | Yes    | Yes   | No     | No     | No     |

Table 2.2: Performance Characteristics of Transistors (Pozar, 2011)

### 2.4.1.5 <u>Transistor Impedances</u>

One thing to note is that each transistor is different and will have different typical impedances at different frequencies. Meaning there are no general values of impedances for transistors. It is typically easier to get the scattering parameters of a particular transistor and use those to calculate the impedance than to try and model the transistor (Pozar, 2011).

### 2.4.2 Amplifier Classes

With all transistors used in RF applications, the amplifier must be biased to achieve the desired amplification. The different biasing techniques define the different "Classes" of amplifiers.

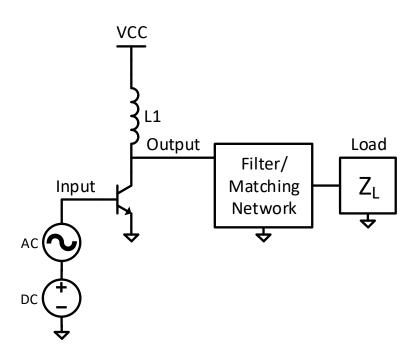

# 2.4.2.1 Class A Amplifier

Class A amplifiers are a class of linear amplifiers that runs a transistor in its linear region all the time. The transistor in this amplifier acts as a current source controlled by the gate voltage, which is biased into allowing the transistor always to be conducting. When a sine wave passes through the amplifier, the transistor will pass the entire wave out, assuming no violation of the amplifier's gain design. Another way to state this is that the transistor has a conduction angle of 360° (Kazimierczuk, 2015). Class A amplifiers are typically the least efficient amplifier with a theoretical max at 50% efficiency (Raab, et al., 2002).

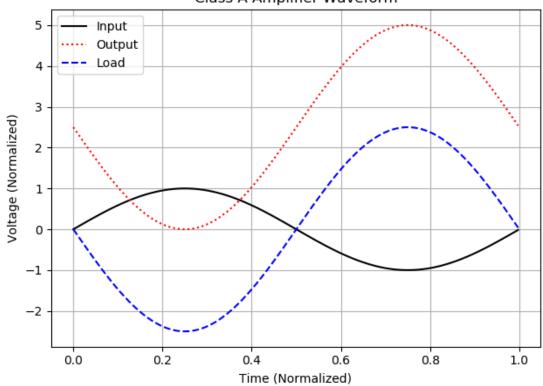

On the other hand, Class A amplifiers offer high gain, good linearity, and operate up to the transistors maximum frequency (Raab, et al., 2002). *Figure 2.19* shows a standard class A amplifier. Note that there are two voltage sources in series. The DC source is used to bias the transistor into its conduction region, and the AC source is the RF input signal that will modulate the transistor. *Figure 2.20* shows the waveform of this circuit (Kazimierczuk, 2015). Here the amplifier gain was set to 2.5. The time and voltage scales are normal for generalization purposes. Assume a DC blocking section of the filter/matching network stage to remove the DC offset caused by the single-sided amplifier design.

Figure 2.19: Class A Amplifier Basic Design

Class A Amplifier Waveform

Figure 2.20: Class A Amplifier Output Waveform

# 2.4.2.2 Class B Amplifier

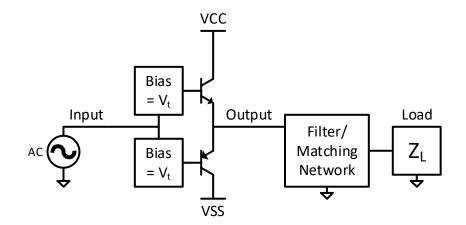

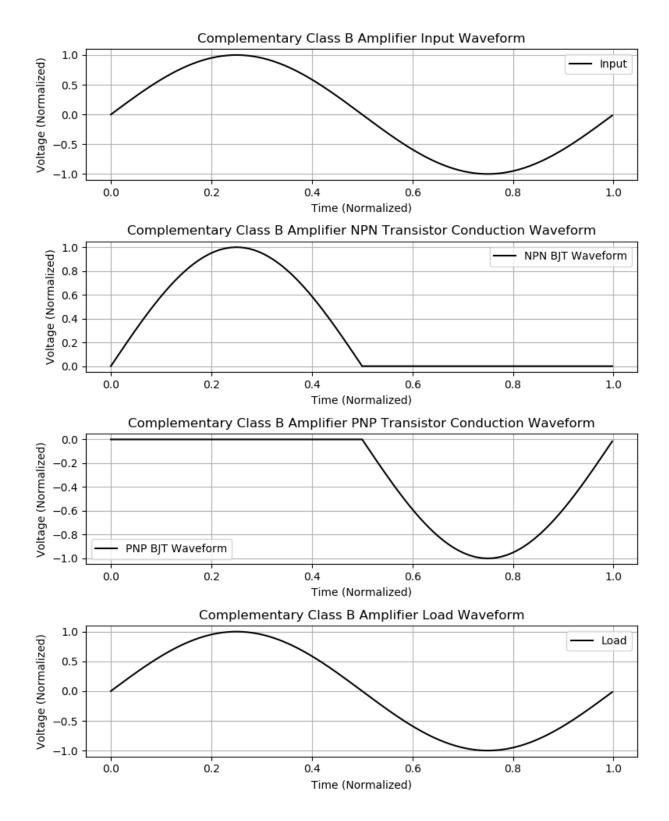

Class B amplifiers are another form of a linear amplifier, but unlike Class A, where the transistor is biased into conduction for both the positive and negative cycles of a sine wave. Class B Amplifiers are biased at its conduction threshold  $(V_t)$ , so it only transmits half the wave (Kazimierczuk, 2015) to the load. Due to each transistor's conduction angle being 180°, these kinds of amplifiers have a higher efficiency than Class A amplifiers, upwards of 78%. Currently, Class B amplifiers are standard in wideband applications (Raab, et al., 2002). Two complementary transistors are required for the amplifier because each is biased to output only half of the waveform. This configuration is known as a complementary amplifier. This topology allows for the recreation of most of the entire waveform. One issue with this amplifier is that both transistors are off at the zero-crossing, causing a small amount of distortion (Kazimierczuk, 2015). Figure 2.21 shows the basic circuit design for a complimentary Class B amplifier. The boxes that state "Bias =  $V_t$ " are placeholders for circuits that would be used to bias that transistor to its threshold voltage. Figure 2.22 shows the common voltage waveforms of a Class B Amplifier (Kazimierczuk, 2015). Note for the waveforms that state either "NPN Transistor Conduction Waveform" or "PNP Transistor Conduction Waveform"; the flat line is when the transistor is no longer conducting. One sees that each waveform for each transistor starts and stops conducting at exactly the zero crossing.

Figure 2.21: Class B Complementary Amplifier Basic Design

Figure 2.22: Class B Amplifier Waveforms

### 2.4.2.3 <u>Class AB amplifier</u>

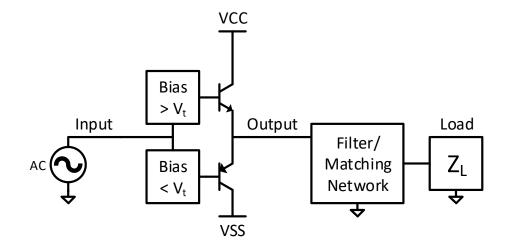

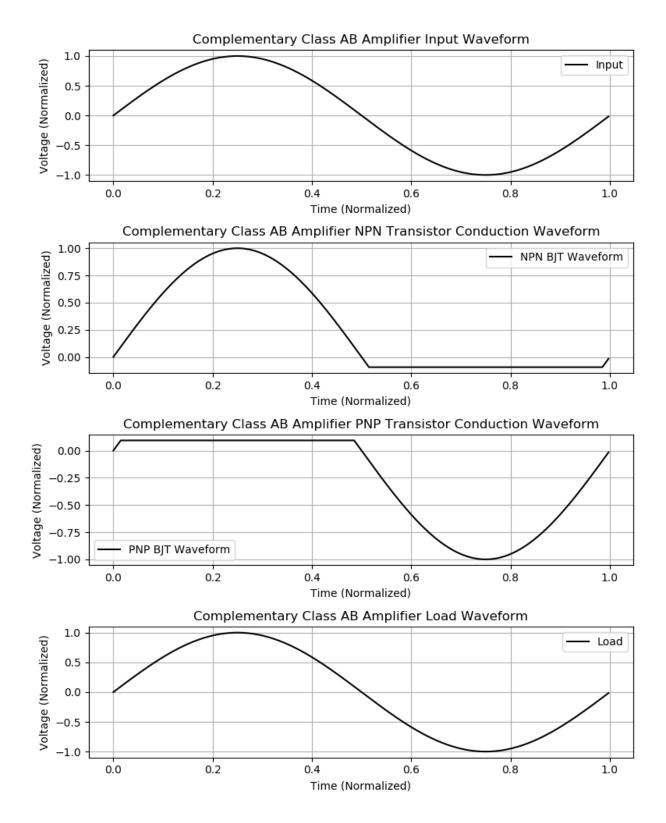

Class AB amplifiers are a combination of Class A and Class B Amplifiers. This classification is similar to Class B amplifiers in that each transistor only conducts for part of the input waveform. However, it is related to Class A amplifiers in that each transistor conducts more than half of the waveform. A Class AB amplifier's conduction angle is between 180° and 360° (Raab, et al., 2002). Each transistor is biased just beyond its threshold voltage to begin the transistor's conduction early. The efficiency of this amplifier sits between Class A and Class B. Each transistor is only conducting part of the time, unlike Class A, which is all the time but is not as efficient as Class B since each transistor is conducting more than that configuration. An advantage of this amplifier is that it fixes Class B amplifiers' distortion at the zero crossing by allowing both transistors to be still conducting (Kazimierczuk, 2015). *Figure 2.23* shows the basic design of a Class AB complementary amplifier.

Note that the bias blocks here have the same effect as in the Class B amplifier section but are adjusted to conduct the transistors before reaching the threshold voltage. *Figure 2.24* shows the typical voltage waveforms of this amplifier class (Kazimierczuk, 2015). The flat portions of the "NPN Transistor Conduction" and "PNP Transistor Conduction" waveforms are when the transistors are no longer conducting.

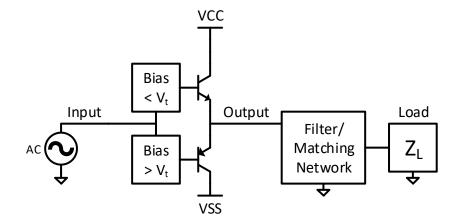

Figure 2.23: Class AB Complementary Amplifier Basic Design

Figure 2.24: Class AB Amplifier Waveforms

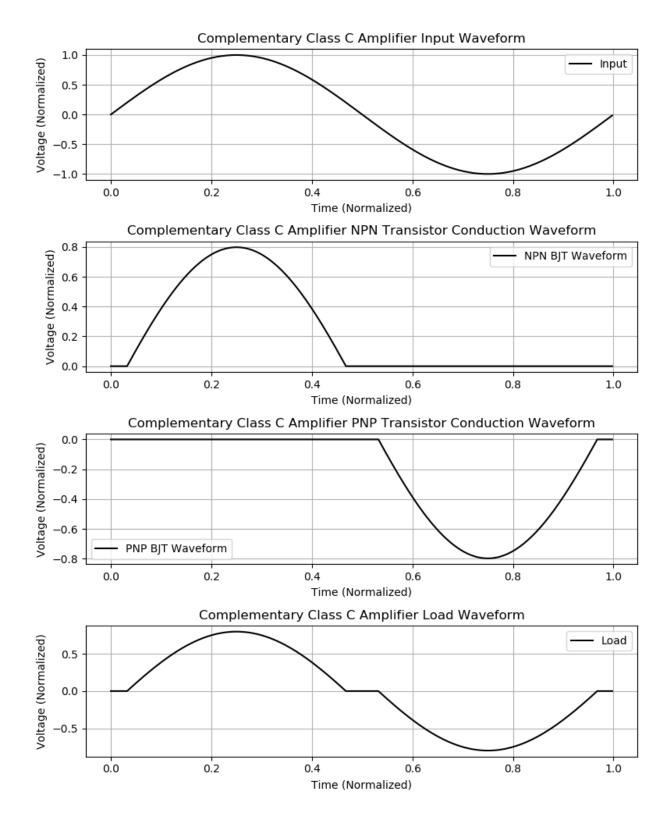

# 2.4.2.4 Class C Amplifier

Class C amplifiers are the last form of linear amplifiers to be covered. These amplifiers have the highest efficiency and worst linearity out of all the previously mentioned linear amplifiers. This amplifier class can almost reach 100% efficiency by changing when the transistors will begin conducting. The bias of each transistor is below its respected threshold voltage. A typical conduction setting for this amplifier is to set the threshold to occur when the input waveform is conducting for 150°. This conduction angle gives the amplifier efficiency of 85%, which means that each transistor will conduct less than half of each waveform cycle. Due to the waveform not being entirely recreated, this amplifier adds a significant distortion to the amplified signal. Class C amplifiers are only commonly found in vacuum tube transmitters or when the transmitted wave has a constant envelope (Raab, et al., 2002). Figure 2.25 shows the basic design of a Class C Amplifier. It shares the same topology as the Class B and AB amplifier, but the Bias blocks are below the transistor's threshold voltage. Figure 2.26 shows the typical waveforms of this type of amplifier (Kazimierczuk, 2015). As in the previous designs, the flat sections of the "NPN Transistor Conduction" and "PNP Transistor Conduction" are when those transistors are not conducting. The load and output voltage are identical as well in this amplifier design.

Figure 2.25: Class C Complementary Amplifier Basic Design

Figure 2.26: Class C Amplifier Waveforms

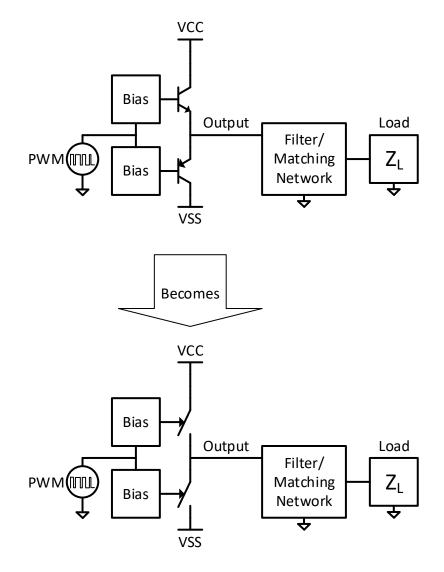

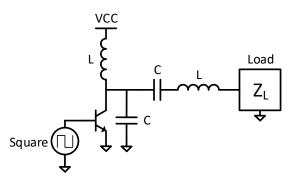

### 2.4.2.5 <u>Class D Amplifier</u>

Class D amplifiers fall under the classification of "Switching" amplifiers. This amplifier implements a complementary amplifier design. However, unlike the previous classes of amplifiers, each transistor will be driven into saturation, causing it to act like a switch rather than a variable source. In saturation, the transistors' resistance is minimal compared to when it is conducting in its linear region. The reduction in transistor losses leads to improved efficiencies.

This amplifier requires the input to be a PWM signal that is proportional to its output. The amplifier's output is a PWM version of the desired signal, and it must pass through a low pass filter. The filter removes the high-frequency switching and instead passes only the fundamental frequency out of the amplifier. Also, because the transistors are going into saturation, the drain to source capacitance becomes a significant issue and limits the maximum switching speed.

The switching speed needs to be several orders of magnitude higher than the desired output frequency, or else the amplifier output will show the PWM signal. Slow switching speeds lead to linearity and distortion problems. Also, if the amplifier is switching fast enough, it will spend more time in its linear region than in its saturation state, which will cause the efficiency of the amplifier to go down as well. This amplifier's realistic implementations only up to 1GHz (Raab, et al., 2002).

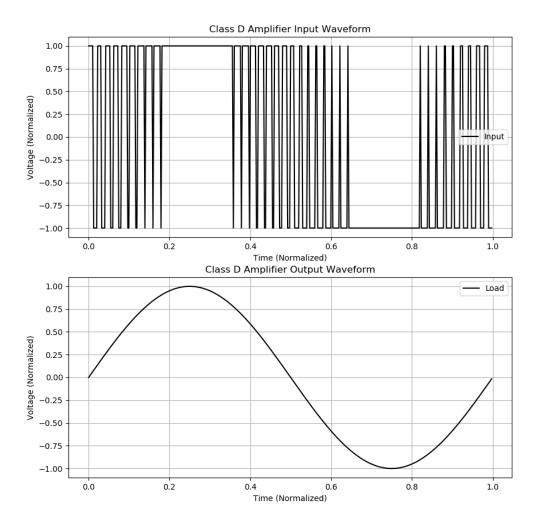

*Figure 2.27* shows the basic design of a Class D amplifier. The bias circuitry avoids the transistors' cross conduction and drives the transistors into saturation (Kazimierczuk, 2015). Note that the transistors effectively become switches in this figure, represented by the arrow showing the transformation. *Figure 2.28* shows the input and filtered output of a Class D amplifier to remove the PWM signal. The PWM input is the direct representation of a sine wave at the normalized frequency and voltage.

Figure 2.27: Class D Amplifier Basic Design

Figure 2.28: Class D Amplifier Waveforms

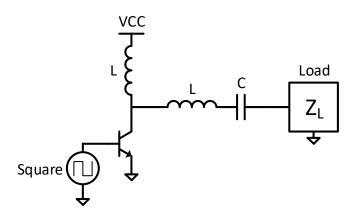

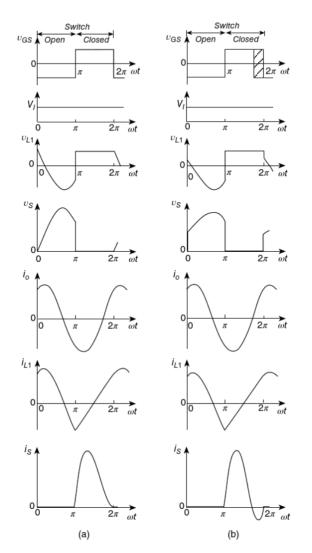

# 2.4.2.6 Class E Amplifier

The Class E amplifier is another form of switching amplifier. It can come in two configurations zero voltage and zero current switching. The amplifier operates by switching the transistor on and off at a set time and uses it to charge and discharge a resonating circuit. The resonating circuit takes the switched wave, turns it into an AC wave, and transmits it to the load. The resonating circuit is highly dependent on frequency and load impedance. When tuned correctly, the transistor switches at the zero crossings for either the current or the voltage. Any misalignment in this causes the amplifier to lose efficiency. Though incredibly efficient, the amplifier does not have a broad bandwidth and has a limited overall frequency range. *Figure*

2.29 and *Figure 2.30* show the circuit for a Class E Zero Voltage Crossing Amplifier and its subsequent waveforms. *Figure 2.31* and *Figure 2.32* show the circuit for a Zero Current Crossing amplifier and its waveforms. The output of the amplifier should be sinusoidal (Kazimierczuk, 2015).

Figure 2.29: Class E Zero Voltage Crossing Amplifier

*Figure 2.30:* Waveforms for a Zero Voltage Crossing Amplifier. A) Optimum Operation. B) Below 50% Duty Cycle. C) Above 50% Duty Cycle. (Kazimierczuk, 2015)

Figure 2.31: Class E Zero Current Crossing Amplifier

*Figure 2.32:* Zero Current Crossing Class E Amplifier Waveforms: A) Optimum Operation. B) Suboptimum Operation (Kazimierczuk, 2015)

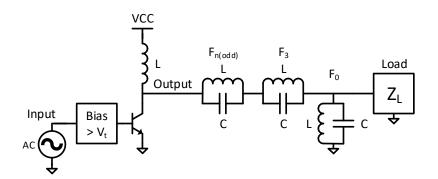

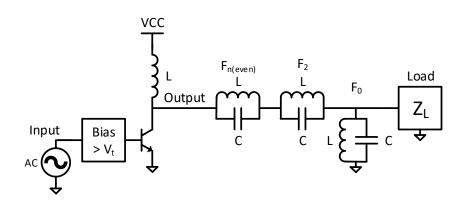

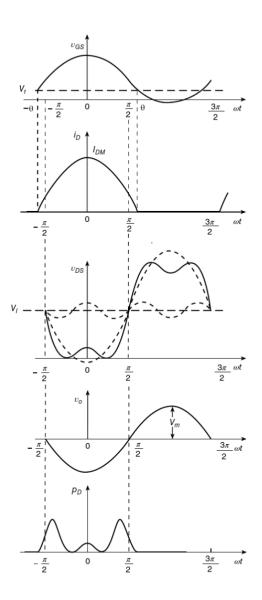

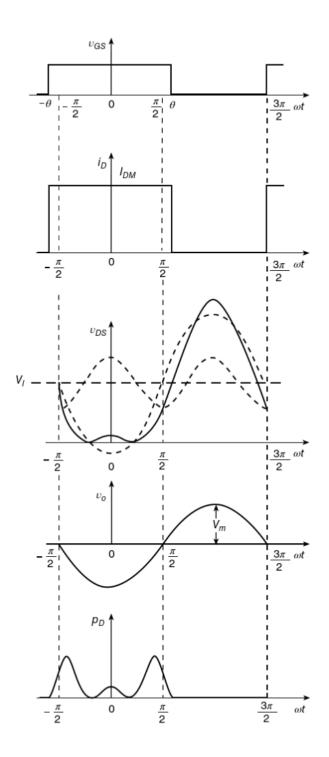

### 2.4.2.7 <u>Class F Amplifier</u>

Class F amplifiers use output harmonic resonators to create a square wave and then filter it back to a sine wave. There are two kinds of Class F amplifiers; these are standard and inverse. The standard Class F amplifier uses a partially saturated transistor and odd harmonic resonators to present a high impedance to the output's voltage waveform. The resonators reflect the transistor's voltage wave at the specified harmonics, causing it to combine into a square wave with the fundamental frequency. The current sees a short through all odd harmonics and high impedances at even harmonics combining into a half-sine current waveform. Using more harmonics allows for a better approximation of a square wave at the transistor's drain. This configuration, in turn, yields higher efficiency (Kazimierczuk, 2015).

Each harmonic resonator is placed in series starting with the highest harmonic closest to the drain (Raab, et al., 2002). The inverse Class F amplifier uses even harmonics to create the voltage waveform, which resembles a half-sine and odd harmonics to generate a square wave. The more harmonics used, the better the efficiency (Grebennikov, Sokal, & Franco, Switchmode RF Power Amplifiers, 2007).

This type of amplifier can be complex to design, and it only operable at specific frequencies. *Figure 2.33* shows the circuit for a Class F amplifier and the inverse Class F amplifier in *Figure 2.34*. The waveforms for a Class F amplifier are *Figure 2.35*, and the Inverse Class F amplifier waveforms *Figure 2.36*.

Figure 2.33: Class F Amplifier

Figure 2.34: Inverse Class F Amplifier

Figure 2.35: Class F Amplifier Typical Waveforms (Kazimierczuk, 2015)

Figure 2.36: Inverse Class F Amplifier Typical Waveforms (Kazimierczuk, 2015)

# 2.4.3 Power Amplifier Summary

Typical power amplifier designs use either class A, AB, or B for low distortion, frequency range, and high linearity, even with lower efficiencies (Pozar, 2011). *Table 2.3* shows a comparison of all discussed power amplifier classes.

| Amplifier<br>Class | Pros                                                               | Cons                                                                                                                                                 |

|--------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| А                  | <ul><li>High Linearity</li><li>Wide Frequency Operation</li></ul>  | Low Efficiency                                                                                                                                       |

| В                  | • Wide Frequency Operation                                         | <ul><li>Medium Linearity</li><li>Medium Efficiency</li></ul>                                                                                         |

| AB                 | <ul><li>High Linearity</li><li>Wide Frequency Operation</li></ul>  | Medium Efficiency                                                                                                                                    |

| С                  | <ul><li>High Efficiency</li><li>Wide Frequency Operation</li></ul> | Low Linearity                                                                                                                                        |

| D                  | High Efficiency                                                    | <ul><li>For sub 1GHz designs only</li><li>Not linear</li></ul>                                                                                       |

| E                  | • High Efficiency                                                  | <ul> <li>Low range of frequency operation<br/>due to harmonic resonators</li> <li>Sensitive to changes in output load</li> <li>Not linear</li> </ul> |

| F                  | • High Efficiency                                                  | <ul> <li>Not linear</li> <li>Low range of frequencies due to harmonic resonators</li> </ul>                                                          |

*Table 2.3:* Power Amplifier Summary

#### 2.5 <u>Tunable Elements</u>

Components that can vary their value based on a controlled input are an enabling technology for tunable matching networks. The capacitors and inductors of static matching networks are replaced with these tunable components and allow the matching network's properties to be adjusted. This section covers the different types of tunable capacitors and inductors available.

### 2.5.1 Tunable Capacitors

This section outlines the different types of tunable capacitors and can be considered a direct drop-in replacement for matching network capacitors.

### 2.5.1.1 <u>Micro Electro-Mechanical System (MEMS) Capacitor</u>

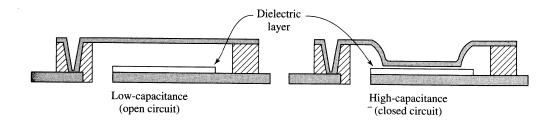

MEMS capacitors are a mechanical-based type of variable capacitor. It consists of two conductive layers that are parallel to each other. One layer is stationary while the other layer is allowed to move. A DC bias voltage is applied to the device, changing how close the two plates are to one another. The distance changes the device's capacitance (Li, Zhang, Miao, Li, & Zhao, 2006). *Figure 2.37* shows the crossectional view of a MEMS capacitor in its two states.

MEMs capacitors operate on the order of 40GHz+ (Peroulis & Katehi, 2003) and power ranging from a few hundred microwatts ( $100\mu$ w) to a few Watts (Cruau, Tassetti, Nicole, & Lissorgues, 2003). MEMS capacitors also offer "good loss characteristics, very low power consumption, and wide bandwidths, and (unlike diode or transistor switches) exhibit virtually no intermodulation distortion" (Pozar, 2011). Due to the nature of MEMs, the theoretical tuning resolution is infinite; however, typically, only two states are achieved out of a MEMS capacitor, creating more of a switched capacitor. Devices that incorporate MEMS capacitors have several in an array to switch between to create a more fine resolution that is  $2^n$  where "n" is the number of MEMS components. Another theoretical advantage of MEMS is that the device can have upwards of 100:1 tuning range; however, in a practical application, the tuning range is closer to 2-5:1 (Qin & Barker, 2006). The device's mechanical nature slows down the tuning time to  $30+\mu$ s and limits the part's life (Pozar, 2011).

Figure 2.37: MEMS Capacitor (Pozar, 2011)

# 2.5.1.2 Varactor Diodes

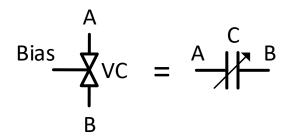

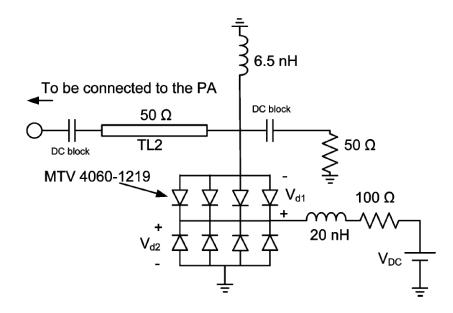

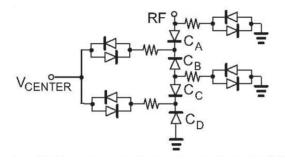

Varactors have been around for decades and found uses in various applications, oscillators, antenna tuners, and tunable filters (Buisman, et al., 2007). *Figure 2.38* shows the diode model of a varactor with a typical back-to-back configuration. A varactor diode consists of a reversed biased diode, doped to provide a specific capacitance versus voltage (CV) curve, and placed in series, common cathode, with another varactor (Pozar, 2011). Varactors rely on applying a DC voltage to the bias line of the varactor. As the voltage changes, so does the capacitance of the device. This effect gives the device a theoretically infinite tuning resolution though the voltage source resolution limits it.

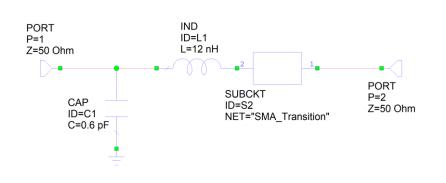

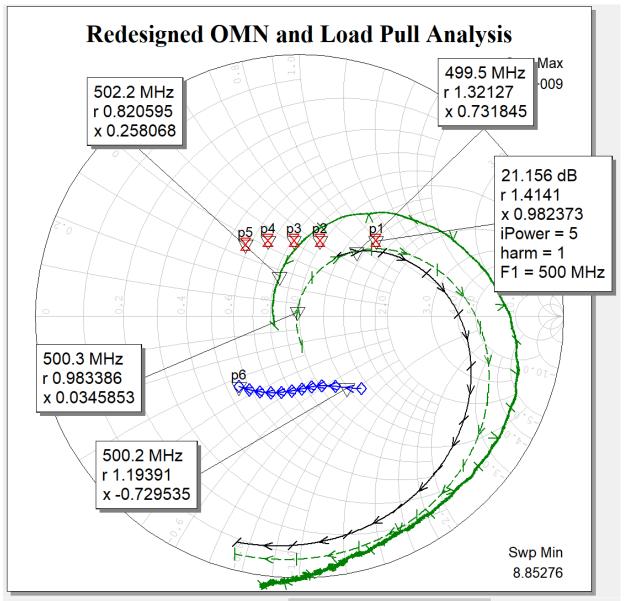

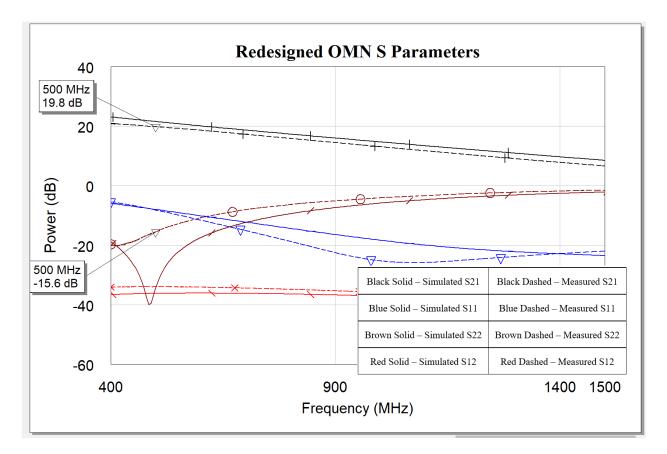

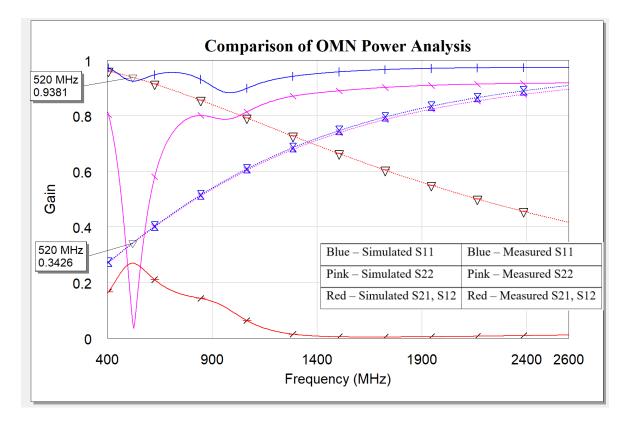

The device's solid-state nature allows quick tuning times on the order of 1-100 nanoseconds (Huang, et al., 2010). The low voltage required for operation and no junction noise make varactors ideal for low-power systems (Bahl, 2003). Varactors have a much higher capacitance density than MEMS components though it comes at the cost of nonlinearities in the CV tuning curve (Huang, et al., 2010). The other disadvantage of the varactor is that as the system power increases tuning range decreases. The degradation in power handling occurs as the RF signal's voltage interferes with the varactor's bias as RF energy passes through the device. Essentially the varactor needs to be biased with a large enough voltage that the effect of the added RF voltage is negligible.