## A PROCESS FOR HYBRID SUPERCONDUCTING AND GRAPHENE DEVICES

by

Zachary Cochran

A Thesis

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Master of Science

Department of Electrical and Computer Engineering Indianapolis, Indiana May 2021

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

Dr. Maher Rizkalla, Chair

Department of Electrical and Computer Engineering

### Dr. Trond Ytterdal

Department of Electronic Systems, Norwegian University of Science and Technology

### Dr. Lauren Christopher

Department of Electrical and Computer Engineering

### Approved by:

Dr. Brian King

## ACKNOWLEDGMENTS

I would like to thank my thesis committee Chair, Dr. Maher Rizkalla, and thesis committee member, Dr. Trond Ytterdal for the exceptional guidance and support throughout my work on this thesis, plus the constructive conversations regarding suggestions and ideas for this topic. I would also like to thank Dr. Lauren Christopher, also on my committee, for her guidance and insights into VLSI, especially with the courses on that subject, which were foundational to a large portion of this work. I would also like to thank Sherrie Tucker and Jane Simpson for their guidance as the Graduate and Undergraduate Advisors, respectively, in the Indiana University-Purdue University (IUPUI) ECE Department, without whom I would have not had any clear direction of what to do to earn my degrees. Finally, I would also like to thank Dr. Yogesh Joglekar, from the IUPUI Physics Department, without whose support I would have never started doing research, or grown into a researcher.

# TABLE OF CONTENTS

| LI | ST O  | F TAB  | LES                                                                       | 7  |

|----|-------|--------|---------------------------------------------------------------------------|----|

| LI | ST O  | F FIGU | JRES                                                                      | 8  |

| LI | ST O  | F SYM  | BOLS                                                                      | 12 |

| AI | BBRE  | VIATI  | ONS                                                                       | 14 |

| N  | OME   | NCLAT  | URE                                                                       | 16 |

| GI | LOSS. | ARY .  |                                                                           | 17 |

| AI | BSTR  | ACT    |                                                                           | 18 |

| 1  | INTI  | RODUC  | CTION                                                                     | 19 |

|    | 1.1   | Motiva | ation                                                                     | 19 |

|    | 1.2   | Thesis | Problem Statement and Research Issues                                     | 20 |

|    | 1.3   | Presen | t Efforts and Current Work                                                | 20 |

|    | 1.4   | Presen | t Limitations                                                             | 21 |

|    | 1.5   | Thesis | Organization                                                              | 22 |

| 2  | BAC   | KGRO   | UND AND BASIC THEORY                                                      | 24 |

|    | 2.1   | Superc | conducting Devices                                                        | 24 |

|    | 2.2   | Semico | onducting Devices and Nanotechnology                                      | 29 |

| 3  | DEV   | ICE PI | HYSICS, MODELING, AND OPERATION                                           | 33 |

|    | 3.1   | Superc | conductive Devices                                                        | 33 |

|    |       | 3.1.1  | Josephson Junctions                                                       | 33 |

|    |       | 3.1.2  | Wires and Striplines                                                      | 37 |

|    | 3.2   | Nanot  | echnology Devices                                                         | 40 |

|    |       | 3.2.1  | The GNRFET Model                                                          | 40 |

|    |       |        | Model Background                                                          | 40 |

|    |       |        | Effective Capacitances                                                    | 41 |

|    |       |        | GNRFET Device Behavioral Curves                                           | 44 |

|    |       | 3.2.2  | The GNRFET-Based Amplifier                                                | 51 |

|    |       |        | A Simple Two-Stage Amplifier                                              | 51 |

|    |       | 3.2.3  | The GNRFET Amplifier System Stability and a Three-Stage Modifi-<br>cation | 53 |

|   |         |         | Ideal System Simulations                                              |

|---|---------|---------|-----------------------------------------------------------------------|

|   |         |         | Simplified Transmission-Line Effects within the GNRFET Amplifier . 59 |

|   |         | 3.2.4   | Predicted Noise Performance of the GNRFET Amplifier 61                |

|   |         | 3.2.5   | Comparison of the GNRFET Amplifier to Other Technologies 64           |

|   | 3.3     | Norma   | al Conductor Transmission Lines and Characteristic Impedances $65$    |

|   |         | 3.3.1   | Multilayer Substrate Effects    65                                    |

|   |         | 3.3.2   | Microstrip Transmission Lines                                         |

|   |         |         | Background Theory                                                     |

|   |         | 3.3.3   | Planar Inductor                                                       |

|   |         |         | Circuit Theory                                                        |

|   |         | 3.3.4   | Simulation Considerations                                             |

| 4 | DEV     | VICE IN | TERFACING                                                             |

|   | 4.1     | Interfa | ace Limitations                                                       |

|   |         | 4.1.1   | Substrate Limitations                                                 |

|   |         |         | Superconductors                                                       |

|   |         |         | Graphene Nanoribbons                                                  |

|   |         | 4.1.2   | Process Limitations                                                   |

|   |         | 4.1.3   | Superconductor-to-Metal Junctions                                     |

|   | 4.2     | Propo   | sed Schemes                                                           |

|   | 4.3     | EHF 7   | Fransmission Line Analysis    86                                      |

|   |         | 4.3.1   | Directly-Coupled Transmission Lines                                   |

|   |         |         | Superconductive Transmission Lines                                    |

|   |         |         | GNR-based Transmission Lines                                          |

|   |         |         | The Superconductor-GNR Hybrid Line                                    |

|   |         | 4.3.2   | Indirectly-Coupled Transmission Lines                                 |

|   |         |         | Coupled Line Electromagnetic Simulations                              |

|   |         |         | Planar Transformer Electromagnetic Simulations                        |

|   | 4.4     | Conclu  | usions and Proposed Process                                           |

| 5 | FUT     | TURE V  | VORK                                                                  |

| 6 | SUMMARY |         |                                                                       |

| RI | EFER | ENCES                                          | 10 |

|----|------|------------------------------------------------|----|

| А  | SPIC | CE AND VERILOG-A MODELING    14                | 41 |

|    | A.1  | SPICE Model                                    | 41 |

|    | A.2  | Verilog-A Model                                | 42 |

| В  | МАТ  | TLAB MODELING    14                            | 43 |

|    | B.1  | MATLAB Superconducting Transmission Line Model | 43 |

# LIST OF TABLES

| 2.1 | A list of historical and common superconductors.                                                                                                                      | 25 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | A comparison of technologies and their relative performances. A higher figure of merit is better. "-" indicates the data could not be determined or was not provided. | 64 |

| 4.1 | A list of substrates used for superconductive (YBCO) devices at microwave or EHF ranges and cryogenic temperatures. "-" indicates no data found                       | 78 |

| 4.2 | A list of substrates used for GNR and GNRFET devices. "N.A." indicates the relevant information is not applicable for substrate purposes                              | 80 |

| 4.3 | The dimensions used for transmission line simulations here. The values are approximate values, based strongly on values presented in a number of papers.              | 88 |

## LIST OF FIGURES

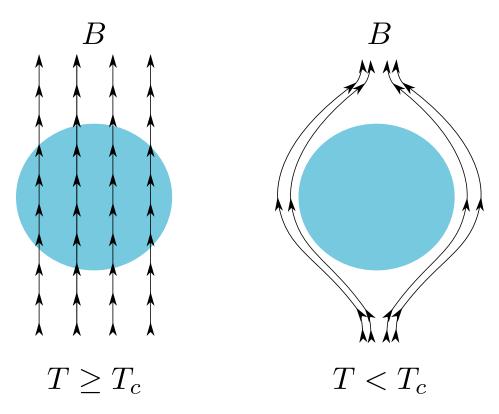

| 2.1 | The Meissner effect on a type-I superconductor, as demonstrated with a round object. The lines of flux, when temperature $T \ge T_c$ , pass through the object and, when $T < T_c$ , pass around the object, completely expelled.                                                                                                                                                                                                                                   | 26 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

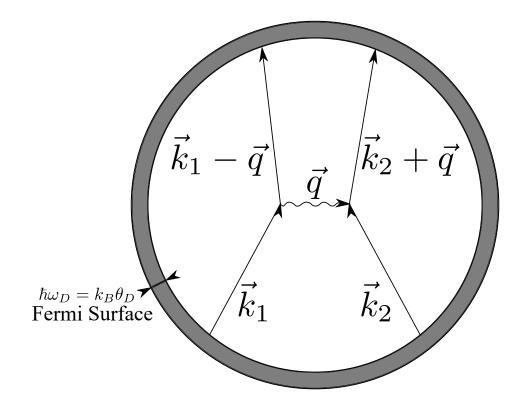

| 2.2 | A simple illustration of a Cooper pair, where $\vec{k}_{1,2}$ are the momentums of electrons "1" and "2," respectively, in the Fermi surface with a maximum energy separation of $\hbar\omega_D = k_B\theta_D$ , where $\theta_D$ is the Debye temperature and $\omega_D$ is the Debye frequency. The interaction with the phonon is represented by the momentum exchange $\vec{q}$ .                                                                               | 27 |

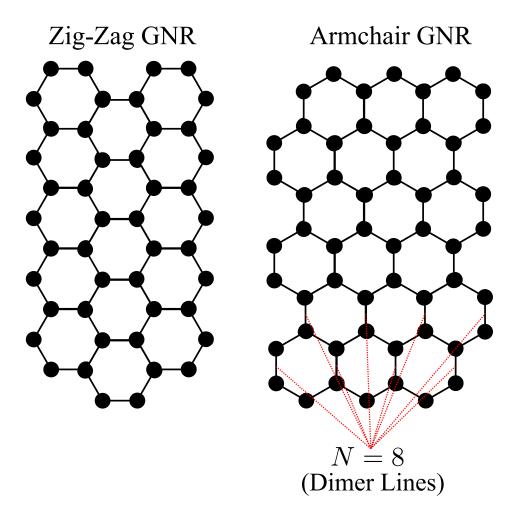

| 2.3 | An illustration of conducting zig-zag GNR (ZZGNR – left) and semiconducting armchair GNR (AGNR – right) with $N = 8$ dimer lines (annotated).                                                                                                                                                                                                                                                                                                                       | 30 |

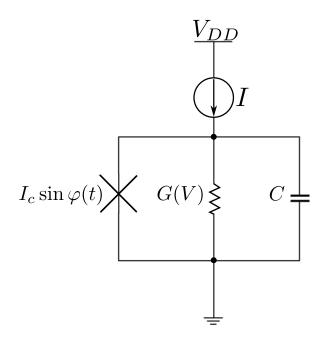

| 3.1 | A schematic-level illustration of the RCSJ Josephson junction model. It consists of an ideal junction $I(t) = I_c \sin \varphi(t)$ , a voltage-dependent conductance $G(V)$ , and a capacitance $C$ .                                                                                                                                                                                                                                                               | 35 |

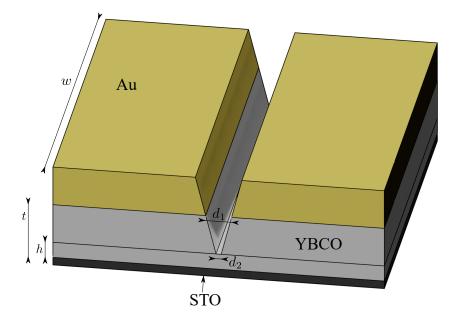

| 3.2 | A diagram of the YBCO Josephson junction using the VTB model, as implemented in Ref. [70]. The substrate originally used was STO, but other substrates may potentially also be utilized, as discussed in Chapter 4.1.                                                                                                                                                                                                                                               | 36 |

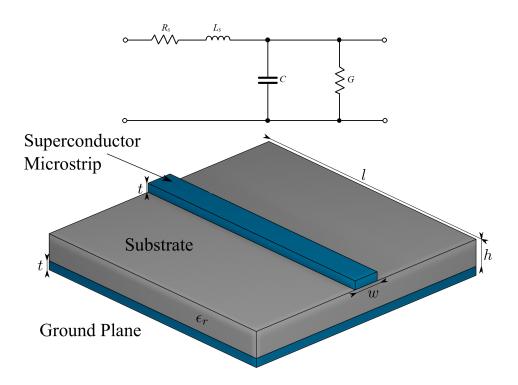

| 3.3 | The superconductor stripline 3D model (bottom) with its equivalent circuit (top)                                                                                                                                                                                                                                                                                                                                                                                    | 39 |

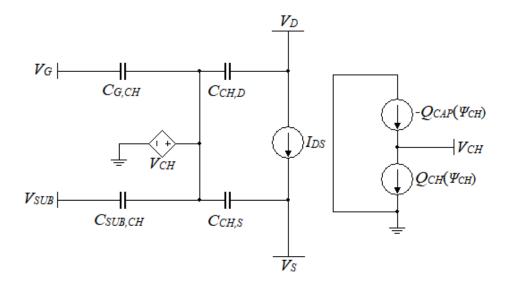

| 3.4 | The equivalent-circuit model of the GNRFET as described in Refs. [29], [30].                                                                                                                                                                                                                                                                                                                                                                                        | 41 |

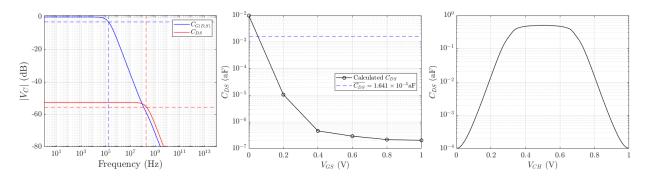

| 3.5 | Simulated outputs used to determine capacitor values. The left image is the magnitude of the output of the low-pass filter, with resulting corner frequencies of 159 kHz ( $C_{G(D,S)}$ ) and 192 MHz ( $C_{DS}$ ). The middle image is the result of simulated Elmore delay to determine $C_{DS}$ , with a mean simulated $C_{DS}$ of $1.6 \times 10^{-3}$ aF. The right image is the calculation of $C_{DS}$ based on channel capacitances and terminal voltages. | 42 |

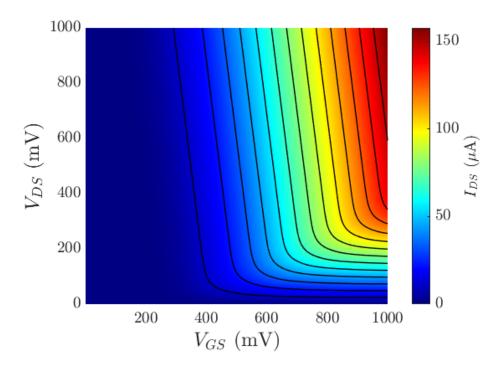

| 3.6 | I-V Surface for $I_{DS}$ as a function of $V_{GS}$ and $V_{DS}$ .                                                                                                                                                                                                                                                                                                                                                                                                   | 44 |

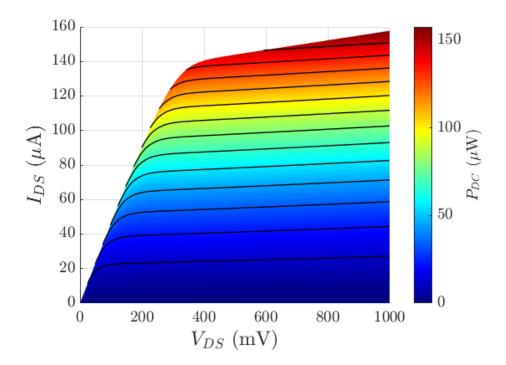

| 3.7 | DC power consumption surface as a function of $V_{DS}$ and $I_{DS}$ . As can be seen,<br>DC power consumption is quite low. In fact, for the range of values utilized<br>here, the GNRFETs individually consume less than 50 $\mu$ W of power                                                                                                                                                                                                                       | 45 |

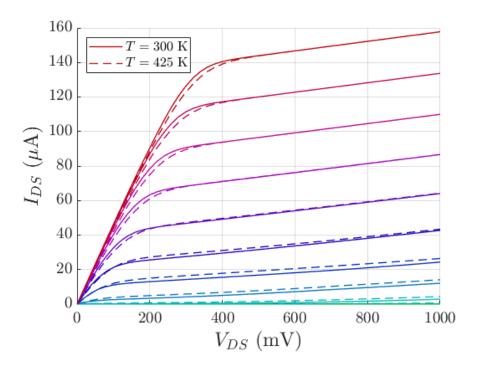

| 3.8 | A comparison between $I_{DS}$ at $T = 300$ K (solid) and $T = 425$ K (dashed), for<br>varying $V_{GS}$ . As can be seen, the difference is minimal between them. $V_{GS}$<br>varies between 0 and 1 V with a step of 0.1 V. Increasing maximum curve                                                                                                                                                                                                                |    |

|     | height corresponds to increasing $V_{GS}$                                                                                                                                                                                                                                                                                                                                                                                                                           | 46 |

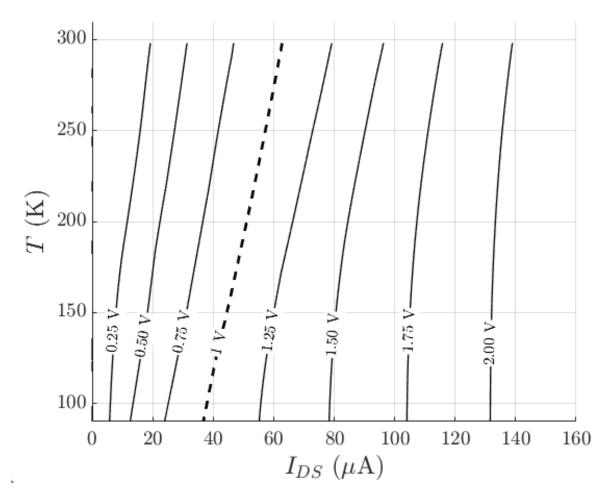

| 3.9  | $V_{DS}$ surface contours as $I_{DS}$ varies from 0 to 160 $\mu$ A and T varies from 90 K to 300 K, with $V_{GS}$ fixed at 300 mV. The dashed line indicates the maximum permitted $V_{DS}$ , indicating that, as temperature increases, the current required to reach that maximum value also increases by almost 20 $\mu$ A, which also increases DC power consumption. |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

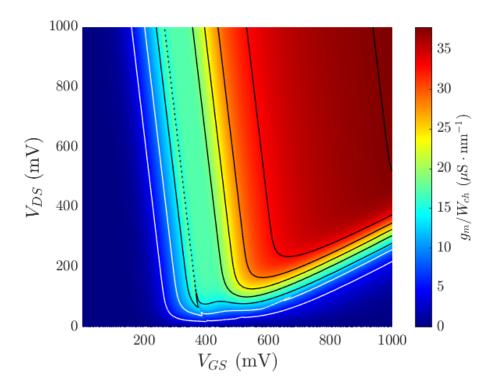

| 3.10 | Transconductance-per-channel width $g_m/W_{ch}$ of the transistor as a function of $V_{GS}$ and $V_{DS}$ . Channel width is $W_{ch} = 1.5987$ nm per nanoribbon $(n_{rib} = 4)$ , for a total width, excluding gaps, of 6.3948 nm                                                                                                                                         |

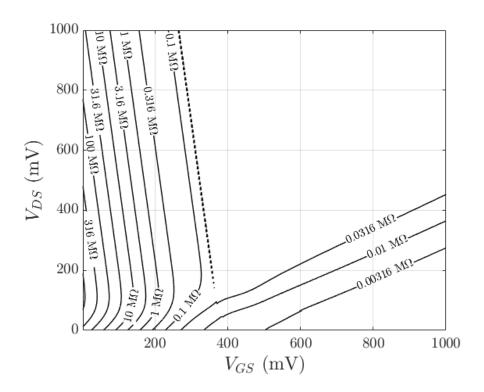

| 3.11 | $r_o$ resistance surface contours as a function of $V_{GS}$ and $V_{DS}$ .                                                                                                                                                                                                                                                                                                |

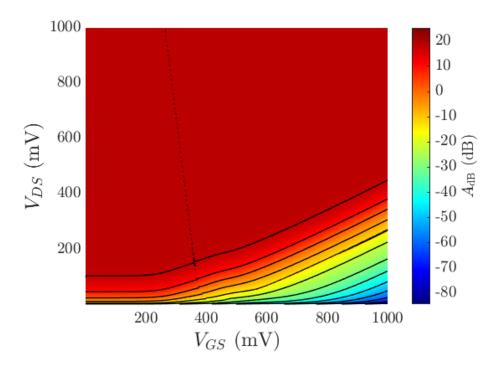

| 3.12 | Autogain (dB) surface as a function of $V_{GS}$ and $V_{DS}$                                                                                                                                                                                                                                                                                                              |

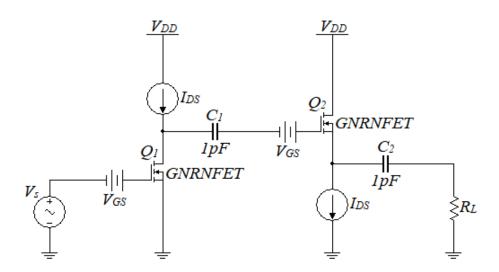

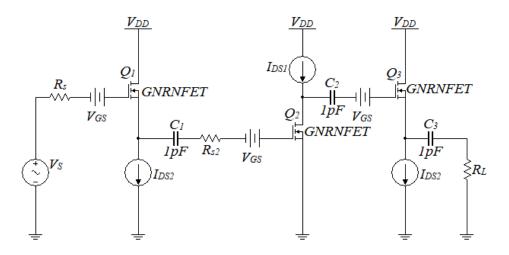

| 3.13 | A simple two-stage amplifier.                                                                                                                                                                                                                                                                                                                                             |

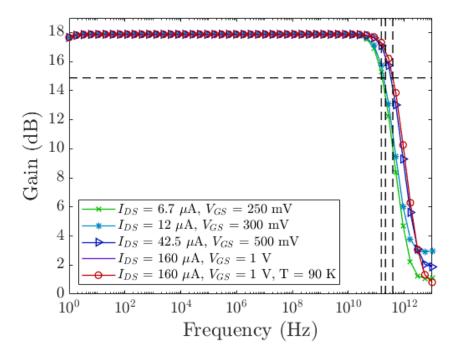

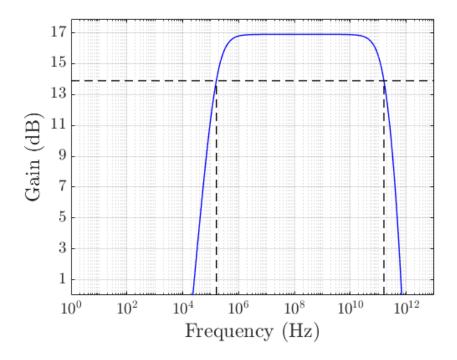

| 3.14 | Unloaded gain for a simple two-stage amplifier.                                                                                                                                                                                                                                                                                                                           |

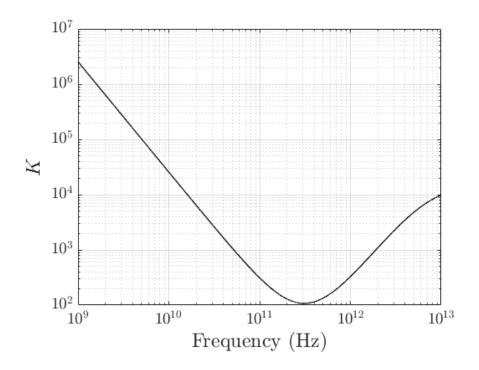

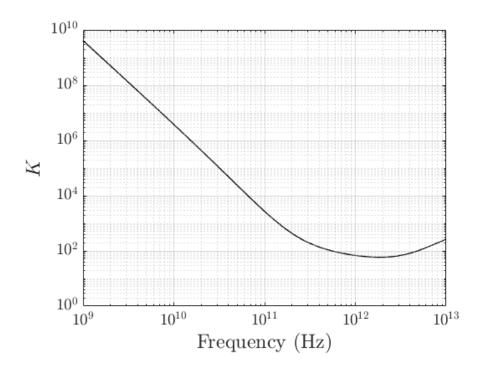

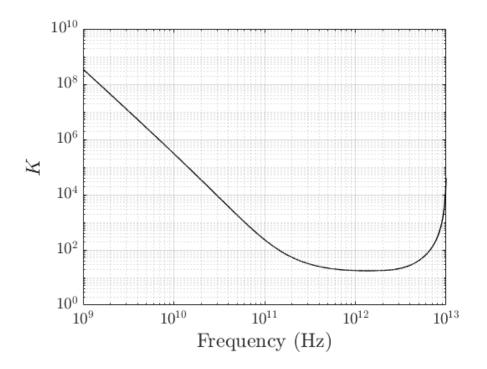

| 3.15 | The Stern stability factor K for the original amplifier, for $R_s = 1.5 \mathrm{k}\Omega$ .                                                                                                                                                                                                                                                                               |

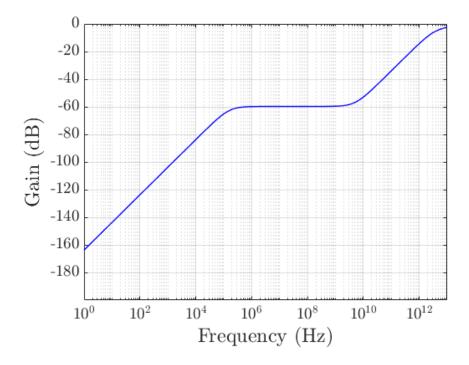

| 3.16 | The new gain for the two-stage amplifier for $R_s = 1.5 \text{ k}\Omega.$                                                                                                                                                                                                                                                                                                 |

| 3.17 | The corrected, 3-stage amplifier. Note the presence of $R_s$ and $R_{s2}$ for noise performance and stability. It was found that $R_{s2} = 0 \Omega$ is an appropriate selection and does not impact stability adversely.                                                                                                                                                 |

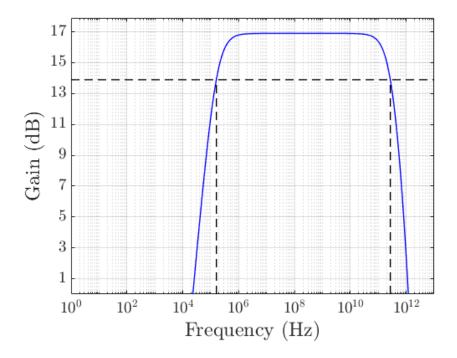

| 3.18 | Gain of the corrected idealized amplifier. The sudden presence of a low-<br>frequency cutoff frequency is very apparent, and should be resolved by an<br>external sag compensation circuit.                                                                                                                                                                               |

| 3.19 | The Stern stability factor $K$ for the idealized three-stage circuit with series resistance $R_s = 16.05 \text{ k}\Omega.$                                                                                                                                                                                                                                                |

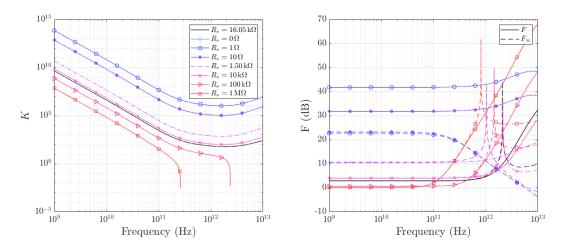

| 3.20 | Demonstration of the trade-off between stability (left) and noise performance (right), the latter of which is discussed in greater detail later. As can be seen, low $R_s$ improves stability greatly, but decreases noise performance (increases noise figure), and vice-versa.                                                                                          |

| 3.21 |                                                                                                                                                                                                                                                                                                                                                                           |

| 3.22 | Gain of the three-stage circuit, $R_s = 16.05 \mathrm{k\Omega}$ , given simplified transmission<br>lines with approximate $R = 150 \Omega$ and $C_{SH} = 9 \mathrm{aF}$ .                                                                                                                                                                                                 |

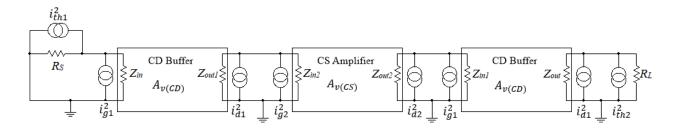

| 3.23 | Equivalent simplified noise model for the three-stage amplifier. Each amplifier stage is represented by an equivalent block with input and output impedances. Current and voltage sources are, for simplicity, considered noiseless.                                                                                                                                      |

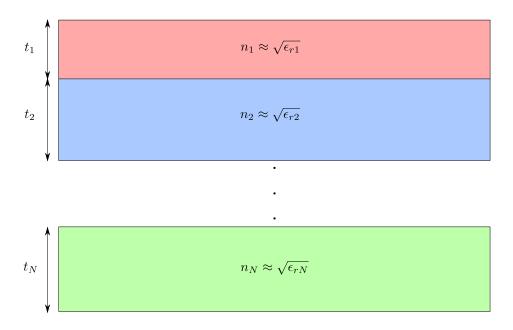

| 3.24 | An illustration of a hybrid/multilayer substrate. The effective permittivity depends on the thicknesses and $\epsilon_r$ of each layer.                                                                                                                                                                                                                                   |

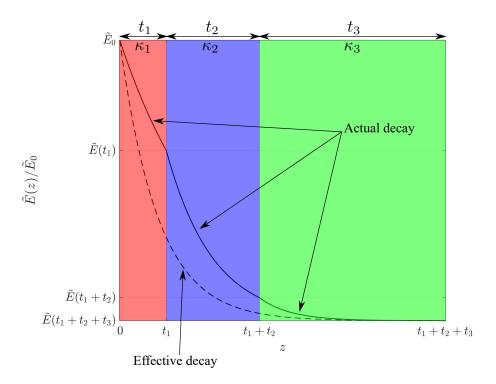

| 3.25 | A demonstration of consecutive field decays.                                                                                                                                                                                                                                                                                                                              |

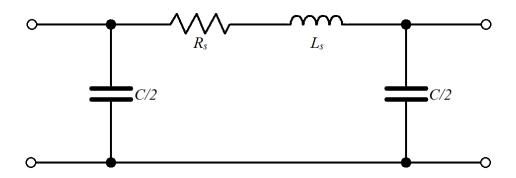

| 3.26 | The equivalent $\Pi$ -model of a simple transmission line $\ldots \ldots \ldots \ldots \ldots$                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

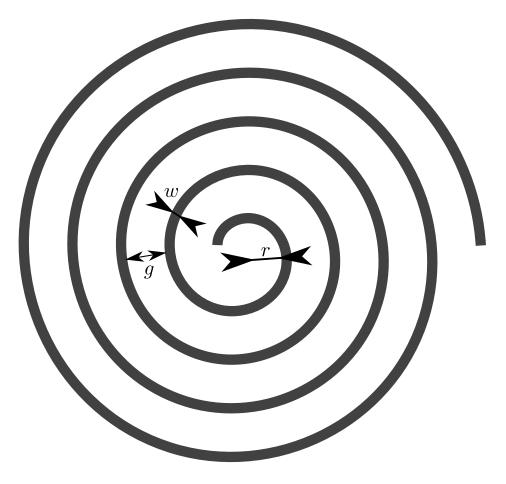

| 3.27 | A 2D spiral inductor.                                                                                                                                                                                                                                    |

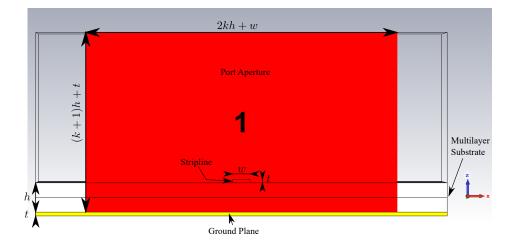

| 3.28 | An illustration of a waveport of the appropriate aperture size, drawn in CST Studio. The "1" is the port number (port "1" of a two-port network)                                                                                                         |

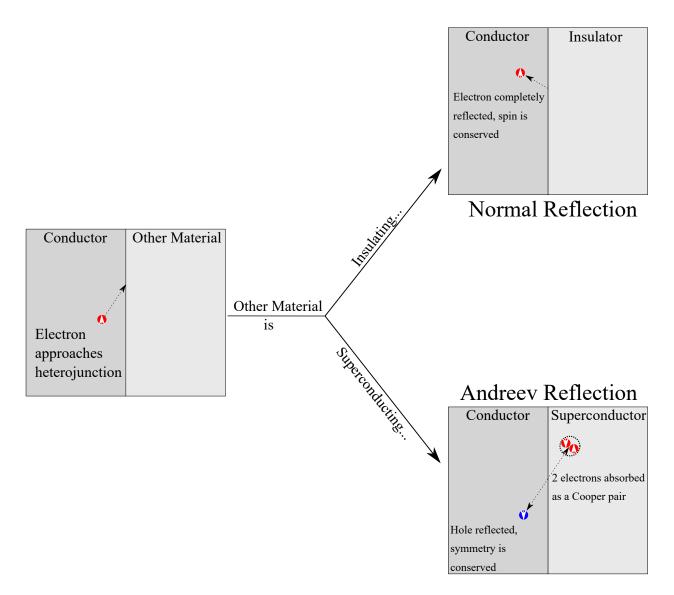

| 4.1  | An illustration of a conductor-insulator/superconductor junction. The insu-<br>lator (top) exhibits normal reflections, while the superconductor (bottom)<br>exhibits Andreev reflections.                                                               |

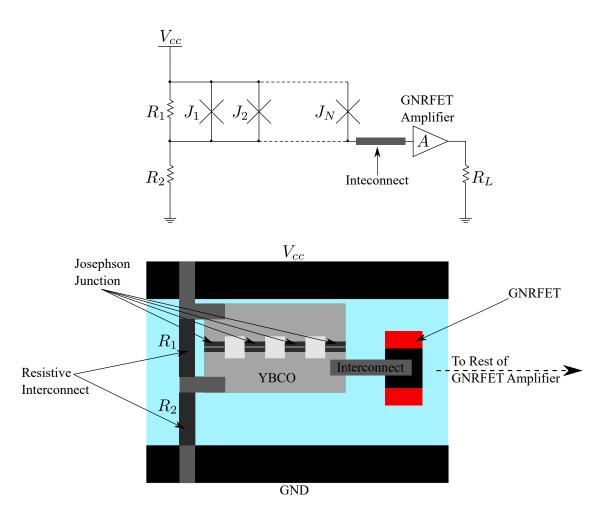

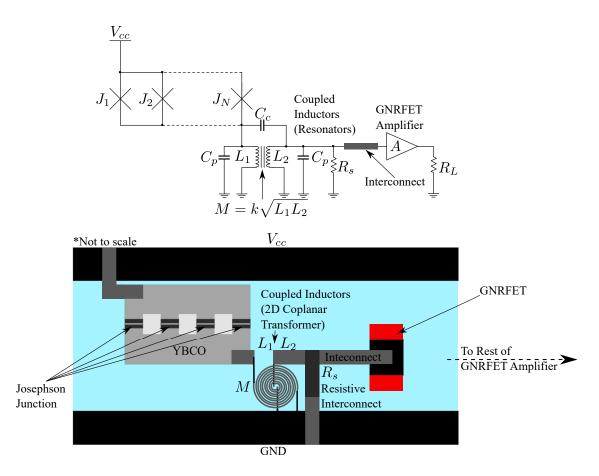

| 4.2  | The schematic and corresponding rough layout for a system that relies upon physical interconnects between the YBCO and GNRFET systems                                                                                                                    |

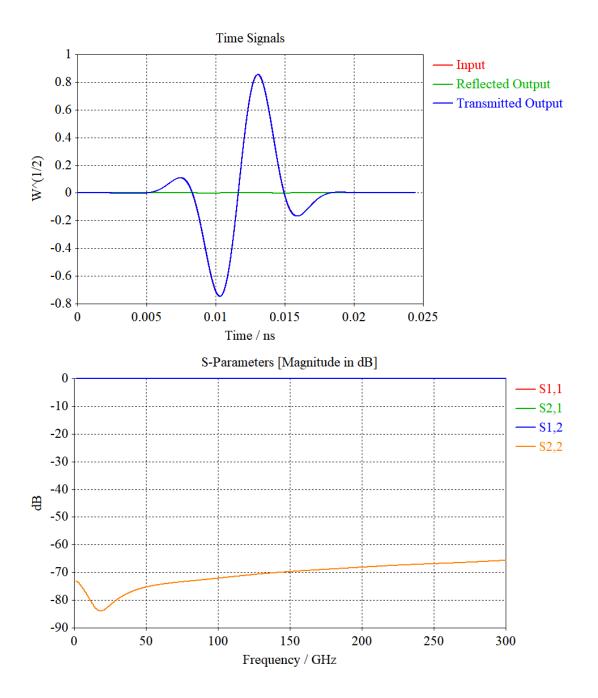

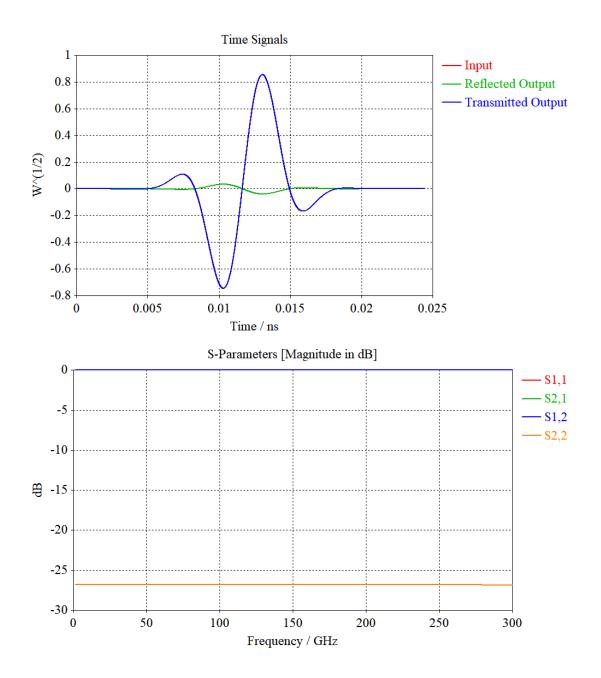

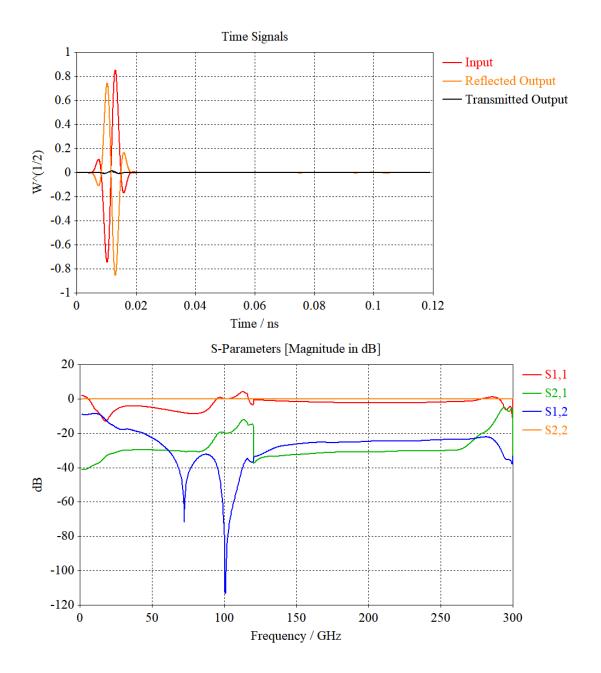

| 4.3  | The input excitation into the superconducting microstrip line and the scat-<br>tered and transmitted outputs (top), and the corresponding S-parameters<br>(bottom)                                                                                       |

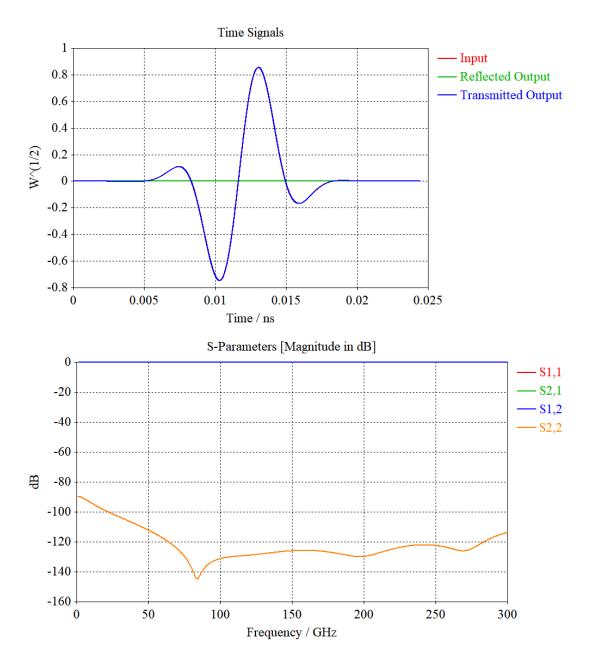

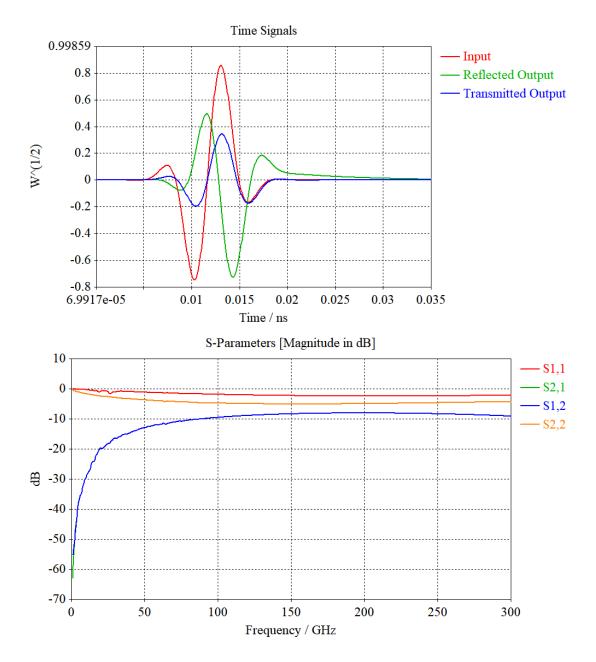

| 4.4  | The input excitation into the graphene microstrip line and the scattered and transmitted outputs (top), and the corresponding $S$ -parameters (bottom).                                                                                                  |

| 4.5  | The input excitation into the hybrid microstrip line and the scattered and transmitted outputs (top), and the corresponding $S$ -parameters (bottom).                                                                                                    |

| 4.6  | The schematic and corresponding rough layout for a system that relies upon<br>coupling between the YBCO and GNRFET systems. The coupling method<br>demonstrated here utilizes a coplanar transformer                                                     |

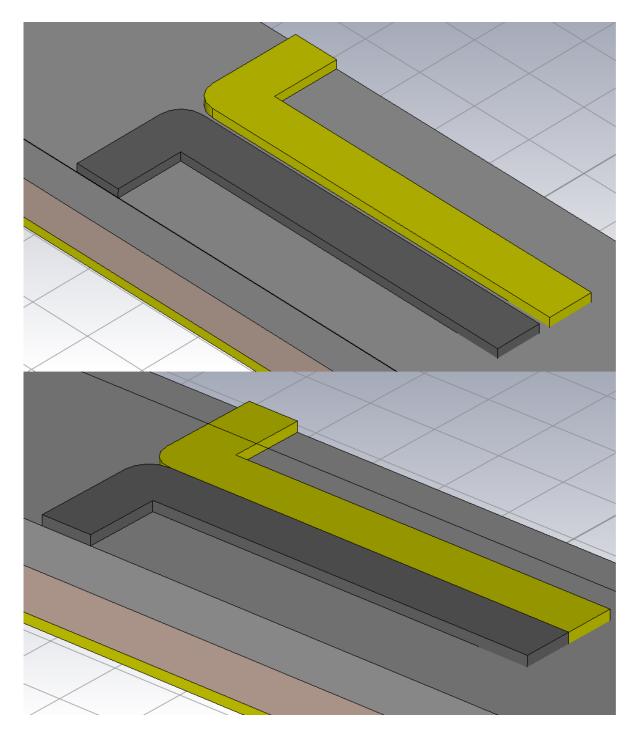

| 4.7  | The 3D layout for the coupled microstrip setup. The ends of the strips are connected to the ground plane by vias. The grey stripline is YBCO, and the yellow one is copper. The top layout has a gap of size $g_c$ , and the bottom layout is gapless.   |

| 4.8  | The input excitation into the coupled microstrip line and the scattered and transmitted outputs (top), and the corresponding $S$ -parameters (bottom).                                                                                                   |

| 4.9  | The input excitation into the direct-contact coupled microstrip line and the scattered and transmitted outputs (top), and the corresponding S-parameters (bottom).                                                                                       |

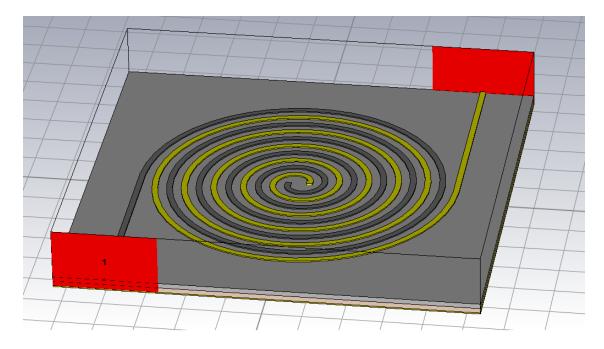

| 4.10 | The 3D layout for the planar transformer. The grey coil is YBCO, and the yellow one is copper. The internal endpoints of both are connected to ground by vias.                                                                                           |

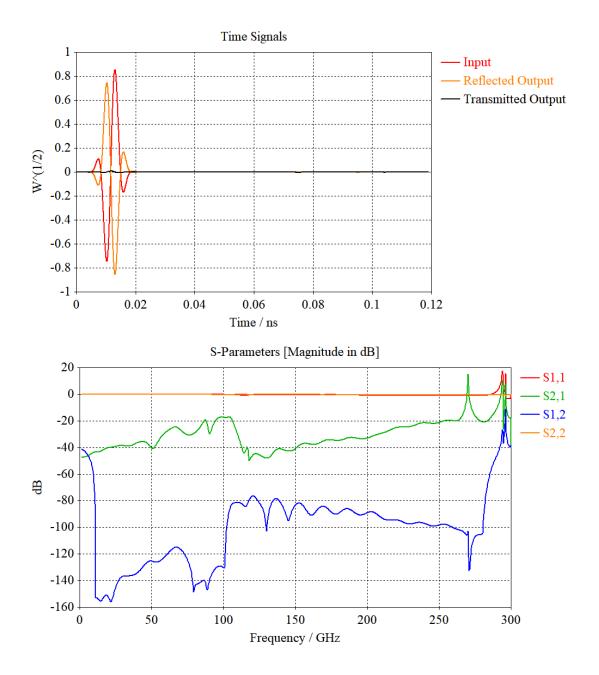

| 4.11 | The input excitation into the planar transformer and the scattered and trans-<br>mitted outputs (top), and the corresponding <i>S</i> -parameters (bottom). The<br>reflections are asymmetric, while transmission parameters are approximately<br>equal. |

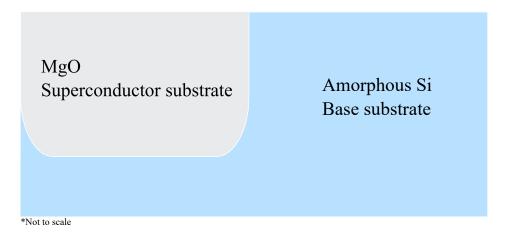

| 4.12 | The proposed substrate solution for the hybrid system                                                                                                                                                                                                    |

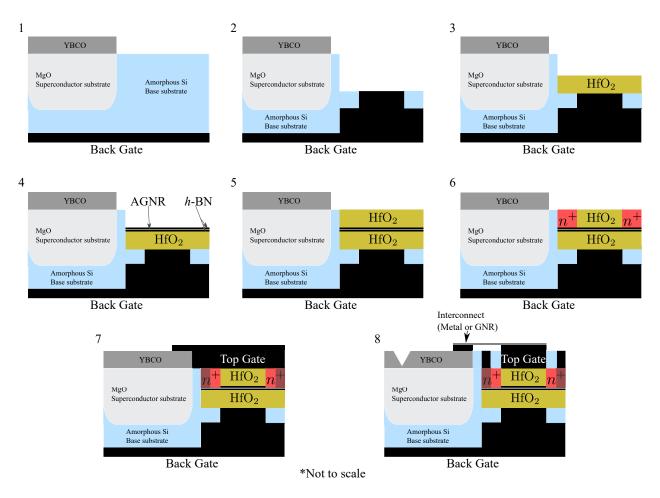

| 4.13 | The proposed construction process.                                                                                                                                                                                                                       |

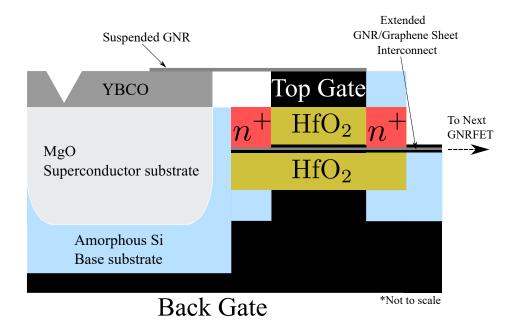

| 4.14 | An alternative post-process layout incorporating suspended GNR/graphene |     |

|------|-------------------------------------------------------------------------|-----|

|      | sheet for an interconnect between the YBCO and gate of the GNRFET and   |     |

|      | demonstrates the GNRFET-to-GNRFET interconnect.                         | 102 |

### LIST OF SYMBOLS

| $B_c$ | superconduct | ing critical | magnetic field |

|-------|--------------|--------------|----------------|

| - c   | Superconduce |              | megneere mere  |

C capacitance

$C_{ox}$  transistor oxide characteristic capacitance

c speed of light in a vacuum,  $c = (\mu_0 \epsilon_0)^{-1/2} = 299792458 \,\mathrm{m \cdot s^{-1}}$

$\chi_m$  magnetic susceptibility,  $\chi_m \equiv \mu_r - 1$

$\Delta$  subgap potential energy at T = 0 K

$\tan \delta$  loss tangent

- *e* fundamental charge,  $e = 1.60218^{-19}$  C (not to be confused with Euler's number, e)

- $\epsilon$  material electrical permittivity

$\epsilon_0$  permittivity of free space,  $\epsilon_0 = 8.8541878 \times 10^{-12} \,\mathrm{F \cdot m^{-1}}$

$\epsilon_r$  relative permittivity/dielectric constant,  $\epsilon_r = \epsilon/\epsilon_0$  (sometimes " $\kappa$ ")

h Planck's constant,  $h = 6.62607 \times 10^{-34} \,\mathrm{m^2 \cdot kg \cdot s^{-1}}$ , or height (usage varies)

$\hbar$  Planck's reduced constant,  $\hbar \equiv h/2\pi$

$I_c$  superconducting critical current

$I_{DS}$  transistor drain-source current

k wavevector/wavenumber,

$$k = 2\pi/\lambda$$

, or an arbitrary constant (usage varies)

$k_B$  Boltzmann constant,  $k_B = 1.38064852 \times 10^{-23}\,\mathrm{J\cdot K^{-1}}$

L inductance or length (usage varies)

$\lambda$  wavelength

$\lambda_L$  London penetration depth

m mass

$m_{\rm e}$  electron mass

$m_p$  hole (effective) mass

$\mu$  mobility or material magnetic permeability (usage varies)

$\mu_0$  magnetic permeability of free space,  $\mu_0 \approx 4\pi \times 10^{-7} \,\mathrm{H \cdot m^{-1}}$

$\mu_{\rm e}$  electron mobility

$\mu_p$  hole mobility

| $\mu_r$     | relative magnetic permeability, $\mu_r = \mu/\mu_0$          |

|-------------|--------------------------------------------------------------|

| n           | charge carrier density or index of refraction (usage varies) |

| ω           | angular frequency                                            |

| $\omega_D$  | Debye frequency                                              |

| $\phi$      | electromagnetic flux                                         |

| $\Phi_0$    | single-flux quanta, $\Phi_0 = 2\pi\hbar/2e$                  |

| $\varphi$   | electron momentum phase difference                           |

| R           | resistance                                                   |

| $R_N$       | "normal" resistance                                          |

| $R_{SG}$    | subgap resistance                                            |

| $\sigma$    | conductivity                                                 |

| $\sigma_n$  | normal conductivity (sometimes $\sigma_1$ )                  |

| T           | absolute temperature in Kelvin                               |

| t           | thickness or time (usage varies)                             |

| $T_c$       | superconducting critical temperature                         |

| $t_{ox}$    | transistor oxide thickness                                   |

| $\theta_D$  | Debye temperature                                            |

| $V_{DD}$    | transistor drain voltage supply                              |

| $V_{SG}$    | subgap voltage, $2\Delta/e$                                  |

| v           | velocity                                                     |

| W           | width (usually transistor channel width, sometimes $w$ )     |

| ξ           | superconductor wave coherence length (sometimes $\xi_s$ )    |

| $\zeta$     | magnetic energy stored in a superconducting material         |

| $Z_s$       | surface impedance                                            |

| $\sigma FT$ | finite thickness surface impedance                           |

$Z_s^{FT} \quad {\rm finite-thickness} \ {\rm surface} \ {\rm impedance}$

## ABBREVIATIONS

| AGNR          | armchair graphene nanoribbon                                |

|---------------|-------------------------------------------------------------|

| BCS           | Bardeen-Cooper-Schrieffer                                   |

| BTB           | band-to-band                                                |

| CDA           | common-drain attenuator (amplifier)                         |

| CNT           | carbon nanotube                                             |

| CNTFET        | carbon nanotube field-effect transistor (sometimes "CNFET") |

| CSA           | common-source amplifier                                     |

| CVD           | chemical vapor deposition                                   |

| DOS           | density-of-states                                           |

| EHF           | extremely high frequency                                    |

| FET           | field-effect transistor                                     |

| FHIB          | focused helium ion beam                                     |

| FinFET        | fin field-effect transistor                                 |

| $\mathbf{FM}$ | frequency modulation                                        |

| FOM           | figure of merit                                             |

| GBWP          | gain-bandwidth product                                      |

| GFET          | graphene field-effect transistor                            |

| GNR           | graphene nanoribbon                                         |

| GNRFET        | graphene nanoribbon field-effect transistor                 |

| HEMT          | high-electron-mobility transistor                           |

| HTS           | high-temperature superconductor                             |

| IBAD          | ion-beam-assisted deposition                                |

| JJ            | Josephson junction                                          |

| LTS           | low-temperature superconductor                              |

| MMIC          | monolithic microwave integrated circuit                     |

| MMW           | millimeter wave                                             |

| NEGF          | non-equilibrium Green functions                             |

| PLD           | pulsed laser deposition                                     |

|               |                                                             |

| PLL      | phase-locked loop                                            |

|----------|--------------------------------------------------------------|

| RCSJ     | resistive capacitively-shunted junction                      |

| SB       | Schottky-barrier                                             |

| SBGNRFET | Schottky-barrier graphene nanoribbon field-effect transistor |

| SET      | single-electron transistor                                   |

| SN       | superconductor-normal metal                                  |

| SNS      | superconductor-normal-superconductor                         |

| TEM      | transverse electromagnetic mode                              |

| TFA-MOD  | metal organic deposition using trifluoroacetate salts        |

| TFET     | tunneling field-effect transistor                            |

| TSV      | through-silicon via                                          |

| ULSI     | ultra-large-scale integration                                |

| VCO      | voltage-controlled-oscillator                                |

| VLSI     | very large-scale integration                                 |

| VTB      | variable-thickness-bridge                                    |

| ZZGNR    | zig-zag graphene nanoribbon                                  |

# NOMENCLATURE

| ALO                                        | aluminum oxide $(Al_2O_3, \text{ sometimes "sapphire"})$                           |  |  |

|--------------------------------------------|------------------------------------------------------------------------------------|--|--|

| Au                                         | elemental gold                                                                     |  |  |

| $\mathrm{BaZrO}_3$                         | barium-doped zirconium                                                             |  |  |

| BSCCO                                      | bismuth strontium calcium copper oxide ("bisko") ceramic HTS                       |  |  |

| $CeO_2$                                    | cerium oxide                                                                       |  |  |

| <i>h</i> -BN                               | hexagonal 2D boron nitride                                                         |  |  |

| $H_2S$                                     | metallic hydrogen sulfide                                                          |  |  |

| $\mathrm{H}_{2}\mathrm{S}+\mathrm{CH}_{4}$ | carbonaceous sulfur hydride                                                        |  |  |

| $H_2SO_4$                                  | sulfuric acid                                                                      |  |  |

| $\mathrm{HfO}_{2}$                         | hafnium oxide                                                                      |  |  |

| Hg                                         | elemental mercury                                                                  |  |  |

| $\mathrm{KMnO}_4$                          | potassium permanganate                                                             |  |  |

| $LaH_{10}$                                 | metallic lanthanum hydrogen                                                        |  |  |

| LAO                                        | lanthanum aluminum oxide (LaAlO <sub>3</sub> or LaAl <sub>2</sub> O <sub>3</sub> ) |  |  |

| LBCO                                       | lanthanum barium copper oxide HTS                                                  |  |  |

| MgO                                        | magnesium oxide                                                                    |  |  |

| Nb                                         | elemental niobium                                                                  |  |  |

| NbN                                        | niobium nitrate                                                                    |  |  |

| $\mathrm{Nb}_3\mathrm{Sn}$                 | niobium tin                                                                        |  |  |

| $NdGaO_3$                                  | neodymium gallium oxide                                                            |  |  |

| Pb                                         | elemental lead                                                                     |  |  |

| Si                                         | elemental silicon                                                                  |  |  |

| SiC                                        | silicon carbide                                                                    |  |  |

| $\mathrm{SiO}_2$                           | silicon oxide (sometimes just "oxide")                                             |  |  |

| STO                                        | strontium titanate $(SrTiO_3)$                                                     |  |  |

| TBCCO                                      | thallium barium calcium copper oxide ("tibco") ceramic HTS                         |  |  |

| YBCO                                       | yttrium barium cupric oxide ceramic HTS                                            |  |  |

| YSZ                                        | yttria-stabilized zirconia                                                         |  |  |

|                                            |                                                                                    |  |  |

## GLOSSARY

| BCS Theory              | Bardeen-Cooper-Schrieffer theory of superconductivity               |  |  |

|-------------------------|---------------------------------------------------------------------|--|--|

| Debye Frequency         | the maximum supported phonon standing-wave frequency                |  |  |

|                         | present in an ionic lattice enclosed in a finite cube               |  |  |

| Debye Temperature       | the temperature associated with the Debye frequency,                |  |  |

|                         | $k_B \theta_D = \hbar \omega_D$                                     |  |  |

| EHF                     | radio wave band designation for 30-300 GHz                          |  |  |

| Heterojunction          | a junction formed at the interface between two different            |  |  |

|                         | materials                                                           |  |  |

| MMW                     | another name for EHF                                                |  |  |

| quasi-TEM               | an approximation of the electromagnetic fields in wires that        |  |  |

|                         | assumes the modes are nearly TEM fields                             |  |  |

| Relativistic conduction | conduction in a material where charge velocities are comparable     |  |  |

|                         | to the speed of light                                               |  |  |

| Retroreflection         | a variation on reflection, where velocity is reversed, but angle is |  |  |

|                         | not changed, so that which is reflected follows the path it took    |  |  |

|                         | to reach the surface of reflection, rather than scatter off of it   |  |  |

| SI Junction             | superconductor-insulator junction                                   |  |  |

| SIS Junction            | superconductor-insulator-superconductor junction, frequently        |  |  |

|                         | forms a thin Josephson junction                                     |  |  |

| SN Junction             | superconductor-normal metal junction                                |  |  |

| SNS Junction            | superconductor-normal-superconductor junction, frequently           |  |  |

|                         | forms a Josephson junction                                          |  |  |

| TEM                     | an electromagnetic mode on wires that assumes the electric and      |  |  |

|                         | magnetic fields are orthogonal                                      |  |  |

| Type-I Superconductor   | superconductor with zero magnetic flux penetration depth            |  |  |

| Type-II Superconductor  | superconductor with nonzero magnetic flux penetration depth         |  |  |

### ABSTRACT

As the search for ever-higher-speed, greater-density, and lower-power technologies accelerates, so does the quest for devices and methodologies to fulfill the increasingly-difficult requirements for these technologies. A possible means by which this may be accomplished is to utilize superconducting devices and graphene nanoribbon nanotechnologies. This is because superconductors are ultra-low-power devices capable of generating extremely high frequency (EHF) signals, and graphene nanoribbons are nanoscale devices capable of extremely highspeed and low-power signal amplification due to their high-mobility/low-resistance channels and geometry-dependent bandgap structure. While such a hybrid co-integrated system seems possible, no process by which this may be accomplished has yet been proposed.

In this thesis, the system limitations are explored in-depth, and several possible means by which superconducting and graphene nanotechnological systems may be united are proposed, with the focus being placed on the simplest method by which the technologies may be hybridized and integrated together, while maintaining control over the intended system behavior. This is accomplished in three parts. First, via circuit-level simulation, a semioptimized, low-power (~0.21 mW/stage) graphene-based amplifier is developed using ideal and simplified transmission line properties. This system is theoretically capable of 159-269 GHz bandwidth with a Stern stability  $K \gg 1$  and low noise figure  $2.97 \le F \le 4.33$  dB for all appropriate frequencies at temperatures between 77 and 90 K. Second, an investigation of the behavior of several types of possible interconnect methodologies is performed, utilizing hybrid substrates and material interfaces/junctions, demonstrating that an Ohmic-contact superconducting-normal transmission line is optimal for a hybrid system with self-reflections at less than -25 dB over an operating range of 300 GHz. Finally, a unified layout and lithography construction process is proposed by which such a hybrid system could be developed in a monolithic physical system on a hybrid substrate while maintaining material and layout integrity under varying process temperatures.

### 1. INTRODUCTION

#### 1.1 Motivation

Since the discovery of the Josephson effect, there have been many significant applications: the discovery of the DC effect led to the idea for the official NIST voltage standard [1]–[6], and the ability to store electromagnetic flux quanta in a loop formed by two parallel junctions as a superconducting quantum interference device (SQUID) led to significant research in the area of low-flux magnetometers [7], quantum computing and qubit research [8]–[11], the area of physics research called parity-time-symmetry ( $\mathcal{PT}$ -symmetry, which studies non-Hermitian Hamiltonians) [9], [12], [13], and many other research areas. These SQUIDs also became useful for superconducting logic systems, rapid single-flux quantum (RSFQ) logic [3], [14], [15], and have been applied in a number of ways, such as VLSI/ULSI-style memory arrays [16], nano-scale inductors [17], flip-flops [18], and other computational applications [19], [20]. Recent research has used also used SQUIDs as terahertz/millimeter-wave (THz/MMW) signal generators [3], [4], [21]–[24], monolithic-microwave IC (MMIC) devices [3], [4], [25], RF/antenna applications [4], [21], [22], and phase-locked loops (PLLs), especially due to the voltage-controlled-oscillator (VCO) properties these devices exhibit and the inherent ACand DC-effects making them ideal for signal generation and reception.

The vast number of high-speed and high-accuracy/precision applications for which these devices have been suggested makes them a desirable technology, but the challenge remains in combining them with normal technologies, such as CMOS or CMOS-like systems, due in part to their temperature requirements and due in part with the different manufacturing methods required. While graphene nanoribbon FETs (GNRFETs) can potentially handle the temperature requirements [23], [24], [26], the manufacturing methods for both are exceptionally challenging, as no one set of process rules exist because GNRFETs themselves are still experimental devices with very few process rules, and the concept of hybrid graphene-Josephson junction (JJ) systems is still theoretical. Thus, this the motivation for this research: to propose a basic, unified process and layout scheme which can be used to develop precise design rules.

#### 1.2 Thesis Problem Statement and Research Issues

To combine superconducting devices together with non-superconducting devices, such as analog GNR nanostructures or CMOS, to create extremely high-frequency (EHF) systems, this thesis answers the following five major research questions about such a hybrid system:

- Hybrid Interfacing: How might superconductive systems, which rely on low temperatures and power, be combined with nanotechnological systems which may or may not operate properly in the same operational regions?

- Physics-based issues: With EHF systems, how does the electromagnetic physics place restrictions on the design of the system? What kind of issues may result from SN heterojunctions, especially considering Andreev reflections?

- Transmission-line analysis: At EHF ranges, how well do interconnects work? How lossy are they? Is there a benefit to utilizing nanostrip/nanoribbon interconnects compared to superconducting interconnects or nanowires? Would electromagnetically-coupled resonators operate more optimally?

- Substrate compatibility: Can superconducting devices and graphene nanotechnologies operate on the same physical substrate, or do they need separate substrates due to lattice constant-related issues? If different substrates are required, is 3D substrate layering a viable option, with TSVs, or would separate dies be required, utilizing nanowires?

- Process considerations: How could a hybrid system like the ones propose here be potentially grown or otherwise physically developed?

Here, these considerations are investigated thoroughly, and a proposed process for combining the two distinct systems into one is developed based on these questions.

### **1.3** Present Efforts and Current Work

Some work in regards to developing a basic hybrid system has been performed already, investigating whether or not it is conceivably possible to even interface ideal graphene-based and superconducting-based devices, especially due to temperature differences. Utilizing a simple Josephson junction model written in SPICE (Appendix A.1) and Verilog-A (Appendix A.2), and simulated at temperature of 90 K, previous work presented in Refs. [24] and [23] demonstrate that it is theoretically possible to generate, control, and transmit a sub-terahertz signal from a Josephson junction array to a GNRFET-based amplifier chain, raising the signal level from millivolt to volt levels at frequencies between 200 and 300 GHz.

While this initial work assumes ideal wires, current and voltage sources, and noiseless devices, it remains a promising prospective means of generating such high-frequency signals. However, the liquid-nitrogen-temperatures, relative to room temperature (300 K), are somewhat of a limitation, and, as of the time those papers were published, the noise and stability properties of the junctions and amplifiers were still unknown.

The amplifier presented in [23] and [24] is also itself rudimentary and designed on the assumption that the amplifier is stable and has sufficient noise properties to work in the EHF range, without stability and noise analysis. To be a viable system model, the GNRFET CDA-CSA-CDA amplifier needs to go under a more intensive investigation that takes stability and noise into consideration, as well as some level of transmission-line effects.

#### 1.4 Present Limitations

There are several limitations for this research. First is the inability to provide experimental results beyond those of physics-based or highly-accurate simulation modeling. Because of the combination of lack of access to the systems required to construct these devices and the sheer difficulty of precisely and consistently manufacturing devices such as the GNRFETS, according to Refs. [27]–[32], no physical results or experimental data can be acquired, relegating this research to the realm of theoretical/experimental devices.

Simulations themselves are limited due to access to physics-based simulation software primarily intended for superconductor research or 2D material exploration. As such, superconductor modeling must rely on the capabilities or limitations of material modeling in CST Studio, and simulating the GNR-based devices is restricted to the capabilities and limitations of HSPICE/Verilog-A modeling of RF, graphene, or superconducting devices in Cadence Virtuoso. While software like CST Studio and Cadence Virtuoso are exceptionally-accurate for ideal systems and a significant number of realistic systems, there are some instances where their results may not be able to be properly verified, simply due to lack of experimental data or the limitations of the device models themselves.

Unrelated to the tools at hand, other limitations for this research are more physical, in that they are general challenges that physicists and engineers are, to this day, struggling against. Perhaps the most obvious of these challenges is that of the high-temperature or room-temperature superconductor. While the high-temperature superconductive ceramic YBCO is utilized or referenced here as the superconductor of choice (due to its widespread use and the easy access to liquid nitrogen), it is still severely limited by the fact that it is operable around 90 K, though typically used at temperatures closer to 77 K. Future research may one day remove this limitation and others, but until then, this point remains the greatest challenge/limitation to this research.

Other limitations are discussed in greater depth in Chapter 4, but many of them are limitations which this research seeks to address and resolve, as have been mentioned previously in Sec. 1.2.

#### 1.5 Thesis Organization

This research follows the development of a hybrid superconducting-graphene nanotechnology system from the fundamental physics aspect to the proposed physical implementation, discussing the considerations as the thesis progresses. Starting in Chapter 2, the historical perspective and context of superconductivity and graphene nanodevices is provided, as well as a brief, high-level overview of their theory of operation, as necessary to further develop the discussion on the system limitations. In Chapter 3 the superconducting and graphene device models are reviewed, with the GNRFET-based amplifiers revisited and investigated under more thorough analysis (Chapters 3.1 and 3.2, respectively). Chapter 4 investigates, in-depth, the limitations and means of hybridization of the technologies, particularly with the substrates and interconnect methodology (Chapters 4.1 and 4.3, respectively), and finally a proposal for the possible process (Chapter 4.4). Chapter 5 proposes future work that could extend from this research, and Chapter 6 summarizes these findings succinctly, and re-iterates the proposed hybridization process.

## 2. BACKGROUND AND BASIC THEORY

#### 2.1 Superconducting Devices

An unexpected discovery was made by Kamerlingh Onnes in 1911 while measuring the temperature-dependence of conductivity in mercury [3], [4]. He described superconductivity to be the phenomenon wherein the resistivity of a material disappears when cooled below some critical temperature,  $T_c$ , leading to zero DC power dissipation. Later, a magnetic-field-effect named after one of its discoverers, Meissner and Ochsenfeld [3], [4], [33]–[37], would be found as a consequence of zero resistivity. Since then, many new superconducting compounds have been discovered, with requirements ranging from 4.2 K temperatures at ambient pressure to nearly-room-temperature (287 K) at 267 GPa pressures [38], and many parameters in between. Table 2.1 summarizes some superconductors of historical and modern importance.

One of the means used to prove a material is superconducting is the Meissner effect. In this effect, magnetic field lines are expelled entirely (Type-I superconductors) or nearlyentirely (Type-II superconductors) from a material, and instead either wrap around the superconductor, as illustrated in Fig. 2.1, or are completely folded back over the magnetic field source. When magnetic flux is applied near the superconductor, it induces a circulation current in the superconductor. Because there is zero resistance, the current formed by Faraday's Law is exactly strong-enough to equal and oppose the external magnetic field. Because of this, the magnetic field inside the superconductor is zero, but since magnetic flux lines cannot terminate (causing  $\nabla \times \boldsymbol{B} \neq 0$ , which is prohibited as far as is known), the external magnetic field lines must either go around the superconductor or otherwise double back on themselves without crossing, which results in a phenomenon called *flux pinning* [3], [4], [33], [37]. Thus, the Meissner effect is equivalent to perfect diamagnetism. The presence or absence of the Meissner effect is what is used to verify the superconductivity of a material, and was used to prove that superconductivity was not perfect conductivity and instead that a superconductor's conductivity was finite [4], [33], [37].

If superconductors were perfect conductors, then the current generated in the superconductor would be infinite, and the resulting opposing magnetic field would be, accordingly,

| Material           | Year | $T_{c}$ (K) | Pressure |  |  |

|--------------------|------|-------------|----------|--|--|

| Hg [3]             | 1911 | 4.15        | Ambient  |  |  |

| Pb [3], [39]       | 1912 | 7.19        | Ambient  |  |  |

| Nb [3], [39]       | 1925 | 8.4         | Ambient  |  |  |

| NbN [3], [40]      | 1942 | 16          | Ambient  |  |  |

| $Nb_3Sn [3], [41]$ | 1954 | 18.3        | Ambient  |  |  |

| $Nb_3Ge [3], [42]$ | 1973 | 23.2        | Ambient  |  |  |

| LBCO [3], [43]     | 1986 | $\leq 35$   | Ambient  |  |  |

| YBCO [3], [44]     | 1987 | $\geq 92$   | Ambient  |  |  |

| BSCCO [3], [45]    | 1988 | 110         | Ambient  |  |  |

| TBCCO [3], [46]    | 1988 | 127         | Ambient  |  |  |

| $H_2S$ [47]        | 2015 | 203         | 100  GPa |  |  |

| $LaH_{10}$ [48]    | 2018 | 250         | 170  GPa |  |  |

| $H_2S + CH_4 [38]$ | 2020 | 287         | 267 GPa  |  |  |

Table 2.1. A list of historical and common superconductors.

infinite, which is impossible. Thus, because a finite magnetic field is created, it must mean that the superconductor has some finite conduction, despite having zero resistance. This led to the prediction of type-I and type-II superconductors [3], [4], development of the London constitutive equations [33], [49], the Ginzburg-Landau theory [3], [4], [33], [50], [51], and eventually the Bardeen-Cooper-Schrieffer (BCS) theory of superconductivity [34], [35].

The BCS theory of superconductivity was perhaps one of the biggest breakthroughs in superconductivity research. While, in its original state, it cannot directly explain HTS materials [34], [35], [44], the exact mechanism for which remains a mystery to this day, it is perhaps one of the most-successful microscopic theories of superconductivity.

The basic BCS theory of superconductivity posits that, when a material's temperature is sufficiently low enough, all valence energy bands of the material are full. Thus, any electrons added must sit in the *Fermi sea*, which is the collection of electrons in the conduction bands. If the energy of the system is low enough, then mechanical vibrations of the crystal lattices, quasiparticles called *phonons*, are still present, but are also very low energy. These phonons, which are bosonic in nature, interact with electrons, which are fermionic (and thus follow the Pauli exclusion principle by nature) with spin-1/2. However, when these phonons interact with two electrons, it is able to overcome Coulomb repulsion and instead couples them together, treating two sufficiently-close electrons as though they were a single spin-1 boson,

Figure 2.1. The Meissner effect on a type-I superconductor, as demonstrated with a round object. The lines of flux, when temperature  $T \ge T_c$ , pass through the object and, when  $T < T_c$ , pass around the object, completely expelled.

as illustrated in Fig. 2.2. This phonon-coupled paired-electron psuedoparticle is called a *Cooper pair*, and, because it acts as as boson, no longer follows the Pauli exclusion principle. As such, all similar Cooper pairs can occupy the same quantum states, no longer limited by their fermionic nature. This allows as many Cooper pairs to exist on any particular crystal lattice site as desired, no longer prohibited from site-to-site hopping to sites already occupied, per the Hubbard model of spin site-hopping [33], [52]. This unlimited hopping capability is what permits a zero-resistance conduction of electrons [3], [4], [33]–[36]. How quickly or easily pairs can perform this site-hopping is what leads to the finite conductivity.

Bardeen, Cooper, and Schrieffer were also able to predict the other phenomenon seen in superconduction (such as the Meissner effect, various thermodynamic properties, finite conduction, critical currents, critical magnetic fields, type-I and -II superconductors, *et cetera*), but also predicted an upper limit to superconductor critical temperatures near 30 K, as phonon coupling could not overcome thermal vibrational modes above this point [3], [4],

**Figure 2.2.** A simple illustration of a Cooper pair, where  $\vec{k}_{1,2}$  are the momentums of electrons "1" and "2," respectively, in the Fermi surface with a maximum energy separation of  $\hbar\omega_D = k_B\theta_D$ , where  $\theta_D$  is the Debye temperature and  $\omega_D$  is the Debye frequency. The interaction with the phonon is represented by the momentum exchange  $\vec{q}$ .

[33]–[36]. Obviously, "high- $T_c$ " superconductors do exist, which indicates that the BCS theory may be incomplete. Considering the success it has had everywhere else, and how HTS materials do, for the most part, still follow the BCS theory, physicists are inclined to believe that there must be some other kind of bosonic coupling between electrons in HTS Cooper pairs, the mechanism for which remains elusive even today.

In 1962, after some unusual results from experiments from nanoscale superconductorinsulator-superconductor (SIS) junctions where the presence of currents in the junctions was detected while no electric potential was applied, B.D. Josephson hypothesized that this was the result of Cooper pairs forming across the junctions, despite the physical separation, as long as the gap was less than the coherence length,  $\xi$ , of the superconductor. If this were the case, then the Schrödinger equation for this pair could be written in such a way that pair tunneling probability across the junction was nonzero, even if the potential difference was zero. A nonzero tunneling probability indicated that it was possible that these quasiparticles would spontaneously cross the junction via a phenomenon later denoted *Giaever tunneling* [53]–[55]. If enough crossed the junction within a certain amount of time, it could constitute a noticeable amount of current. This *supercurrent* exists as a noise current when V = 0with a current density  $J = J_c \sin \varphi$ , where  $\varphi$  is the momentum phase difference between the electrons in the pair (not to be confused with  $\phi$ , which is typically magnetic flux or an angle). This phenomenon is, accordingly, called the *Josephson effect* [3], [4], [33], [36], [56], [57], and while many were initially dubious about the effect for some time, it was verified a year later [54], [58], and later discovered in superfluid helium [59].

Now, if the potential across the junction, now called a *Josephson junction*, was nonzero, then the momentum phase difference is easily predicted by:

$$\frac{\partial \varphi}{\partial t} = \frac{2e}{\hbar} V \tag{2.1}$$

If V is constant, then  $\varphi(t) = \frac{2e}{\hbar}Vt = \frac{2\pi V}{\Phi_0}t$  (where  $\frac{\Phi_0 \equiv 2\pi\hbar}{2e}$  is the single flux quanta), and  $J(t) = J_c \sin \varphi(t)$ . What this shows is that a DC voltage gives rise to an alternating current, at a conversion rate of 483.6 GHz per millivolt, making an ideal JJ a perfect gigahertz-level voltage-controlled-oscillator. This is known as the *AC-effect*, and is foundational for the motivation for this research.

Thus far, there have been quite a number of fabrication methodologies and applications for JJs using both original LTS and HTS junctions. Originally, superconductors and JJs were typically fabricated using LTS materials and layered structures, such as layered Nb-AlO<sub>x</sub>-Nb LTS junctions [1], [3], [4], [36], [60], and recently superconduction had been discovered in bilayer graphene [61], [62]. However, extensive research has been put into developing HTS junctions, typically made of YBCO and utilizing a different form of junction called a grain-boundary junction, wherein the internal grain defects of the material, upon being deposited on its substrate, themselves form junctions [5], [21], [22], [25], [63]–[69]. This effect can be intentionally engineered or done unintentionally (which makes certain forms of deposition challenging). Another method is to create a variable-thickness-bridge (VTB) trench junction [70]. Because  $\xi$  for HTS materials is typically an order of magnitude lower than  $\xi$  for LTS ones, these junctions are extremely challenging to manufacture, thus why they are only a more recently-viable option. Applications of these HTS junctions are thus part of the motivation for this research.

#### 2.2 Semiconducting Devices and Nanotechnology

As Moore's Law rapidly approaches its end, the search for smaller, faster, and lower-power technologies has rapidly accelerated. Even though process node names have not reflected physical geometry since the 90s [71], technologies *equivalent to* sub-65nm processes have been developed, including, but not limited to, FinFET technologies [72], [73], of which currently-active and widely-used processes include Intel's 14 nm process [74], Samsung's 7 nm process [75], and TSMC's 7 nm process [76], each of which is on the order of roughly 50 nm in scale, give or take 20 nm; TFET devices [77]–[81]; single-electron transistors (SETs) [82]–[84]; high-mobility transistors (HEMT), like GaN, GaAs, and many other III-V materials [85]–[97]; and even superconducting transistors [19], [97], [98]. Each has its benefits and issues, as each attempts to focus on one particular issue over another (e.g.: power versus speed versus transistor density). There are a few types in particular, however, that attempt to focus on all three major issues simultaneously: carbon nanotube (CNT)-based or graphene-based transistors, which are a type of tunneling HEMT [79], [80], [99]. These kinds of devices make use of the phenomenal electrical properties of these various allotropes of carbon.

Semi-recently-discovered single-layer graphene is a material consisting of a 2D lattice of carbon atoms [31], [32], [100]. Because of its regular shape and nearly-perfect 2D properties, it and CNTs exhibit ballistic transport up to a length of 16  $\mu$ m [101] and have, in certain conditions, phenomenal conductivity – up to over six times the conductivity of copper [102], [103]. Recently, however, it was discovered that these materials, in an external electric field, could also exhibit semiconducting properties [71], [104], [105], despite zero-band-gap properties (called *Dirac points* in band diagrams). This led to the development of CNTFETs and their 2D cousin, GFETs. However, due to the intrinsic lack of bandgap, these devices had some notable issues, such as scaling problems, insufficient on-to-off-current ratios, insufficient

Figure 2.3. An illustration of conducting zig-zag GNR (ZZGNR – left) and semiconducting armchair GNR (AGNR – right) with N = 8 dimer lines (annotated).

subthreshold swings, conductivity issues, and other problems [79], [80], [106]–[108]. Thus, some kind of resolution to these particular issues was required.

In 1996, a new form of graphene was introduced, called the graphene nanoribbon, which exist in two types: the zig-zag GNR (ZZGNR), and the armchair GNR (AGNR), as illustrated in Fig. 2.3. Prior studies of graphene had focused primarily on graphene sheet, the behavior of which can be approximated by assuming, relative to the size of a single carbon atom site, the sheet is periodic and infinite in all directions. However, by making a ribbon – a sheet of graphene of finite width and length, new solid-state and electromagnetic properties arise. While ZZGNRs remain extremely conductive, maintaining the zero-band-gap

and Dirac points in the energy band structure, AGNRs demonstrate drastically different behavior: they are semiconducting, with a bandgap size dependent on the number of dimer lines (parallel lines of carbon atom pairs forming a Bravais lattice unit cell across the width) [109]–[111]. By choosing the width and lengths of AGNRs, the bandgap and semiconducting properties of graphene can be engineered to suit the needs of a system [88]. More recent research with AGNRs have confirmed the AGNR energy band structure [112], found discretestep conductivity if the GNRs are edge-terminated with hydrogen [113], determined that the bandgap can also be better-controlled with hydrogen-termination [114], discovered interesting conduction properties in buckled AGNRs [115], found twisting/3D-shape formation of the GNRs with interesting electromechanical properties [106], and shown long-distance ballistic charge transport in GNRs [101], [116].

Despite their discovery being in the late-90s, it was almost 15 years between the discovery and the potential application of GNRs for transistors. This is very likely due to how GNRs could not be precisely produced until 2009, when two groups independently developed ways to unzip carbon nanotubes: one via action of KMnO<sub>4</sub> and H<sub>2</sub>SO<sub>4</sub> on multi-walled CNTs [117], and the other by plasma by etching [118]. Other methods have been developed since then, either for unzipping [119], [120], direct growth [121], [122], etching [123], or by a bottom-up approach and CVD [124], [125], which may include doping as well.

The first theoretical device that could be considered a proto-GNR transistor was developed in 2007 to study quantum capacitances in GNRs. This device consisted of a GNR-oninsulator, with a top- and optional bottom-gate structure. This study found, as expected, that the GNR *C-V* characteristics were strongly-dependent on edge shape [126]. For N = 41and N = 42 AGNR devices, with lengths of approximately 5 nm and a dielectric constant of the 2 nm-thick insulator  $\epsilon_r = 16$ , the resulting simulated capacitances were quite small: on the order of picofarads per centimeter, corresponding to roughly tenths of attofarads per nanometer, dependent on gate voltage. The results from this work demonstrate further that GNRs are good potential candidates for transistor channel materials.

Around the same time, several papers came out discussing the possibilities [127] and simulations for GNRFETs (or proto-GNRFETs) [128]–[131], especially as compared to CNTFETs, which had a number of issues. Of these, the Stanford models were, perhaps, most influen-

tial in the initial stages of research, as they were some of the first physically-implemented room-temperature sub-10 nm GNRFETs [130], [131]. However, the first formal physicsbased simulation model was developed initially in 2011 by Unluer, *et al.* [132], and then a SPICE-compatible physics model in 2013 by Chen, *et al.* [30] for MOS-like GNRFETs, which included doping properties, which, as it turns out, in GNRFETs, mobilities  $\mu_e$  and  $\mu_p$ are nearly the same. This was followed by a Schottky-barrier-type GNRFET (SBGNRFET) the following year [28]. Both models have been refined since then [31], [32]. A comparison of these devices was released the same year, discussing the devices' capabilities, and formally classifying them as a type of TFET [80]. These models have proven to be remarkablyaccurate to physical versions [27], [28], [30]–[32], and the resulting simulation models, available on Nanohub [29], have been widely-used. These devices are phenomenal, and may have many applications, from high-speed digital [27], [28], [30]–[32], to low-temperature, low-power small-signal analog amplification [23], [24].

### 3. DEVICE PHYSICS, MODELING, AND OPERATION

#### 3.1 Superconductive Devices

#### 3.1.1 Josephson Junctions

The ideal Josephson junction has a very simple equivalent circuit consisting of a phasedifference-controlled current source, but there are also several non-ideal effects that need to be considered. First is the critical current density,  $J_c$ , above which the superconducting device acts like a normal conductor and has an effective normal resistance,  $R_N$ . In the JJ, the potential energy required to bring the junction to this point is referred to as the (sub)gap potential or quasiparticle tunneling gap,  $\Delta$ . The corresponding subgap voltage is  $V_{SG} = 2\Delta/e$ . Ideally,  $R_N$  can also be calculated by:

$$R_N = \frac{\pi}{4} \frac{V_{SG}}{I_c} = \frac{\pi}{2} \frac{\Delta}{eI_c}$$

(3.1)

The actual value of  $R_N$  varies from junction to junction, even between junctions of the same construction. For JJs, the parameter  $\frac{\pi}{4}V_{SG} = I_cR_N$  is frequently given instead, and either  $J_c$  or  $I_c$  is specified separately. From this, the JJs' specific  $\Delta$  and  $R_N$  may be extracted [3], [70].

$\Delta$  itself is an interesting parameter, resulting from the BCS theory of superconductivity. Its value is typically around 1 meV, and describes the energy difference between particles in a Cooper pair. Specifically,  $2\Delta$  can be seen as the binding energy of the electron pair. If the energy difference between two electrons exceeds  $\Delta$ , then the two electrons cannot couple. This observation is what led to the initial prediction by Bardeen, Cooper, and Schrieffer for the maximum critical temperature a superconductor could hold [3], [4], [33]–[35].

The second major non-ideal feature of the JJ is the subgap resistance,  $R_{SG}$ , which exists in voltage-driven JJs and describes the quasiparticle tunneling due to typical conduction, rather than the Josephson effect. It may be considered to be infinite, generally, but it may still occur in certain conduction models for the JJ [3], [25], [58]. It may also be referred to as the subgap conductance,  $G_{SG}$ , which is effectively zero. Combined with  $R_N$ , the complete conduction model for a JJ can be written as:

$$G(V) = \begin{cases} G_{SG} = R_{SG}^{-1} & |V| < V_{SG} \\ G_N = R_N^{-1} & |V| \ge V_{SG} \end{cases}$$

(3.2)

Finally, because JJs frequently consist of two parallel superconducting plates, the model must also include a capacitance. Sometimes an inductance is considered as well, but it depends on the model and physical junction size. How all these non-ideal parameters affect the junction are summarized with Stewart-McCumber parameter [3], [133], [134]:

$$\beta_c \equiv \frac{\omega_c}{\alpha} = \frac{\omega_c C}{G} = \frac{2e}{\hbar} \frac{I_c}{G_N^2} C \tag{3.3}$$

A junction is considered over- or under-damped based on  $\beta_c$  ( $\beta_c < 1$  corresponding to over-damped and  $\beta_c > 1$  corresponding to under-damped), which functions identically to a harmonic oscillator's *Q*-factor.

The simplest model to incorporate all these parameters is called the *resistive capacitively-shunted junction* (RCSJ) model, as seen in Fig. 3.1 [3], [4], [25], [55]. While it does not natively incorporate electromagnetic effects (such as the DC effect), it is sufficiently for simulation purposes. There are some non-physical additions to the model that are introduced to maintain accuracy and to allow the simulator to work with smooth, rather than piecewise or otherwise non-differentiable, equations – especially with the subgap conduction model presented in Eq. 3.2. Given  $G(V) \equiv R(V)^{-1}$ , the subgap resistance  $R_{SG}$ , normal resistance  $R_N$ , and the subgap potential  $\Delta$ , then the conduction model can be smoothly approximated by:

$$R(V) \approx R_{SG} + \frac{R_N - R_{SG}}{1 + \exp\left(-k\left[\left(\frac{eV}{2\Delta}\right)^2 - 1\right]\right)}$$

(3.4)

The parameter k is an arbitrarily-large positive constant  $(k \to \infty)$  to achieve the sharpness of the piecewise model. The electron charge term, e, may be dropped if  $\Delta$  is in units of electron-volts rather than Joules. This is implemented in the SPICE and Verilog-A models

**Figure 3.1.** A schematic-level illustration of the RCSJ Josephson junction model. It consists of an ideal junction  $I(t) = I_c \sin \varphi(t)$ , a voltage-dependent conductance G(V), and a capacitance C.

utilized here, originally developed and presented in Ref. [23], with an updated version of them given in Appendix A. The default values for the model are  $R_N = 17 \ \Omega$ ,  $R_{SG}/R_N = 20$ ,  $\Delta = 1.08 \text{ meV}$ ,  $I_c = 100 \ \mu\text{A}$ , and k = 100 for the SPICE model, based on example numbers given in Ref. [3] for a Nb/AlOx/Nb junction.

The Verilog-A model is slightly different, primarily based on a variation of the Nb junctions:  $R_N = 10.7 \ \Omega$  (calculated from  $I_c$  and  $\Delta$ ),  $R_{SG}/R_N = 40$ ,  $\Delta = 1.5 \text{ meV}$ ,  $I_c = 220 \ \mu\text{A}$ , and k = 100. For both, the junction capacitance is set to 18 fF. The SPICE model specifies, as parameters,  $I_c$ ,  $R_N$ , the subgap ratio, and C, while the Verilog-A model specifies, as parameters,  $I_c$ ,  $\Delta$ , the subgap ratio, and C. They are equivalent, though the Verilog-A model is more intuitively-constructed (as it was designed sometime after the initial SPICE model). These SPICE models assume an ideally-calculated  $R_N$ , rather than an empirical  $R_N$ .

Inductances can also be included, but are typically present only in large-scale JJ models or SQUIDs. This inductance would be included at the input and output nodes of the junction, and are called the *Josephson inductance*,  $L_J = \Phi_0/2\pi I_c$  [3].

Figure 3.2. A diagram of the YBCO Josephson junction using the VTB model, as implemented in Ref. [70]. The substrate originally used was STO, but other substrates may potentially also be utilized, as discussed in Chapter 4.1.

The model parameters for a HTS JJ are a little more complicated to determine. Using the JJ developed in Ref. [70], which consists of an etched trench in gold-coated YBCO-on-STO, the model parameters are calculated by the width of the junction, w, the thickness of the YBCO, t, the unetched depth of the YBCO, h, the top trench width,  $d_1$ , and the bottom trench width,  $d_2$ , along with  $J_c$ ,  $I_cR_N$ , and the subgap ratio, SGR. A diagram of the VTB model, as implemented in Ref. [70], is shown in Fig. 3.2.

For pure YBCO,  $\Delta \approx 16.7$  meV (equivalent to  $I_c R_N = 6.55$  mV) [135] and  $J_c \approx 2.75 \text{ MA} \cdot \text{cm}^{-2}$  [136], though for this junction, if h = 80 nm,  $w = 4 \ \mu\text{m}$ ,  $d_1 = 50$  nm,  $d_2 \leq 16$  nm, and t = 170 nm, then Ref. [70] reports a decrease in critical temperature to 80 K and subdued  $J_c = 2 \text{ MA} \cdot \text{cm}^{-2}$  and  $I_c R_N = 50 \ \mu\text{V}$  (for  $\Delta = 0.127 \text{ meV}$ ,  $I_c \approx 100 \ \mu\text{A}$

and  $R_N \approx 0.5 \Omega$ ). With these parameters specified, the previous models could be fit to this junction, with  $SGR \approx 10$ ,  $I_c = wtJ_c$ , and capacitance approximated geometrically:

$$\tan \alpha = \left| \frac{4(t-h) (d_1 - d_2)}{(d_1 - d_2)^2 - 4(t-h)^2} \right|$$

(3.5a)