## COMPUTE-IN-MEMORY PRIMITIVES FOR ENERGY-EFFICIENT MACHINE LEARNING

by

Amogh Agrawal

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana August 2021

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Kaushik Roy, Chair

School of Electrical and Computer Engineering

### Dr. Anand Raghunathan

School of Electrical and Computer Engineering

## Dr. Sumeet K. Gupta

School of Electrical and Computer Engineering

### Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

This work is dedicated to Baba, Amma, Mausi, Nanaji and Nani.

### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor Prof. Kaushik Roy for his continued support and guidance during my PhD study and research. His exceptional mentorship helped me shape myself as a researcher and allowed me to explore various interesting topics, while building my skills and critical thinking. I could not have imagined a better mentor for my PhD study.

I would also like to thank my committee members Prof. Anand Raghunathan, Prof. Sumeet Gupta, and Prof. Vijay Raghunathan for their encouragement and always being easily approachable. Their invaluable advice at each step of my PhD journey helped me stay motivated and focused.

My sincere thanks also goes to Dr. Ajey Jacob, Dr. Steven Woo and Dr. Thomas Vogelsang for offering me the summer internship opportunities for working on very exciting projects, which helped me broaden my scope and build network outside academia.

I thank all my fellow NRL members and alumni. Special thanks to Dr. Akhilesh Jaiswal for helping me get started on my first project, Dr. Ankit Sharma for all his help initially, and Dr. Minsuk Koo for the very helpful insights during the tapeout process. Also I thank all my collaborators: Mustafa, Nitin, Dr. Indranil Chakraborty, Dr. Deboleena Roy, Dr. Aayush Ankit, Dr. Chankyu Lee, Adarsh, Sangamesh, Dong Eun, Tanvi, Deepika, Utkarsh, Shubham, Eunseon, and Dr. Cheng Wang, with whom I had the pleasure of working, having stimulating discussions, and all the fun times together.

I would also like to acknowledge Nicole for efficiently administering C-BRIC and always being ready to offer help with almost anything.

Lastly, but most importantly, I would like to thank my parents Dr. Vivek Agrawal and Dr. Jolly, my sister Dr. Akanksha Agrawal, my brother-in-law Dr. Shrihari Kulkarni, and all friends and family for their unconditional love and support.

## TABLE OF CONTENTS

| LI | ST O | F TAB     | LES                                                             | 11 |

|----|------|-----------|-----------------------------------------------------------------|----|

| LI | ST O | F FIGU    | JRES                                                            | 12 |

| A  | BSTR | ACT       |                                                                 | 21 |

| 1  | INT  | RODU      | CTION                                                           | 23 |

| 2  |      |           | G IN-MEMORY BOOLEAN COMPUTATIONS IN STANDARD 8T                 | 27 |

|    | 2.1  | Introd    | luction                                                         | 27 |

|    | 2.2  | In-Me     | mory Computations in 8-Transistor SRAM Bit-Cells                | 31 |

|    |      | 2.2.1     | 8-Transistor SRAM: NOR operation                                | 33 |

|    |      | 2.2.2     | 8-Transistor SRAM: NAND operation                               | 35 |

|    |      | 2.2.3     | 8 Transistor SRAM: Voltage Divider Scheme for IMP and XOR gates | 36 |

|    |      | 2.2.4     | Proposed 'read-compute-store' (RCS) scheme                      | 40 |

|    | 2.3  | $8^+$ Tra | ansistor Differential Read SRAM                                 | 42 |

|    | 2.4  | Discus    | ssions                                                          | 45 |

|    | 2.5  | X-SR      | AM based non-standard von-Neumann Computing for AES Encryption  | 47 |

|    |      | 2.5.1     | Simulation Methodology                                          | 48 |

|    |      | 2.5.2     | Results and Discussion                                          | 49 |

|    | 2.6  | Conclu    | usion                                                           | 50 |

| 3 | ACCELERATING BINARY CONVOLUTIONAL NEURAL NETWORKS IN 10T |         |                                                  |    |  |  |  |  |  |  |

|---|----------------------------------------------------------|---------|--------------------------------------------------|----|--|--|--|--|--|--|

|   | SRA                                                      | M ARF   | RAYS                                             | 51 |  |  |  |  |  |  |

|   | 3.1                                                      | Introd  | uction                                           | 51 |  |  |  |  |  |  |

|   | 3.2                                                      | In-mer  | nory Binary Convolution – Proposal-A             | 54 |  |  |  |  |  |  |

|   |                                                          | 3.2.1   | Circuit Description                              | 55 |  |  |  |  |  |  |

|   |                                                          | 3.2.2   | Dual Read-Wordline based Dual-stage ADC          | 57 |  |  |  |  |  |  |

|   |                                                          | 3.2.3   | Sectioned Memory Array for Parallel Computing    | 61 |  |  |  |  |  |  |

|   |                                                          | 3.2.4   | Results                                          | 63 |  |  |  |  |  |  |

|   | 3.3                                                      | In-mer  | mory Binary Convolution – Proposal-B             | 64 |  |  |  |  |  |  |

|   |                                                          | 3.3.1   | Bitwise XNORs                                    | 65 |  |  |  |  |  |  |

|   |                                                          | 3.3.2   | Popcount                                         | 66 |  |  |  |  |  |  |

|   |                                                          | 3.3.3   | Results                                          | 67 |  |  |  |  |  |  |

|   | 3.4                                                      | Systen  | n-level Evaluation Framework for BNN             | 68 |  |  |  |  |  |  |

|   |                                                          | 3.4.1   | Simulation Methodology                           | 69 |  |  |  |  |  |  |

|   |                                                          | 3.4.2   | Mapping Weights and Activations to Xcel-RAM      | 70 |  |  |  |  |  |  |

|   |                                                          | 3.4.3   | Results and Discussion                           | 72 |  |  |  |  |  |  |

|   | 3.5                                                      | Conclu  | 1sion                                            | 74 |  |  |  |  |  |  |

| 4 | ENA                                                      | BLING   | DOT-PRODUCT COMPUTATIONS IN STANDARD 8T-SRAM AR- |    |  |  |  |  |  |  |

|   | RAY                                                      | 'S USIN | IG CHARGE ACCUMULATION AND SHARING               | 75 |  |  |  |  |  |  |

|   | 4.1                                                      | Introd  | uction                                           | 75 |  |  |  |  |  |  |

|   | 4.2                                                      | Relate  | d Works                                          | 78 |  |  |  |  |  |  |

|   | 4.3 | Charg  | e Sharing based In-Memory Dot-Product Operation                  | 79  |

|---|-----|--------|------------------------------------------------------------------|-----|

|   |     | 4.3.1  | 8T-SRAM: Structure and Operation                                 | 80  |

|   |     | 4.3.2  | 8T-SRAM: Charge sharing based Dot-Product Operation              | 81  |

|   |     | 4.3.3  | SPICE Characterization                                           | 82  |

|   |     | 4.3.4  | Self-Compensation                                                | 84  |

|   |     | 4.3.5  | Compensating for Transistor Non-linearity                        | 85  |

|   | 4.4 | č      | n Integration of CASH-RAM for Accelerating Ternary Weight Neural | 87  |

|   |     | 4.4.1  | Cache Integration                                                | 88  |

|   |     | 4.4.2  | Subarray Details                                                 | 88  |

|   |     | 4.4.3  | Data Mapping                                                     | 89  |

|   | 4.5 | Result | S                                                                | 89  |

|   |     | 4.5.1  | Experimental methodology                                         | 90  |

|   |     | 4.5.2  | Impact of Non-idealities on Classification Accuracy              | 90  |

|   |     | 4.5.3  | Energy, Delay and Area Estimates                                 | 92  |

|   | 4.6 | Conclu | usion                                                            | 97  |

| 5 | LOC | )KUP 7 | TABLE BASED COMPUTING USING ROM-EMBEDDED SRAM                    | 98  |

|   | 5.1 | Introd | uction                                                           | 98  |

|   | 5.2 | RECa   | che: Design and Operation                                        | 100 |

|   |     | 5.2.1  | 8T-SRAM                                                          | 100 |

|   |      | 5.2.2  | 8 <sup>+</sup> T Differential Read SRAM       | 103 |

|---|------|--------|-----------------------------------------------|-----|

|   | 5.3  | Evalua | ating RECache on realistic workloads          | 105 |

|   | 5.4  | Conclu | nsions                                        | 107 |

| 6 | SPIF | KING N | EURAL NETWORK ACCELERATION USING LOOKUP TABLE |     |

|   | BAS  | ED IN- | MEMORY-COMPUTING                              | 108 |

|   | 6.1  | Introd | uction                                        | 108 |

|   | 6.2  | Backg  | round                                         | 110 |

|   |      | 6.2.1  | ROM-Embedded RAMs                             | 110 |

|   |      | 6.2.2  | SNN: Spiking Neural Networks                  | 115 |

|   |      | 6.2.3  | LUT based storage in R-SRAMs and R-MRAMs      | 116 |

|   | 6.3  | SPAR   | E: SNN Accelerator using ROM-embedded RAMs    | 117 |

|   |      | 6.3.1  | SPARE Organization                            | 117 |

|   |      | 6.3.2  | Inter-layer pipelining                        | 120 |

|   |      | 6.3.3  | Processing Element (PE)                       | 121 |

|   |      | 6.3.4  | Modeling complex neuro-synaptic functionality | 123 |

|   | 6.4  | Experi | imental Methodology                           | 124 |

|   | 6.5  | Result | 8                                             | 126 |

|   |      | 6.5.1  | Energy                                        | 126 |

|   |      | 6.5.2  | Area                                          | 130 |

|   |      | 6.5.3  | Performance                                   | 130 |

|   |     | 6.5.4  | Complex neuro-synaptic models                            | 130 |

|---|-----|--------|----------------------------------------------------------|-----|

|   | 6.6 | Conclu | nsion                                                    | 131 |

| 7 |     |        | GITAL COMPUTE-IN-MEMORY MACRO ENABLING SPIKE-BASE        |     |

|   | SEQ | UENTI  | AL LEARNING IN 10T SRAM ARRAY                            | 133 |

|   | 7.1 | Introd | uction                                                   | 133 |

|   | 7.2 | IMPU   | LSE: Structure and Operation                             | 134 |

|   |     | 7.2.1  | Reconfigurable Column Peripherals                        | 136 |

|   |     | 7.2.2  | In-Memory SNN Instructions                               | 137 |

|   |     | 7.2.3  | Multiple Neuron Functionalities                          | 139 |

|   | 7.3 | Impler | nentation Results                                        | 139 |

|   | 7.4 | Multi- | macro Architecture                                       | 143 |

|   |     | 7.4.1  | Introduction                                             | 143 |

|   |     | 7.4.2  | Zero-skipping                                            | 145 |

|   |     | 7.4.3  | Macro Pipeline                                           | 146 |

|   |     | 7.4.4  | Support for Multiple Bit-precision                       | 148 |

|   |     | 7.4.5  | Configurations for Low and High Fan-in CNN Layers        | 149 |

|   |     | 7.4.6  | Timestep Pipelining: Leveraging Additional Weight Re-use | 151 |

|   |     | 7.4.7  | Preliminary Results                                      | 152 |

|   | 7.5 | Conclu | nsion                                                    | 153 |

| 8 | SUM | IMARY  | AND FUTURE DIRECTIONS                                    | 155 |

| Α  | CHA   | LLENC  | GES WITH       | 6T SRA   | AM FO   | OR EN | VABI | ING | COM | IPU7 | ГЕ-II | N-M | EMC | DRY | • | 156 |

|----|-------|--------|----------------|----------|---------|-------|------|-----|-----|------|-------|-----|-----|-----|---|-----|

|    | A.1   | Opera  | tion of $6T S$ | RAM      | •••     |       |      | ••• |     |      |       |     |     |     |   | 156 |

|    | A.2   | Read S | Stability Ch   | allenges | s due t | o CIM | 1.   | ••• |     |      | •••   |     |     |     |   | 156 |

|    |       | A.2.1  | Short-circu    | it path  | s       |       |      | ••• |     |      | •••   |     |     |     |   | 156 |

|    |       | A.2.2  | Pseudo-wr      | ite      | •••     |       |      | ••• |     |      | •••   |     |     |     | • | 158 |

| Rł | EFER  | ENCES  | 5              |          | •••     |       |      | ••• |     |      | •••   |     |     |     |   | 159 |

| VI | TA    |        |                |          | •••     |       |      | ••• |     |      |       |     |     |     |   | 174 |

| PU | JBLIC | CATIO  | NS             |          |         |       |      |     |     |      |       |     |     |     |   | 175 |

## LIST OF TABLES

| 2.1 | Summary of proposals described in the manuscript. The table shows average energy consumption per-bit and latency for the in-memory operations on various bit-cells. Pros and cons of each proposal are also listed | 44  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Benchmark Binary Neural Network [6] used for classifying CIFAR10 and SVHN datasets.                                                                                                                                | 71  |

| 4.1 | Hardware Parameters Description                                                                                                                                                                                    | 94  |

| 4.2 | Network Parameters Description                                                                                                                                                                                     | 95  |

| 4.3 | Energy, Delay, and Area Comparison                                                                                                                                                                                 | 95  |

| 4.4 | Area breakdown                                                                                                                                                                                                     | 96  |

| 5.1 | Benchmarks used to evaluate RECache [49], [118]                                                                                                                                                                    | 105 |

| 5.2 | ROM and RAM energy per-access for various array sizes obtained from CACTI.                                                                                                                                         | 106 |

| 7.1 | Energy Efficiency of SNN over LSTM.                                                                                                                                                                                | 142 |

| 7.2 | Comparison with prior works.                                                                                                                                                                                       | 143 |

## LIST OF FIGURES

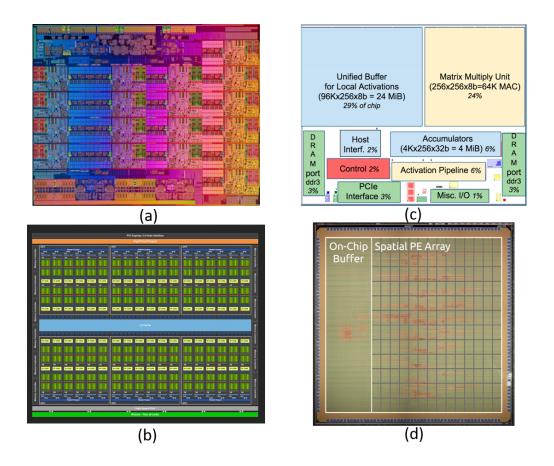

| 1.1 | (a) Intel Xeon CPU [18]. (b) NVIDIA Turing GPU [19]. (c) Google TPU [20]. (d) Eyeriss chip [21].                                                                                                                                                                                                                                                                                                                                                                                                    | 25 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

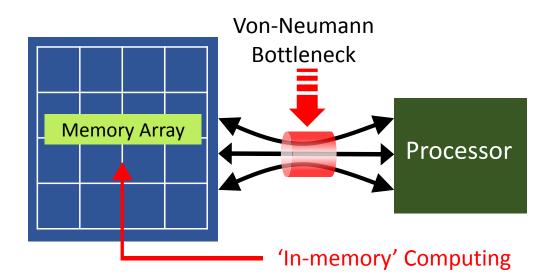

| 2.1 | Illustration of the von-Neumann bottleneck. Frequent to-and-fro data trans-<br>fers between the processor and memory units incur large energy consumption<br>and limits the throughput. Computing within the memory array enhances the<br>memory functionality thereby reducing the number of unnecessary transfers<br>of data for certain class of operations like vector bit-wise Boolean logic <i>etc.</i> .                                                                                     | 28 |

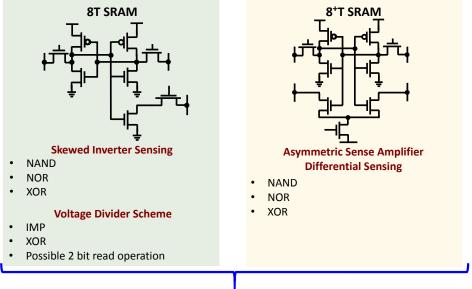

| 2.2 | A summary of <i>In-Memory</i> computing schemes proposed. With respect to the 8T cell, we present bit-wise NAND, NOR and XOR operations using skewed inverter sensing. Further, we present the voltage-divider based operation of 8T-cells for IMP and XOR gates. With respect to the 8 <sup>+</sup> T-cells, we present bit-wise NAND, NOR and XOR operations using asymmetric differential SAs. Moreover, a <i>'read-compute-store'</i> operation has been presented for both types of bit-cells. | 29 |

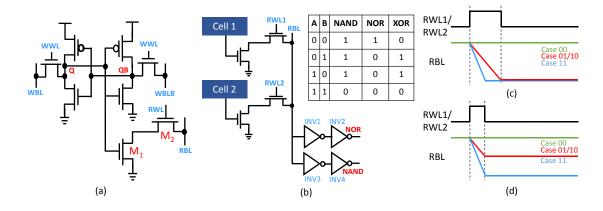

| 2.3 | a) Schematic of a standard 8T-SRAM bit-cell. In addition to the standard 6T cell, two additional transistors form the read path using a separate read bit-line (RBL). b) Single ended sensing of NAND/NOR using gated skewed inverters. Figure also shows the truth table for NAND/NOR/XOR operations. c) Timing diagram for reading NOR output of Cell 1 and Cell 2. d) Timing diagram for reading NAND output of Cell 1 and Cell 2                                                                | 32 |

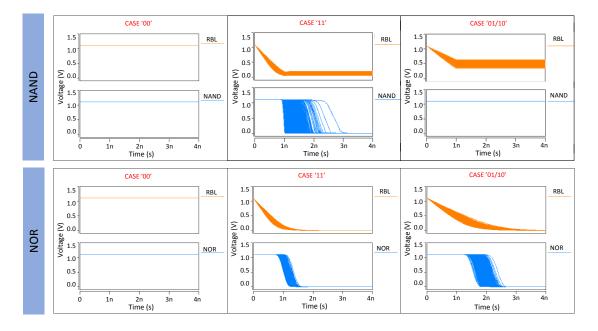

| 2.4 | Monte-Carlo simulations in SPICE for NAND and NOR outputs for all possible input cases $-$ '00,01,10,11', in presence of 30mV sigma variations in threshold voltage.                                                                                                                                                                                                                                                                                                                                | 33 |

| 2.5 | Monte-Carlo simulations across process corners (TT corner and SS corner shown) under voltage and temperature variations for NAND outputs for the borderline cases $-$ '01/10' and '11'. The distribution of RBL voltage is plotted under 30mV sigma threshold voltage variations for two different temperatures and $\pm 10\%$ variation in nominal $V_{DD}$ .                                                                                                                                      | 34 |

| 2.6 | a) Circuit schematic of the 8T-SRAM for implementing the voltage-divider scheme. b) Equivalent circuit traced by transistors $M1 - M4$ while data is read from Cell 1 and Cell 2. c) Monte-Carlo simulations in SPICE for all possible input cases, showing the output of the two asymmetric inverters                                                                                                                                                                                              | 37 |

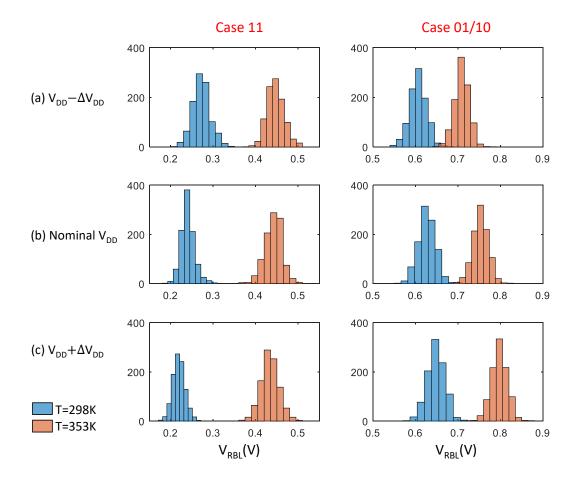

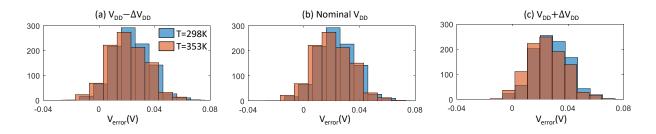

| 2.7  | Monte-Carlo simulations with variations in supply voltage and temperature<br>across process corners for the voltage-divider scheme for the case (1,1). $V_{error}$<br>is defined as the difference between the RBL voltage (when both the operands<br>are '1') and the initial pre-charge voltage $V_{pre}$ . The distribution of $V_{error}$<br>is plotted under 30mV sigma threshold voltage variations for two different<br>temperatures and $\pm 10\%$ variation in nominal $V_{DD}$ . The variations in $V_{pre}$ are<br>also accounted for. | 38 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

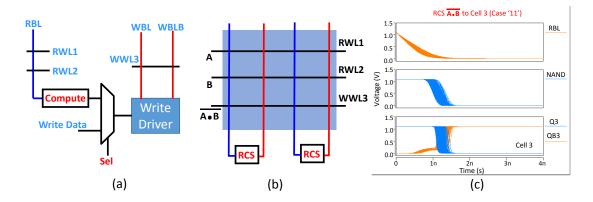

| 2.8  | a) Proposed 'read-compute-store' (RCS) scheme. RWL1 and RWL2 are en-<br>abled, corresponding to the data to be computed. The computation output<br>is selectively passed to the write-driver of that column, while simultaneously<br>enabling the WWL3, where data is to be stored. b) Block diagram showing<br>the RCS blocks in the memory array. The NAND of row 1 and row 2 is to<br>be stored in row 3. c) Monte-Carlo simulations in SPICE, showing the final<br>state of Cell 3 stores the desired output.                                 | 40 |

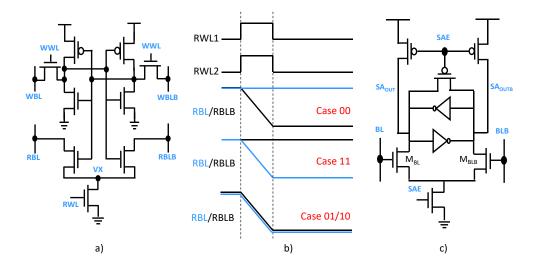

| 2.9  | a) Circuit schematic of an $8^+T$ Differential SRAM bit-cell [45]. b) Timing diagram used for in-memory computations on the $8^+T$ Differential SRAM. c) Circuit schematic of the proposed asymmetric differential sense amplifier                                                                                                                                                                                                                                                                                                                | 41 |

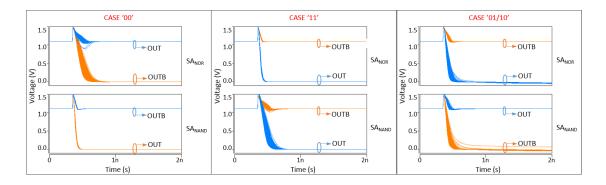

| 2.10 | Monte-Carlo simulations in SPICE for SA outputs for all possible input cases $-$ '00,01,10,11', in presence of 30mV sigma variations in threshold voltage.                                                                                                                                                                                                                                                                                                                                                                                        | 42 |

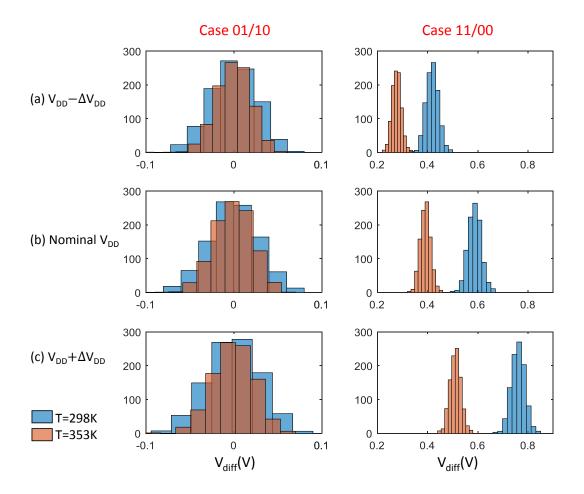

| 2.11 | Monte-Carlo simulations across process corners under $V_T$ and temperature<br>and supply-voltage variations for the 8 <sup>+</sup> T SRAM configuration for the cases<br>'01/10' and '11/00'. $V_{diff}$ is defined as the absolute difference between the<br>RBL and RBLB voltages at the instant when the sense amplifier is enabled.<br>The distribution of $V_{diff}$ is plotted under 30mV sigma threshold voltage vari-<br>ations for two different temperatures and $\pm 10\%$ variation in nominal $V_{DD}$ .                             | 43 |

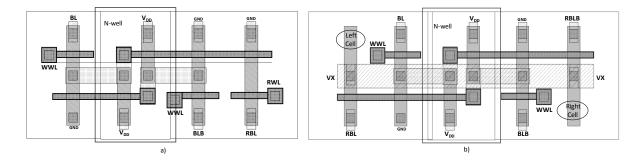

| 2.12 | a) Thin cell layout for the standard 8T-SRAM bit-cell shown in Fig. 2.3(a).<br>b) Thin cell layout for the 8 <sup>+</sup> T Differential SRAM bit-cell [45] illustrated in<br>Fig. 2.9(a). Left- and right-most diffusion tracks are shared with adjacent<br>bit-cells. The ninth transistor in Fig. 2.9(a) is common for the row and is<br>connected at the periphery to the node 'VX'.                                                                                                                                                          | 46 |

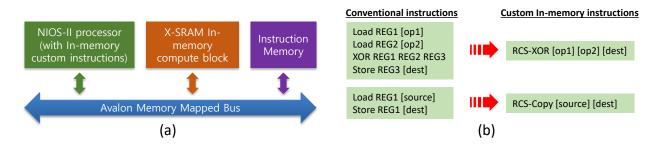

| 2.13 | (a) System-level implementation of a typical von-Neumann architecture with X-SRAM as the memory block. The processor, data-memory and the instruction-<br>memory blocks are connected via a shared system bus. (b) Illustration of cus-<br>tom in-memory instructions added to the instruction set of the Nios-II pro-<br>cessor. Substituting in-memory instructions reduces unnecessary read-writes<br>into the memory.                                                                                                                         | 47 |

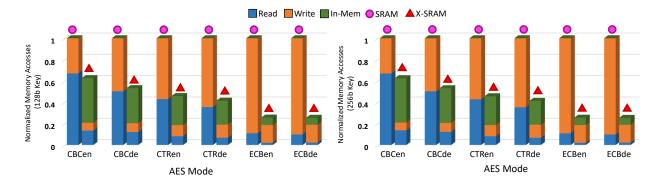

| 2.14 | Normalized number of memory accesses for various AES encryption and de-<br>cryption modes and two different key-sizes, with and without using X-SRAM<br>custom in-memory instructions. The total memory transactions are split into<br>memory read instructions, memory write instructions and custom in-memory<br>instructions.                                                                                                                                                                                                                  | 19 |

|      | instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48 |

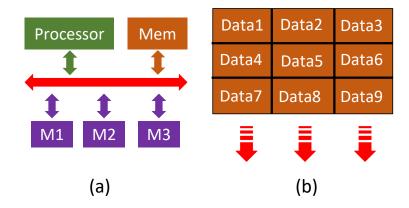

| 2.15 | (a) Realistic scenario for a typical system with multiple masters over a shared<br>bus. An arbiter keeps track of the memory traffic and controls which master<br>has access to the bus at a given point in time. (b) Data-parallelism in memory<br>arrays. X-SRAM performs bit-wise operations throughout the row, where<br>each row may store multiple data words. Thus multiple computations occur<br>in parallel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

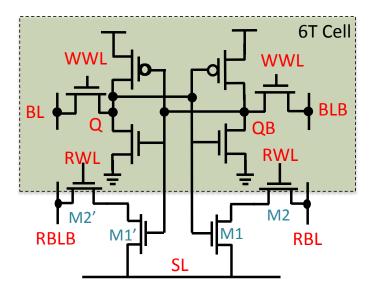

| 3.1  | The 10 transistor SRAM cell featuring a differential decoupled read-port com-<br>prising of transistors M1-M2 and M1'-M2'. The write port is constituted by<br>write access transistors connected to WWL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 54 |

| 3.2  | Illustration of the binary convolution operation within the 10T-SRAM array.<br>a) Step 1: Pseudo-read. RBLs/RBLBs are pre-charged and RWL for a row<br>storing the input activation (A1) is enabled. Depending on the data A1,<br>RBLs/RBLBs either discharge or stay pre-charged. The SAs are not enabled,<br>in contrast to a usual memory read. Thus, the charge on RBLs/RBLBs repre-<br>sent the data A1. b) Step 2: XNOR on SL. Once the charges on RBLs/RBLBs<br>have settled, RWL for the row storing the kernel (K1) is enabled. Charge shar-<br>ing occurs between the RBLs/RBLBs and the SL, depending on the data K1.<br>The RBLs either deposit charge on the SL, or take away charge from SL. c)<br>The truth table for Step 2 is shown. The pull-up and pull-down of the SL<br>follow the XNOR truth table. Moreover, since the SL is common along the<br>row, the pull-ups and pull-downs are cumulative. Thus, the final voltage on<br>SL represents the XNOR + <i>popcount</i> of A1 and K1. | 56 |

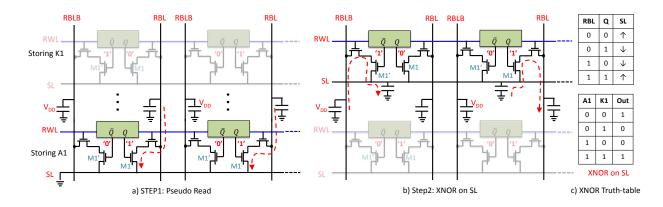

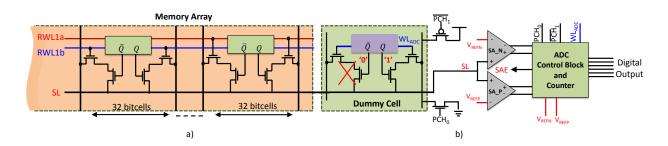

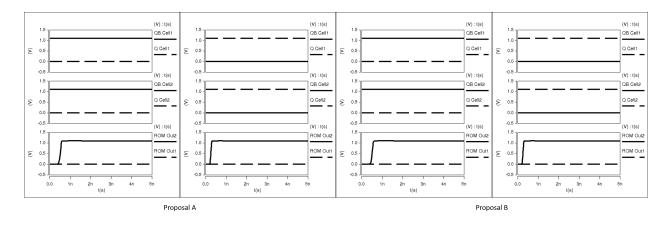

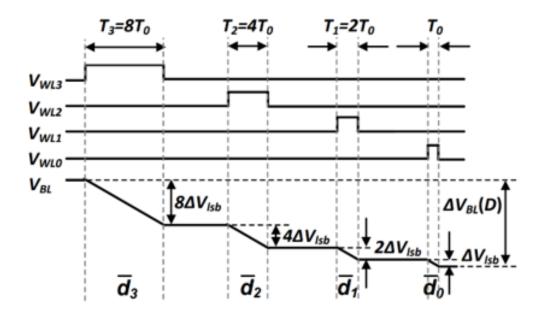

| 3.3  | a) Dual RWL technique. b) Dual-stage ADC scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57 |

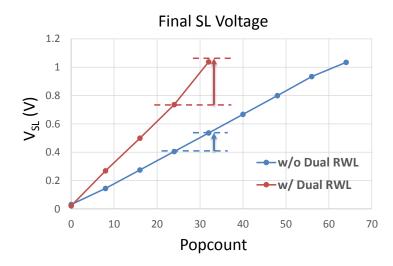

| 3.4  | The plot shows the final SL voltage with and without the Dual RWL approach. A larger sense margin is obtained with our Dual RWL approach, thus relaxing the constraints on the low-overhead ADC. Note that with Dual RWL technique we restrict the distinct voltage levels on SL to 32 at a time, instead of 64. However, the voltage swing on SL remains the same, thereby increasing the sense margin between the states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 58 |

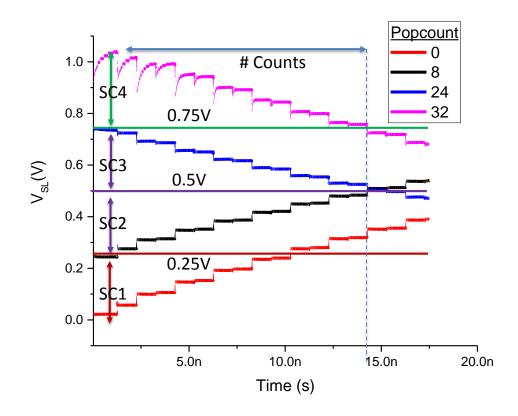

| 3.5  | The figure shows the timing diagrams for the dual-stage ADC scheme. The figure plots the SL voltage for various <i>popcount</i> cases. In the first-stage, the sub-class SC1-4 is determined using multiple references (0.25V, 0.5V and 0.75V). In the second-stage, charge is pumped-in/out of SL successively, depending on the SC. The number of cycles it takes for SL to reach $V_{REF}$ are counted. $V_{REF}$ for SC1-4 is 0.25V, 0.5V, 0.5V and 0.75V, respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59 |

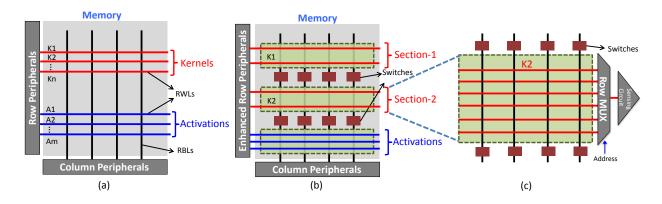

|      | activations A1-Am, and kernels K1-Kn. b) Proposed sectioned-SRAM array.<br>By introducing switches along the RBLs, the array is divided into sections.<br>The kernels are mapped into the sectioned-SRAM with each section storing<br>different kernel. Once the activations are read onto the RBLs, the switches<br>are opened, and the memory array is divided into sections. c) Since the RBLs<br>for each section have been decoupled, one RWL in each section can be si-<br>multaneously enabled such that each section performs the binary convolution<br>concurrently. The Row-MUX connects the corresponding SL to the sensing<br>circuit. For example, if A1 was read onto the RBLs before sectioning, en-<br>abling the rows K1 and K2 in Section 1 and 2 respectively, we obtain A1*K1<br>and A1*K2 in parallel on the SLs, which are sensed by the ADC. | 61 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

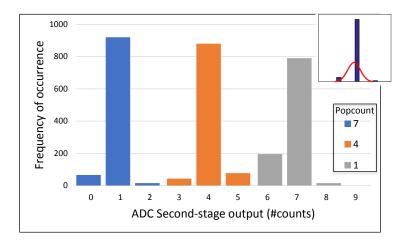

| 3.7  | Monte-Carlo simulations. The figure plots the histogram of the second-stage output of the ADC, for various <i>popcount</i> cases, in presence of process variations. Inset: Each histogram is fitted with a Gaussian distribution. The average standard deviation of the counts is $\sim 0.4359$ . The trend repeats for higher <i>popcount</i> cases with modulo-8, since only the lower 3bits of the output are generated in the second-stage.                                                                                                                                                                                                                                                                                                                                                                                                                    | 64 |

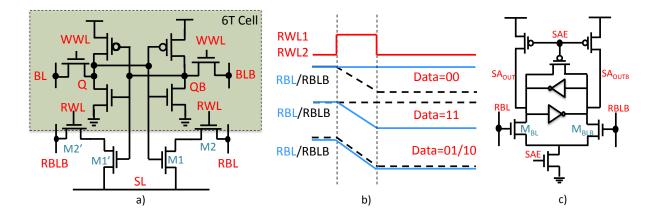

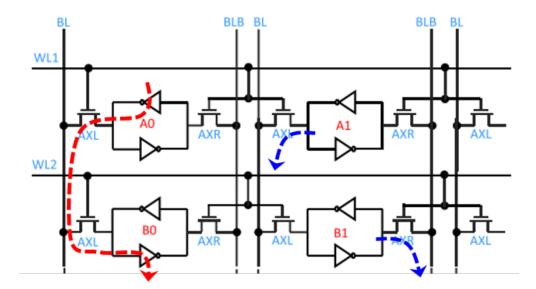

| 3.8  | (a) A 10T-SRAM bitcell schematic is repeated here for convenience. (b)<br>Timing diagram used for in-memory computing with 10T-SRAM bitcells. (c)<br>Circuit schematic of the asymmetric differential sense amplifier. [61]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 65 |

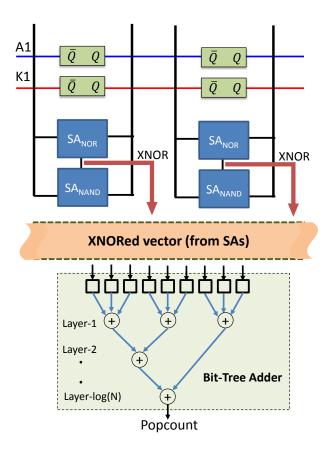

| 3.9  | Modified peripheral circuitry of the SRAM array to enable binary convolution operations. It consists of two asymmetric SAs - $SA_{NOR}$ and $SA_{NAND}$ which pass the XNORed data vector to a bit-tree adder. The adder has log(N) layers, where N is the number of inputs to the adder. It sums the input bits to generate the <i>popcount</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67 |

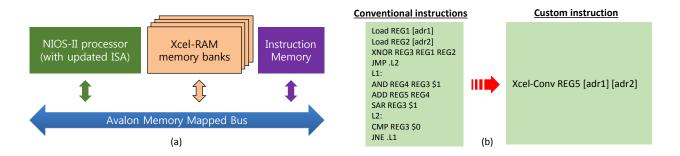

| 3.10 | (a) Modified von-Neumann architecture based on Xcel-RAM memory banks<br>and enhanced instruction set architecture (ISA) of the processor. (b) Snip-<br>pet of assembly code for performing a binary convolution operation using<br>conventional instructions and custom instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68 |

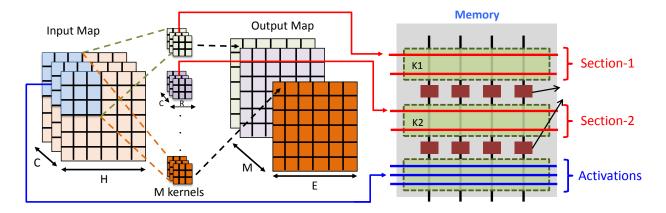

| 3.11 | Mapping of weights and activations of a convolutional neural network to Xcel-<br>RAM. The kernels and the input feature maps are flattened and stored into<br>multiple rows in the memory array. Xcel-RAM banks have dedicated rows<br>for storing kernels and activations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 70 |

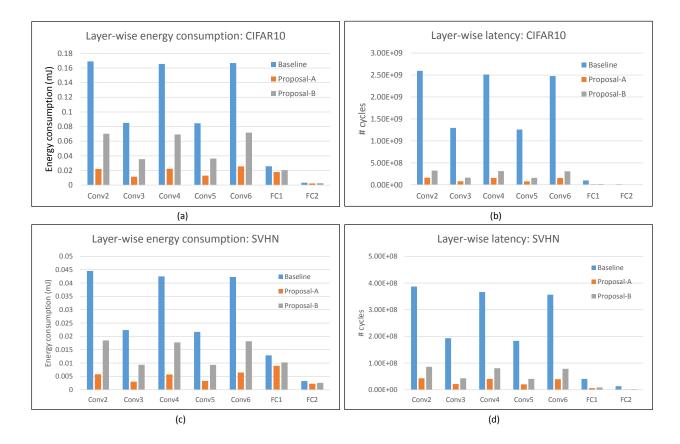

| 3.12 | Layer-wise energy consumption and latency, for running the CIFAR-10 (a-b), and SVHN (c-d) image classification benchmarks on the proposed designs, and the baseline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |

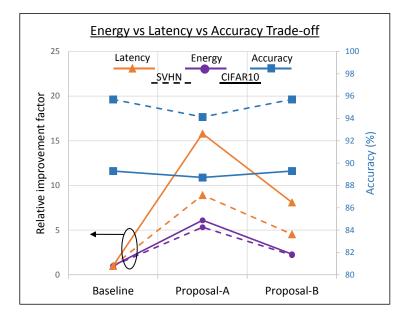

| 3.13 | Energy, latency and accuracy tradeoff for classifying CIFAR-10 and SVHN dataset with BNN, using the proposed techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 73 |

3.6 a) Typical SRAM memory array with row and column peripherals storing the

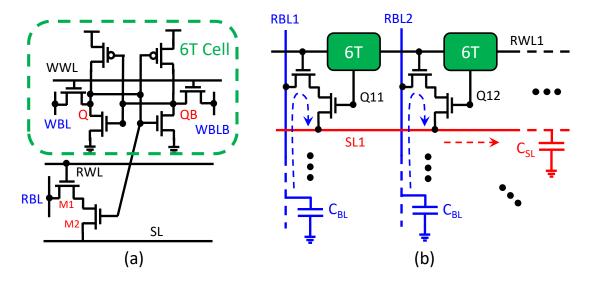

| 4.1 | (a) Schematic of the standard 8T-SRAM bitcell (b) Parasitic capacitance $C_{BL}$ and $C_{SL}$ for an array of 8T-SRAM cells. The dotted arrows show the charge-sharing path used in our approach.                                                                                                                                                                                                                                                                                                                                                                         | 80  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

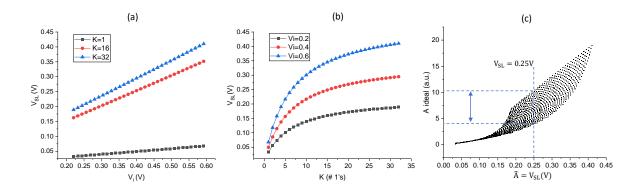

| 4.2 | Data obtained from SPICE simulations. (a) Final SL voltage as a function of input voltage $v_i$ . Three cases of $K=1,16,32$ are shown. (b) Final SL voltage as a function of $K$ . Three cases for $v_i=0.2,0.4,0.6$ V are shown. (c) Representation of $V_{SL}$ as a function of ideal dot product $A$ . The degree of spread represents the non-idealities, as illustrated in the figure taking an example of $V_{SL}=0.25$ V.                                                                                                                                         | 83  |

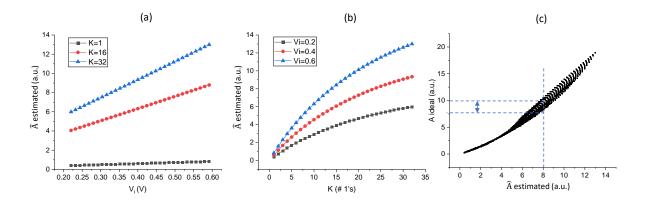

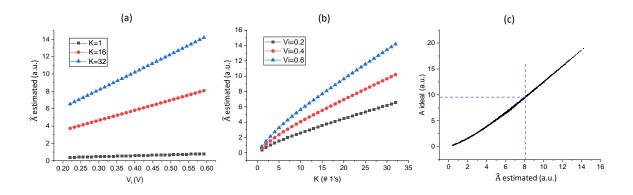

| 4.3 | Data obtained from SPICE simulations and $\hat{A}$ estimated from Eq. 4.8. (a) $\hat{A}$ as a function of input voltage $v_i$ . Three cases of $K=1,16,32$ are shown.<br>(b) $\hat{A}$ as a function of $K$ . Three cases for $v_i=0.2,0.4,0.6$ V are shown. (c) Representation of $\hat{A}$ as a function of ideal dot product $A$ . The degree of spread is significantly lower than in Fig. 4.2(c).                                                                                                                                                                    | 85  |

| 4.4 | Data obtained from SPICE simulations and $\hat{A}$ estimated from Eq. 4.9. (a) $\hat{A}$ as a function of input voltage $v_i$ . Three cases of $K=1,16,32$ are shown.<br>(b) $\hat{A}$ as a function of $K$ . Three cases for $v_i=0.2,0.4,0.6$ V are shown. (c) Representation of $\hat{A}$ as a function of ideal dot product $A$ . The degree of spread has further reduced significantly than in Fig. $4.3$ (c)                                                                                                                                                       | 86  |

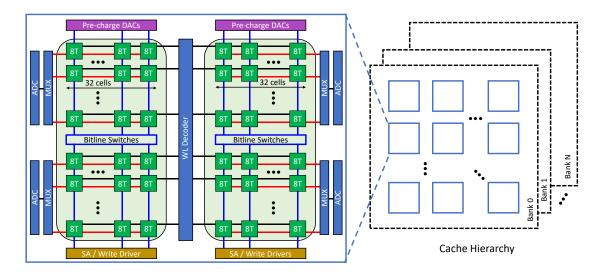

| 4.5 | CASH-RAM system integration for accelerating TWNNs. A typical multi-<br>bank cache hierarchy is shown on the right, where each bank consists of mul-<br>tiple sub-arrays. The subarray is shown on the left, with additional peripheral<br>circuitry to augment dot-product computations within the cache                                                                                                                                                                                                                                                                 | 87  |

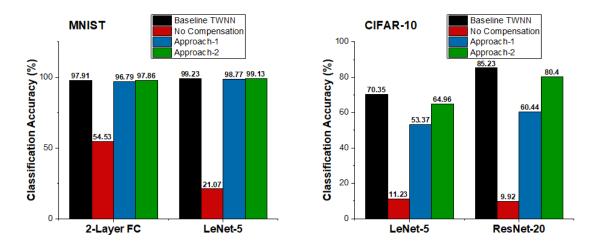

| 4.6 | Classification accuracy obtained on MNIST and CIFAR-10 datasets for differ-<br>ent benchmarks, for with and without self-compensation. Approach-1 corre-<br>sponds to self-compensation while Approach-2 corresponds to compensating<br>for transistor non-linearity.                                                                                                                                                                                                                                                                                                     | 91  |

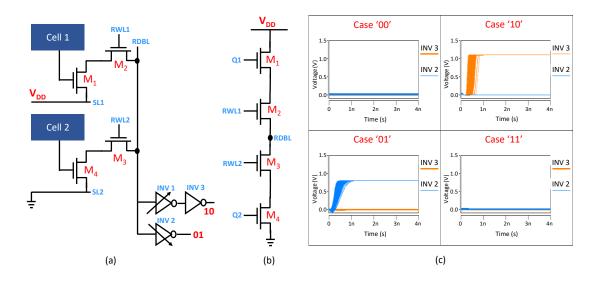

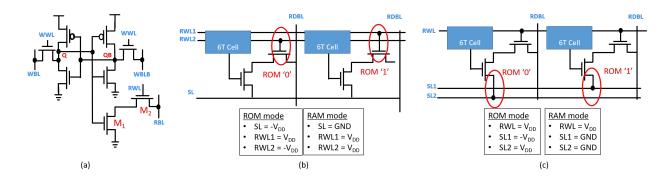

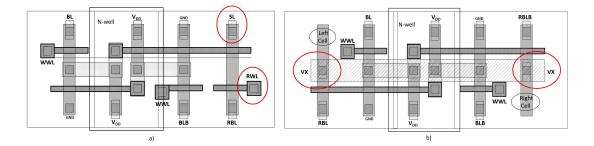

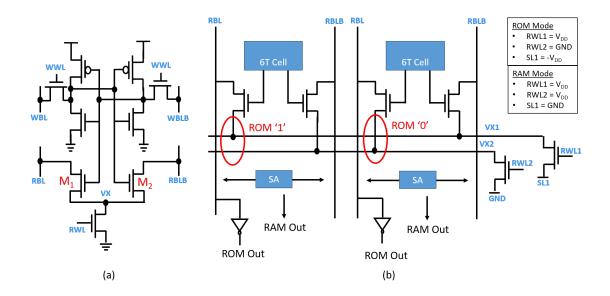

| 5.1 | (a) Schematic of a standard 8T-SRAM bitcell. Transistors M1 and M2 form<br>the decoupled read port of the SRAM cell. (b) Proposal-A for RECache.<br>The cell has an extra RWL, and the ROM data stored is '1' if the access<br>transistor is connected to RWL1, and '0' if it is connected to RWL2. The node<br>voltages for RAM and ROM modes of operation are listed. (c) Proposal-B<br>for RECache. This configuration has two SLs, instead of two RWLs. ROM<br>data stored is '1' if the access transistor is connected to SL1, and '0' if it is<br>connected to SL2. | 99  |

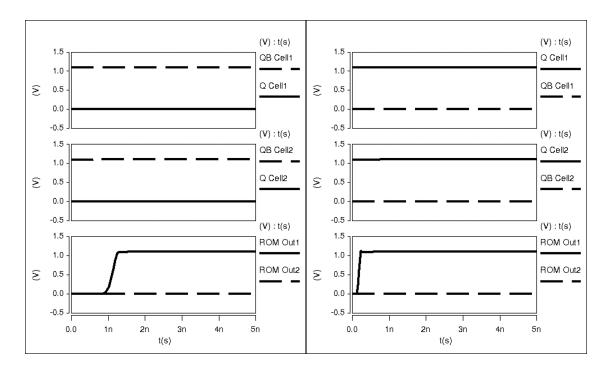

| 5.2 | Timing diagrams generated from HSPICE for Proposal-A,B. The correct ROM Output data is generated, without disturbing the RAM data stored in the cell. The circuit shown in Fig. 5.1(b-c) are simulated.                                                                                                                                                                                                                                                                                                                                                                   | 100 |

| 5.3 | (a) Thin cell layout of a standard 8T-SRAM cell. The circled contacts, RWL and SL, are common to adjacent bitcells in the horizontal and vertical direction, respectively. (b) Thin cell layout of the 8 <sup>+</sup> T-SRAM bit-cell. The circled contacts (VX) on either side of the bitcell are shared by adjacent bitcells                                                                                                                                                                         | 101 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4 | (a) Schematic of the differential 8 <sup>+</sup> T-SRAM bitcell. Transistors M1 and M2 form a differential read port decoupled from the 6T write port. The ninth transistor connected to RWL is common for the entire row. (b) RECache using the differential 8 <sup>+</sup> T-SRAM. The connection of M1 to either VX1 or VX2 determines the ROM bit stored in the cell. The ROM retrieval process is exactly same as the 8T-RECache. The node voltages for ROM and RAM mode of operation are listed. | 102 |

| 5.5 | Timing diagrams obtained from HSPICE. The correct ROM Output data is generated, without disturbing the RAM data stored in the cell. The circuit shown in Fig. 5.4(b) was simulated                                                                                                                                                                                                                                                                                                                     | 103 |

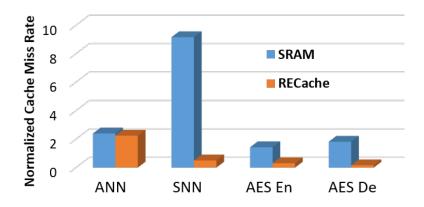

| 5.6 | Normalized cache miss-rate for various benchmarks – artificial neural network (ANN), spiking neural network (SNN) and advanced encryption standard (AES), with RECache and standard SRAM caches.                                                                                                                                                                                                                                                                                                       | 104 |

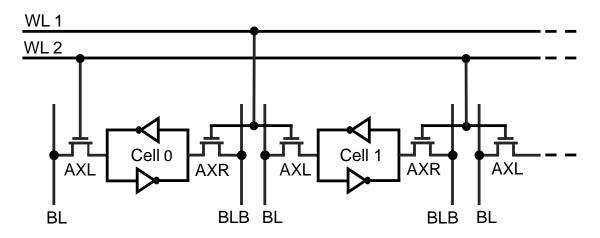

| 6.1 | R-SRAM Schematic: Standard 6T-SRAM embedded with ROM. The only difference is the addition of extra word-line (WL1 and WL2) to embed ROM functionality.                                                                                                                                                                                                                                                                                                                                                 | 109 |

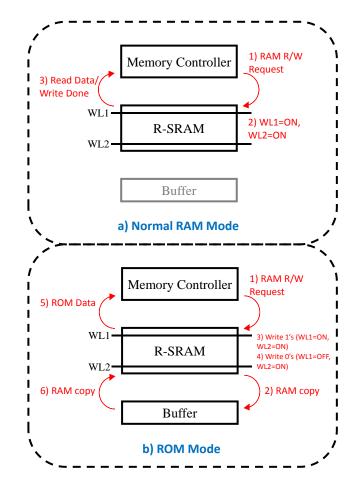

| 6.2 | Operation of R-SRAM in a) Normal RAM Mode and b) ROM Mode                                                                                                                                                                                                                                                                                                                                                                                                                                              | 111 |

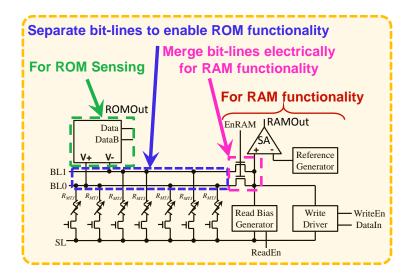

| 6.3 | R-MRAM Schematic: Standard STT-MRAM array with two bit-lines (BL1 and BL0) to embed ROM functionality. The peripheral circuitry for RAM and ROM mode of operation is highlighted.                                                                                                                                                                                                                                                                                                                      | 112 |

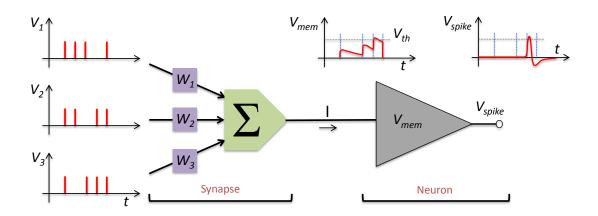

| 6.4 | Typical SNN dynamics. The input spikes are modulated by the synaptic weights, and the accumulated synaptic current in fed to the neuron. The neuron integrates the current and outputs a spike (fires) once its membrane potential exceeds a threshold.                                                                                                                                                                                                                                                | 113 |

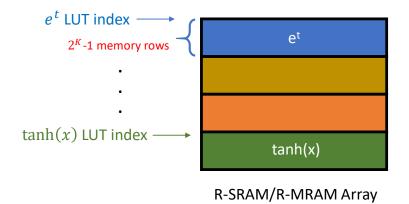

| 6.5 | Storage of LUTs for various functions within the same ROM-Embedded RAM array. The starting address for each type of LUT is predefined. An offset address (calculated from the input) is added to the starting address to perform the table lookup from the R-SRAM/R-MRAM. The number of memory rows required by each LUT type is predefined based on the desired precision of the transcendental function to be stored.                                                                                | 113 |

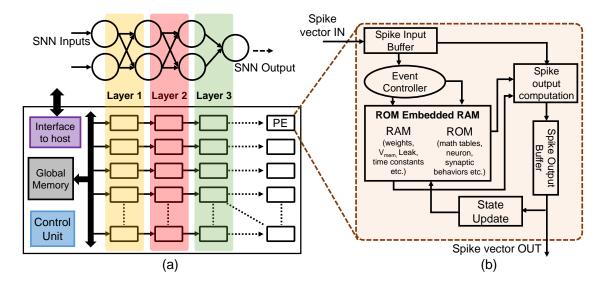

| 6.6  | Block level diagram of SPARE. (a) Figure shows how a deep neural network<br>is mapped to a 2-D array of PEs connected together. The global memory<br>stores the spiking events at every layer output, and broadcasts them to the<br>input of next layer. (b) Figure zooms into the logical diagram of the PE. It<br>consists of a ROM-embedded RAM to store the state variables along with<br>LUTs of synapse, neuron and synaptic plasticity models, computation core<br>to generate output spikes, input buffers to store incoming spike broadcast,<br>event controller to schedule memory transactions, state updater to update<br>the entries in the memory, and an output buffer to store the output spikes<br>generated. | 114 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

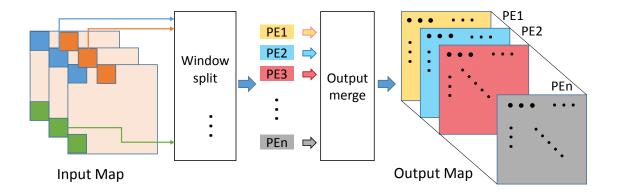

| 6.7  | Mapping of CNNs in SPARE: The input map is window-split based on the kernel size of the particular layer. These are then broadcast to all PEs mapped to that layer. Each PE stores different kernels, and process the data in parallel as they receive the inputs in a window split-manner. Each PE computes part of the output feature map, highlighted through color coding of PEs in figure. The output is rearranged and stored back to the global memory unit.                                                                                                                                                                                                                                                            | 118 |

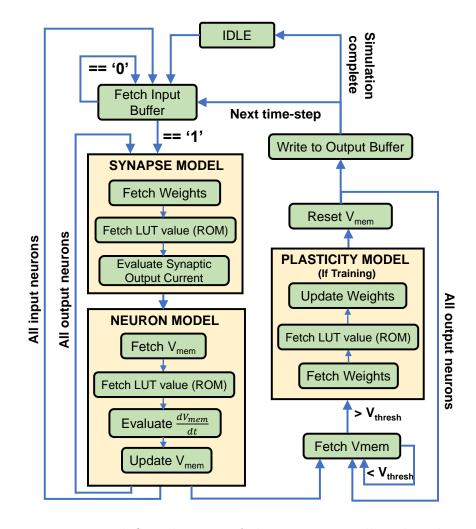

| 6.8  | Logical flow diagram of the event controller, describing SNN computations<br>performed in the PE. The subsequent computation is subdivided into three<br>main blocks. 1) Synapse model block: computes output synaptic current.<br>2) Neuron model block: keeps track of the membrane potential of output<br>neurons. 3) Plasticity model block: updates synaptic weights during the<br>training phase. This block is skipped during the inference phase.                                                                                                                                                                                                                                                                      | 119 |

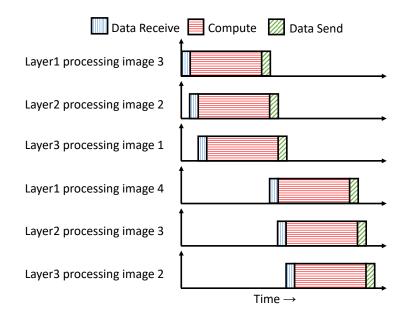

| 6.9  | Timing diagram illustrating the inter-layer pipelining in SPARE. As soon as<br>the PEs receive and buffer the input data, they start processing. Meanwhile,<br>data for PEs mapped to subsequent layers is transmitted. Since the data<br>transfer time is small compared to the computation time within the PE, all<br>PEs process data in parallel.                                                                                                                                                                                                                                                                                                                                                                          | 120 |

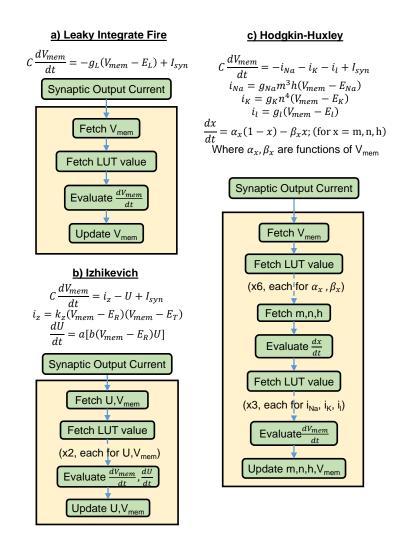

| 6.10 | Differential equations describing the dynamics of neurons and an LUT based approach to implement them in SPARE. (a) Leaky-integrate-fire neuron (b) Izhikevich neuron (c) Hodgkin-Huxley neuron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 122 |

| 6.11 | Energy and latency for read-write accesses from all designs considered – SRAM, R-SRAM, STT-MRAM, and R-MRAM. (* ROM Read for R-SRAM includes additional overhead of buffering RAM, retrieving ROM data and storing back the buffered RAM data, as described in Section 6.2.1).                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 123 |

| 6.12 | uArchitecture design parameters used for simulations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 123 |

| 6.13 | SNN benchmarks used in SPARE evaluation [118], [129]. The figure tabulates the number of PEs required, memory requirement, and the RAM/ROM content for each benchmark and neuron model.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 124 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -   |

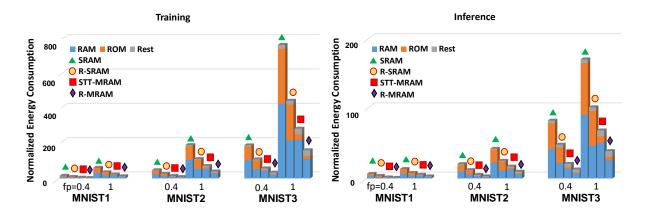

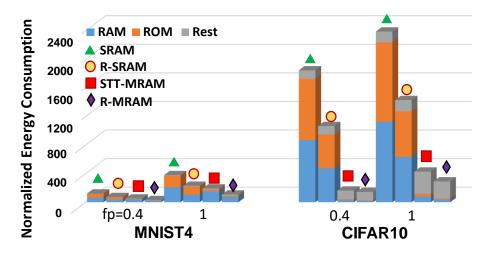

| 6.14 | Normalized energy consumption for a) Training phase and b) Inference phase,<br>for benchmarks 'MNIST1-3'. The simulations are performed for max firing<br>rate $fp = 0.4$ and 1. The energy bars are further split into RAM (read/write<br>energy + leakage), ROM (read energy + leakage) and Rest (core energy).<br>The energy values are normalized to the common base reference | 126 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.15 | Normalized energy consumption for benchmarks 'MNIST4' and 'CIFAR10'. The simulations are performed for max firing rate $fp = 0.4$ and 1. The energy bars are further split into RAM (read/write energy + leakage), ROM (read energy + leakage) and Rest (core energy). The energy values are normalized to the common base reference.                                              | 127 |

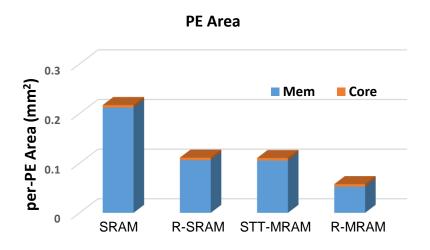

| 6.16 | per-PE area with SRAM, R-SRAM, STT-MRAM and R-MRAM as memory units (for iso-storage).                                                                                                                                                                                                                                                                                              | 129 |

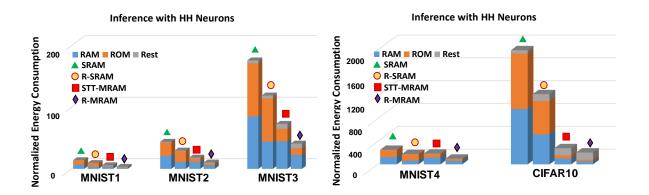

| 6.17 | Normalized energy consumption for using Hodgkin-Huxley neuron models on SNN benchmarks. The simulations are performed for max firing rate $fp = 0.4$ . The energy bars are further split into RAM (read/write energy + leakage), ROM (read energy + leakage) and Rest (core energy). The energy values are normalized to the common base reference.                                | 129 |

| 7.1  | (a) LSTM having hidden state (h <sup>t</sup> , C <sup>t</sup> ) for processing sequential tasks. (b) Intrinsic temporal dynamics of neuron membrane potentials ( $V^t_{MEM}$ ) in SNNs for processing sequential tasks.                                                                                                                                                            | 134 |

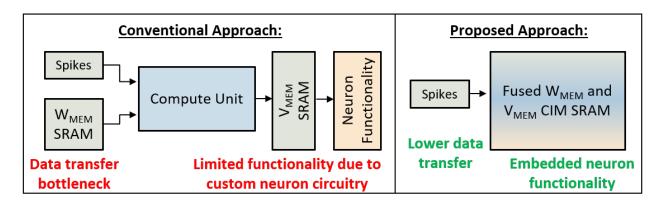

| 7.2  | Limitations of current digital SNN hardware accelerators and our proposed approach of fused weight and membrane potential CIM SRAM.                                                                                                                                                                                                                                                | 134 |

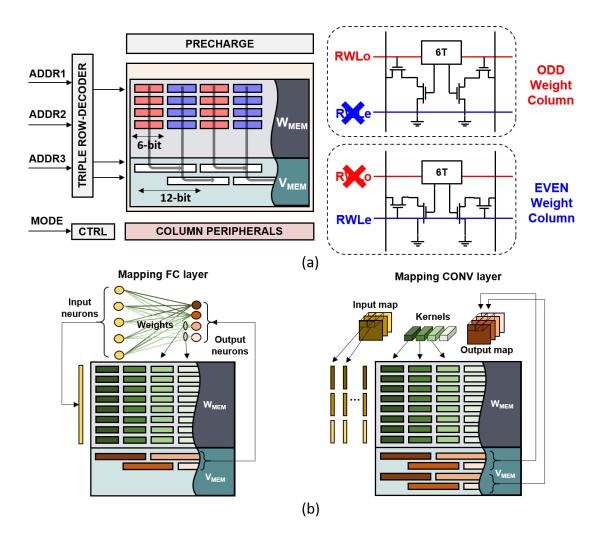

| 7.3  | (a) Organization of the fused $W_{MEM}/V_{MEM}$ 10T-SRAM macro. (b) Mapping of FC and Conv layers on the proposed macro                                                                                                                                                                                                                                                            | 135 |

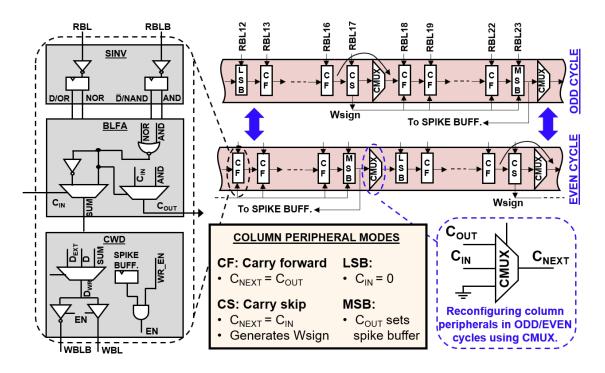

| 7.4  | Detailed description of the reconfigurable column peripherals                                                                                                                                                                                                                                                                                                                      | 136 |

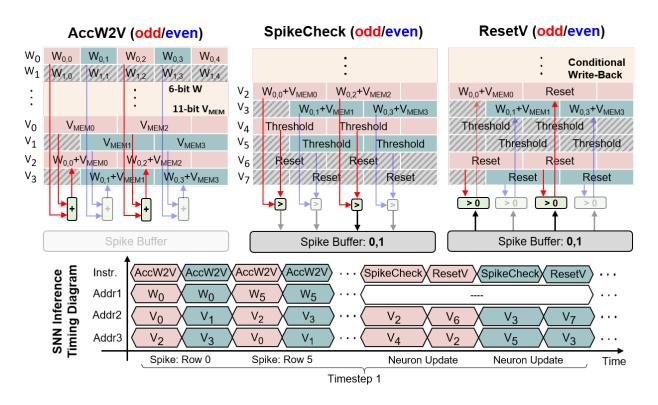

| 7.5  | Illustration of supported in-memory SNN instructions.                                                                                                                                                                                                                                                                                                                              | 137 |

| 7.6  | Multiple neurons can be implemented using in-memory instructions                                                                                                                                                                                                                                                                                                                   | 138 |

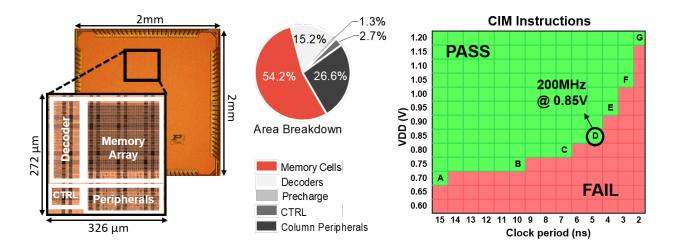

| 7.7  | Die micrograph, area breakdown, and Shmoo plot for CIM operations                                                                                                                                                                                                                                                                                                                  | 139 |

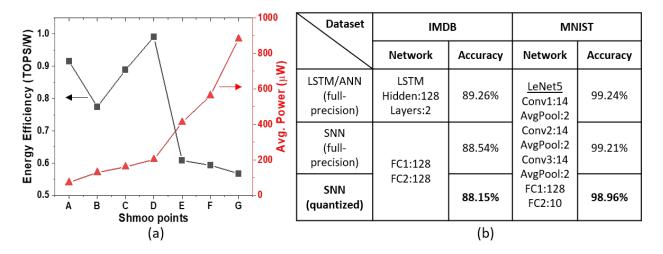

| 7.8  | <ul><li>(a) Measured average power and energy-efficiency for AccW2V instruction.</li><li>(b) SNN architecture and accuracy on IMDB and MNIST datasets</li></ul>                                                                                                                                                                                                                    | 140 |

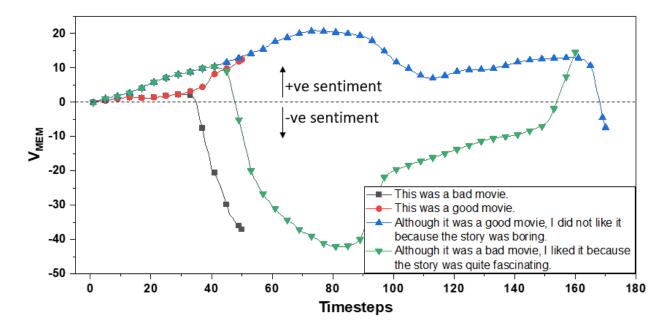

| 7.9  | Progression of the final output neuron's membrane potential with timesteps, where each word is presented to the SNN for 10 timesteps.                                                                                                                                                                                                                                              | 141 |

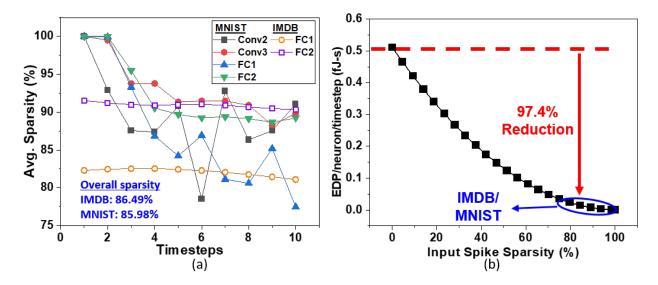

| 7.10 | (a) Average sparsity obtained at each layer of SNN for each timestep. (b)<br>Measured EDP per-neuron per-timestep with varying sparsity                                                                                                                                                                                                                                            | 142 |

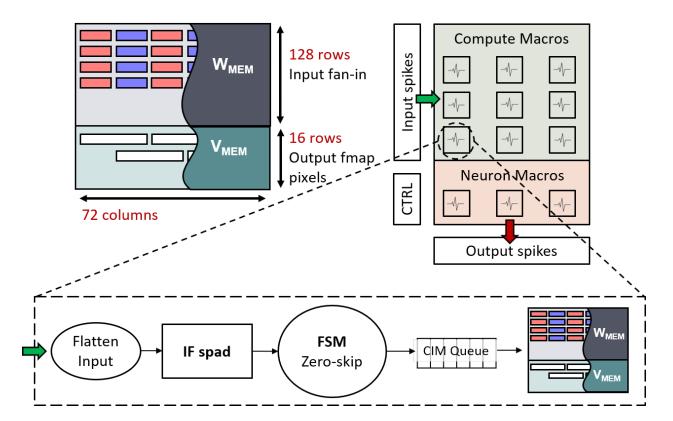

| 7.11 | Limited fan-in of single macro (left). Multi-macro architecture is shown on the right consisting of compute and neuron macros and moving partial $V_{MEM}$ among them to compute the final spikes (right). The block diagram showing each processing element (bottom).                                                                                                                          | 144 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

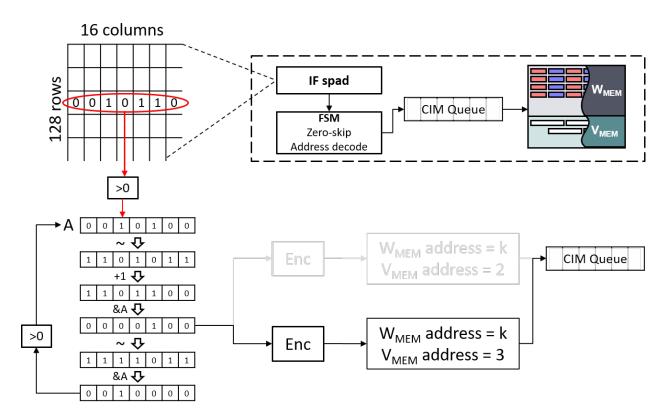

| 7.12 | Zero-skipping using leading-one detector.                                                                                                                                                                                                                                                                                                                                                       | 145 |

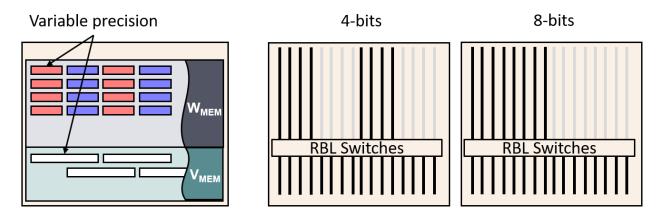

| 7.13 | Macro Pipeline. Pipeline stages Read, Compute and Store corresponding to<br>the column peripheral blocks SINV, BLFA and CWD, respectively (right).<br>Timing diagram of the macro processing is shown on the left.                                                                                                                                                                              | 147 |

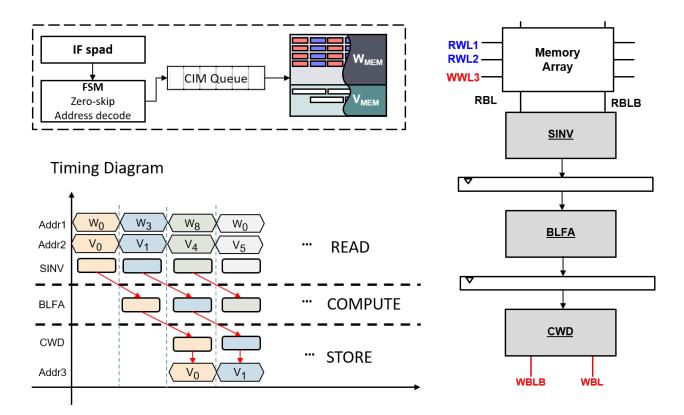

| 7.14 | Amortizing the reconfigurability overhead for processing odd and even columns, by maintaining two queues having appropriate depth. The graph on the right plots the energy per operation as a function of number of consecutive odd/even operations.                                                                                                                                            | 148 |

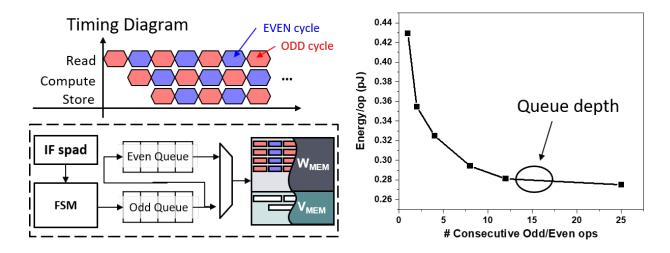

| 7.15 | Variable bit-precisions can be supported by introducing RBL switches to decouple the RBL between the $W_{MEM}$ and $V_{MEM}$ subarrays.                                                                                                                                                                                                                                                         | 148 |

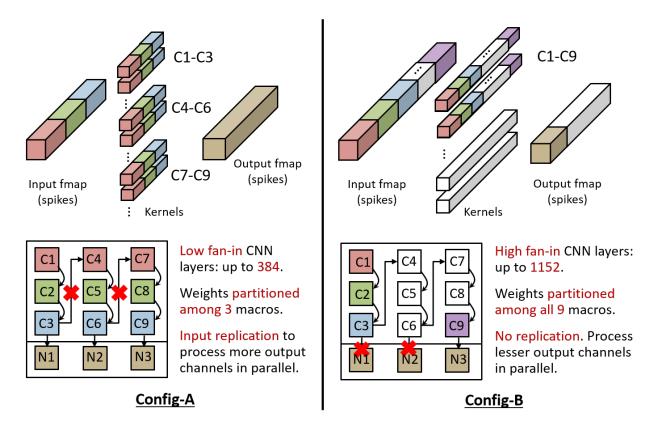

| 7.16 | Two supported configurations to efficiently run low fan-in and high fan-in CNN layers with high throughput.                                                                                                                                                                                                                                                                                     | 149 |

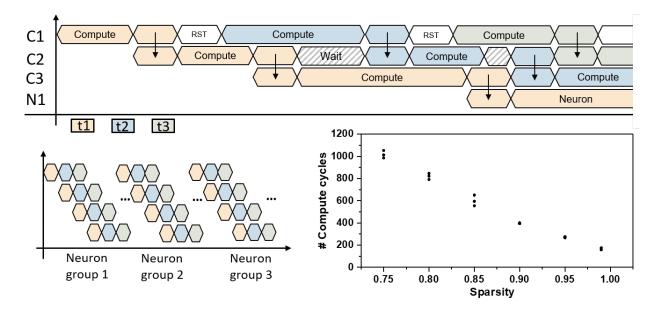

| 7.17 | Timing diagram showing the top-level timestep pipelining among the macros (top). Once all timesteps are performed for one group of neurons, we can start processing the next group and so on, thereby leveraging weight re-use across neurons and across timesteps. The plot (bottom right) shows the dependency of compute cycles on the data-sparsity, showing the benefits of zero-skipping. | 150 |

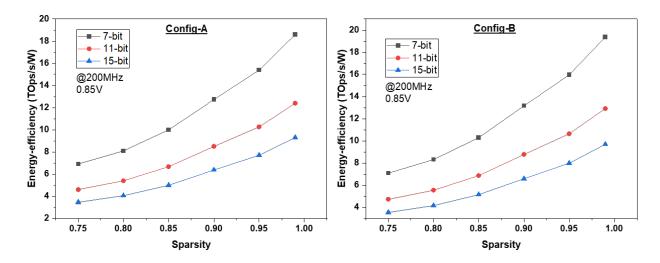

| 7.18 | Energy-efficiency of the proposed multi-macro architecture, as a function of data-sparsity and the bit-precision, for the two proposed configurations                                                                                                                                                                                                                                           | 151 |

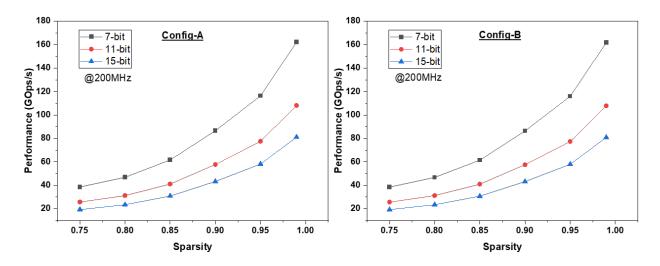

| 7.19 | Throughput of the proposed multi-macro architecture, as a function of data-<br>sparsity and the bit-precision, for the two proposed configurations                                                                                                                                                                                                                                              | 152 |

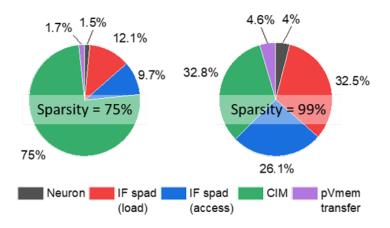

| 7.20 | Energy breakdown for two levels of sparsity (75% and 99%). $\ldots$                                                                                                                                                                                                                                                                                                                             | 152 |

| A.1  | Schematic showing a 6T-SRAM array. The red and blue arrows show the current path and the charge discharge path, respectively, causing read-stability issues for performing in-memory computing.                                                                                                                                                                                                 | 157 |

| A.2  | Staggered activation of wordlines to avoid short circuit paths, leading to bit-<br>line discharge [90]                                                                                                                                                                                                                                                                                          | 158 |

### ABSTRACT

Machine Learning (ML) workloads, being memory and compute-intensive, consume large amounts of power running on conventional computing systems, restricting their implementations to large-scale data centers. Thus, there is a need for building domain-specific hardware primitives for energy-efficient ML processing at the edge. One such approach is in-memory computing, which eliminates frequent and unnecessary data-transfers between the memory and the compute units, by directly computing the data where it is stored. Most of the chip area is consumed by on-chip SRAMs in both conventional von-Neumann systems (e.g. CPU/GPU) as well as application-specific ICs (e.g. TPU). Thus, we propose various circuit techniques to enable a range of computations such as bitwise Boolean and arithmetic computations, binary convolution operations, non-Boolean dot-product operations, lookuptable based computations, and spiking neural network implementation – all within standard SRAM memory arrays.

First, we propose X-SRAM, where, by using skewed sense amplifiers, bitwise Boolean operations such as NAND/NOR/XOR/IMP etc. can be enabled within 6T and 8T SRAM arrays. Moreover, exploiting the decoupled read/write ports in 8T SRAMs, we propose read-compute-store scheme where the computed data can directly be written back in the array simultaneously.

Second, we propose Xcel-RAM, where we show how binary convolutions can be enabled in 10T SRAM arrays for accelerating binary neural networks. We present charge sharing approach for performing XNOR operations followed by a population count (popcount) using both analog and digital techniques, highlighting the accuracy-energy tradeoff.

Third, we take this concept further and propose CASH-RAM, to accelerate non-Boolean operations, such as dot-products within standard 8T-SRAM arrays by utilizing the parasitic capacitances of bitlines and sourcelines. We analyze the non-idealities that arise due to analog computations and propose a self-compensation technique which reduces the effects of non-idealities, thereby reducing the errors.

Fourth, we propose ROM-embedded caches, RECache, using standard 8T SRAMs, useful for lookup-table (LUT) based computations. We show that just by adding an extra word-line (WL) or a source-line (SL), the same bit-cell can store a ROM bit, as well as the usual RAM bit, while maintaining the performance and area-efficiency, thereby doubling the memory density. Further we propose SPARE, an in-memory, distributed processing architecture built on RECache, for accelerating spiking neural networks (SNNs), which often require high-order polynomials and transcendental functions for solving complex neuro-synaptic models.

Finally, we propose IMPULSE, a 10T-SRAM compute-in-memory (CIM) macro, specifically designed for state-of-the-art SNN inference. The inherent dynamics of the neuron membrane potential in SNNs allows processing of sequential learning tasks, avoiding the complexity of recurrent neural networks. The highly-sparse spike-based computations in such spatio-temporal data can be leveraged for energy-efficiency. However, the membrane potential incurs additional memory access bottlenecks in current SNN hardware. IMPULSE triew to tackle the above challenges. It consists of a fused weight ( $W_{MEM}$ ) and membrane potential ( $V_{MEM}$ ) memory and inherently exploits sparsity in input spikes. We propose staggered data mapping and re-configurable peripherals for handling different bit-precision requirements of  $W_{MEM}$  and  $V_{MEM}$ , while supporting multiple neuron functionalities. The proposed macro was fabricated in 65nm CMOS technology. We demonstrate a sentiment classification task from the IMDB dataset of movie reviews and show that the SNN achieves competitive accuracy with only a fraction of trainable parameters and effective operations compared to an LSTM network.

These circuit explorations to embed computations in standard memory structures shows that on-chip SRAMs can do much more than just store data and can be re-purposed as on-demand accelerators for a variety of applications.

### 1. INTRODUCTION

In the past decade, we have seen a tremendous growth in Machine Learning (ML) algorithms, especially Deep Neural Networks (DNNs). DNNs have been shown to be extremely effective for various cognitive applications, such as classification, recognition, detection and autonomous systems, which are being adopted into various disciplines [1], [2]. The primary reason for their exponential growth and widespread adoption in the past decade can be attributed to the advancements in computational power and resources [3]. Availability of powerful large-scale CPU and GPU servers and clusters enabled execution of computationally expensive DNN models, leading to superior performance [3]. Even today, the size of the state-of-the-art DNNs grows exponentially [4]. Although large-scale data-centers having multiple CPU clusters and GPUs, enable large parallelism and faster execution of DNNs, they are extremely power hungry. This is because DNN compute models are inherently different from general-purpose workloads and are immensely memory- and compute-intensive. Running data-intensive applications on such von-Neumann machines, like artificial intelligence, search engines, neural networks, biological systems, financial analysis etc., are limited by the von Neumann bottleneck [5]. This bottleneck results due to frequent and large amounts of data transfer between the physically separate memory units and compute cores. Moreover, frequent to-and-fro data transfers incur large energy overheads in addition to limiting the overall throughput. This has largely restricted the execution of DNNs to large-scale data-centers, due to such high power demands.

Nowadays, most real-time data is generated at the edge-devices, such as sensor nodes, drones, and IoT devices. Most of these devices are battery-operated, and thus have limited battery life. Transferring large amounts of data from the edge devices to the cloud is not only energy expensive, but sometimes undesirable due to security reasons, such as in defense or automotive applications. Thus, there is a need for processing data at the edge, to enable energy-efficient DNN inference. There have been innovations in both algorithmic as well as hardware fronts, to mitigate the energy problem of exploding DNNs. Recently, there have been emergence of *memory-friendly* quantized networks, such as binary networks [6], XNOR-Net [7], and ternary networks [8], [9]. The basic idea is to reduce the bit-precision of

the network parameters (weights, or activations, or both), from full-precision (32-bit or 64bit floating point) to low-precision fixed-point notation (1-bit, 2-bit, etc.). This drastically reduces the computational complexity of the network, while also reducing the amount of data movement, without significant loss in state-of-the-art accuracies owing to the error-resiliency of neural networks, and their ability to re-train.

On the hardware side of things, there have been significant interest in beyond von-Neumann computing, especially the paradigm of in-memory computing [10], which aims to embed logic within the memory array in order to reduce memory-processor data transfers. In-memory techniques tend to bypass the von-Neumann bottleneck by accomplishing computations right inside the memory array. In other words, in-memory-compute blocks store data exactly like a standard memory, however, they enable additional operations without expensive area or energy overheads. By enabling logic computations in-memory, significant improvements, both in energy efficiency and throughput are expected [11]–[14].This approach embeds some basic computations within the memory arrays, where the data is stored. By using such enhanced memory structures, frequent and unnecessary data-transfers between the memory and the compute units can be eliminated, without significantly changing the memory hierarchy and the conventional read/write functionality of memory arrays. Moreover, this opens up the internal bandwidth of memory arrays, which is much larger than the external input/output bandwidth, and can be exploited to enable parallelism.

Due to the potential impact of in-memory computing on future computing platforms, various proposals spanning right from conventional complementary metal-oxide semiconductor (CMOS) to beyond-CMOS technologies can be found in the literature. For example, Ref. [15] proposed integrating an ALU (arithmetic-logic-unit) close to the memory unit to exploit the wide memory bandwidth, while Ref. [11] reconfigures a standard 6 transistor (6T) static random-access memory (SRAM) cells as content addressable memories (CAMs) and enable bit-wise logical operations. 6T-SRAM cells have also been used to implement machine learning classifiers [16], and dot-products in analog domain for pattern recognition [13]. The underlying idea is to enable multiple rows of memory bit-cells and directly read out a voltage at the pre-charged bit-lines corresponding to the desired operation. However, the 6T-SRAM bit-cells have a coupled read-write path that imposes conflicting constraints

**Figure 1.1.** (a) Intel Xeon CPU [18]. (b) NVIDIA Turing GPU [19]. (c) Google TPU [20]. (d) Eyeriss chip [21].