## TOWARD ENERGY-EFFICIENT MACHINE LEARNING: ALGORITHMS AND ANALOG COMPUTE-IN-MEMORY HARDWARE

by

Indranil Chakraborty

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana August 2021

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

### Dr. Kaushik Roy, Chair

School of Electrical and Computer Engineering

#### Dr. Anand Raghunathan

School of Electrical and Computer Engineering

### Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

### Dr. Shreyas Sen

School of Electrical and Computer Engineering

### Approved by:

Dr. Dimitrios Peroulis

Dedicated to my mother, my late father, my sister, my brother-in-law, my niece and Deboleena

### ACKNOWLEDGMENTS

I would like to express my gratitude towards my advisor Prof. Kaushik Roy for helping me shape my understanding of research and guiding me through my journey at the Nanoelectronics Research Laboratory (NRL) thus far. Kaushik has been inspirational in my development as a researcher, always keeping me in touch with the higher level aspects of my research. A remarkable quality in Kaushik is his dedication and commitment towards his students, which I have truly reaped benefits of, during my course here by engaging in regular discussions, not only about the technical aspects of research but also its philosophical values. Overall, I will forever be indebted to Kaushik for his immense support and constructive criticism which has brought me where I am today.

I would also like to thank my doctoral thesis committee members: Prof. Anand Raghunathan, Prof. Vijay Raghunathan and Prof. Shreyas Sen. I would like to take this opportunity to individually express my gratitude towards my committee members. Aside from the countless meaningful interactions I have had with Prof. Anand, I have had the opportunity to collaborate with Prof. Anand on two review papers where I have learnt immensely about framing my research to the community. Prof. Vijay has been very welcoming for any discussion on relatable topic. Prof. Shreyas has also taught me a lot about analyzing any situation better. Finally, I would like to thank my Master's advisor, Prof. Udayan Ganguly at Indian Institute of Technology, Bombay without whom I probably wouldn't have never been introduced to research or thought about doing a PhD.

I would also like to thank the NRL members for creating an environment conducive for research as well as fun activities. I have had the opportunity to know some of the best minds who would surely make a difference in our future. I reserve a special gratitude for my friend, now Prof. Abhronil Sengupta at Penn State University, for support since the day I started here. I would like to also thank Dr. Akhilesh Jaiswal for helping me start my research here. I have been grateful to have friends in NRL such as Mustafa, Nitin, Aayush, Amogh during my PhD. Finally, a big thanks to all my collaborators and fellow lab-mates at NRL for their immense support.

Last, but not the least, I would like to dedicate my doctoral journey to a few really special people in my life: My better half, Deboleena, who has been there through all the ups and downs in my life in the last three and a half years and helped me cope with the pressure and stress, my mother who has always been supportive of my decision to do a PhD despite her having to cope alone in the house, my late father who still inspires me to be a better person, my sister for her constant encouragement, my brother-in-law and my niece for making my life a happier place.

## TABLE OF CONTENTS

| LI | ST O | F TAB  | LES                                                                                                    | 14 |

|----|------|--------|--------------------------------------------------------------------------------------------------------|----|

| LI | ST O | F FIGU | JRES                                                                                                   | 15 |

| A  | BSTR | ACT    |                                                                                                        | 25 |

| 1  | INT  | RODU   | CTION                                                                                                  | 28 |

| 2  |      |        | CTING ENERGY-EFFICIENT MIXED-PRECISION NEURAL NET-<br>HROUGH PRINCIPAL COMPONENT ANALYSIS FOR EDGE IN- |    |

|    | TEL  | LIGEN  | ICE                                                                                                    | 32 |

|    | 2.1  | Introd | luction                                                                                                | 32 |

|    | 2.2  | Relate | ed Work                                                                                                | 34 |

|    | 2.3  | PCA-   | driven Hybrid-Net Design                                                                               | 37 |

|    |      | 2.3.1  | PCA-driven identification of significant layers                                                        | 38 |

|    |      | 2.3.2  | Hybrid-Net Design                                                                                      | 40 |

|    | 2.4  | Exper  | iments, Results and Discussion                                                                         | 42 |

|    |      | 2.4.1  | Experiments                                                                                            | 42 |

|    |      |        | Energy efficiency and Memory compression                                                               | 43 |

|    |      | 2.4.2  | Results - PCA                                                                                          | 45 |

|    |      |        | ResNet Architectures - CIFAR-100                                                                       | 45 |

|    |      |        | VGG Architectures - CIFAR-100                                                                          | 46 |

|    |      |        | ResNet Architectures - ImageNet                                                                        | 47 |

|   |     | 2.4.3  | Image Classification Results - CIFAR-100            | 48 |

|---|-----|--------|-----------------------------------------------------|----|

|   |     |        | ResNet Architectures                                | 48 |

|   |     |        | VGG architecture                                    | 50 |

|   |     | 2.4.4  | Image Classification Results - ImageNet             | 51 |

|   |     | 2.4.5  | Statistical Analysis                                | 52 |

|   |     |        | Fixed Optimal Solutions:                            | 52 |

|   |     |        | Varying Optimal Solutions:                          | 53 |

|   |     | 2.4.6  | Optimality Studies                                  | 54 |

|   |     | 2.4.7  | Discussion                                          | 55 |

|   | 2.5 | Conclu | nsion                                               | 58 |

| 3 | RES | ISTIVE | C CROSSBARS AS BUILDING BLOCKS FOR MACHINE LEARNING | 60 |

|   | 3.1 | Introd | uction                                              | 60 |

|   | 3.2 | The A  | natomy of Resistive Crossbars                       | 63 |

|   |     | 3.2.1  | Device Technologies                                 | 64 |

|   |     |        | Two Terminal Devices                                | 65 |

|   |     |        | Three Terminal Devices                              | 67 |

|   |     | 3.2.2  | Circuits: Peripherals and Access                    | 68 |

|   |     |        | Selectors/Access transistors                        | 68 |

|   |     |        | Input Encoding                                      | 70 |

|   |     |        |                                                     |    |

|   |     | 3.2.3  | Crossbar Write Operations                          | 72 |

|---|-----|--------|----------------------------------------------------|----|

|   |     | 3.2.4  | Silicon Demonstrations                             | 74 |

|   |     |        | NVM MVM macros:                                    | 74 |

|   |     |        | CMOS MVM macros:                                   | 75 |

| 4 | TEC | HNOL   | OGY AWARE TRAINING IN MEMRISTIVE NEUROMORPHIC SYS- |    |

|   |     |        | R NONIDEAL SYNAPTIC CROSSBARS                      | 77 |

|   | 4.1 | Crossb | oar Implementation of Neural Networks              | 79 |

|   |     | 4.1.1  | Types of network topologies                        | 79 |

|   |     |        | Fully Connected Networks                           | 79 |

|   |     |        | Convolutional Networks                             | 79 |

|   |     | 4.1.2  | Hardware representations of Neural networks        | 80 |

|   |     | 4.1.3  | Training                                           | 82 |

|   |     | 4.1.4  | Technologies                                       | 83 |

|   | 4.2 | Model  | ing the non-idealities                             | 84 |

|   |     | 4.2.1  | Neuron Resistance                                  | 85 |

|   |     | 4.2.2  | Source Resistance                                  | 86 |

|   |     | 4.2.3  | Memristive Conductance Variations                  | 87 |

|   |     | 4.2.4  | Proposed Training Algorithm                        | 87 |

|   | 4.3 | Simula | ation Framework                                    | 90 |

|   |     | 4.3.1  | Model simulations                                  | 90 |

|   |      | FCN                                                   |

|---|------|-------------------------------------------------------|

|   |      | CNN                                                   |

|   |      | 4.3.2 SPICE-like Simulations for validation           |

|   | 4.4  | Results and Discussion                                |

|   |      | Source and Neuron Resistance                          |

|   |      | Weight variations                                     |

|   |      | Crossbar Size                                         |

|   | 4.5  | Conclusion                                            |

| 5 | GEN  | NEX: A GENERALIZED APPROACH TO EMULATING NON-IDEALITY |

|   | IN M | AEMRISTIVE XBARS USING NEURAL NETWORKS                |

|   | 5.1  | Introduction                                          |

|   | 5.2  | Related Work                                          |

|   | 5.3  | Analysis of NVM Non-Idealities                        |

|   | 5.4  | GENIEx - A Neural Network Based Crossbar Model 10     |

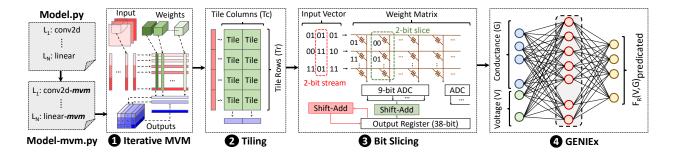

|   | 5.5  | Functional Simulator                                  |

|   | 5.6  | Experimental Methodology 110                          |

|   | 5.7  | Results                                               |

|   |      | 5.7.1 Impact on Design Parameters                     |

|   |      | 5.7.2 Impact of Quantization                          |

|   |      | 5.7.3 Impact of Bit Slicing                           |

|   | 5.8         | Conclusion                                                                | 115 |

|---|-------------|---------------------------------------------------------------------------|-----|

| 6 | 8T S        | SRAM CELL AS A MULTIBIT DOT-PRODUCT ENGINE FOR BEYOND                     |     |

|   | VON         | N NEUMANN COMPUTING 1                                                     | 116 |

|   | 6.1         | Introduction                                                              | 116 |

|   | 6.2         | 8T-SRAM as a Dot Product Engine                                           | 118 |

|   | 6.3         | Results                                                                   | 122 |

|   | 6.4         | Variation Analysis                                                        | 129 |

|   |             | 6.4.1 Corner Analysis                                                     | 129 |

|   |             | 6.4.2 Effect of Line-Resistances                                          | 130 |

|   |             | 6.4.3 $V_T$ Variations                                                    | 134 |

|   | 6.5         | Discussions                                                               | 136 |

|   | 6.6         | Conclusion                                                                | 139 |

| 7 |             | RSITY AWARE COMPUTE-IN-MEMORY PROCESSOR BASED ON 8T                       |     |

|   | SRA<br>(Wor | rk done in collaboration with Mustafa Ali)                                | 140 |

|   | 7.1         | Introduction                                                              | 140 |

|   | 7.2         | 8T SRAM based Compute-in-Memory Cell - A Brief Recap                      | 141 |

|   | 7.3         | Analysis of Sparsity in ML Workloads                                      | 141 |

|   | 7.4         | Sparsity-Aware Compute-in-memory Macro with Reconfigurable Precision ADC1 | 144 |

|   |             | 7.4.1 Macro Structure                                                     | 144 |

|   |             | 7.4.2 Reconfigurable-Precision SAR ADC                                    | 146 |

|   |     | 7.4.3   | Measurement Results                                                                     | 148                |

|---|-----|---------|-----------------------------------------------------------------------------------------|--------------------|

|   |     | 7.4.4   | Conclusion                                                                              | 151                |

|   | 7.5 | Sparsit | ty-Aware Compute-in-memory Processing Core                                              | 151                |

|   |     | 7.5.1   | Related Work                                                                            | 152                |

|   |     | 7.5.2   | CIM Core Features                                                                       | 152                |

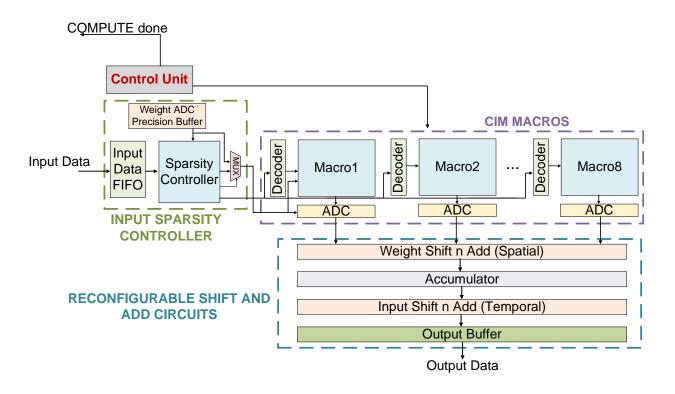

|   |     | 7.5.3   | Sparsity Aware CIM Compute Unit (SCU) Microarchitecture                                 | 154                |

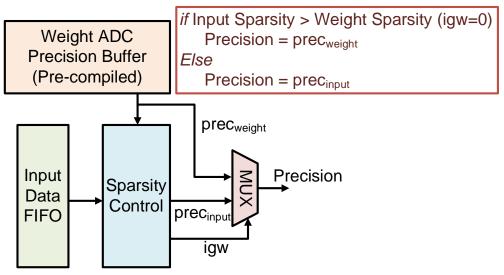

|   |     |         | Sparsity Controller (SC)                                                                | 156                |

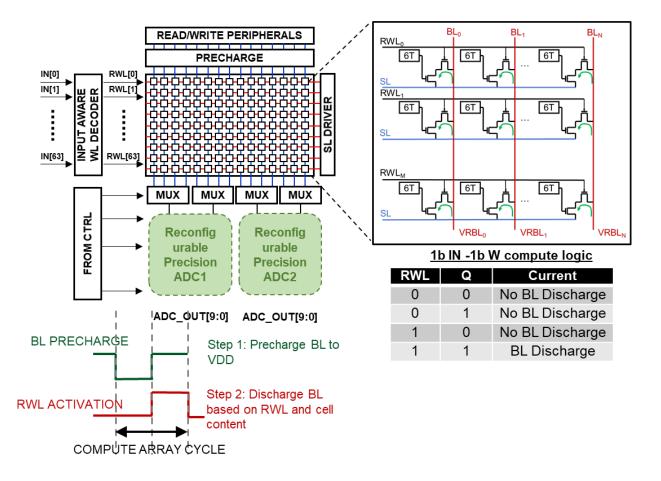

|   |     |         | CIM Macro                                                                               | 157                |

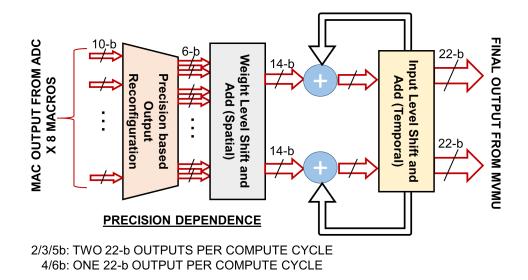

|   |     |         | Reconfigurable Shift-and-Add Circuits (RSnA)                                            | 158                |

|   |     | 7.5.4   | Core Microarchitecture                                                                  | 160                |

|   |     | 7.5.5   | Mapping and Dataflow                                                                    | 160                |

|   |     | 7.5.6   | Tentative Floorplan                                                                     | 162                |

|   |     | 7.5.7   | Preliminary Results                                                                     | 164                |

| 8 | NEU | ROMO    | RPHIC COMPUTING USING GST-BASED PHOTONIC PLATFORM                                       | <mark>S</mark> 167 |

|   | 8.1 | Introd  | uction                                                                                  | 167                |

|   | 8.2 | GST o   | n Micro-ring Resonators                                                                 | 169                |

|   | 8.3 |         | d Fast Neural Computing using All-Photonic Phase Change Spiking                         | 172                |

|   | 8.4 |         | nic In-Memory Computing Primitive for Spiking Neural Networks Using<br>Change Materials | 184                |

|   |     | 8.4.1   | Photonic Dot Product Engine                                                             | 188                |

|   |     |         |                                                                                         |                    |

|   |     |        | Network Design                                   | 188 |

|---|-----|--------|--------------------------------------------------|-----|

|   |     |        | Synapse Design constraints                       | 189 |

|   |     | 8.4.2  | Operation of All-Photonic Spiking Neural Network | 191 |

|   |     | 8.4.3  | Results 1                                        | 195 |

|   |     |        | Device Simulations                               | 195 |

|   |     |        | Device to System Framework 1                     | 195 |

|   |     | 8.4.4  | Device Simulations                               | 195 |

|   |     |        | Interference Errors                              | 198 |

|   |     |        | System Level SNN performance                     | 198 |

|   |     | 8.4.5  | Discussion                                       | 203 |

|   |     | 8.4.6  | Conclusion                                       | 207 |

| 9 | SUM | IMARY  | AND FUTURE WORK                                  | 209 |

|   | 9.1 | Summ   | ary                                              | 209 |

|   | 9.2 | Future | e Work                                           | 210 |

| А | ENE | RGY E  | EFFICIENCY AND MEMORY CALCULATIONS FOR DNNS 2    | 212 |

|   | A.1 | Energ  | y Efficiency                                     | 212 |

|   | A.2 | Memo   | ory Compression                                  | 214 |

| В | CRC | SSBAR  | R NON-IDEALITIES                                 | 215 |

|   | B.1 | Read r | non-idealities                                   | 215 |

|   |     | B.1.1  | Linear read non-idealities                       | 215 |

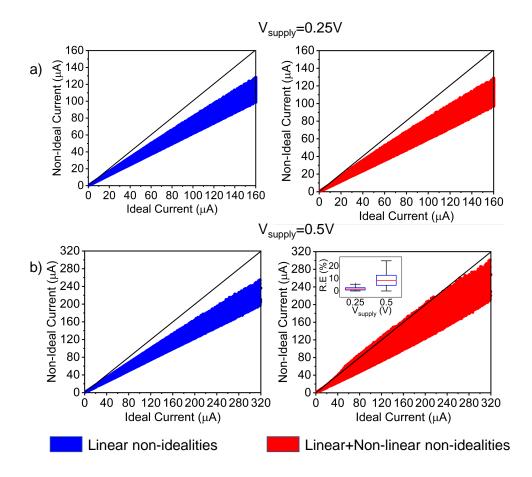

|       | B.1.2  | Non-linear read non-idealities            |

|-------|--------|-------------------------------------------|

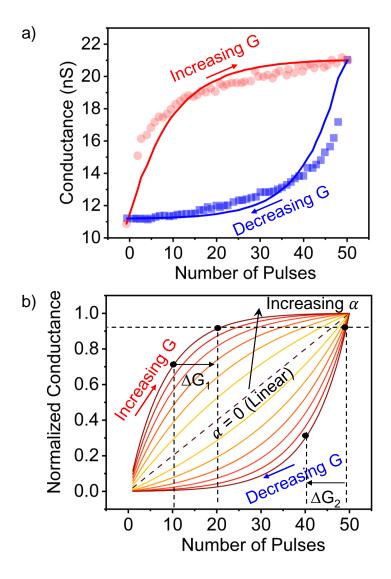

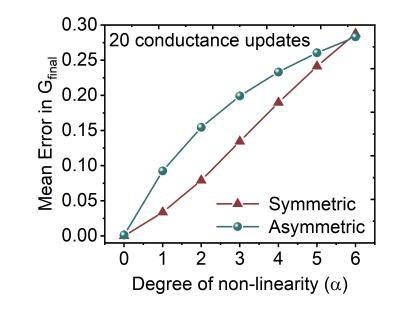

| B.2   | Write  | non-idealities                            |

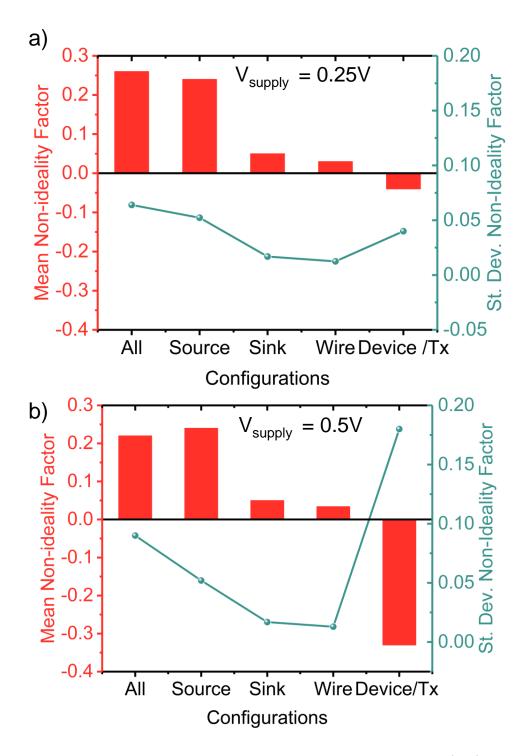

| B.3   | Impac  | t of non-idealities on the output current |

|       | B.3.1  | Read non-idealities                       |

|       | B.3.2  | Write Non-idealities                      |

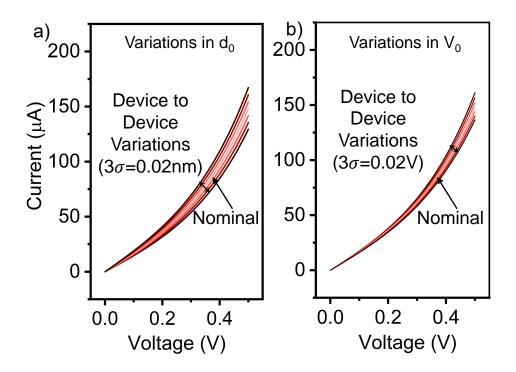

|       | B.3.3  | Process Variations                        |

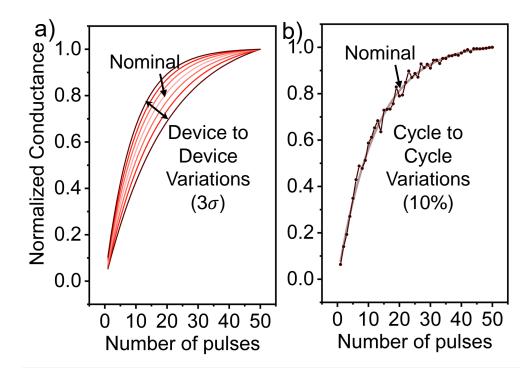

|       | B.3.4  | Device to Device Write Variations         |

|       | B.3.5  | Cycle to Cycle Write Variations           |

|       | B.3.6  | Device to Device Read Variations          |

| REFER | ENCES  | 8                                         |

| VITA  |        |                                           |

| PUBLI | CATION | NS                                        |

## LIST OF TABLES

| 2.1 | Networks architectures for ImageNet classification task $\ldots \ldots \ldots \ldots \ldots$                                                                                      | 44  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Significant Layers identified by PCA analysis                                                                                                                                     | 47  |

| 2.3 | Comparison of different networks on CIFAR-100                                                                                                                                     | 49  |

| 2.4 | Comparison of different networks on CIFAR-100 for VGG-15                                                                                                                          | 50  |

| 2.5 | Comparison of different networks on ImageNet                                                                                                                                      | 51  |

| 2.6 | Analysis of effect of random initialization on varying optimal Hybrid-Net archi-<br>tecture (ResNet-20 on CIFAR-100)                                                              | 53  |

| 2.7 | Network Configurations with randomly chosen layers as $k_b$ -bit precision                                                                                                        | 54  |

| 2.8 | Analysis of quantization of first and last layers in Hybrid-Net (2,2) (Delta=4) on ResNet-32 for CIFAR-100                                                                        | 57  |

| 3.1 | Silicon Demonstrations                                                                                                                                                            | 73  |

| 4.1 | Resistance Ranges for Various technologies                                                                                                                                        | 84  |

| 4.2 | CNN Architecture                                                                                                                                                                  | 90  |

| 5.1 | Related work comparison                                                                                                                                                           | 102 |

| 5.2 | Non-idealities in crossbar                                                                                                                                                        | 103 |

| 5.3 | Functional simulator parameters                                                                                                                                                   | 109 |

| 6.1 | Comparison of 8T DPE inference accuracy on MNIST                                                                                                                                  | 136 |

| 7.1 | Comparison with state of the art                                                                                                                                                  | 149 |

| 8.1 | Dimensions and Material parameters                                                                                                                                                | 175 |

| 8.2 | Simulation Parameters                                                                                                                                                             | 194 |

| A.1 | Number of operations in a $k_b$ -bit layer $\ldots \ldots \ldots$ | 213 |

| B.1 | Crossbar Simulation Parameters                                                                                                                                                    | 221 |

### LIST OF FIGURES

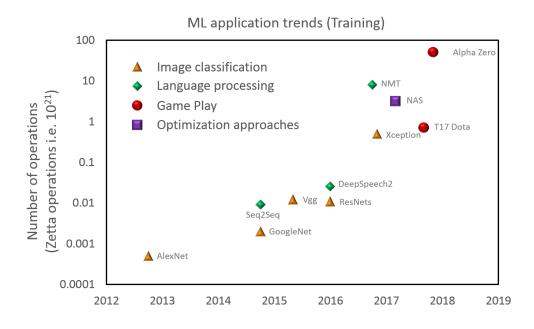

| 1.1 | Trends of ML applications in terms of computational complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

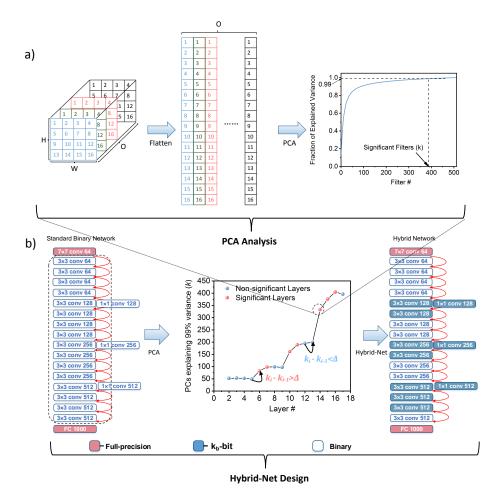

| 2.1 | (a) The PCA function in Algorithm. 1 for a particular layer showing flattening<br>of an instance of a 4-D tensor and subsequent PCA analysis yielding the<br>plot showing how the cumulative explained variance accrues with the number<br>of filters in a particular layer. Number of Significant filters, $k$ is defined<br>as the number of filters at which the cumulative sum reaches a threshold<br>(say 0.99). (b) The Main() function in Algorithm. 1 is explained as we<br>take a standard binary network (leftmost, with first and final layers having<br>full-precision weights and activations) and perform the aforementioned PCA<br>function on each binary layer (shown in white). The resulting plot (middle)<br>shows the layer-wise variation in $k$ in a ResNet-18 on ImageNet for example.<br>A layer is considered significant (shown by red markers), when $k$ increases by<br>at least $\Delta$ . The new Hybrid-Net (rightmost) is designed by increasing the<br>precision of weights and activations for the significant layers (shown in blue). | 36 |

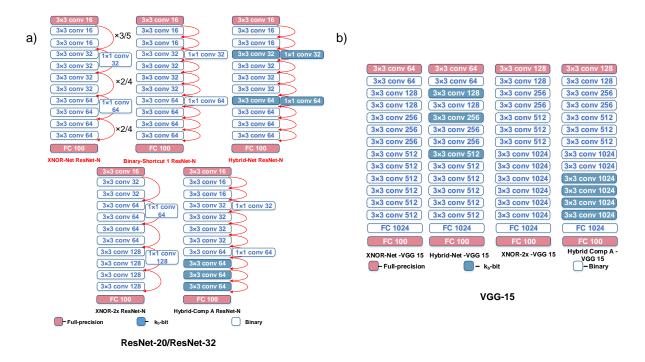

| 2.2 | Different network configurations based on a) ResNet-20/ResNet-32 and b) VGG-15 architectures showing binary, $k_b$ -bit and full-precision layers in each of the networks as described in Section 4.2. The width of the layer shown in this figure is for CIFAR-100 dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42 |

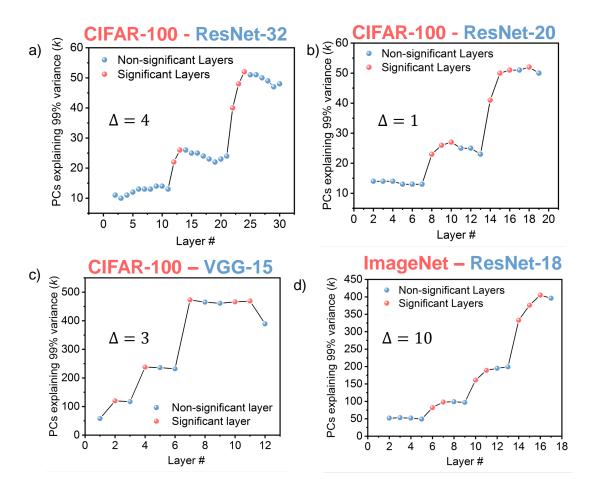

| 2.3 | PCA analysis plot showing the number of principal components required to explain 99% variance at the output of convolutional layers across different layers for a) ResNet-32 ( $\Delta = 4$ ), b) ResNet-20 ( $\Delta = 1$ ), and c) VGG-15 ( $\Delta = 3$ ) on CIFAR-100 dataset and d) for ResNet-18 ( $\Delta = 30$ ) on ImageNet dataset .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 46 |

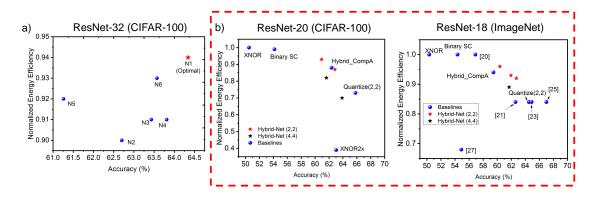

| 2.4 | Illustration of energy-accuracy optimality of Hybrid-Net. a) Accuracy v/s Energy efficiency plot showing that PCA-driven Hybrid network design achieves more optimal tradeoffs than randomly chosen layers b) Normalized Energy Efficiency v/s Accuracy plot showing optimality boundaries for the considered network configurations. It shows that Hybrid-Net (2,2) networks lie right on the optimal boundary among the networks considered. Note, that PACT involves a more advanced quantization algorithm than other networks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

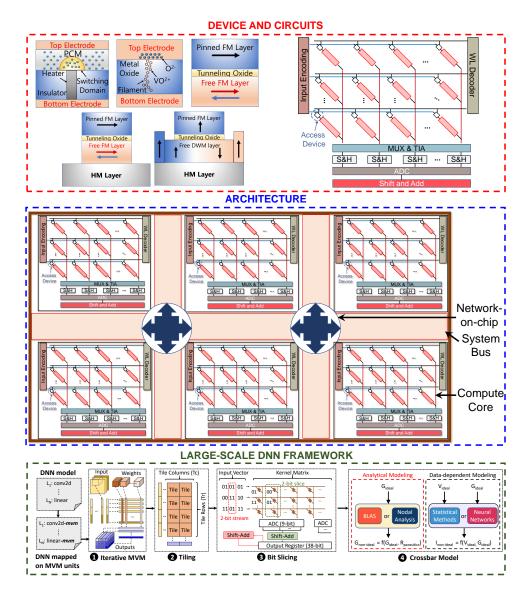

| 3.1 | Layers of abstractions of resistive crossbar systems for DNN accelerators.<br>First, the basic building blocks of such systems are the NVM devices based<br>on technologies such as PCM, RRAM and Spintronics. Crossbar array with<br>NVM devices, is augmented with peripheral circuits to enable MVM computa-<br>tions. Such crossbars can be used to design large-scale hardware accelerators.<br>Finally, software frameworks allow workloads to be mapped to such hardware<br>fabrics and evaluated considering the impact of non-idealities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61 |

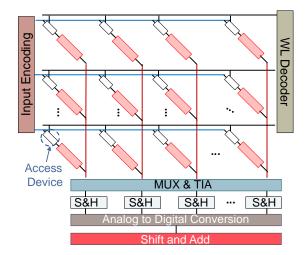

| 3.2 | resistive crossbar and its peripherals for large-scale integration. Input Encod-<br>ing circuits apply analog voltages to the rows and Word-line (WL) decode ac-<br>tivates the access devices. At the output of the crossbar, muxing network and<br>transimpedance amplifiers (TIA) converts analog current to voltage, which is<br>then passed through Sample & Hold (S&H) circuits. The Analog to Digital<br>Converter (ADC) is shared across the columns. The ADC outputs go through<br>shift and add circuits to account for bit-slicing and bit-streaming | 63 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

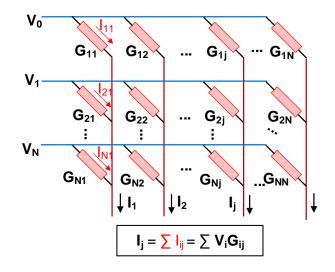

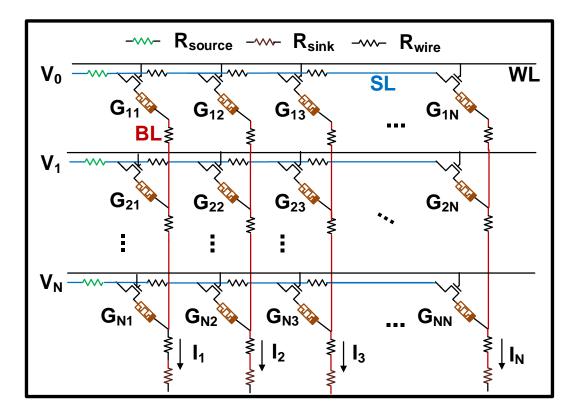

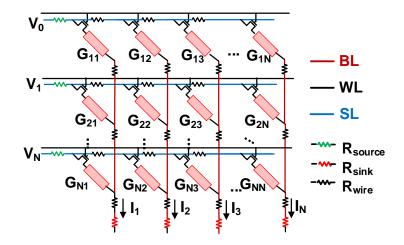

| 3.3 | Crossbar arrangement of NVM devices to enable matrix-vector multiplication operations. A voltage vector, $V_0, V_1,, V_N$ is applied to each row of the resistive crossbar where the conductance of the devices, $G_{11},, G_{NN}$ , form the 2-D matrix. The current output vector $I_1, I_2,, I_N$ in the column represents the MVM result.                                                                                                                                                                                                                   | 64 |

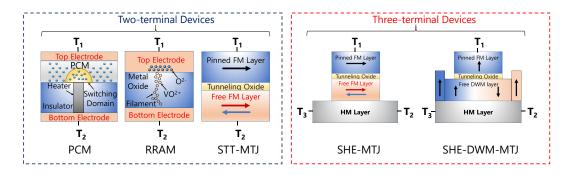

| 3.4 | Different NVM device technologies can be broadly categorized into two types:<br>Two terminal Devices and Three terminal Devices. Two terminal devices<br>include Phase Change Material (PCM), metal oxide Resistive Random access<br>memory (RRAM) and Spin Transfer Torque Magnetic Tunnel Junction (STT-<br>MTJ). Three terminal devices include Spin Hall Effect MTJ (SHE-MTJ) and<br>SHE domain wall magnet MTJ (SHE-DWM-MTJ).                                                                                                                              | 66 |

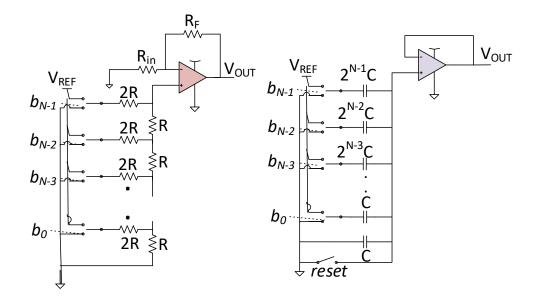

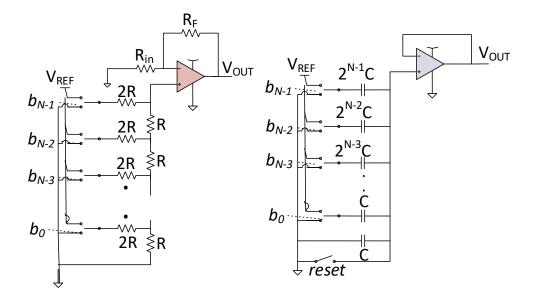

| 3.5 | (a) R-2R ladder based DAC. (b) Capacitance-based DAC [102]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 69 |

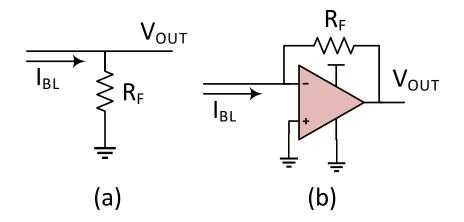

| 3.6 | (a) The resistor-based current-to-voltage converter. (b) The op-amp based TIA [106]                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71 |

| 3.7 | (a) Flash ADC architecture. (b) SAR ADC architecture [107], [108]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 72 |

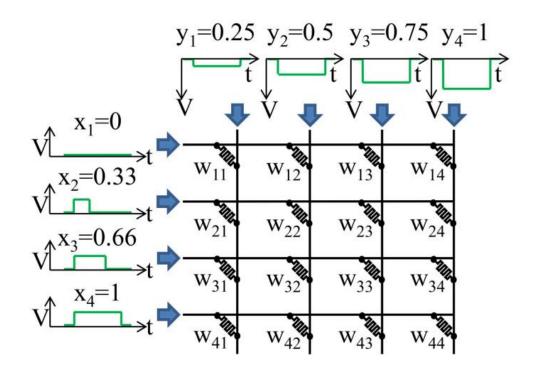

| 3.8 | Row inputs, $x_i$ , are encoded by the pulse-width and the column inputs, $y_j$ , encoded as pulse amplitude. Simultaneous application of pulses at the rows and column produces a multiplicative effect such that a higher voltage at the column and longer pulse at the row results in a bigger change in conductance of the NVM devices at the crosspoint [116]                                                                                                                                                                                              | 74 |

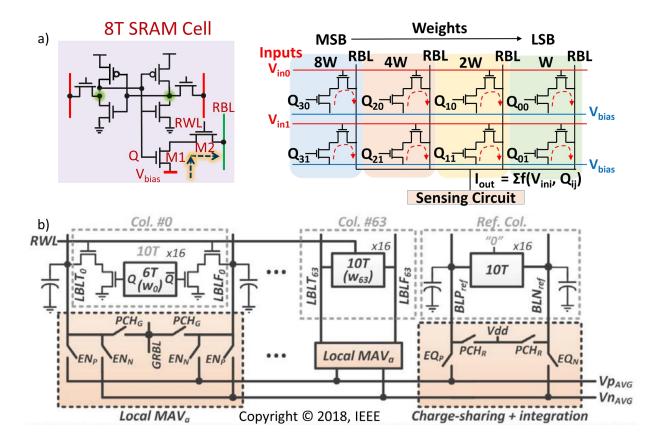

| 3.9 | (a) MVM macro using current based computations in 8T SRAM cells. The weight bit is represented by node 'Q'. By applying a voltage on RWL, the current in the RBL is a function of the weight bit and the applied voltage. The transistors are sized appropriately to represent multi-bit weights. (b) MVM macro using voltage based computation in 10T SRAM cells. The local bit-lines (LBLT and LBLF) are discharged according to the weight bit stored in the 6T SRAM. Through charge sharing, average MVM output is calculated in the horizontal lines [11]. | 75 |

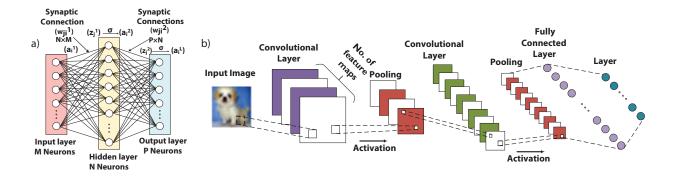

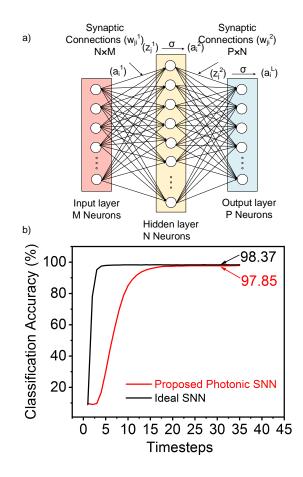

| 4.1 | (a) Fully connected 3-layered neural network showing the input layer, hidden layer, and an output layer. Each neuron in a particular layer is fed by weighted sum of all inputs of the previous layer and it performs a sigmoid operation on the sum to provide the inputs for the next layer. (b) CNN Architecture with different convolutional and pooling layers terminated by a fully connected layer.                                                                                                                                                      | 78 |

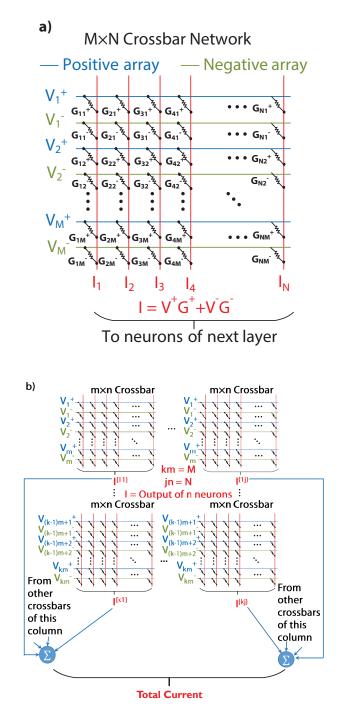

| 4.2 | (a) Hardware implementation of a single fully connected network layer represented by two resistive crossbar arrays. The output of the crossbar will be fed to another crossbar representing the next layer. (b) An arrangement of multiple sub-crossbars to realize the functionality of a large crossbar                                        | 81  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

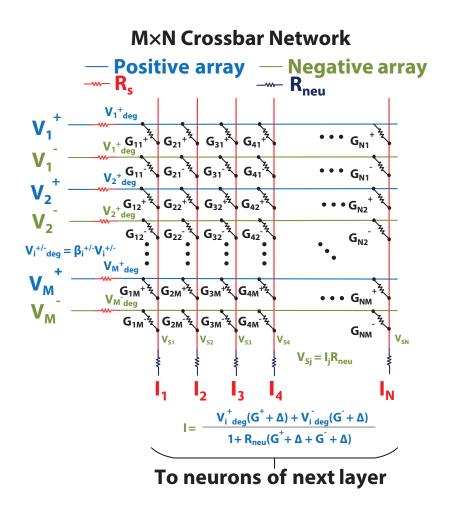

| 4.3 | Crossbar Architecture showing non-ideal elements like source and neuron re-<br>sistances. The final output current equation is modified by the impact of<br>these non-ideal elements.                                                                                                                                                            | 85  |

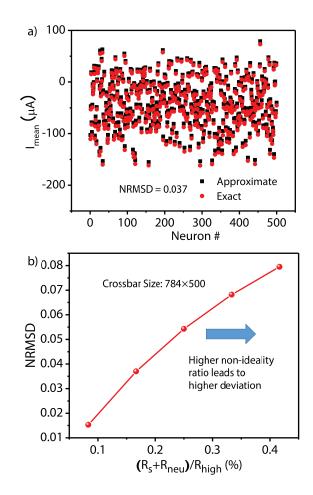

| 4.4 | (a) Distribution of output currents $(I_{mean})$ , averaged over 100 images, across 500 neurons in the hidden layer comparing the approximate model to SPICE-like simulation framework. (b) Variation of Normalized Root Mean Square Deviation (NRMSD) with non-ideality ratio. NRMSD is close to zero for the relevant range of non-idealities. | 91  |

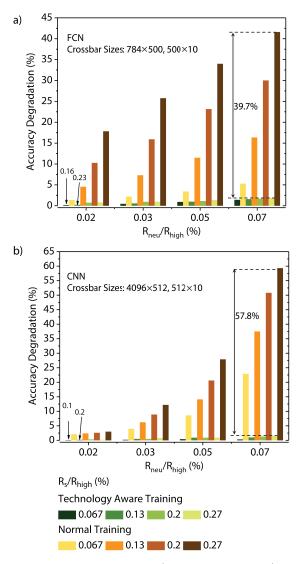

| 4.5 | Accuracy degradation v/s varying $R_{neu}/R_{high}$ ratio for different $R_s/R_{high}$ combinations comparing technology aware training scheme with normal training for (a) FCN and (b) CNN.                                                                                                                                                     | 93  |

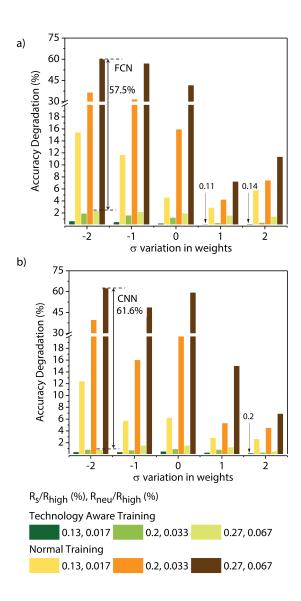

| 4.6 | Accuracy degradation v/s $\sigma$ variations in weights for various $R_s/R_{high}$ and $R_{neu}/R_{high}$ combinations comparing the technology aware training scheme with normal training for (a) FCN and (b) CNN.                                                                                                                              | 95  |

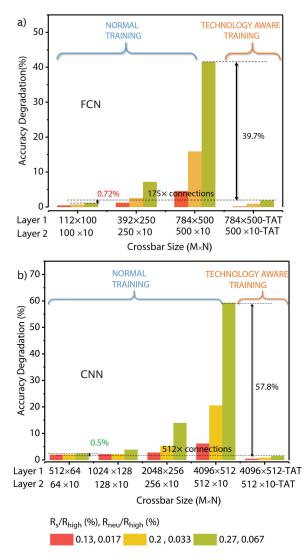

| 4.7 | Accuracy degradation v/s crossbar size for various $R_s/R_{high}$ and $R_{neu}/R_{high}$<br>combinations comparing the technology aware training scheme with normal<br>training for (a) FCN and (b) CNN. Larger crossbars show higher accuracy<br>degradation.                                                                                   | 97  |

| 5.1 | A typical non-ideal crosspoint structure with NVM devices accompanied by a transistor at every junction of the word-lines (WL) and bit-lines (BL).                                                                                                                                                                                               | 103 |

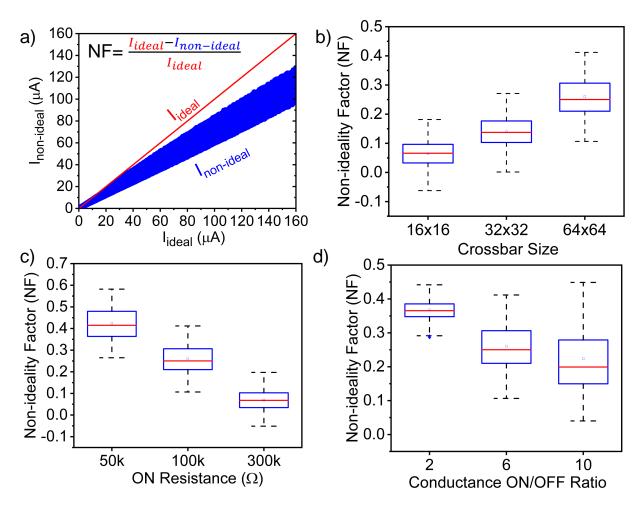

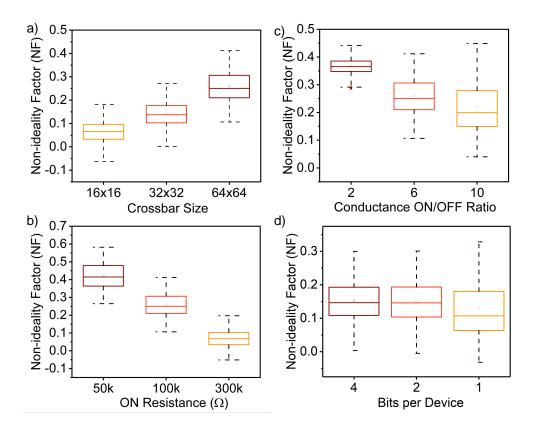

| 5.2 | (a) Output currents from a 64x64 crossbar showing the deviation of $(I_{non-ideal})$ from $(I_{ideal})$ . (b), (c) and (d) shows the box-plot variation of the NF with varying crossbar design parameters.                                                                                                                                       | 104 |

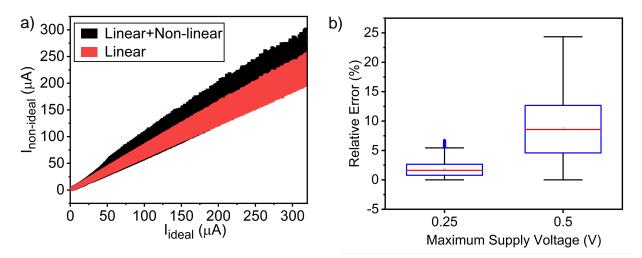

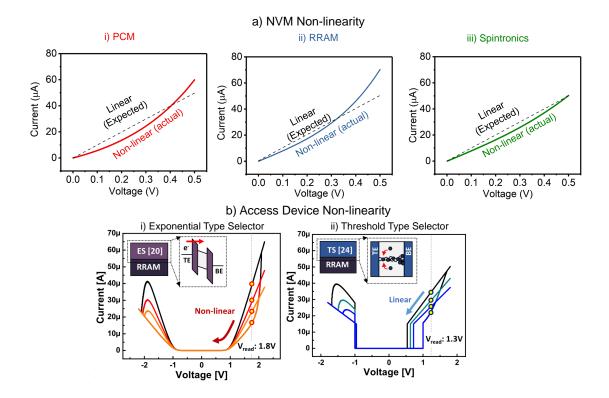

| 5.3 | (a) Output current distribution showing impact of non-linearity. (b) Relative error between the cases with and without nonlinearity increases with increase in maximum supply voltage                                                                                                                                                            | 105 |

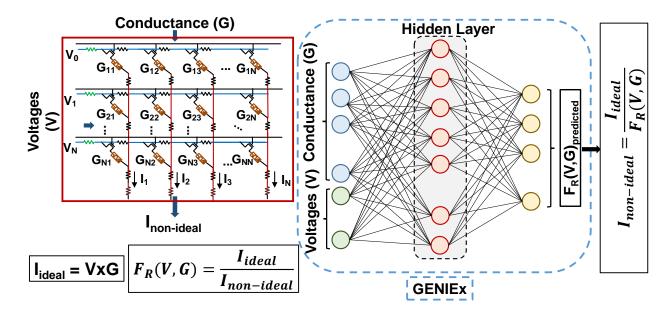

| 5.4 | Crossbar computation mapped to GENIEx. $V$ and $G$ are concatenated to form the input vector for neural network, with output being the ratio $f_R = I_{ideal}/I_{non-ideal}$ .                                                                                                                                                                   | 106 |

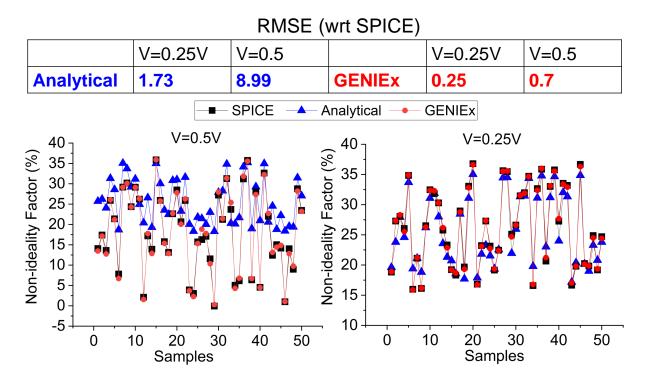

| 5.5 | Comparison of $NF$ for a typical 64x64 crossbar between HSPICE outputs, analytical model and GENIEx.                                                                                                                                                                                                                                             | 108 |

| 5.6 | Logical organization of functional simulator                                                                                                                                                                                                                                                                                                     | 108 |

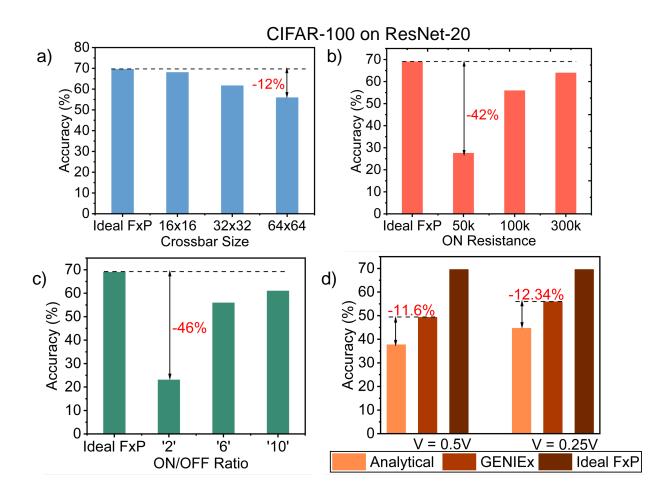

| 5.7 | Impact of non-idealities with crossbar design parameters (a) Crossbar Size,<br>(b) ON resistance, (c) ON/OFF ratio. (d) Comparison between analytical<br>model and GENIEx.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 112 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

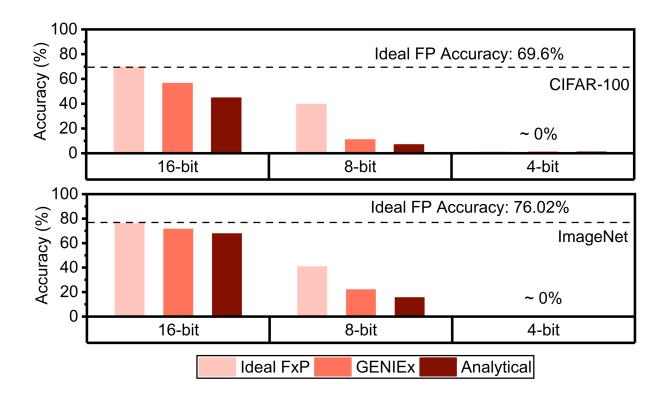

| 5.8 | Impact of precision of weights and activations on classification accuracy under the influence of non-idealities.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 113 |

| 5.9 | Impact of number of bits/device and bits/stream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 114 |

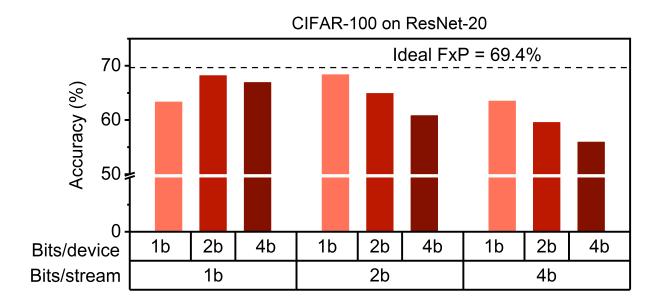

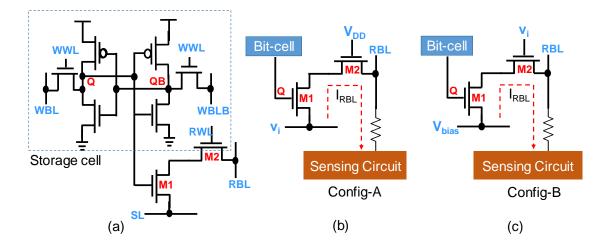

| 6.1 | (a) Schematic of a standard 8T-SRAM bit-cell. It consists of two decoupled<br>ports for reading and writing respectively. (b) First proposed configuration<br>(Config-A) for implementing the dot product engine using the 8T-SRAM bit-<br>cell. The SL is connected to the input analog voltage $v_i$ , and the RWL is<br>turned ON. The current $I_{RBL}$ through the RBL is sensed and is proportional<br>to the dot product $v_i \cdot g_i$ , where $g_i$ is the ON/OFF conductance of the transis-<br>tors $M1$ and $M2$ . (c) Second proposed configuration (Config-B). The input<br>analog voltages are applied to the RWL, while the SL is supplied with a con-<br>stant voltage $V_{bias}$ . The current through the RBL is sensed in the same way<br>as in Config-A. | 117 |

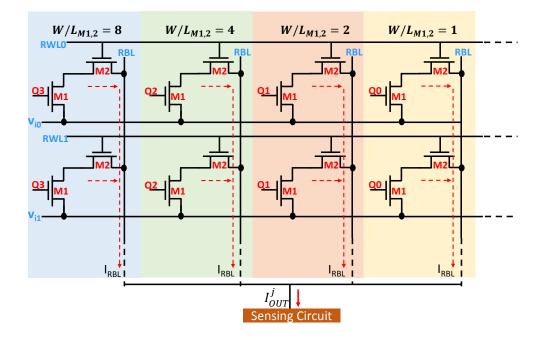

| 6.2 | 8T-SRAM memory array for computing dot-products with 4-bit weight preci-<br>sion. Only the read port is shown, the 6T storage cell and the write port are<br>not shown. The array columns are grouped in four, and the transistors $M1$<br>and $M2$ are sized in the ratio $8:4:2:1$ for the four columns. The output<br>current $I_{OUT}^{j}$ represents the weighted sum of the $I_{RBL}$ of the four columns,<br>which is approximately equal to the desired dot-product.                                                                                                                                                                                                                                                                                                   | 120 |

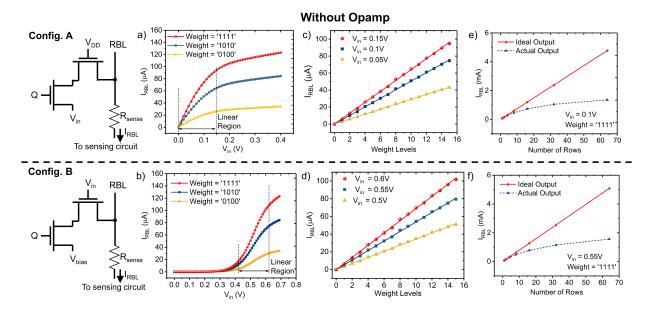

| 6.3 | $I_{RBL}$ versus $V_{in}$ characteristics for (a) Config. A and (b) Config. B shows the<br>linear region of operation for different weights. $I_{RBL}$ versus Weight levels for<br>(c) Config. A and (d) Config. B shows desirable linear relationship at various<br>voltages $V_{in}$ . $I_{RBL}$ shows significant deviation from ideal output ( $I_N = N \times I_1$<br>with increasing number of rows for both (e) Config. A and (f) Config. B,<br>where $I_1$ is the current corresponding to one row and N is the number of<br>rows. The analyses were done for $V_{DD} = 0.65V$                                                                                                                                                                                         | 122 |

| 6.4 | $I_{RBL}$ versus $V_{in}$ characteristics for (a) Config. A and (b) Config. B shows<br>the linear region of operation for different weights. $I_{RBL}$ versus weight levels<br>for (c) Config. A and (d) Config. B shows desirable linear relationship at<br>various voltages $V_{in}$ . $I_{RBL}$ shows almost zero deviation from ideal output<br>$(I_N = N \times I_1$ with increasing number of rows for both (e) Config. A and<br>(f) Config. B, where $I_1$ is the current corresponding to one row and N is the<br>number of rows. These analyses were done for $V_{DD} = 0.65V$                                                                                                                                                                                        | 124 |

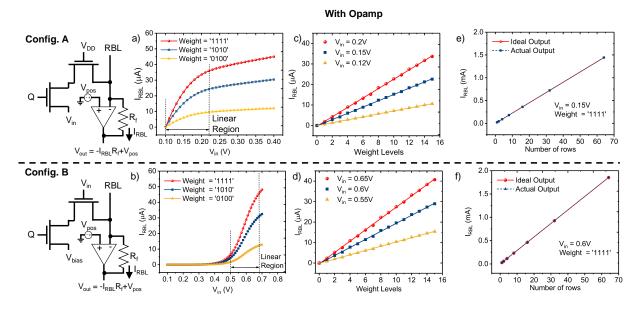

| 6.5 | Fully connected network topology consisting of 3 layers, the input layer, the hidden layer and the output layer [22]. We have used $M=784$ , $N = 500$ and $P = 10$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 126 |

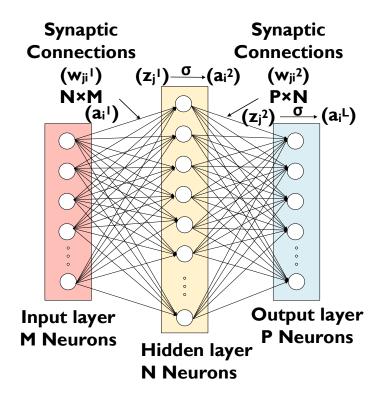

| 6.6 | Thin-cell layout for a standard 8T-SRAM bit-cell [196].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 127 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

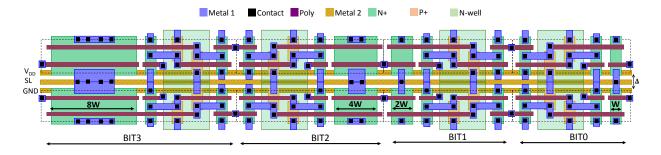

| 6.7  | Thin-cell layout for the proposed 8T-SRAM array with 4-bit precision weights. The width of read transistors of different bit positions are sized in the ratio 8:4:2:1. An additional metal line for SL is also required, which runs parallel to the power-lines. This incurs an area overhead of $\sim 29.4\%$ compared to the standard 8T-SRAM bit-cell.                                                                                                                                                                                                                                                                                                                                                                                            | 127 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

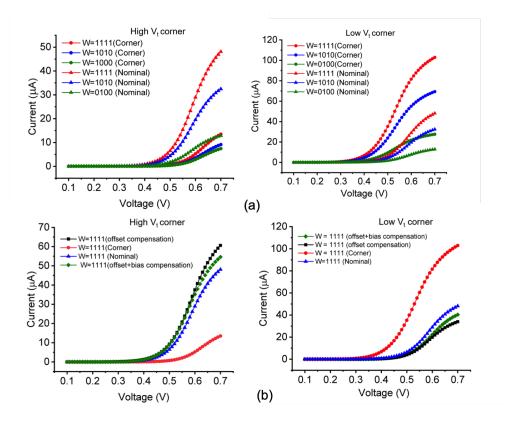

| 6.8  | (a) Shows the effect of global change in VT on the output current for +/-<br>90mV change in the nominal VT. (b) Shows that by adjusting the Vpos (<br>Offset compensation) or Vpos in addition to Vbias (Offset + bias compen-<br>sation), the resultant currents in presence of global variations can be easily<br>compensated for.                                                                                                                                                                                                                                                                                                                                                                                                                 | 128 |

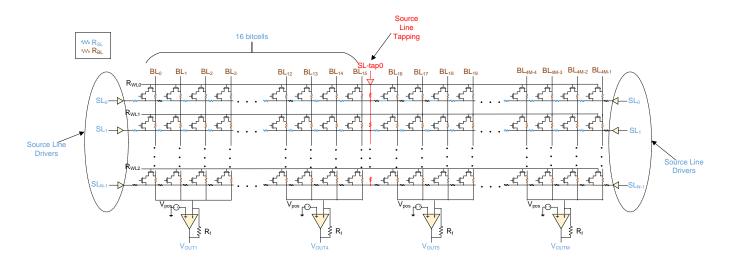

| 6.9  | Bitcell organization of Config. B variants showing SL driven from both ends<br>and tapping of SL every 16 bitcells. The line resistances in the source line<br>(SL) and the bit-line (BL) are shown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 131 |

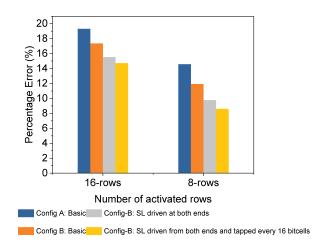

| 6.10 | Percentage error in output current for worst case combination (highest input values and all weights = '1111'). The left set of bar graphs represent the error for various combinations assuming 16 rows are activated simultaneous for the dot product computation, while the right set of bar graphs correspond to simultaneous activation of 8 rows.                                                                                                                                                                                                                                                                                                                                                                                               | 132 |

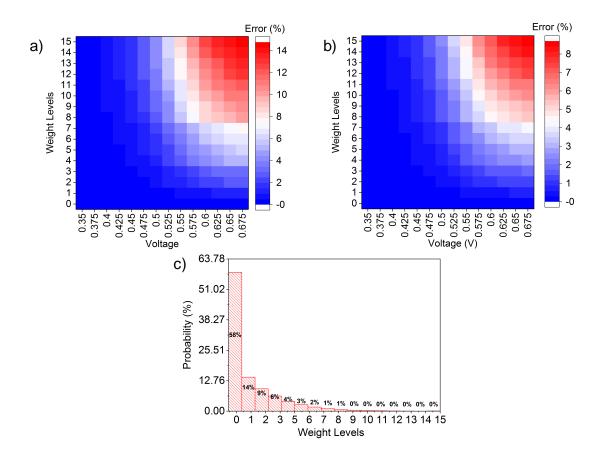

| 6.11 | (a) and (b) shows the percentage error map arising due to line resistance for different weight levels ranging from '0000' to '1111' and input voltages ranging from $0.35V$ to $0.675V$ for 16 and 8 activated rows. For e.g., the data point corresponding to $V = 0.35V$ and weight level = '0000' means the test case where all the 4-bit weight elements in the memory array are considered to be at weight '0000' and the input voltages to all rows are $0.35V$ . The percentage error decreases with decreasing weight and input value. (c) Probability of occurrence of weight levels in a trained neural network on MNIST dataset shows lowest weight levels have the highest frequency, thus indicating low impact due to line resistance. | 133 |

| 6.12 | (a) Standard deviation of current due to variations in Vt of the transistors of the bitcells with increasing current for 1000 Monte Carlo simulations. A single data point shown here refers to the standard deviation in output current when 16 rows are activated and input voltages to all rows are $V_{in}$ and weights of all elements are $w$ . For different data points, we consider $V_{in}$ values ranging from 0.35V to 0.675V in steps of 0.025V and weight levels ranging from 1 to 16 to capture the impact of $V_T$ variations across the input parameter space. (b) Standard deviation as a percentage of the total current showing a decreasing trend with higher current.                                                          | 134 |

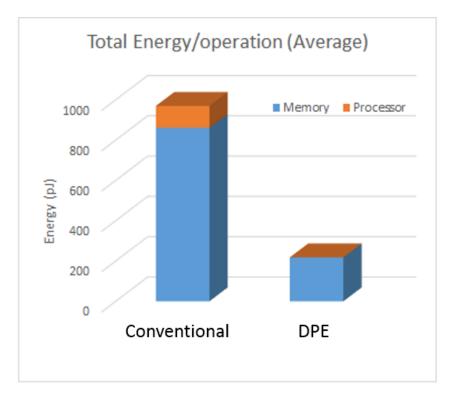

| 6.13 | Average Energy comparison between conventional digitial sequential imple-<br>mentation and proposed Dot-product Engine (DPE). The energy is reported<br>for 16x16 dot product computations wherein 16 rows are simultaneously ac-<br>tivated and each row consists of 16 4-bit words.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 138 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

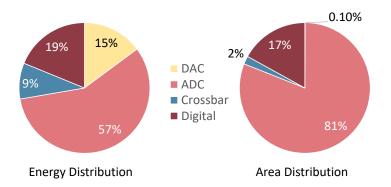

| 7.1  | Energy and area distribution of ReRam-based MVMU                                                                                                                                                                                                                                            | 140 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

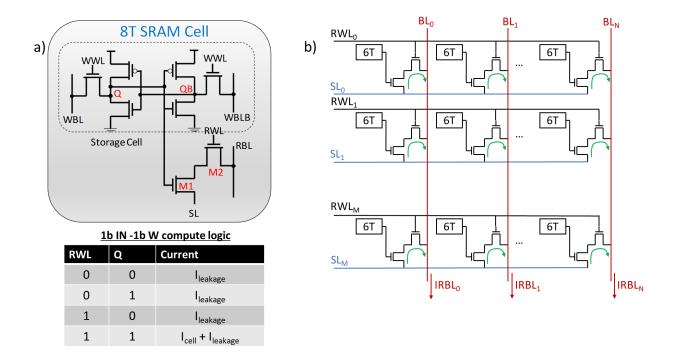

| 7.2  | 8T SRAM array deploying current-domain compute to perform MAC opera-<br>tions, with the table showing compute logic.                                                                                                                                                                        | 142 |

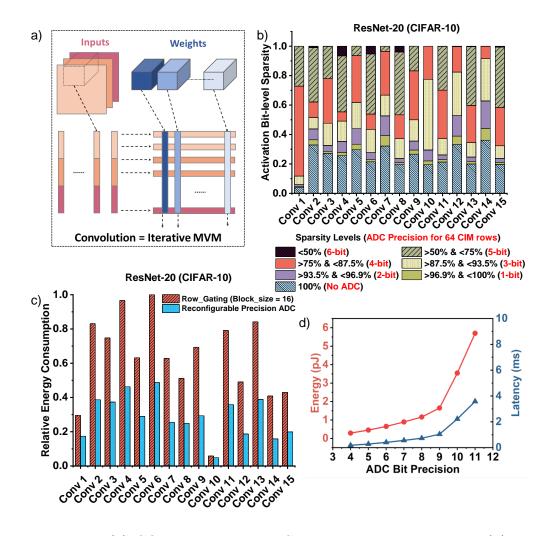

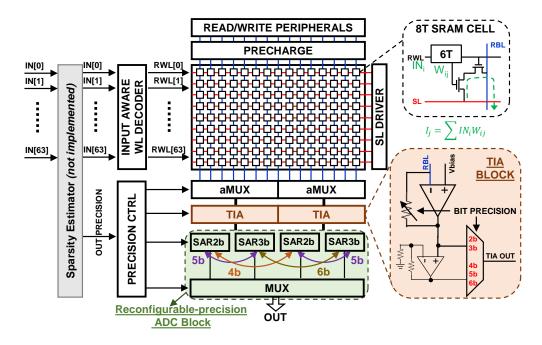

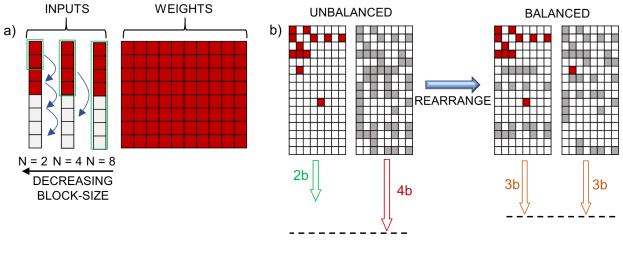

| 7.3  | (a) CONV operation on CIM using iterative MVMs. (b) Bit-level sparsity of<br>a ResNet-20 model running CIFAR-10 with the required ADC precision. (c)<br>Comparison between row gating and reconfigurable-precision ADC in terms<br>of energy. (d) Energy/latency scaling with ADC precision | 143 |

| 7.4  | The proposed macro structure and timing diagram.                                                                                                                                                                                                                                            | 145 |

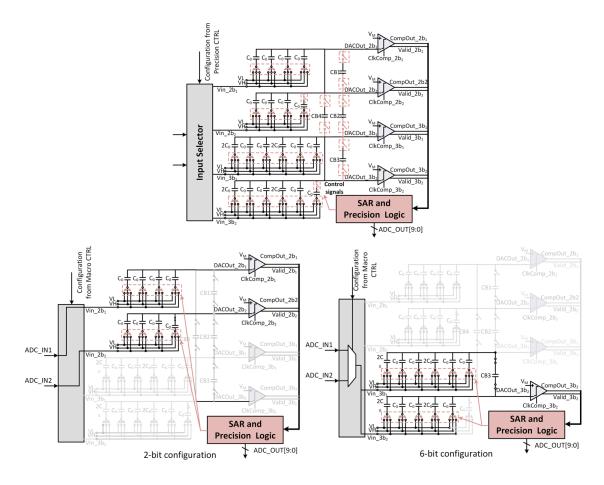

| 7.5  | The proposed reconfigurable-precision SAR ADC with two example configu-<br>rations: 2-bit and 6-bit precision                                                                                                                                                                               | 146 |

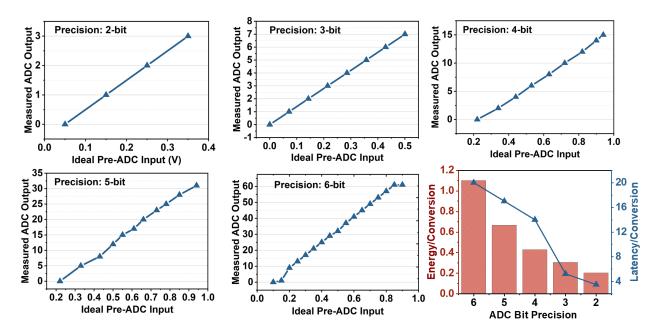

| 7.6  | Measured ADC results showing output vs input voltage, energy and latency for various precisions.                                                                                                                                                                                            | 147 |

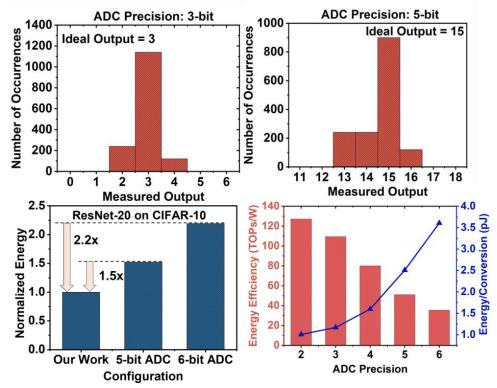

| 7.7  | Measured CIM macro results show good agreement between expected output<br>and measured output, energy efficiency for different precision and baseline<br>comparison on workload.                                                                                                            | 149 |

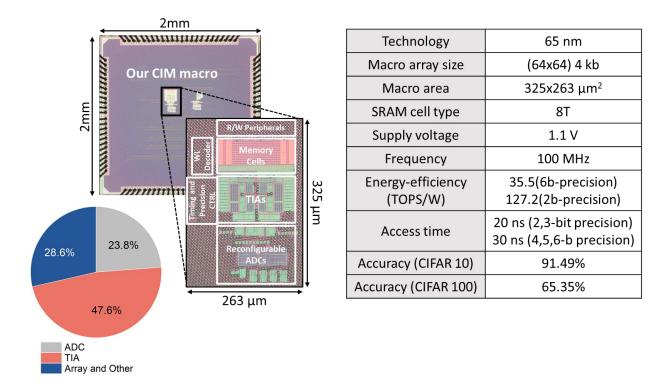

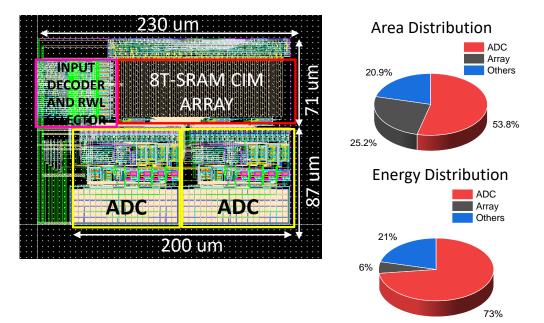

| 7.8  | Die micrograph and chip summary with the macro energy breakdown                                                                                                                                                                                                                             | 150 |

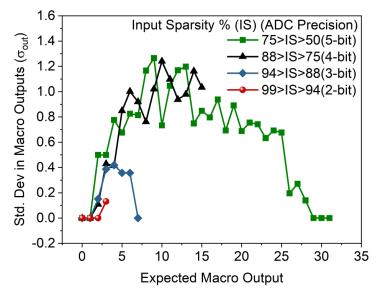

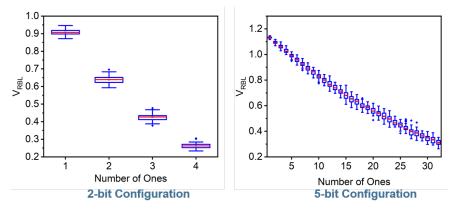

| 7.9  | Standard Deviation in measured outputs from proposed CIM Macro                                                                                                                                                                                                                              | 150 |

| 7.10 | Accuracy of fixed precision ADC v/s reconfigurable precision ADC                                                                                                                                                                                                                            | 151 |

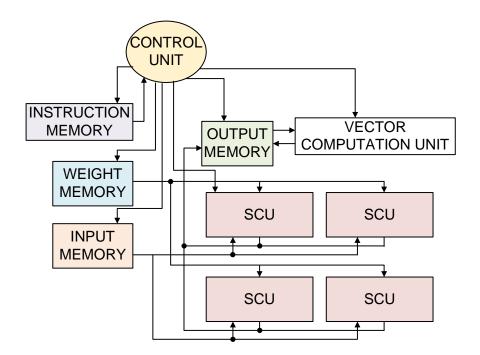

| 7.11 | CIM Core Features: a) SNR-aware Row Gating and b) Latency Balancing .                                                                                                                                                                                                                       | 153 |

| 7.12 | SCU Microarchitecture                                                                                                                                                                                                                                                                       | 155 |

| 7.13 | Sparsity Contoller Logical Diagram                                                                                                                                                                                                                                                          | 156 |

| 7.14 | Sparsity-Aware CIM Macro with Reconfigurable Precision ADC, leveraging charge-domain computation                                                                                                                                                                                            | 157 |

| 7.15 | Reconfigurable Shift-and-add circuit logical flow                                                                                                                                                                                                                                           | 159 |

| 7.16 | Core Microarchitecture                                                                                                                                                                                                                                                                      | 160 |

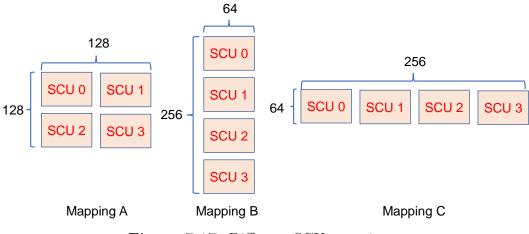

| 7.17 | Different SCU mappings                                                                                                                                                                                                                                                                      | 161 |

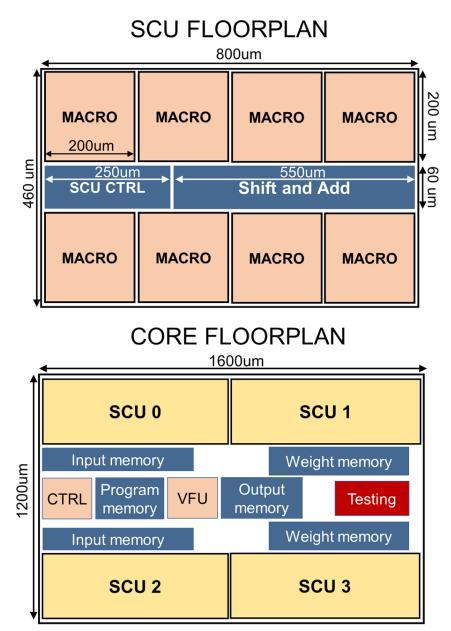

| 7.18 | Tentative SCU and Core Floorplan                                                                                                                                                                                                                                                            | 163 |

| 7.19 | Simulation Results for Macro                                                                                                                                                                                                                                                                | 164 |

| 7.20 | Macro Layout and Energy/Area Distribution of components                                                                                                                                                                                                                                     | 165 |

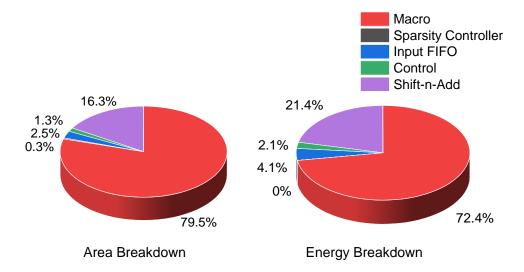

| 7.21 | Preliminary SCU Energy/Area Breakdown                                                                                                                                                                                                                                                       | 166 |

| 7.22 | Estimated SCU Performance in TOPS/s                                                                                                                                                                                                                                                         | 166 |

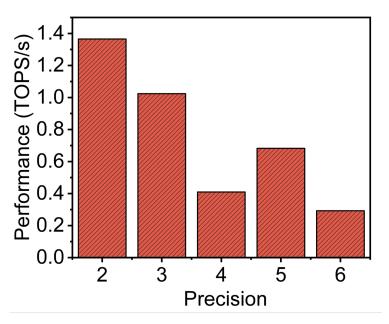

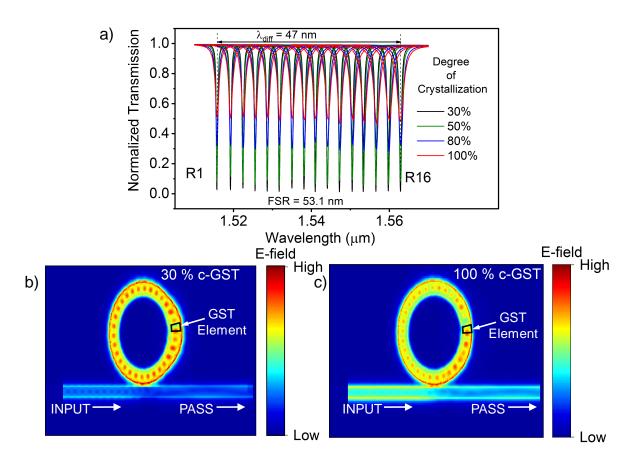

| 8.1 | (a) A perspective view of an add-drop microring resonator with a small patch<br>of GST on top showing its ports and materials. (b) A two-dimensional<br>top view of the ring resonator illustrating the input, output, coupling and<br>transmission parameters. Theoretically calculated transmission at various<br>wavelengths for different degrees of amorphization of GST ranging from 0%<br>(crystalline) to 100% (amorphous) showing that the transmission at the (c)<br>'THROUGH' ((d) 'DROP') port decreases (increases) with increasing degree<br>of amorphization.                                                                                                                                                                                                                                                                                                                                                              | 170 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

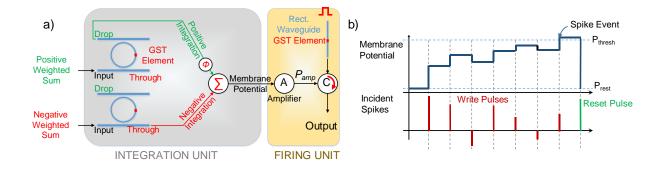

| 8.2 | (a) Schematic of a bipolar integrate and fire neuron based on GST-Embedded<br>Ring resonator devices showing the integration and firing unit. (b) Timing<br>diagram showing the integration of membrane potential for various incident<br>pulses demonstrating the operation of the proposed neuron.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 172 |

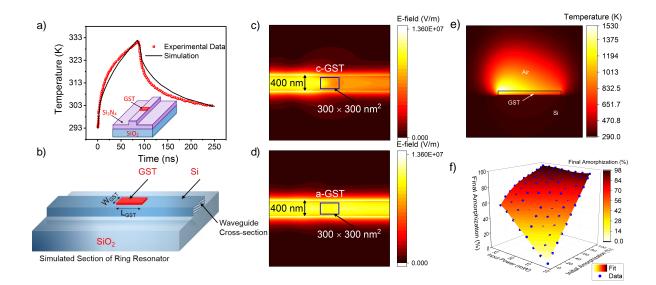

| 8.3 | (a) Experimental benchmarking on a $Si_3N_4$ -SiO <sub>2</sub> ridge-waveguide system, validating our simulation framework. (b) Simulated volume of the GST section in the ring resonator described in Fig. 8.1 (a) delineating the different materials used. Surface electric field propagation of (c) c-GST and (d) a-GST shows significant contrast. (e) Temperature distribution along the length of cGST. (f) Plot of final percentage amorphization as a function of initial percentage amorphization and input power.                                                                                                                                                                                                                                                                                                                                                                                                              | 176 |

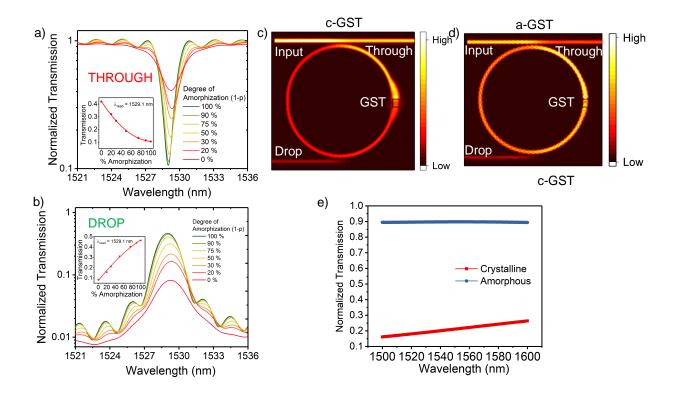

| 8.4 | Normalized Transmission at the (a) 'THROUGH' and (b) 'DROP' ports with<br>increasing degree of amorphization for a particular range of frequencies includ-<br>ing a resonance peak at $\lambda_{read} = 1529.1nm$ . As the degree of amorphization<br>increases, transmission at 'THROUGH' ('DROP') port decreases (increases)<br>thus realizing negative (positive) integration action of the neuron. (c) and (d)<br>shows the top-view E-field distribution of a GST-embedded ring resonator for<br>c-GST and a-GST showing higher field absorption for the former when the<br>wave passes the GST region. (e) High contrast between c-GST and a-GST<br>for the rectangular waveguide in the firing unit of the neuron.                                                                                                                                                                                                                 | 178 |

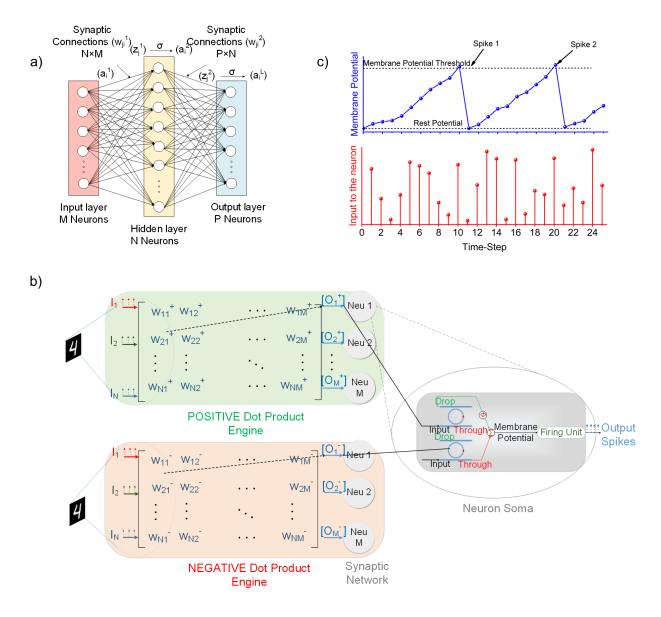

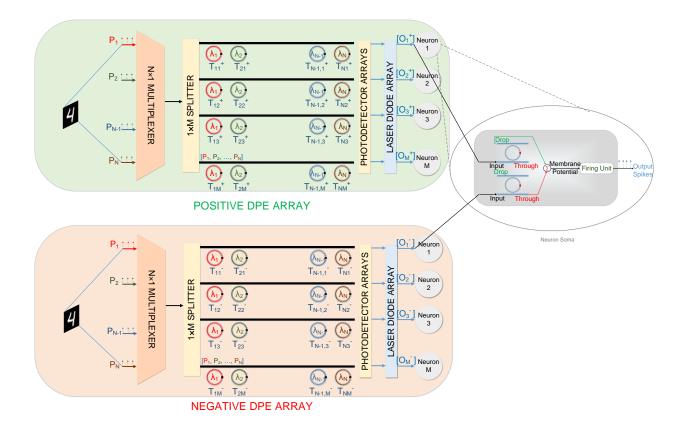

| 8.5 | (a) Fully connected ANN topology showing 3 interconnected layers, namely, the input layer, the hidden layer and the output layer[22], (b) Schematic of potential integration of an integrate-and-fire neuron in a spiking neural network framework consisting of bipolar weights. The positive and negative weighted sums are computed using two separate dot-product engines and input to two different ring-resonators. The bidirectional integrating action of the two ports of the ring resonator is leveraged to calculate the effective membrane potential under the action of the bipolar weighted sums. Output spikes are generated when the effective membrane potential of the neuron crosses a threshold by the spike generation mechanism described. (c) The behavior of the proposed integrate-and-fire neuron in the simulated SNN showing the variation of the membrane potential under the action of incident pulses thus |     |

|     | showing integrate and firing action.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 180 |

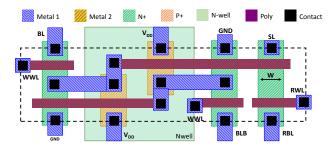

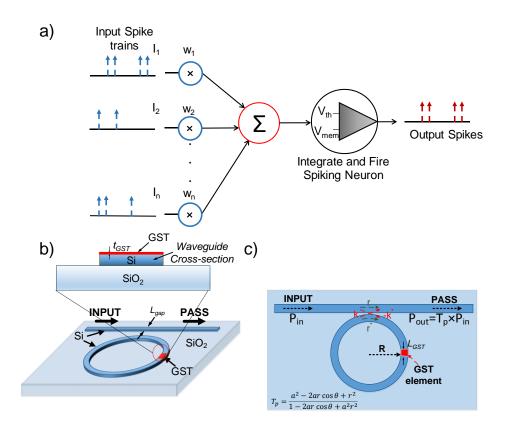

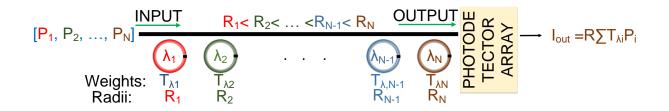

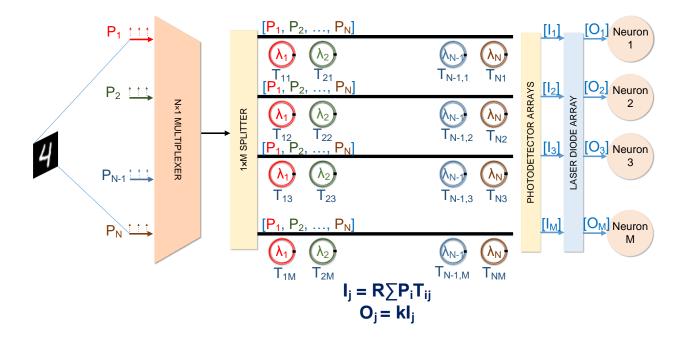

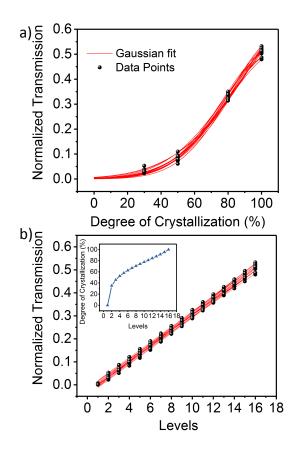

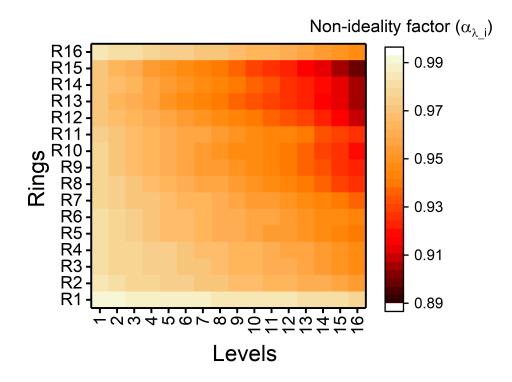

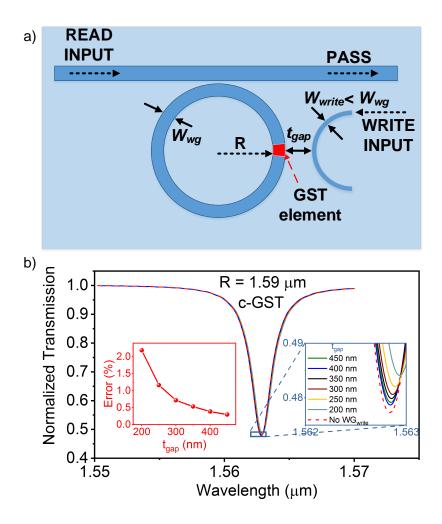

| (a) The basic functional elements of an SNN are spiking neurons and weighted synaptic connections. At each time instant, the inputs are weighted by the synaptic weights to produce a resultant output represented as $\sum_i P_i w_i$ . The 'integrate-and-fire' neuron's membrane potential $(V_{mem})$ is updated according to the weighted sum and compared with a threshold value $(V_{th})$ . (b) GST-embedded single bus microring resonator structure with Si waveguides on SiO <sub>2</sub> substrate. (c) Top view of the device illustrating the different parameters pertaining to the ring resonator structure. The synaptic device performs an analog multiplication of input $P_{in}$ and transmission $T$ . | 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

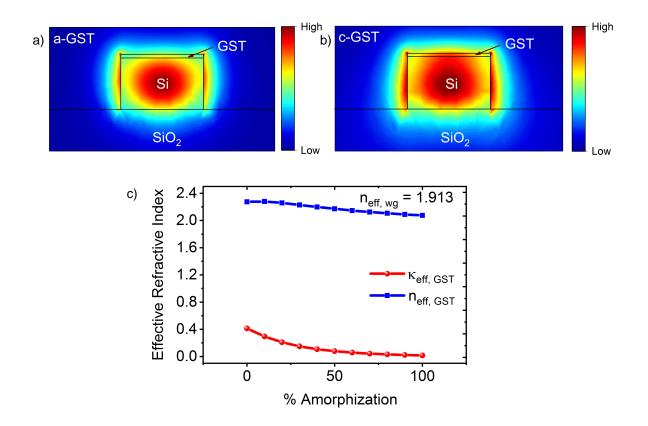

| Cross-section view of Fundamental Mode profiles for a GST-embedded Si-<br>SiO <sub>2</sub> waveguide section for (a) a-GST and (b) c-GST showing visible contrast<br>in optical absorption for the two boundary states of GST. (c) The variation of<br>the real $(n_{eff,GST})$ and imaginary $(\kappa_{eff,GST})$ refractive indices of GST with<br>degree of crystallization.                                                                                                                                                                                                                                                                                                                                             | 187                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |