## FABRICATION AND CHARACTERIZATION OF SILICON PHOTONIC DEVICES

by

Abdullah Al Noman

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana August 2021

## THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Andrew M Weiner, Chair

School of Electrical and Computer Engineering

### Dr. Minghao Qi, Co-Chair

School of Electrical and Computer Engineering

## Dr. Alexandra Boltasseva

School of Electrical and Computer Engineering

### Dr. Peter Bermel

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

This thesis is dedicated to my son Izaan Abdullah, who not only supported and inspired me during my whole PhD life, but also sacrificed a lot. I love you, Son.

## ACKNOWLEDGMENTS

Firstly I want to convey my gratitude to Almighty for giving me the ability and strength to complete this thesis. I want to convey my heartfelt thanks and gratitude to my supervisor Professor Andrew M Weiner. It was impossible for me to finish this thesis without his continuous support and guidance. During my whole graduate life, he has been like a constant guardian and supported me with everything like a father. I personally learned a lot of things from him and I'll try my best to implement them in my professional life. I am also very thankful to my co-advisor Professor Minghao Qi for all his guidance towards the fabrication side of my thesis. He also has been very very patient with me and supported me all along with valuable discussions and encouragements. I am grateful to my committee members Professor Peter Bermel and Professor Alexandra Boltasseva for their valuable time, help and suggestion for improving my work. I also want to convey my gratitude to Dr. Yi Xuan, who is currently a professor in Indiana University (IU) at Indianapolis, for helping and guiding me during my initial fabrication efforts.

I am grateful to Dr. Daniel E. Leaird for all his help and guidance during my PhD life. Whenever I faced any problem regarding any measurements or any equipment in our measurement lab, he was always there to solve it. I'm ever grateful to our wonderful group members from our Ultrafast Optics group for their help and support from the beginning. I want to specially mention Cong Wang, Nathan O'Malley, Keith McKinzie, Dr. Mohammed Saleh Al alshaykh, Dr. Jose Jaramillo and Saleha Fatema's name, they have been extremely patient and helpful. They not only helped me to develop my measurement skills, but also measured many of the devices that I fabricated. I'm grateful to Birck Nanotechnology Center of Purdue University and all its staffs for providing me a top class fabrication facility. I want to specifically mention Dr. Justin Wirth, Richard Hosler, Dan Hosler, Bill Rowe, Francis Manfred, Dave Lubelski, Jeremiah Shepard, Dr. Joon Park and all other research staffs at Birck who not only trained me on equipment and kept them up, but also helped me to evolve and try new things during my PhD life. Over the years, I had so many interactions with them that a personal relation grew with many of them beside our professional one. I'm grateful to Ron Reger, Stephen Jurss and all the building and safety team for keeping us safe and keeping the facility operational during the difficult COVId situation. I'm grateful to all the clerical staffs at Birck, specially Mary Jo Totten who used to love me like a mother, helped me a lot and always used to ask about my well-beings. I'm grateful to all the cleaners and maintenance people for keeping the facility clean, safe and usable for all the students. I'm grateful to many graduate students at Birck whom I came to know during my PhD timeline. Many of them helped me with valuable suggestions, helps or even with the presence inside the cleanroom. I want to specifically mention my group mates from Professor Qi's group-Yun Jo Lee, Gregory Cheng, Ruihan Chen, Ziyun Cong, Yingheng Tang and Dr. Min Tang for all their help and support. I also want to thank Dr. Naeemul Islam, Samuel Paena, Dr. Rahul Ramamurthy and Sarah Nahar Chowdhury for their immense help and cooperation in cleanroom.

Finally I'm grateful to my family members and my friends whose constant support and encouragement has been very very important for my life. I am grateful to my father Md. Abdul Quader who has always supported me. I'm grateful to my siblings Md. Abdul Kaium Omi, Irin Parvin Nipu and Lamia Tasnim Suhi for always inspiring me. I'm grateful to my wife Rafatul Faria for always supporting me. I'm grateful to our son Izaan Abdullah, who has been very very patient and sacrificed a lot due to my busy schedules and always inspired me. I'm grateful to all my friends at Purdue University, specially the people from Bangladesh Community who made me feel at home and helped me in all possible ways. I want to thank all the people from Purdue University Cricket Club, where I had some wonderful years with many good memories. They always treated me like a family and I am always grateful for developing many good friends there over the years. Finally, I want to thank my mother, who is watching me from heaven and I hope she is proud of this moment.

# TABLE OF CONTENTS

| LIST OF         | TABLES                                               | 10 |  |  |  |  |

|-----------------|------------------------------------------------------|----|--|--|--|--|

| LIST OF FIGURES |                                                      |    |  |  |  |  |

| LIST OF         | SYMBOLS                                              | 17 |  |  |  |  |

| ABBREV          | VIATIONS                                             | 18 |  |  |  |  |

| ABSTRA          | ACT                                                  | 19 |  |  |  |  |

| 1 INTR          | ODUCTION                                             | 21 |  |  |  |  |

| 1.1             | Light Confinement Techniques in Photonic Waveguides  | 21 |  |  |  |  |

|                 | 1.1.1 Crosstalk                                      | 21 |  |  |  |  |

|                 | 1.1.2 Light Confinement Techniques                   | 22 |  |  |  |  |

| 1.2             | Microring resonator                                  | 24 |  |  |  |  |

| 1.3             | Optical Frequency Comb                               | 31 |  |  |  |  |

| 1.4             | Organization of the report                           | 36 |  |  |  |  |

| 2 FABR          | RICATION AND LOSS CHARACTERIZATION OF E-SKID DEVICES | 37 |  |  |  |  |

| 2.1             | Motivation and Goal                                  | 37 |  |  |  |  |

| 2.2             | Fabrication of E-skid Devices                        | 37 |  |  |  |  |

| :               | 2.2.1 Fabrication Method                             | 38 |  |  |  |  |

| :               | 2.2.2 Fabrication Challenges                         | 40 |  |  |  |  |

| 2.3             | Crosstalk measurement                                | 42 |  |  |  |  |

| 2.4             | Loss Measurements of E-skid Devices                  | 43 |  |  |  |  |

| 3 FABRICATION AND CHARACTERIZATION OF MODE FILTER DEVICES |     |        |                                                     |    |

|-----------------------------------------------------------|-----|--------|-----------------------------------------------------|----|

|                                                           | FOR | R ON C | HIP MODE DIVISION MULTIPLEXING                      | 48 |

|                                                           | 3.1 | Introd | uction                                              | 48 |

|                                                           | 3.2 | Fabric | ation                                               | 49 |

|                                                           | 3.3 | Measu  | rement set up                                       | 49 |

|                                                           | 3.4 | Mode   | Filter Design using MMI                             | 50 |

| 4                                                         | FAB | RICAT  | TON OF SILICON NITRIDE MICRORING RESONATOR          | 56 |

|                                                           | 4.1 | Objec  | tive and Goal                                       | 56 |

|                                                           | 4.2 | Fabric | ation of Silicon Nitride microring resonator        | 56 |

|                                                           |     | 4.2.1  | Introduction                                        | 56 |

|                                                           |     | 4.2.2  | Old Fabrication steps                               | 58 |

|                                                           |     | 4.2.3  | DARPA A-Phi Project and its unique challenges       | 59 |

|                                                           | 4.3 | Comp   | arative analysis                                    | 65 |

|                                                           |     | 4.3.1  | Efforts on improving the annealing process          | 67 |

|                                                           | 4.4 | Debug  | ging Fabrication: Finding process defects           | 70 |

|                                                           |     | 4.4.1  | Importance of trenches                              | 71 |

|                                                           |     | 4.4.2  | HSQ aging and dosage change                         | 74 |

|                                                           |     | 4.4.3  | Removal of e-beam resist                            | 75 |

|                                                           |     | 4.4.4  | Implementation of changes                           | 77 |

| 5                                                         | MIC | ROHE   | ATER FABRICATION FOR SILICON NITRIDE MICRORING RES- |    |

|                                                           | ONA | ATOR   |                                                     | 83 |

|    | 5.1  | What is a microheater?                                 | 83  |

|----|------|--------------------------------------------------------|-----|

|    | 5.2  | Microheater Fabrication Process                        | 86  |

|    | 5.3  | Challenges and Difficulties                            | 87  |

|    | 5.4  | Characterization of microheaters                       | 92  |

|    | 5.5  | Summary                                                | 98  |

| 6  | EDG  | E POLISHING PROCESS FOR SILICON NITRIDE MICRORESONATOR | 100 |

|    | 6.1  | Edge Polishing Process                                 | 100 |

|    | 6.2  | Overview and Difficulties                              | 103 |

|    | 6.3  | The Steps of the Edge Polishing Process                | 106 |

|    | 6.4  | Results                                                | 108 |

|    |      | 6.4.1 SEM images                                       | 108 |

|    |      | 6.4.2 Measurement results                              | 108 |

|    |      | 6.4.3 The Heterogeneous Integration                    | 109 |

|    | 6.5  | Summary                                                | 111 |

| 7  | CON  | ICLUSION                                               | 112 |

| Rł | EFER | ENCES                                                  | 114 |

| A  | BAS  | IC FABRICATION PROCESS STEPS                           | 123 |

|    | A.1  | Deposition                                             | 123 |

|    | A.2  | Photolithography                                       | 123 |

|    | A.3  | Etching                                                | 126 |

|   | A.4 | Electron-Beam (E-beam) Lithography           | 129 |

|---|-----|----------------------------------------------|-----|

| В | EDG | E POLISHING PROCESS                          | 131 |

|   | B.1 | Loading the Footer using Epoxy               | 131 |

|   | B.2 | Loading the Sample on Sample Holder          | 133 |

|   | B.3 | Polishing the Sample                         | 136 |

|   | B.4 | Taking the Sample off the Sample Holder      | 136 |

|   | B.5 | Cleaning the Sample with Appropriate Solvent | 138 |

| С | MIC | ROHEATER FABRICATION PROCESS                 | 140 |

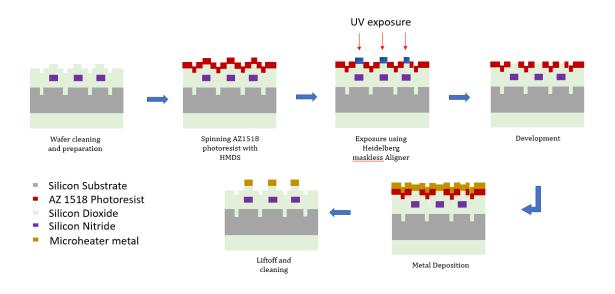

|   | C.1 | Microheater photolithography                 | 140 |

|   | C.2 | Photolithograpy steps                        | 142 |

|   | C.3 | Metal Deposition                             | 143 |

|   | C.4 | Liftoff                                      | 144 |

| D | PUB | LICATIONS                                    | 146 |

# LIST OF TABLES

| 2.1 | Performance Comparison between E-skid and other dielectric waveguides                                                       | 46  |

|-----|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 3.1 | Performance Comparison between some mode filters from literature                                                            | 55  |

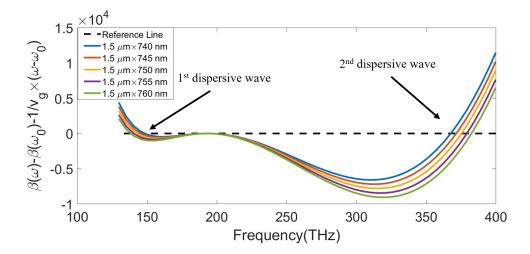

| 4.1 | Thickness Sensitivity of the Dispersive waves                                                                               | 61  |

| 4.2 | Comparison between the fabrication process of different research groups that fabricates Silicon Nitride microring resonator | 65  |

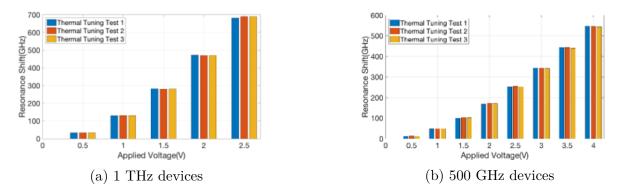

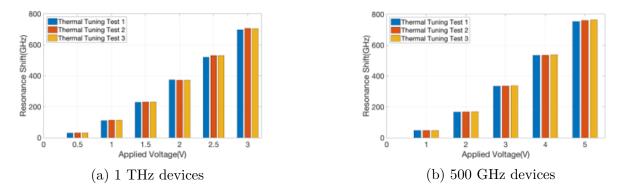

| 5.1 | Characterization of microheaters with 300 nm Titanium and 20 nm Gold $~\ldots$                                              | 93  |

| 5.2 | Characterization of microheaters with 20 nm Titanium and 300 nm Gold                                                        | 94  |

| 5.3 | Comparison of performance for microheaters with 2 different widths                                                          | 94  |

| 5.4 | Characterization of microheaters made of 20nm Ti and 600nm Platinum $\ldots$ .                                              | 96  |

| 5.5 | Performance of microheaters after three hour long constant heating                                                          | 98  |

| 6.1 | Insertion Loss measurement results before and after polishing process                                                       | 110 |

# LIST OF FIGURES

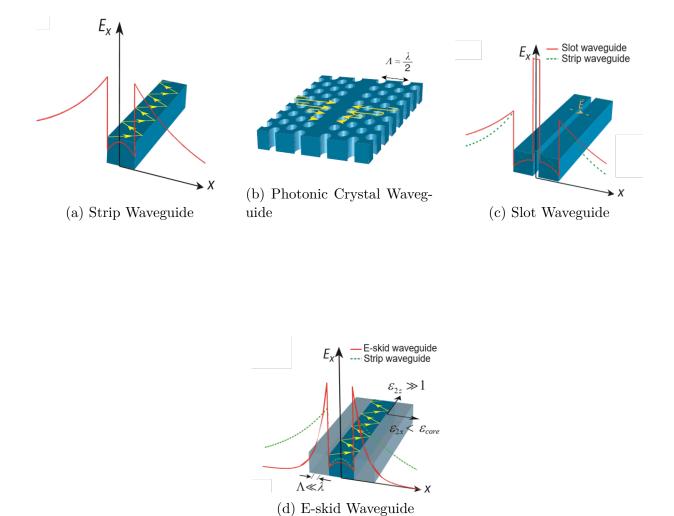

| 1.1 | All Dielectric Waveguides for light confinement in SOI. The Skin Depth of E-skid waveguide is shorter compared to other waveguides. This picture is reproduced from [8].                                                                                                                                                                                                          | 23 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

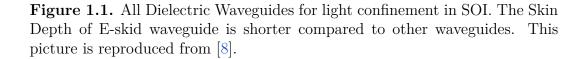

| 1.2 | The basic structure of a microring resonator a) with through port only b) with both through and drop port                                                                                                                                                                                                                                                                         | 26 |

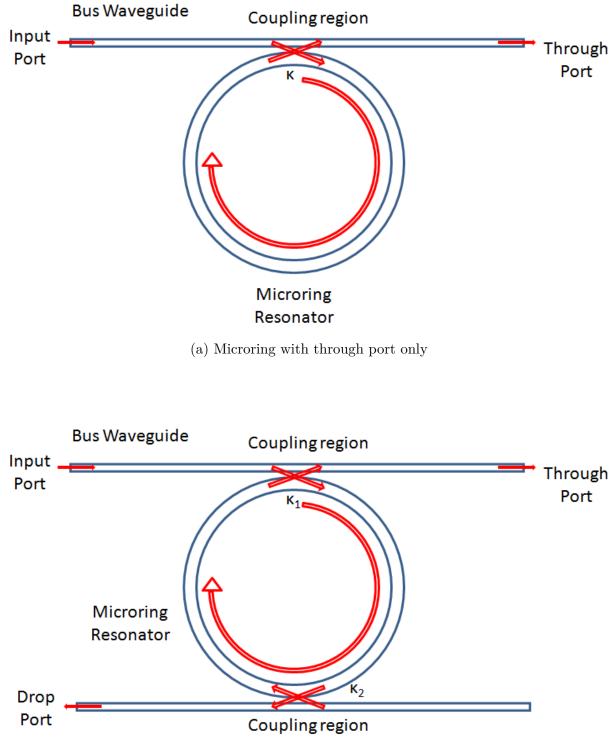

| 1.3 | A sample Transmission Spectrum for a Microring Resonator. Each dip cor-<br>responds to a resonance frequency that the microring resonator can support                                                                                                                                                                                                                             | 27 |

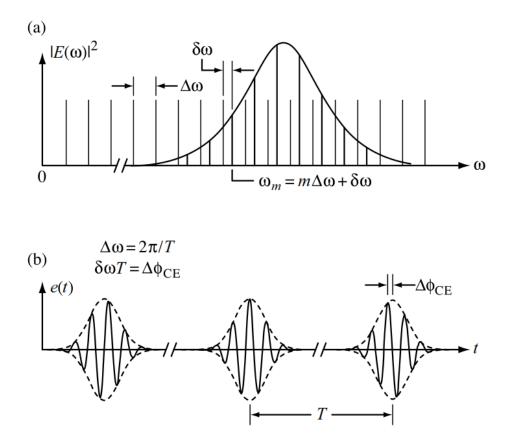

| 1.4 | Mode-locked frequency comb a) The offset frequency $\delta \omega$ is shown b) Pulse to pulse phase shift $\Delta \phi_{CE}$ is shown. The picture is taken from [28]                                                                                                                                                                                                             | 32 |

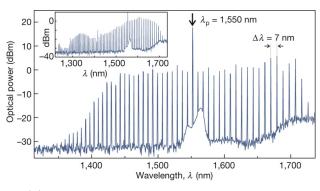

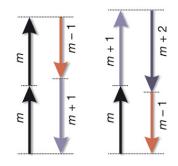

| 1.5 | An example of Optical Frequency comb generated from microresonator via<br>the parametric frequency conversion process. Fig a) shows the broadband<br>frequency comb and Fig. b) shows the difference between degenerate and<br>non-degenerate FWM process. The figure is taken from [7].                                                                                          | 33 |

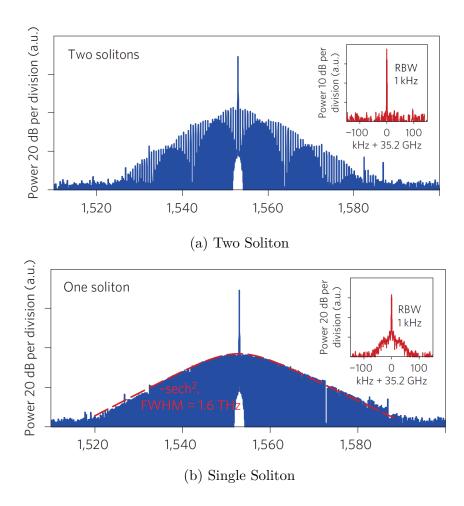

| 1.6 | Frequency comb generation spectrum with (a) Multiple (two) soliton (b) Single soliton. Single soliton spectrum exhibits smoother $sech^2$ profile. Figures are reproduced from [40].                                                                                                                                                                                              | 35 |

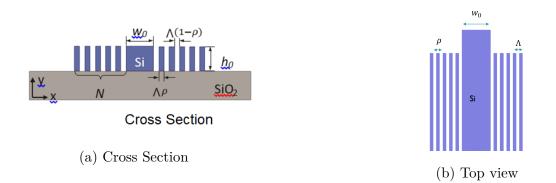

| 2.1 | The design parameters of the E-skid devices. (a) Cross Section and (b) Top view. Here, $w_0$ = Width of the Silicon waveguide= 450nm, $h_0$ = Height of the Silicon waveguide= 220nm, $\rho$ = Width of the AMM structures= 50nm, $\Lambda$ = Spacing between AMM structures= 50nm, N=Number of parallel AMM structures in each side= 5. The cross section is reproduced from [8] | 37 |

| 2.2 | Two different layout schemes for E-skid Devices (a) Grating Coupling Scheme (b) Edge Coupling Scheme. For the final devices we proceed with grating coupling schemes because it needed less number of steps to complete the fabrication.                                                                                                                                          | 38 |

| 2.3 | The three different Layouts for loss measurement (a) Without any AMM structures (b) AMM structures in one arm only (c) AMM structures in both arms                                                                                                                                                                                                                                | 39 |

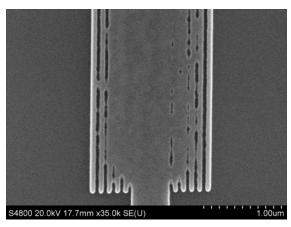

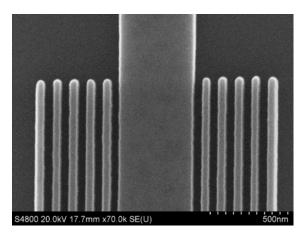

| 2.4 | The effect of dose on structure writing. SEM image of the devices (a) With an unsuitable dose, where the structures merged together (b) With a suitable dose, where the structures are clear and distinct.                                                                                                                                                                        | 41 |

| 2.5 | The effect of high surface tension of water on AMM structures. SEM images of (a) Completely Broken AMM structures (b) Partially Broken AMM structures (c) No Broken AMM structures (used IPA instead of water)                                                                                                                                                                    | 41 |

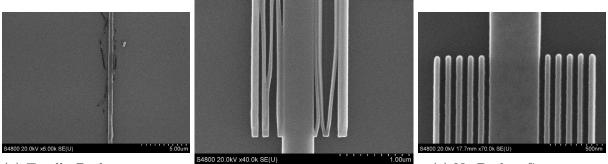

| 2.6 | Experimental demonstrations of low crosstalk with metamaterial sidewalls.<br>(a) Layout and SEM images of the device. (b)(d) Measured power transmissions as a function of device length, when the core widths are (b) $w_0 = 350 \text{ nm}$ and (d) $w_0 = 400 \text{ nm}$ , respectively. Red and blue are the cases with anisotropic (AMM) metamaterial claddings and standard waveguides (STW) respectively. The circles and crosses are for $ S_{21} ^2$ and $ S_{31} ^2$ , respectively. The simulated transmissions are also plotted: $ S_{21} ^2$ (solid line) and $ S_{31} ^2$ (dashed line). (c),(e) Measured power transmission spectra of (c) (L = 120 $\mu$ m) and (e) (L = 200 $\mu$ m) respectively; red and blue are the AMM and STW respectively, and solid lines are for $ S_{21} ^2$ and dashed circles are for $ S_{31} ^2$ . | 42 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

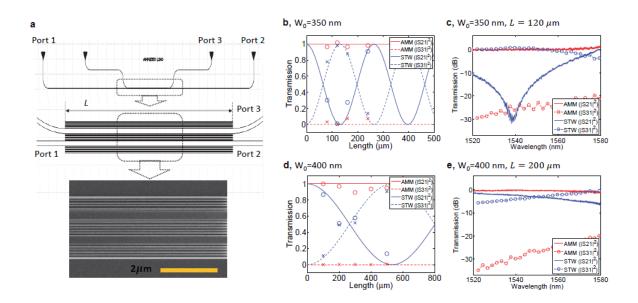

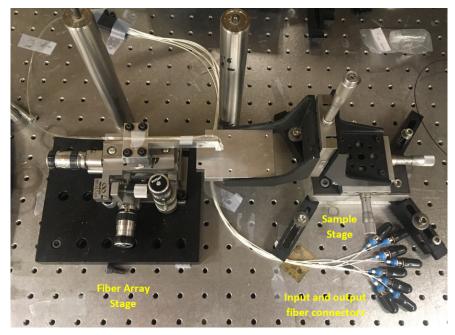

| 2.7 | The set up for loss measurement of e-skid waveguides (a) Schematic Diagram (b) Real set up with fiber array for coupling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44 |

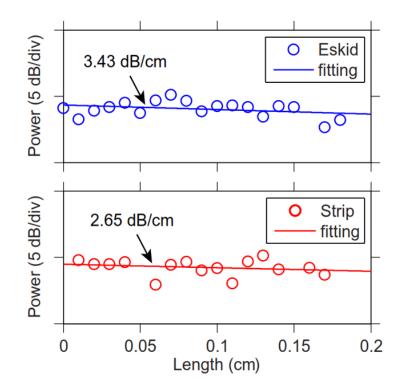

| 2.8 | The Loss measurement of E-skid and the reference strip waveguides. The circle represents normalized transmission through E-skid (blue) and Reference strip (red) waveguides at $\lambda$ =1550 nm. The propagation loss in e-skid and strip waveguide is 3.43 and 2.65 dB/cm at = 1550 nm, and the average losses for e-skid and strip waveguides for wavelengths between 1540 nm to 1560 nm are 3.67 dB/cm and 1.84 dB/cm, respectively, with a standard deviation of 1.0 dB/cm and 1.4 dB/cm, respectively. Figure reproduced from [8]                                                                                                                                                                                                                                                                                                           | 45 |

| 3.1 | A sample set up for measuring Transmission Spectrum for the Mode filter devices. The coupling was done using two lensed fibers and they were very precisely controlled using the 5 axis stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49 |

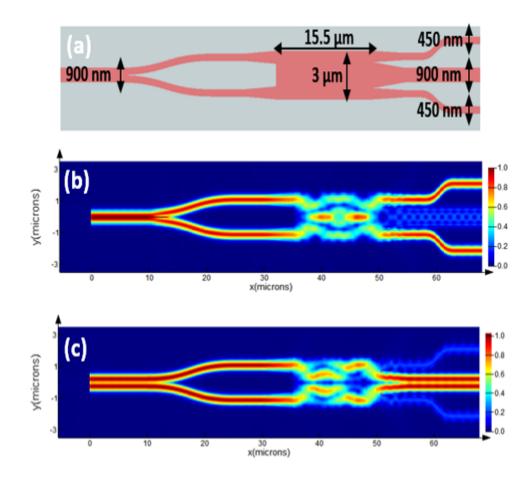

| 3.2 | SOI $TE_1$ pass $TE_0$ filter a) Schematic diagram of the device b) FDTD simula-<br>tion plot of Electric field with $TE_0$ input c) FDTD simulation plot of Electric<br>field with $TE_1$ input. The simulation results were taken from Dr. Min Teng's<br>PhD thesis with permission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51 |

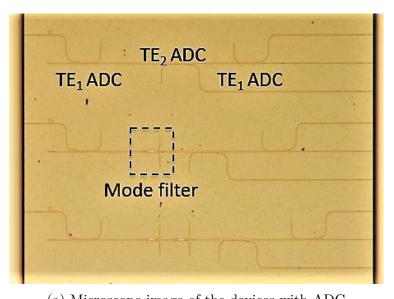

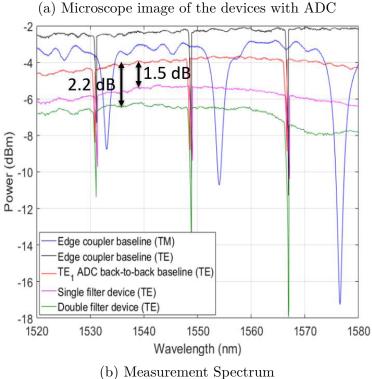

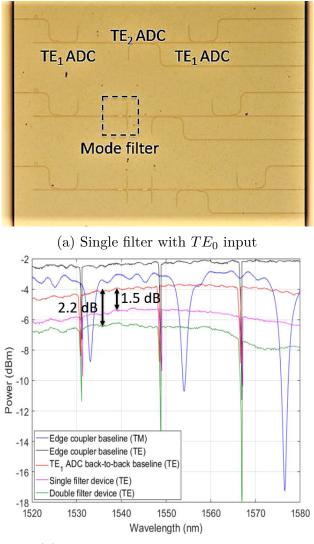

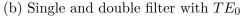

| 3.3 | a) Microscope image of devices using ADC for loss measurement of ADC b) Measurement results of filter device with ADC for both single filter and double filter device with $TE_1$ input. Figure reproduced from Dr. Min Teng's thesis with permission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52 |

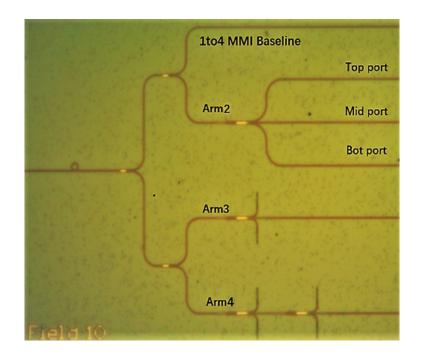

| 3.4 | Microscopic image of the measurement scheme for a $TE_0$ rejection mode filter<br>inside a cascaded MMI system. Top arm is the baseline for the MMI system.<br>Arm 1 & Arm 2 have single & double filters respectively. Figure reproduced<br>from Dr. Min Teng's PhD thesis with permission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53 |

| 3.5 | Measurement spectrum of a mode filter $(TE_0 \text{ rejection})$ a) single filter b)<br>single filter and double filter with $TE_0$ input. Figure is reproduced from Dr.<br>Min Teng's PhD thesis with permission.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54 |

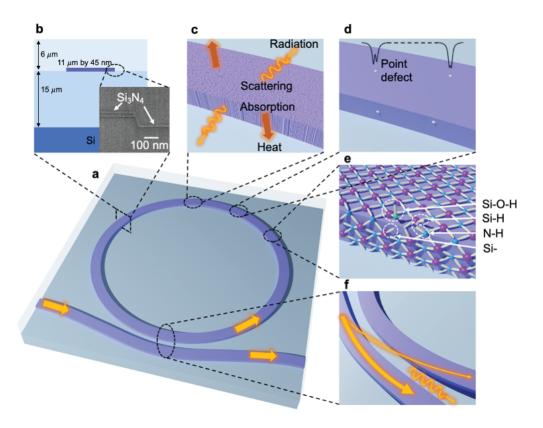

| 4.1 | Different kind of losses in Silicon Nitride microring resonators and their ori-<br>gins. The picture is taken from [65]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57 |

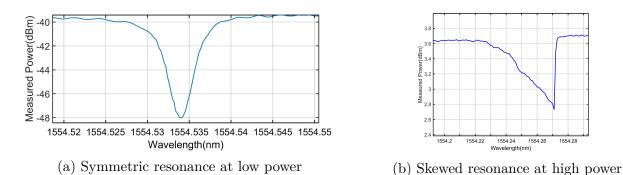

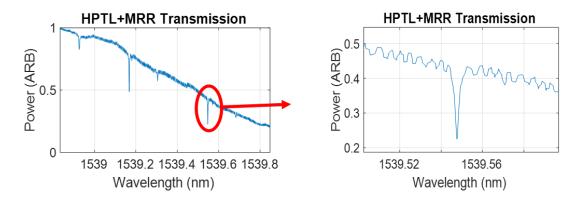

| 4.2  | Resonance skewing due to thermal self locking between the laser and the resonance                                                                                                                                                                                                                                                                                                                                                  |  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

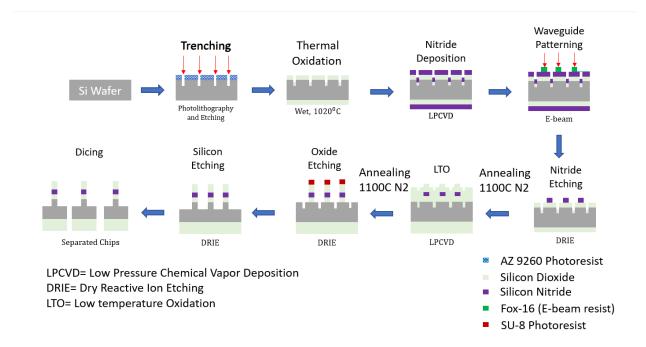

| 4.3  | Process steps during the fabrication of Silicon Nitride microring resonators                                                                                                                                                                                                                                                                                                                                                       |  |

| 4.4  | Vernier Dual comb scheme for the DARPA A-Phi project. Image courtesy:<br>Dr. Mohammed Al Alshaykh.                                                                                                                                                                                                                                                                                                                                 |  |

| 4.5  | Film thickness sensitivity for dispersive wave locations. Thanks to Cong Wang for the simulation.                                                                                                                                                                                                                                                                                                                                  |  |

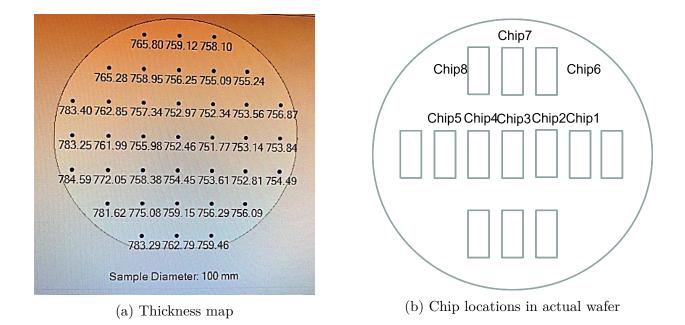

| 4.6  | Thickness mapping for Silicon Nitride films. a) Thickness measured by Filmetrics F40 tool at different points of the wafer b) Sample chip locations in the wafer, each chip's thickness can be read from the thickness map and change the design accordingly to compensate the variation.                                                                                                                                          |  |

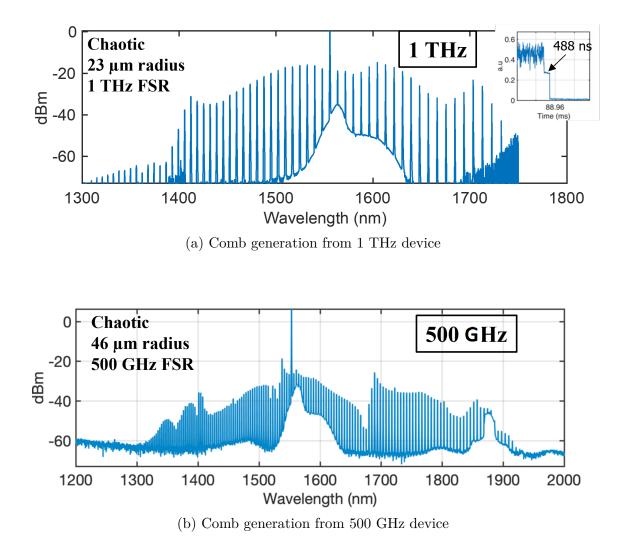

| 4.7  | Examples of Optical Frequency comb generation from our first few efforts in the DARPA project.                                                                                                                                                                                                                                                                                                                                     |  |

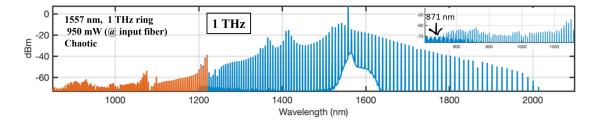

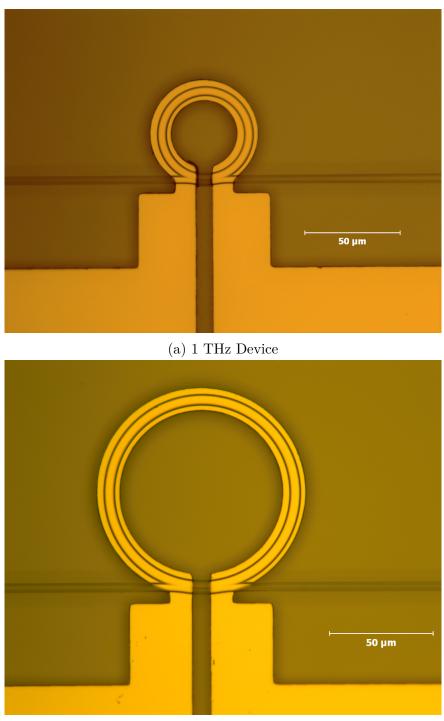

| 4.8  | Our first octave spanning chaotic comb from 1 THz design. The required power to get the octave spanning comb was about 950 mW. Two different OSAs were used to get this data. The Orange lines are the data from standard (visible/near-IR) OSA and the blue lines are the data from long-wavelength OSA.                                                                                                                          |  |

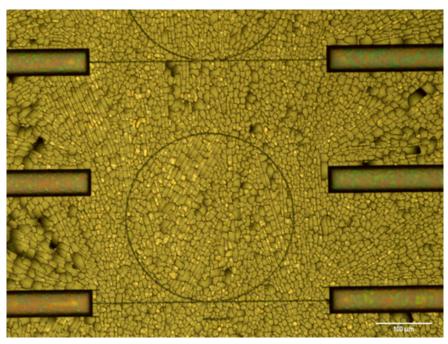

| 4.9  | Microscopic images of annealed samples at Yale university. The samples had $\sim 3 \ \mu m$ upper cladding on top. a) Sample annealed at 1200°C. The upper cladding completely cracked. b) Sample annealed at 1150°C. The upper cladding did not crack, but the device performance did not improve                                                                                                                                 |  |

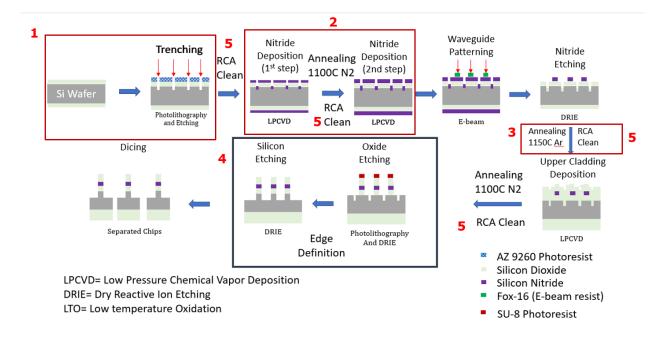

| 4.10 | Modified process steps for the fabrication of Silicon Nitride microring res-<br>onators. 1. Modified trenching process 2. Multi step Silicon Nitride film<br>deposition with added annealing and RCA cleaning step 3. Modified anneal-<br>ing step after Nitride etching and HSQ (E-beam resist) removal 4. Maskless<br>lithography process for edge definition 5. All the RCA cleanings to reduce<br>contamination and particles. |  |

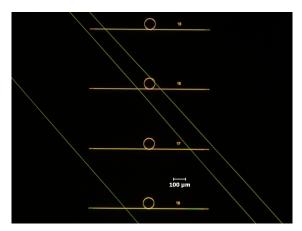

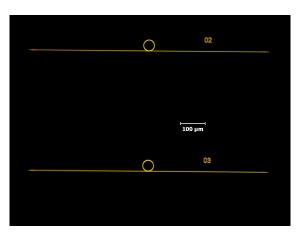

| 4.11 | Dark field microscopic picture of the wafer after e-beam writing a) all the devices went under the film cracks, so none of them would be good b) Some good devices that didn't fall under the film cracks. This reduced our fabrication yield by a huge amount.                                                                                                                                                                    |  |

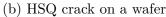

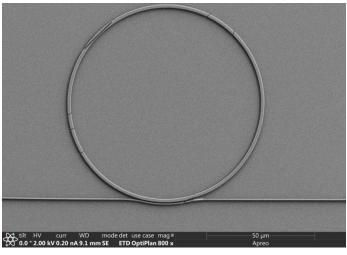

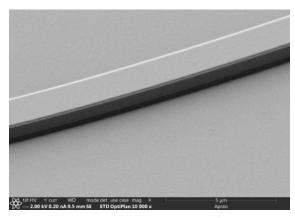

| 4.12 | HSQ cracks a) Cracks on a piece sample b) Cracks on a wafer c) SEM images of the device fabricated that had HSQ cracks.                                                                                                                                                                                                                                                                                                            |  |

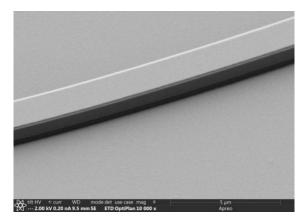

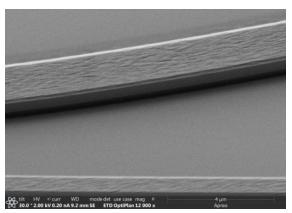

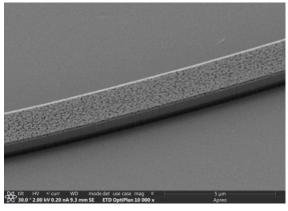

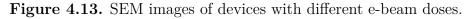

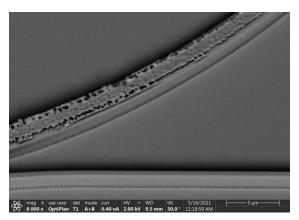

| 4.13 | SEM images of devices with different e-beam doses.                                                                                                                                                                                                                                                                                                                                                                                 |  |

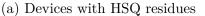

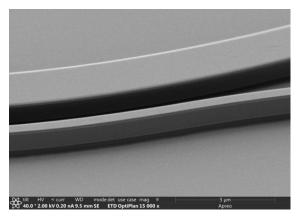

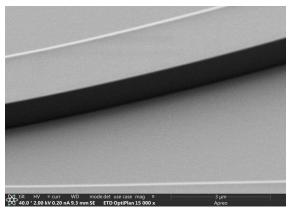

| 4.14 | SEM images of a device that has a) HSQ residues on top of the waveguide after BOE dip b) All the HSQ residues removed from device top.                                                                                                                                                                                                                                                                                             |  |

| 4.15 | SEM images of a) Top view of the device that shows all the residues are gone<br>and we have a smooth top surface b) Top and sidewall view that shows we<br>have very smooth sidewalls.                                                                                                                                                                                                                                                                      | 77                     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

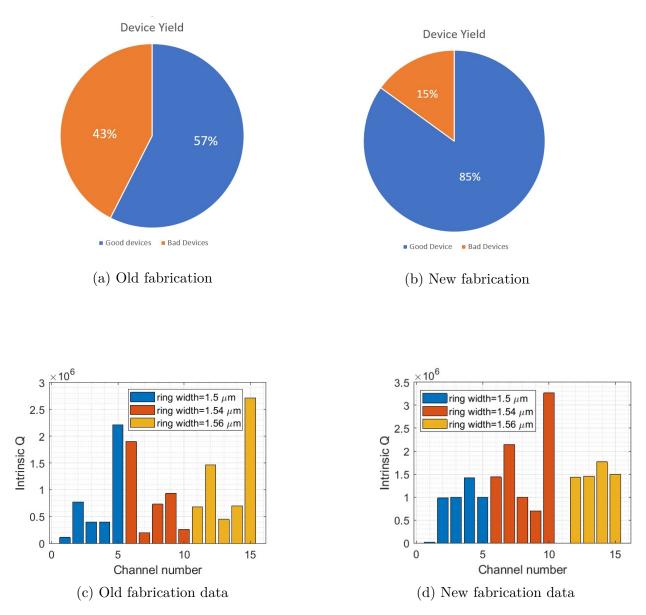

| 4.16 | Measurement statistics between the old fabrication and modified fabrication process. a) Percentage of working devices in our earlier fabrication without those modifications b) Percentage of working devices after those modifications in process c) Quality factors of some measured devices from our earlier fabrication d) Quality factors of similar devices from our new fabrication. Image and data collection courtesy: Saleha Fatema and Cong Wang | 78                     |

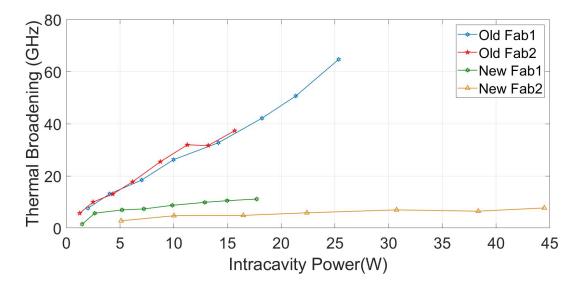

| 4.17 | Comparison of thermal broadening between two fabrication runs. In Old fab-<br>rication run we only had two annealing steps as shown in Fig 4.3. In the new<br>fabrication run we had three annealing steps and a few other improvements<br>as shown in Fig 4.10.                                                                                                                                                                                            | 80                     |

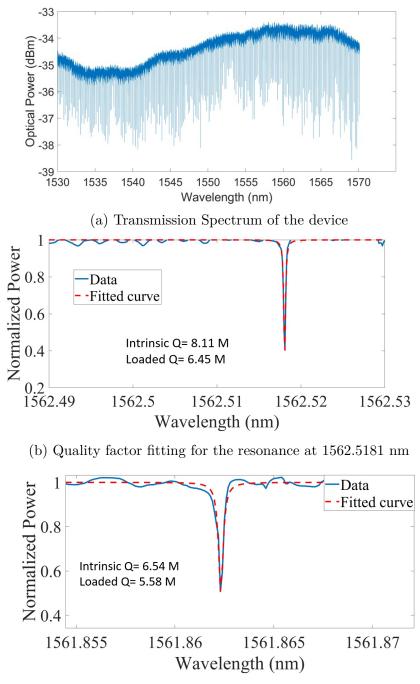

| 4.18 | Measurement data for a large microring resonator a) The transmission spectrum of the device b) Quality factor fitting for the resonance at 1562.5181 nm. The intrinsic quality factor is about 8.11 million with a loaded Q of 6.45 million. c) Quality factor fitting for the resonance at 1561.8623 nm. The intrinsic quality factor is about 6.54 million with a loaded Q of 5.58 million.                                                               | 81                     |

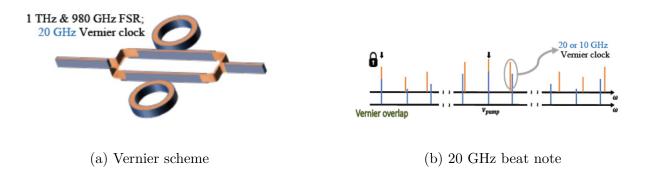

| 5.1  | Vernier clock scheme using two microring resonators with slightly different FSR. The figure is reproduced from [69].                                                                                                                                                                                                                                                                                                                                        | 84                     |

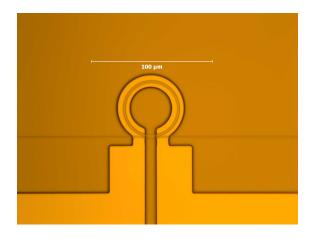

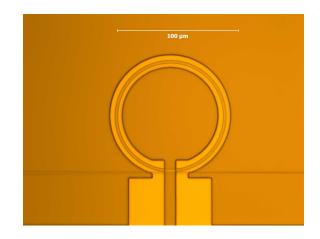

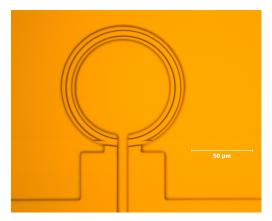

| 5.2  | Different kinds of microheaters for Silicon Nitride microresonators. a) Microheater covering most part of a full ring b) Microheater covering most part of a racetrack resonator c) Microheater covering half of a ring d) Zigzag shaped microheater on top of a dual-ring microresonator [39].                                                                                                                                                             | 85                     |

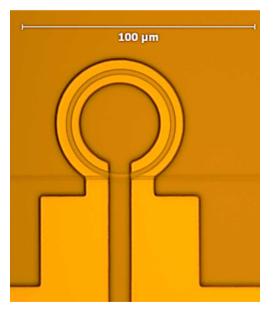

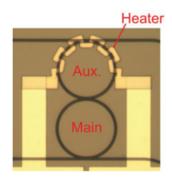

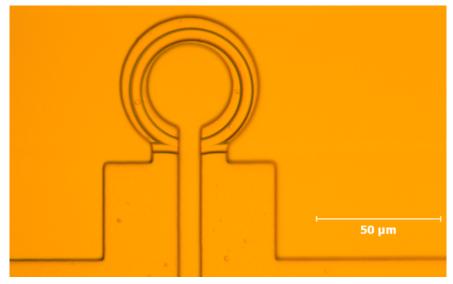

| 5.3  | Location of heater fabrication process in the complete fabrication flow. It<br>is usually done after the final annealing step and before the edge definition<br>lithography step in the complete fabrication flow.                                                                                                                                                                                                                                          | 86                     |

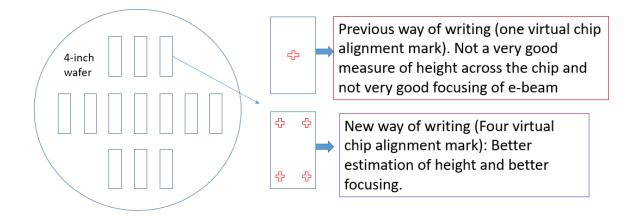

| 5.4  | Misalignment due to e-beam writing issue                                                                                                                                                                                                                                                                                                                                                                                                                    | 88                     |

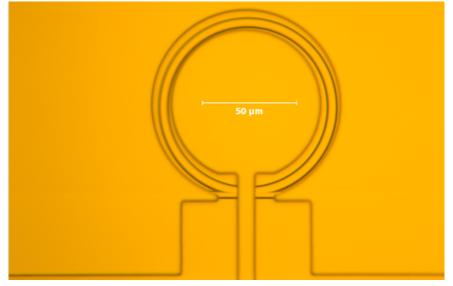

| 5.5  | Modification of e-beam alignment marks for better alignment and writing                                                                                                                                                                                                                                                                                                                                                                                     | 89                     |

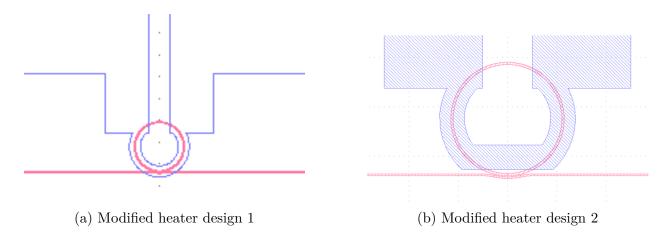

| 5.6  | Modified heater designs for better stability and thermal efficiency                                                                                                                                                                                                                                                                                                                                                                                         | 89                     |

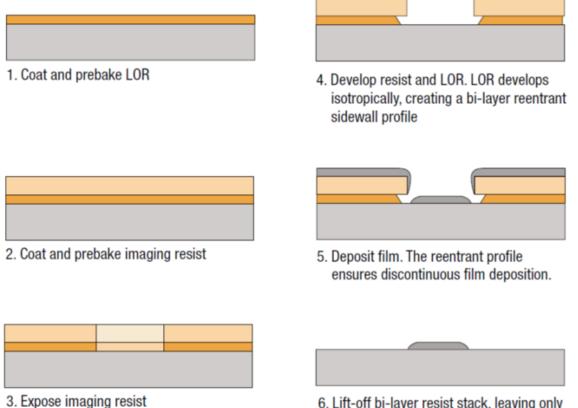

| 5.7  | Process steps of microheater fabrication with LOR and how it helps in our liftoff process. Image courtesy: https://engineering.tufts.edu/microfab/documer LOR.pdf                                                                                                                                                                                                                                                                                           | nts/SOP_Liftoff-<br>90 |

| 5.8  | Microscopic images of micoheaters fabricated with Lift Off Resist                                                                                                                                                                                                                                                                                                                                                                                           | 91                     |

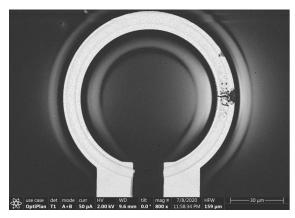

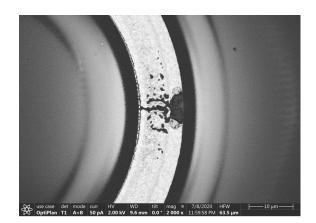

| 5.9  | SEM images of burned microheaters                                                                                                                                                                                                                                                                                                                                                                                                                           | 95                     |

| 5.10 | Short term (10 mins) stability test for Ti/Pt microheaters (Image courtesy:<br>Cong Wang)                                                                                                                                                                                                                                                                                                                                                                   | 97                     |

| 5.11 | Long term (1 hour) stability test for Ti/Pt microheaters (Image courtesy:<br>Cong Wang)                                                                                                                                                                                                                                                       | 98  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

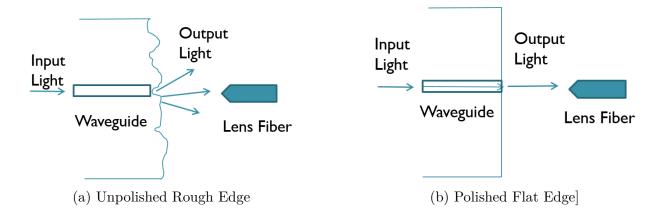

| 6.1  | The problem with a rough edge at the end of photonic chips (a) An unpolished rough edge where the light scatters away while coming out (b) A polished flat edge with low or no scattering                                                                                                                                                     | 101 |

| 6.2  | Logitech Orbis Chemical Mechanical Polisher (a) The CMP machine (b) The<br>Polishing pad and holder inside the CMP machine. The photos are taken<br>from https://logitech.uk.com/product/orbis-cmp-solution/                                                                                                                                  | 102 |

| 6.3  | The difference between surface polishing and edge polishing. (a) A Polished surface, which has a large polishing area (b) A polished edge, which has a smaller area to polish                                                                                                                                                                 | 102 |

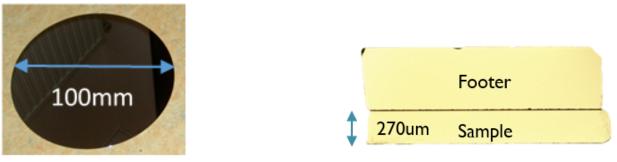

| 6.4  | Importance of Footer (Small Silicon chuck on top of the sample)                                                                                                                                                                                                                                                                               | 104 |

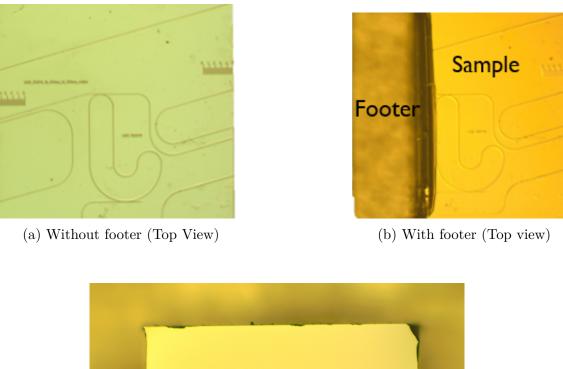

| 6.5  | Chemicals and materials used for the edge polishing process                                                                                                                                                                                                                                                                                   | 105 |

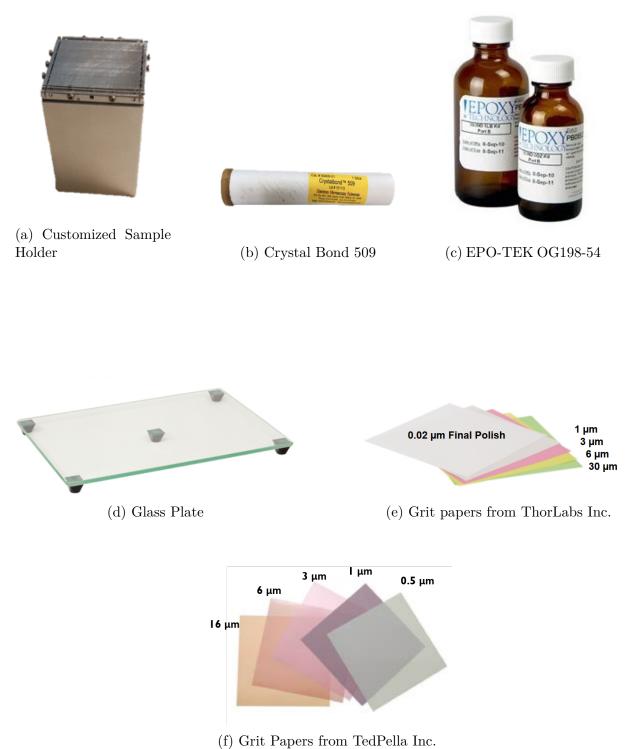

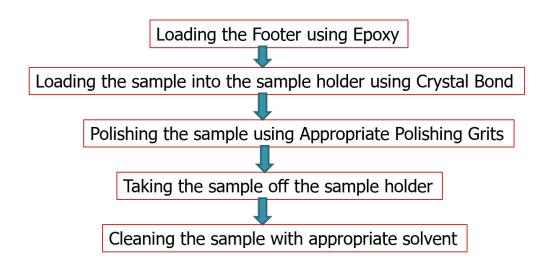

| 6.6  | All the major steps of the edge polishing process                                                                                                                                                                                                                                                                                             | 106 |

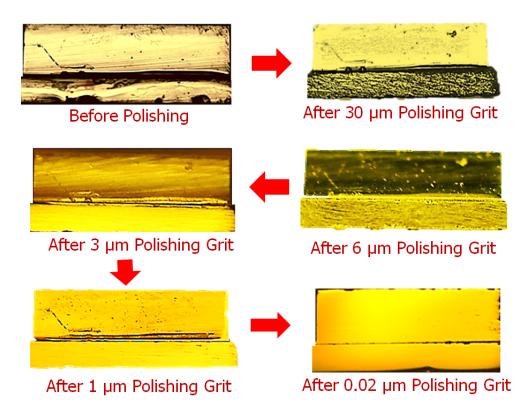

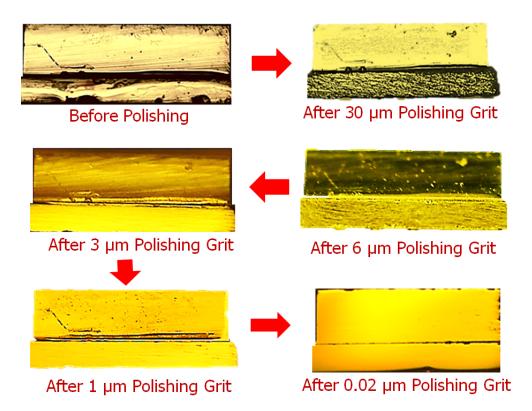

| 6.7  | The effect of polishing on the edge. Starting from $30 \ \mu m$ grit and going down to 20nm grit. Gradual improvement is noticeable as grit size goes from coarse grits to finer grits                                                                                                                                                        | 108 |

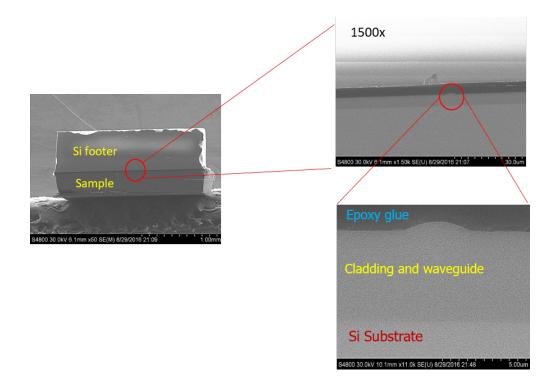

| 6.8  | The SEM images of the polished chips                                                                                                                                                                                                                                                                                                          | 109 |

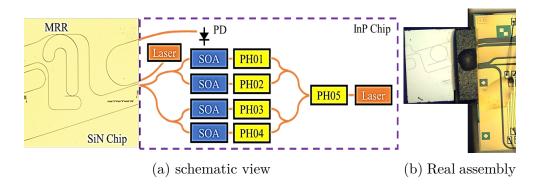

| 6.9  | The heterogeneous integration of SiN-InP chip a) Schematic view of the inte-<br>gration b) Real assembly. This figure is taken from [93]                                                                                                                                                                                                      | 11( |

| 6.10 | The short transmission spectrum of the bonded assembly $[93]$                                                                                                                                                                                                                                                                                 | 111 |

| A.1  | Different deposition tools (a) Horizontal furnaces for LPCVD of thin films (b)<br>Thermal evaporator for metal deposition                                                                                                                                                                                                                     | 124 |

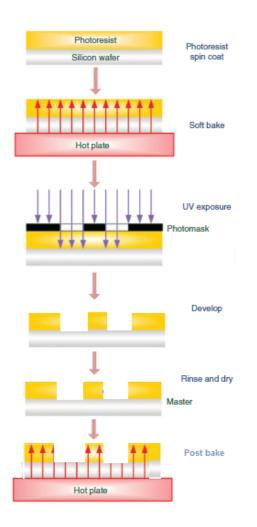

| A.2  | Different steps of the photolithography process.                                                                                                                                                                                                                                                                                              | 125 |

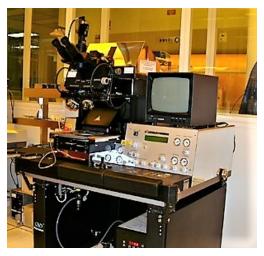

| A.3  | Different tools used in the photolithography process (a) Spin coater by which<br>a wafer surface is coated with photoresist (b) SUSS mjb3 optical aligner sys-<br>tem, by which sample or wafer is aligned and exposed (c) SUSS MA6 optical<br>aligner, an improved version of mjb3, but performs the same task of alignment<br>and exposure. | 12  |

| A.4  | Different tools for performing etching process. (a) STS ASE Silicon etcher<br>(b) Panasonic E620 etcher                                                                                                                                                                                                                                       | 128 |

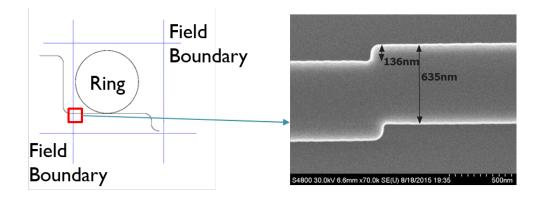

| A.5  | An example of stitching error while writing a waveguide that crosses two field lines between adjacent fields in the e-beam system.                                                                                                                                                                                                            | 13( |

| B.1  | (a) Bad Epoxy control, epoxy spread over the sample (b) Good epoxy control with good alignment                                                                                                                                                                                                                                                | 132 |

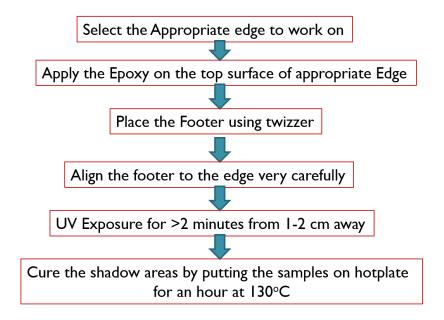

| B.2  | The flowchart of footer loading process for Polishing the sample                                                                                                                                                                                                                                                                              | 133 |

| B.3 | 3 Sample holder and sample loading process                                                                                                                                             |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

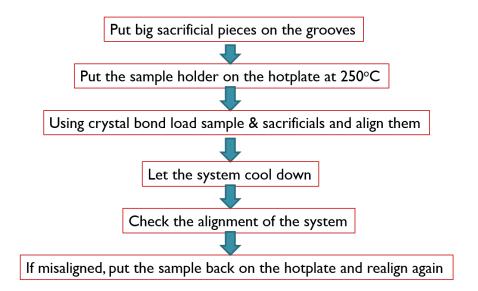

| B.4 | The flowchart of all the steps during sample loading process                                                                                                                           | 135 |

| B.5 | The effect of polishing on the edge. Starting from $30 \ \mu m$ grit and going down to 20nm grit. Gradual improvement is noticeable as grit size goes from coarse grits to finer grits | 137 |

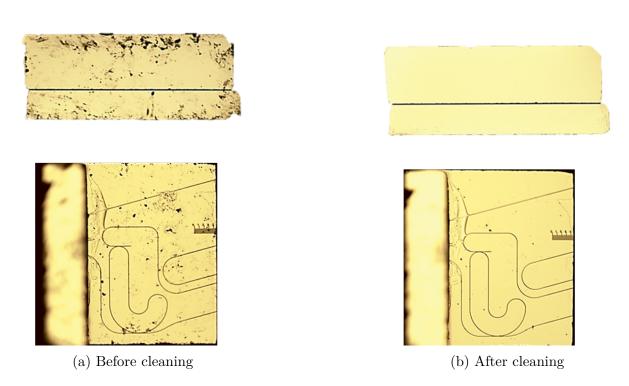

| B.6 | Sample cleaning after the polishing process                                                                                                                                            | 139 |

| C.1 | Photolithography steps in microheater fabrication                                                                                                                                      | 140 |

| C.2 | The photolithography tools available for microheater fabrication: a) Tra-<br>ditional photolithography tool SUSS MA6 b) Heidelberg Maskless Aligner<br>MLA150.                         | 141 |

| C.3 | After Heidelberg lithography and good alignment of heater layout with respect of our ring resonators.                                                                                  | 143 |

| C.4 | Microscopic images of the devices after metal deposition                                                                                                                               | 144 |

| C.5 | Microscopic images of the devices after liftoff process                                                                                                                                | 145 |

## LIST OF SYMBOLS

- c Velocity of Light

- $v_g$  Group Velocity

- $\epsilon$  Electric Permeability

- $\mu$  Magnetic Permittivity

- $\omega$  Angular Frequency

- $\lambda$  Wavelength of Light

- $\beta$  Propagation Constant

- $\psi$  Spectral Phase

- $\beta_2$  Second Order Dispersion

- D Dispersion Coefficient

- T Transmittance

- $n_2$  Kerr Non-linearity

- $f_{CEO}$  Carrier Envelope Offset Frequency

- $\kappa$  Coupling Coefficient

- Q Quality Factor

- $n_g$  Group Refractive Index

## ABBREVIATIONS

| SOI | Silicon | on Insulator |

|-----|---------|--------------|

|     |         |              |

| FSR      | Free Spectral Range                |

|----------|------------------------------------|

| TE       | Transverse Electric                |

| TM       | Transverse Magnetic                |

| E-skid   | Extreme Skin Depth                 |

| AMM      | Anisotropic MetaMaterial           |

| TIR      | Total Internal Reflection          |

| IPA      | Isopropyl Alcohol                  |

| DI water | De-Ionized water                   |

| BOE      | Buffered Oxide Etch                |

| HSQ      | Hydrogen silsesquioxane            |

| RPM      | Revolution per Minute              |

| TMAH     | Tetramethylammonium hydroxide      |

| RIE      | Reactive Ion Etching               |

| SEM      | Scanning Electron Microscope       |

| MMI      | Multi Mode Interference            |

| WDM      | Wavelength Division Multiplexing   |

| PDM      | Polarization Division Multiplexing |

| MDM      | Mode Division Multiplexing         |

| ADC      | Asymmetric Directional Coupler     |

| HSQ      | Hydrogen silsesquioxane            |

| DKS      | Dissipative Kerr Soliton           |

## ABSTRACT

Silicon photonics has become one of the leading candidates for the next generation optical communication platform. In addition to being an inexpensive material and compatible with Complementary metal-oxide-semiconductor (CMOS) manufacturing, silicon exhibits low absorption at optical telecommunication bands. However, high propagation loss and poor light confinement in narrow Si waveguides have limited high-density optical integration. In this work, we show the fabrication and characterization of a novel type of devices named E-skid devices that can reduce the skin depth and suppress the large spatial content of evanescent light. These devices use artificial anisotropic dielectric metamaterial to suppress the evanescent waves. Beside E-skid devices, we also discuss the fabrication and experimental characterization of mode filters using Silicon on Insulator that can block the fundamental  $TE_0$  and allow the higher order modes to pass through using Multi Mode Interference. In this work, the mode is filtered using radiation, not by reflection.

Beside Silicon, Silicon Nitride has also gained much interest because of its low loss, smaller nonlinear absorption and higher Kerr effect. Silicon Nitride waveguides have widely been used for lots of applications specially the optical frequency comb generation. One special case of coherent optical frequency comb is Soliton in which case the non-linearity and dispersion cancel each other's effect and keep the pulse without distortion. In this work, we described the Silicon Nitride fabrication process and did a comparative analysis with other research groups who fabricates similar devices. We tried to improve our process by inserting a few additional steps in our fabrication process. We also investigated our process step by step and found out reasons for our low quality factor and low yield. We found a few factors that might be responsible for the low quality factor and addressed them. We fabricated real devices using our modified process and saw improvement in quality factors, yield and thermal performance of the devices.

Finally, we describe an edge polishing method for Silicon Nitride microring resonator devices, which we developed from scratch and we can polish edges down to sub-micron level.

Thus, the edges become optically flat and it allowed us to do heterogeneous integration with an Indium Phosphide chip. This paves away for some exciting opportunities like on-chip frequency comb generation.

## 1. INTRODUCTION

Silicon photonics has become one of the leading candidates for the next generation optical communication platform which uses Silicon as an optical medium to guide an optical mode. The fabrication cost of Silicon photonics has also been affordable due to the massive development in CMOS industry as they share the same material. From optical perspective, Silicon has the advantage of having low absorption in telecommunication C-band (1530nm-1565nm). Therefore, Silicon has been used to develop on-chip laser sources [1], optical waveguides [2], Electro-optic modulators [3], integrated photodetectors [4], on-chip Mode Division Multiplexing [5] etc. However, the demand for increasing density and miniaturization of these components has led to technological challenges in their manufacturing and operation. Also, Silicon suffers from two-photon absorption and subsequent free-carrier injection [6] which limit the nonlinear efficiency of the medium. Therefore, for nonlinear applications such as Kerr Frequency Comb generation [7], Silicon Nitride is preferred, which has a lower loss, greater thermal stability and no Two Photon Absorption (TPA) process.

The first part of this report contain works that is based on Silicon-on-Insulator (SOI) for some light confinement devices [8] and mode filters using Multi Mode Interference (MMI) which are described in Chapter 2 and 3 respectively. The rest of the chapters (chapter 4, 5 and 6) are based on Silicon Nitride devices, more specifically Silicon Nitride microring resonators that are designed for the purpose of Optical frequency comb generation. Before going into the details, we will focus on some basic terminologies first in the following section.

#### 1.1 Light Confinement Techniques in Photonic Waveguides

#### 1.1.1 Crosstalk

Crosstalk can be defined as the interference between the signals that are propagating on various line or channel in the same system. It is a phenomenon by which the light transmitted in one photonic waveguide or channel of a system creates an undesired effect in another waveguide or channel. It results from coupling of energy from electromagnetic fields generated by neighboring lines and is highly undesirable as it increases the loss for that line or channel.

Miniaturization of photonic chips and dense integration has always been a challenge due to the fact that as the size goes down, it becomes harder to confine the light within the structure. Also, the large spatial extent of evanescent light waves during coupling results in high crosstalk and high radiation loss [9].

#### 1.1.2 Light Confinement Techniques

One of the ways to confine lights in photonic devices is to use plasmonic structures [10], [11]. They can strongly reduce the bending loss and crosstalk because of the sub-diffraction nature of the coupling of light [12]. But the inherent large ohmic loss of metals limits their use for photonic integration [13], [14].

All dielectric structures has been considered a potential solution to that problem and a few all dielectric structures were considered in recent years to make the miniaturization possible [15]–[17]. Fig.1.1 shows a few different classes of dielectric waveguides that were used to confine light in photonic chips.

Fig 1.1a illustrates the most common type of waveguide for guiding light in SOI chip-Strip Waveguides. In this type of waveguide usually the higher index Silicon channel is surrounded by lower index Silicon Dioxide.Due to the high contrast of the refractive index between the core and the cladding, light is usually confined into the core waveguide because of the total internal reflection [9]. The problem with these kind of structures is that when we try to reduce the core size, the mode starts to increase and that creates a stumbling block in its miniaturization [18].

Fig 1.1b illustrates Photonic Crystal Waveguides that can confine light inside a line defect using Bragg Reflection[19]. These waveguides can work very efficiently with sharp bends[20] overcoming the radiation loss at sharp bends. However, the integration density for these kind of waveguides are limited due to the fact that the periodicity of Bragg reflector is on the order of the wavelength. Also, these kind of waveguides cannot be perturbed by any other nearby waveguides[21].

Fig 1.1c illustrates the slot waveguides, which are an opposite arrangement compared to the strip waveguide. In this kind of waveguide, a sub-wavelength low index gap is surrounded by high index dielectric rods [22]. For this kind of arrangements, the electric field peaks inside the gap which leads to light confinement. But at the same time, it causes skindepth expansion in the cladding, which results in crosstalk between adjacent waveguides and radiation loss at sharp bends making dense integration and miniaturization problematic.

Fig 1.1d illustrates the E-skid waveguides, which is fundamentally different from the other approaches and uses all-dielectric anisotropic metmaterials. The confinement of light in this kind of waveguides is based on the photonic skin-depth engineering of evanescent waves in the cladding. This is possible due to an additional degree of freedom in Total Internal Reflection (TIR) which is described in [18], [23]. The relaxed condition enables the control of evanescent wave decay which in turn reduces crosstalk and bending loss.

In E-skid devices, the anisotropic metamaterials is used as cladding and the dielectric waveguides are fabricated on a monolithic Silicon-On-Insulator (SOI) platform. As a consequence of decay control, the crosstalk is reduced down to -30dB in the photonic circuit [8].

#### 1.2 Microring resonator

An optical microring resonator is a set of waveguides which consists of one or more input or output bus waveguides, through which the power is sent or received and one or more closed waveguides in which power is coupled and circulated. The closed waveguide can be of any shape, but the most common shape is a circular ring. A microring resonator usually has two ports, an input port, through which the light is sent in and a through port by which light comes out as shown in Fig 1.2a.

When there is through port only, there is only one waveguide and the input light couples inside the microring via the coupling coefficient  $\kappa$ , circulates around the cavity. We only have one coupling region in this case. But occasionally we have another port, which is called drop port.

When we have drop port in design that usually couples power from the field that develops inside the microring. So a separate waveguide takes power from the ring after the ring takes power from the input bus waveguide as shown in Fig. 1.2b. In this case we have two coupling regions. The input light couples inside the microring via the coupling co-efficient  $\kappa_1$  and the light is again coupled to the drop waveguide from the ring via another coupling co-efficient  $\kappa_2$  and reaches the drop port.

When we send some light through the input waveguide of the microring resonator, some part of light is coupled to microring depending of the wavelength of the light and some of the design parameters of the microring, the rest of the light is transmitted to the output port via the input bus waveguide. The coupled light circulates inside the cavity by internal reflection and suffers some losses due to sidewall roughness, intrinsic absorption of waveguide material and scattering losses due to bending at the edges.

On the other hand as the light completes one round trip, it interferes with the incoming light constructively and thus the light intensity inside the microring is build up. The coupling of light critically depends on the gap between the ring and the input bus waveguide, the effective coupling length along which the coupling of light takes place and the refractive index of the medium between the two waveguides.

(b) Microring with both through port and drop port

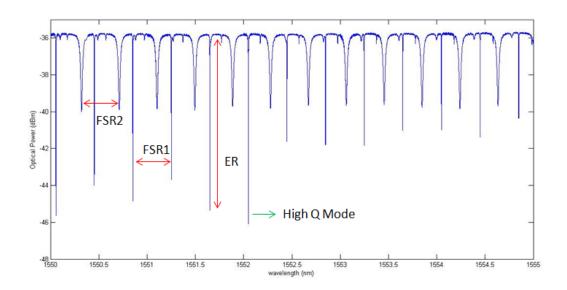

Figure 1.2. The basic structure of a microring resonator a) with through port only b) with both through and drop port

#### **Transmission Spectrum**

The transmission spectrum is obtained by plotting the transmittance for the system. Transmittance is defined as the ratio of the transmitted power to the input power. Let us consider a microring resonator without the drop port as shown in Fig. 1.2a. It has through port only and through the input port we send some light from a laser source and receive the output light from the through port. Transmission spectrum can be obtained by measuring transmittance. The transmittance for such structures can be written as [24]:

$$T = \frac{(\lambda - \lambda_0)^2 + (\frac{v_g \lambda^2}{8\pi^2 Rc})(\kappa_c^2 - \kappa_i^2)^2}{(\lambda - \lambda_0)^2 + (\frac{v_g \lambda^2}{8\pi^2 Rc})(\kappa_c^2 + \kappa_i^2)^2}$$

(1.1)

Where,  $\lambda_0$ =resonant wavelength of the microring, $\kappa_c^2$ = fraction of power losses due to coupling of power to the ring from bus waveguide,  $\kappa_i^2$ =fraction of intrinsic power losses. A sample transmission spectrum is shown in Fig. 1.3.

Figure 1.3. A sample Transmission Spectrum for a Microring Resonator. Each dip corresponds to a resonance frequency that the microring resonator can support

Some important terms related to Transmission Spectrum are Free Spectral range (FSR) and Extinction Ratio (ER).

#### Free Spectral Range (FSR)

Free Spectral Range (FSR) of an optical microresonator is defined as the spacing in frequency or wavelength between two maxima of the dropped power or minima of the through power. FSR can be obtained from transmission spectrum very easily. It is just the difference between two successive resonance frequencies or wavelengths for the same mode family.FSR for different mode families are different. If a microresonator can support multiple modes, then the fundamental mode usually has the highest FSR. Fig 1.3 shows a sample transmission spectrum and FSRs for two different mode families are termed as  $FSR_1$  and  $FSR_2$ . Mathematically, FSR can be defined (in frequency) as [25]:

$$FSR_f = \Delta f_{FSR} = \frac{c}{n_g L} \tag{1.2}$$

Where, c= Velocity of light,  $n_g$ = Group index of the cavity material, L=Length of the cavity. FSR is also the inverse of round-trip time. If the round-trip time for the cavity is  $T_R$ , then:

$$T_R = \frac{1}{FSR_f} = \frac{n_g L}{c} \tag{1.3}$$

### Extinction Ratio (ER)

Extinction ratio (ER) is fundamentally defined as the ratio of two optical signals generated by an optical source. Mathematically, we can express it as-

$$ER = \frac{P_2}{P_1} \tag{1.4}$$

Where,  $P_2$  is the received power and  $P_1$  is the transmitted power. Usually it is expressed in dB units, in which case we write it as:

$$ER = -10\log\frac{P_2}{P_1}(dB) \tag{1.5}$$

For microring resonator, Extinction Ratio (ER) can be defined as the ratio between transmitted power and input power. It can simply be obtained from the transmission spectrum. The difference between the maximum and minimum point in a particular resonance gives us the Extinction Ratio. For example if we see Fig 1.3, the Extinction Ratio for the marked resonance is around 10.5 dB. Extinction Ratio is also important because if ER is too small, then we cannot probably use that for comb generation. Thus Extinction Ratio plays a vital role in the application of microring resonator.

### Quality Factor (Q)

Quality factor or Q factor is a dimensionless parameter that is used for defining the strength of damping of an oscillator. It was initially developed for electronic circuits, but later became very commonly used for photonic cavities or resonators. Quality factors can be defined by two ways:

From oscillator point of view, Q factor is approximately defined as the ratio of the initial energy stored in the resonator to the energy lost in one radian of the cycle of oscillation [26]. Alternatively, Quality Factor can be defined as the ratio of a resonator's resonant frequency to its the full width at half-maximum (FWHM) bandwidth when subject to an oscillating driving force. High Q corresponds to a lower rate of energy loss and low damping. Usually that corresponds to low loss in microring resonators. For microring resonators, Quality factor can be defined as:

$$Q = \frac{\lambda_0}{\Delta\lambda} = \frac{\Delta f}{f_0} \tag{1.6}$$

where,  $\lambda_0$  is the resonant wavelength,  $f_0$  is the resonant frequency,  $\Delta\lambda$  and  $\Delta f$  is the Full Width at Half Maximum (FWHM).

#### Dispersion

The word dispersion generally means the action or process of distributing things over a wide area. In Optics the term dispersion results in similar type of thing- spreading of the pulse. Dispersion causes different frequency components to travel at different velocities, resulting in the pulse broadening. When the pulse is broadened it actually can cause a lot of unwanted situations including distortion of data. Dispersion is a very important parameter for microring resonator. The comb generation process depends on the type of dispersion. Also, it is crucial as it limits the maximum achievable comb bandwidth [27].

In fiber optics, dispersion is usually described in terms of dispersion co-efficient (D) which can be expressed as [28]:

$$D = \frac{\partial \beta_1}{\partial \lambda} = -\frac{2\pi c \beta_2}{\lambda^2} \tag{1.7}$$

where,  $\beta_1$  is the first order dispersion, which is the inverse of group velocity  $v_g$  and it can be expressed as [28]:

$$\beta_1 = \frac{\partial \beta}{\partial \omega}|_{\omega = \omega_0} = \frac{1}{v_g} \tag{1.8}$$

The term  $\beta_2 = \frac{\partial^2 \beta}{\partial \omega^2}$  is called Group Velocity Dispersion (GVD). The unit of D is ps/nmkm and it actually gives the group delay difference of two optical pulses after propagating certain distance in the optical fiber at certain wavelength. Depending on the sign of D we define two distinct type of dispersion:

1) When D>0, the dispersion is called Anomalous Dispersion.

2) When D < 0, the dispersion is called Normal Dispersion.

It is worth mentioning that the frequency comb generation principle is entirely different for these two type of dispersion regimes which is explained later.

#### **1.3 Optical Frequency Comb**

Optical Frequency Combs are evenly spaced periodic spectral lines, which are discrete and the spacing between individual comb lines are constant along the whole spectrum. Thus an optical frequency comb can be used as an optical ruler because if we know the comb frequency we can find any unknown frequency by beating that with the optical frequency comb. Optical frequency combs have been useful in many applications such as comb spectroscopy [29], molecular fingerprinting [30], astronomical calibration [31], arbitrary waveform generation [32] etc.

Optical frequency combs can be generated in many ways, but the most common method is using a mode-locked laser with stable frequency and repetition rate. Fig. 1.4 shows an example of mode locked frequency comb [28]:

In general, the frequencies of individual comb lines for a frequency comb can be expressed as [28]:

$$f_m = m f_{rep} + f_{CEO} \tag{1.9}$$

where,  $f_{rep} = \frac{1}{T}$  is the repetition rate of the laser, T is the period of the optical pulse as shown in Fig. 1.4b and  $f_{CEO}$  is the carrier envelope offset frequency $=\frac{\delta\omega}{2\pi}$ . The carrier envelope offset occurs from the phase slip due to the carrier phase velocity  $v_p$  being faster than the envelope group velocity  $v_g$ . The difference in those two velocities arise from the group velocity dispersion inside the cavity. One useful thing about microring resonator is that the FSR can be controlled very easily. Also microring resonator allow us to reduce the size and

**Figure 1.4.** Mode-locked frequency comb a) The offset frequency  $\delta \omega$  is shown b) Pulse to pulse phase shift  $\Delta \phi_{CE}$  is shown. The picture is taken from [28]

can be implemented in chip level. So, for obtaining high repetition rate combs microring resonators have become very popular recently.

The optical frequency comb in microring resonators are generated by a parametric frequency conversion which is based on the Four Wave Mixing (FWM) process. The parametric conversion must follow both the energy and the momentum conservation law. In this process two pump photons ( $\omega_p$ ) are absorbed at sufficient power and two sidebands are generated as [33]:

$$2\omega_p = \omega_s + \omega_i \tag{1.10}$$

(a) A broadband Optical Frequency comb

(b) Degenerate & non-degenerate FWM

Figure 1.5. An example of Optical Frequency comb generated from microresonator via the parametric frequency conversion process. Fig a) shows the broadband frequency comb and Fig. b) shows the difference between degenerate and non-degenerate FWM process. The figure is taken from [7].

where  $\omega_s = \omega_p + \Delta \omega$  and  $\omega_i = \omega_p - \Delta \omega$  are generated sidebands which must be equidistant to maintain energy and momentum conservation law. Now this process continues and the whole frequency comb is formed. If two pump photons generate sidebands, they are usually called degenerate FWM. When one photon from pump interacts with one photon from nearby sidebands and create two new sidebands, then it is called non-degenerate FWM. An example of frequency comb generated from microring resonator is shown in Fig 1.5.

### Solitons

As mentioned in the previous subsection, the comb initiation process inside the microring resonator is created by an interaction between Kerr nonlinearity and group velocity dispersion, which is called modulational instability. Anomalous dispersion regime inherently supports modulational instability, so frequency comb generation in anomalous dispersion regime has been very popular and widely investigated [7], [34]–[36]. On the other hand, Kerr frequency comb generation in normal dispersion was initially thought to be impossible because of the lack of modulational instability. Later, it has been found that the mode coupling between adjacent mode families can generate modulational instability in normal dispersion regime and hence Kerr frequency comb generation in normal dispersion regime is possible [37], [38]. However, the mode interaction in normal dispersion regime was based on accidental degeneracies between spatial modes and hence thermally controlled mode interaction based frequency comb generation in normal dispersion regime was demonstrated later [39].

A critical issue for most of the application of the comb generation is the requirement of high temporal coherence. In anomalous dispersion regime, coherence can be obtained by soliton mode-locking [40]. A similar kind of route but with a different terminology and physics leads to coherence in normal dispersion regime through dark-pulse mode-locking [41]. The coherence in normal dispersion regime is usually repeatable and dark-pulse number is deterministic [41]. On the other hand, anomalous dispersion regime exhibits stochastic soliton number and the soliton number in most of the cases are greater than 1 [42], [43]. In most of the applications, single soliton is preferred because it has a smooth spectra with single Free Spectral Range (FSR) and greater coherence. The frequency comb spectrum with multi (two) soliton and single soliton are shown in Fig 1.6 [40].

In general, Dissipative Kerr solitons (DKS) generation requires the balance between the loss and gain in an active media, along with the balance between nonlinearity and dispersion. Despite the similarity between the DKS formation and soliton mode-locking in femtosecond lasers, DKS does not require additional saturable absorbers to stabilize them. Also in DKS, the pump laser frequency is a part of the soliton spectrum unlike the fiber soliton which does not require a continuous pump. The external coherent pump provides a central control parameter of the soliton and in addition constitutes one of the comb lines—which has no counterpart in conventional mode-locked lasers [44].

Figure 1.6. Frequency comb generation spectrum with (a) Multiple (two) soliton (b) Single soliton. Single soliton spectrum exhibits smoother  $sech^2$  profile. Figures are reproduced from [40].

#### 1.4 Organization of the report

In chapter 2, we will discuss about E-skid devices that utilizes all dielectric metamaterial structures that reduce the decay length of evanescent light. We also discuss the fabrication details of such devices, the crosstalk and the propagation loss measurement. Low crosstalk and propagation loss make these devices suitable for miniaturization and dense integration.

In chapter 3, we will discuss the fabrication and measurement of some mode filters using Multi Mode Interference (MMI) intended for on-chip Mode Division Multiplexing (MDM). The filters can effectively filter out the fundamental  $TE_O$  mode and allow the higher  $TE_1$ mode to pass be means of radiation.

In Chapter 4, we will discuss the fabrication process of Silicon Nitride microring resonators and all the improvements that we incorporated to the fabrication process after doing a comparative analysis with other groups. We will discuss some of our investigation into our process and some issues that might be responsible for our low Quality factors. Finally we show some characterization results of some devices that were fabricated with our modified process.

In chapter 5, we will discuss the microheater fabrication process. We will show how we explored different materials and combinations to improve our microheater performance and how we ended up successfully fabricating what was needed for one of our projects.

In Chapter 6, we will discuss about the edge polishing process that we developed from the scratch. This process make the edges of our chips optically flat which allows heterogeneous integration paving ways for on-chip frequency comb generation.

Finally in the summary chapter, we summarized all the works.

## 2. FABRICATION AND LOSS CHARACTERIZATION OF E-SKID DEVICES

## 2.1 Motivation and Goal

Large spatial extent of evanescent light waves generated during nanoscale light confinement has always been a major stumbling roadblock to miniaturization. In this chapter, we will discuss the fabrication and loss measurement of a very exciting and new type of devices that can improve the evanescent coupling of light [8]. The major idea of this work is the introduction of anisotropic metamaterials (AMM), which opens a new degree of freedom in total internal reflection (TIR) to reduce the decay length of evanescent waves. The devices were termed as E-skid devices because they work at the extreme skin depth condition of the Silicon. Relatively negligible propagation loss and low crosstalk of these devices makes them suitable for improved photonic integrated circuits.

## 2.2 Fabrication of E-skid Devices

The cross section and the top view of the E-skid devices along with design parameters are shown in Fig 2.1.

Figure 2.1. The design parameters of the E-skid devices. (a) Cross Section and (b) Top view. Here,  $w_0$ = Width of the Silicon waveguide= 450nm,  $h_0$ = Height of the Silicon waveguide= 220nm,  $\rho$ = Width of the AMM structures= 50nm,  $\Lambda$ = Spacing between AMM structures= 50nm, N=Number of parallel AMM structures in each side= 5. The cross section is reproduced from [8]

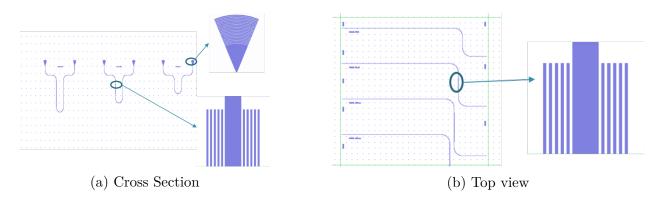

**Figure 2.2.** Two different layout schemes for E-skid Devices (a) Grating Coupling Scheme (b) Edge Coupling Scheme. For the final devices we proceed with grating coupling schemes because it needed less number of steps to complete the fabrication.

For the fabrication of E-skid devices, we tried both the grating coupling scheme and edge coupling scheme as shown in Fig 2.2. The lengths of AMM structure for loss measurement were same, just the coupling region and the main waveguide was different. Initially, we proceeded with the fabrication for both the layouts. But in the end, we decided to go ahead with the grating coupling scheme because it required less number of steps and less time to finish the fabrication process.

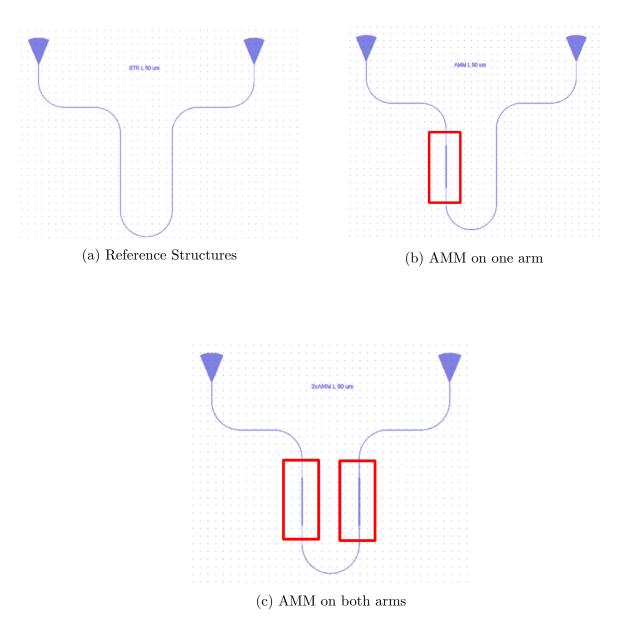

For the purpose of loss measurement, we made 3 different kind of layouts. One layout didn't have any AMM structures, which we called the reference devices (Strip waveguides) (Fig 2.3a). Another one had AMM structures in only one of the arms (Fig 2.3b) and the third one had AMM structures in both the arms (Fig 2.3c) for the grating coupler scheme. The lengths of the straight section of the e-skid and strip waveguides were varied from 0 to 1.8 mm. All the measurements were combined together to find an average value of loss for the E-skid devices, which is described in next subsection.

## 2.2.1 Fabrication Method