# TWO-DIMENSIONAL NANO-TRANSISTORS FOR STEEP-SLOPE DEVICES AND HARDWARE SECURITY

by

Peng Wu

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana December 2021

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

### Dr. Joerg Appenzeller, Chair

School of Electrical and Computer Engineering

### Dr. Zhihong Chen

School of Electrical and Computer Engineering

### Dr. Mark S. Lundstrom

School of Electrical and Computer Engineering

## Dr. Sumeet K. Gupta

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitri Peroulis

## 献给我挚爱的父母

To my beloved parents

吴英彪和姚润芬

Yingbiao Wu & Runfen Yao

### ACKNOWLEDGMENTS

First of all, I would like to express my sincere gratitude to my PhD advisor, Prof. Joerg Appenzeller. I was extremely fortunate to have him as my advisor and mentor. He gave me the freedom and trust to explore new ideas and provided me with guidance and support through the process. He is not only a great teacher, but also a role model who showed me the mentality and integrity that a researcher should possess. The years working with him during my PhD have been a wonderful journey, and the things I learned from him will be a lifelong treasure.

I am also grateful to the members of my PhD committee, Prof. Zhihong Chen, Prof. Mark Lundstrom and Prof. Sumeet Gupta. Prof. Chen was always ready to share her insights and knowledge during our joint group meetings, and my research has also benefited from her efforts in securing the funding and coordinating the interactions with sponsors in the NEWLIMITS center. Prof. Lundstrom's classical papers on transport in nano devices had motivated me to pursue the path of research in nanoelectronics back when I was an undergraduate student, and being able to meet him in person and take his class in nanoscale transport (and got an A+) is like a dream come true. I also need to thank Prof. Gupta for his invaluable insights as a circuit expert, which help me evaluate my device projects from a different perspective.

I would like to thank my colleagues at Purdue University: Dr. Ashish Penumatcha, Dr. Abhijith Prakash, Dr. Feng Zhang, Dr. Chin-Sheng Pang, Dr. Neil Dilley, Jun Cai, Zheng Sun, Theresia Knobloch, Xiangkai Liu, Chin-Cheng Chiang, Dr. Yuqi Zhu, Dr. Ruiping Zhou, Dr. Suki Zhang, Dr. Tingting Shen, Shengjiao Zhang, Dr. Chun-Li Lo, Dr. Terry Hung, Hao-Yu Lan, Yuanqiu Tan, Dr. Vaibhav Ostwal and Dr. Punyashloka Debashis. As the Chinese saying goes, learning without peers leads to ignorance and narrow-mindedness. Over the years, I benefited tremendously from discussing research thoughts and experimental results with my colleagues and a lot of new ideas were stimulated by these discussions. Also, I would like to thank my collaborators, including Dr. Tarek Ameen, Prof. Rajib Rahman and Prof. Gerhard Klimeck from Purdue University; Dr. Huairuo Zhang, Dr. Sergiy Krylyuk, Dr. Leonid Bendersky and Dr. Albert Davydov from NIST; Dayane Reis, Mengyuan Li,

Dr. Bo Zhou, Dr. Xunzhao Yin and Prof. Sharon Hu from University of Notre Dame. Collaborating with people from other research fields have broadened my view and mindset, and it was truly my fortune to work with these talented people. My gratitude also goes to the staff of Birck Nanotechnology Center, including Bill Rowe, Joon Hyeong Park, Dave Lubelski, Jerry Shepard, Kenny Schwartz, Mike Bayless, Lorraine Fox and Mary Jo Totten, for their technical and operational assistance.

Last but not least, to my parents, Yingbiao Wu and Runfen Yao: thank you for your continuous and unconditional love throughout the years! Without your support, I could never achieve what I have today. For this, I dedicate this work to you.

# TABLE OF CONTENTS

| LI              | ST O                                                      | F TABLES                                                        | 10 |  |

|-----------------|-----------------------------------------------------------|-----------------------------------------------------------------|----|--|

| LI              | ST O                                                      | F FIGURES                                                       | 11 |  |

| LIST OF SYMBOLS |                                                           |                                                                 |    |  |

| ABBREVIATIONS   |                                                           |                                                                 |    |  |

| ABSTRACT        |                                                           |                                                                 |    |  |

| 1               | INT                                                       | RODUCTION                                                       | 28 |  |

|                 | 1.1                                                       | Two-dimensional semiconducting materials                        | 28 |  |

|                 | 1.2                                                       | Tunneling field-effect transistors                              | 29 |  |

|                 | 1.3                                                       | Reconfigurable nano-transistors for hardware security           | 32 |  |

|                 | 1.4                                                       | Organization                                                    | 35 |  |

| 2               | BLA                                                       | CK PHOSPHORUS TUNNELING FIELD-EFFECT TRANSISTORS                | 37 |  |

|                 | 2.1                                                       | Introduction                                                    | 37 |  |

|                 | 2.2                                                       | Device structure and operation principle                        | 39 |  |

|                 | 2.3                                                       | Electrical characterization                                     | 42 |  |

|                 | 2.4                                                       | Temperature-dependent measurement                               | 44 |  |

|                 | 2.5                                                       | Performance benchmark and projections                           | 46 |  |

|                 | 2.6                                                       | Conclusion                                                      | 51 |  |

|                 | 2.7                                                       | Appendix                                                        | 51 |  |

|                 |                                                           | 2.7.1 Thickness determination of BP                             | 51 |  |

|                 |                                                           | 2.7.2 Effects of BP orientation and transport direction on BTBT | 54 |  |

|                 |                                                           | 2.7.3 Methods                                                   | 57 |  |

| 3               | BLACK PHOSPHORUS VERTICAL TUNNELING FIELD-EFFECT TRANSIS- |                                                                 |    |  |

|                 | TOF                                                       | RS                                                              | 59 |  |

|   | 3.1 | Introduction                                                                 | 59 |

|---|-----|------------------------------------------------------------------------------|----|

|   | 3.2 | Device structure                                                             | 60 |

|   | 3.3 | Device characteristics                                                       | 61 |

|   |     | 3.3.1 Device operation in p-type configurations                              | 61 |

|   |     | 3.3.2 Device operation in n-type configurations                              | 64 |

|   | 3.4 | Comparison with previous works on 2D TFETs                                   | 66 |

|   | 3.5 | Conclusion                                                                   | 68 |

| 4 | TOV | WARDS CMOS-LIKE DEVICES FROM TWO-DIMENSIONAL MATERIALS                       | 69 |

|   | 4.1 | Introduction                                                                 | 69 |

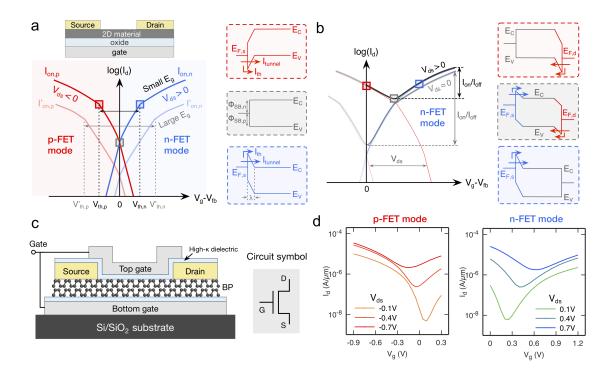

|   | 4.2 | Basic operation of Schottky-barrier field-effect transistors                 | 71 |

|   | 4.3 | Towards unipolar p- and n-type Schottky-barrier FETs                         | 74 |

|   | 4.4 | Experimental implementation                                                  | 75 |

|   | 4.5 | Circuit demonstration                                                        | 80 |

|   | 4.6 | Conclusion                                                                   | 82 |

| 5 | TW  | O-DIMENSIONAL TRANSISTORS WITH RECONFIGURABLE POLARI-                        |    |

|   | TIE | S FOR HARDWARE SECURITY                                                      | 83 |

|   | 5.1 | Introduction                                                                 | 83 |

|   | 5.2 | Polymorphic gates for logic locking and IC camouflaging                      | 84 |

|   | 5.3 | Schottky-barrier FETs for reconfigurable operation                           | 86 |

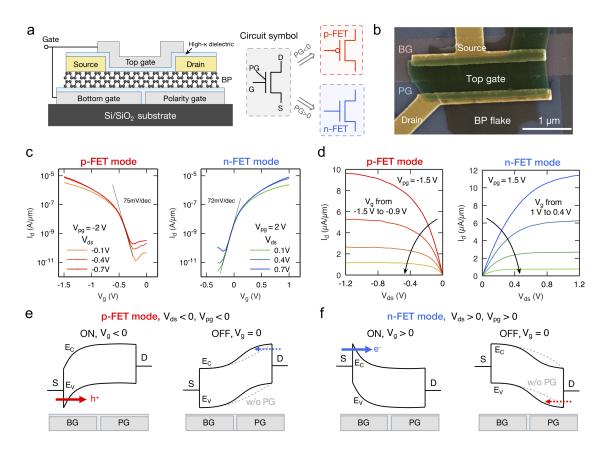

|   | 5.4 | Reconfigurable black phosphorus FETs                                         | 88 |

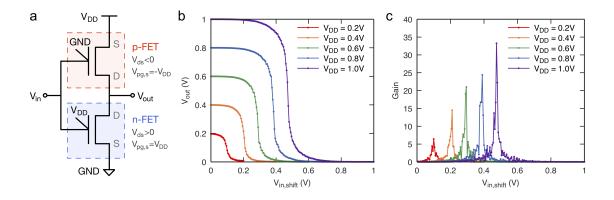

|   | 5.5 | Complementary logic inverter based on reconfigurable BP FETs $\ldots \ldots$ | 92 |

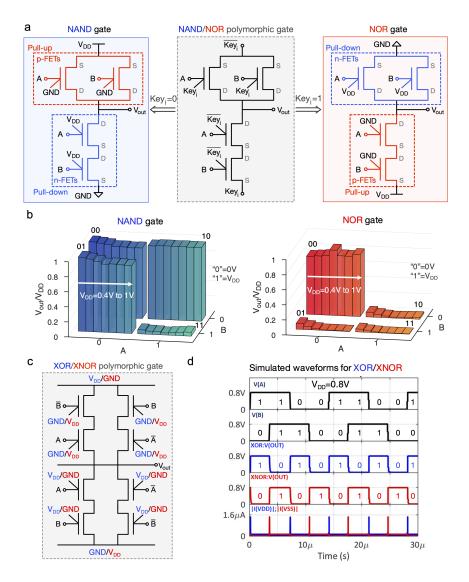

|   | 5.6 | Demonstration of polymorphic gates                                           | 93 |

|   | 5.7 | Robustness of the polymorphic gates                                          | 97 |

|   | 5.8 | Conclusion                                                                   | 97 |

|   | 5.9  | Appen        | dix                                                                                              | 99  |

|---|------|--------------|--------------------------------------------------------------------------------------------------|-----|

|   |      | 5.9.1        | Doping effect of ALD $Al_2O_3$ on BP                                                             | 99  |

|   |      | 5.9.2        | Effect of BP body thickness on the device performance                                            | 99  |

|   |      | 5.9.3        | Device modeling of reconfigurable BP FETs for circuit simulation $\ .$ .                         | 103 |

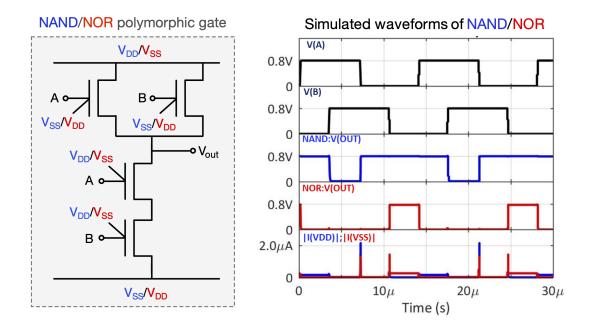

|   |      | 5.9.4        | Circuit simulation of a NAND/NOR polymorphic gate                                                | 104 |

|   |      | 5.9.5        | The effect of band-to-band tunneling on the off-state current of the                             |     |

|   |      |              | reconfigurable BP FETs                                                                           | 105 |

|   |      | 5.9.6        | Monte Carlo simulation for robustness of polymorphic gates $\ldots$ .                            | 107 |

|   |      | 5.9.7        | Methods                                                                                          | 110 |

| 6 | ART  | IFICIA       | L SUB-60 MV/DEC SWITCHING IN A METAL-INSULATOR-METAL-                                            | -   |

|   | INSU | JLATO        | R-SEMICONDUCTOR TRANSISTOR WITHOUT FERROELECTRIC                                                 |     |

|   | COM  | <b>IPONE</b> | NT                                                                                               | 113 |

|   | 6.1  | Introd       | uction $\ldots$ | 113 |

|   | 6.2  | Experi       | mental demonstration of sub-60 mV/dec switching in an MIMIS device                               | 116 |

|   | 6.3  | Model        | ing of the charging dynamics in the MIMIS device                                                 | 118 |

|   | 6.4  | Direct       | measurement of the waveform of gate voltage                                                      | 122 |

|   | 6.5  | Simula       | tion of sub-60 mV/dec switching with constant $V_G$ scan rate $\ldots$ .                         | 124 |

|   | 6.6  | Conclu       | nsion                                                                                            | 127 |

|   | 6.7  | Appen        | dix                                                                                              | 128 |

|   |      | 6.7.1        | Determination of capacitance and resistance components in the RC                                 |     |

|   |      |              | network model                                                                                    | 128 |

|   |      | 6.7.2        | Extraction of scan rates from experiment                                                         | 130 |

|   |      | 6.7.3        | Calculation of quantum capacitance $C_q$                                                         | 132 |

|   |      | 6.7.4        | Measurement of internal FET with different scan rates and hold time                              | 134 |

|   |      | 6.7.5        | Measurement of MIMIS FET with constant gate voltage scan rate                                    | 135 |

|     |      | 6.7.6  | Measurement of MIMIS FET with larger $AlO_x$ layer leakage resistance 13                                                                                                            | 37 |

|-----|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |      | 6.7.7  | Characterization of the thin Ti layer as internal gate electrode $\ldots$ 13                                                                                                        | 39 |

|     |      | 6.7.8  | Gate leakage current during $I_D - V_G$ scan $\ldots \ldots \ldots$ | 41 |

|     |      | 6.7.9  | Methods                                                                                                                                                                             | 42 |

| 7 S | SUM  | MARY   |                                                                                                                                                                                     | 44 |

| REF | FER  | ENCES  |                                                                                                                                                                                     | 45 |

| VIT | А    |        |                                                                                                                                                                                     | 53 |

| PUE | BLIC | CATION | NS                                                                                                                                                                                  | 34 |

# LIST OF TABLES

| 2.1 | A comparison of 2D TFETs. Reprinted with permission from P. Wu et al., "Com-                                                                                                                                                                        |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | plementary Black Phosphorus Tunneling Field-Effect Transistors," ACS Nano 13,                                                                                                                                                                       |    |

|     | 377–385 (2019). Copyright (2019) American Chemical Society                                                                                                                                                                                          | 48 |

| 3.1 | Comparison with other 2D TFETs. Reprinted with permission from P. Wu, J. Appenzeller, "Reconfigurable Black Phosphorus Vertical Tunneling Field-Effect Transistor with Record High ON-Currents," <i>IEEE Electron Device Letters</i> <b>40</b> , 6, |    |

|     | 981-984 (2019). Copyright (2019) IEEE                                                                                                                                                                                                               | 67 |

## LIST OF FIGURES

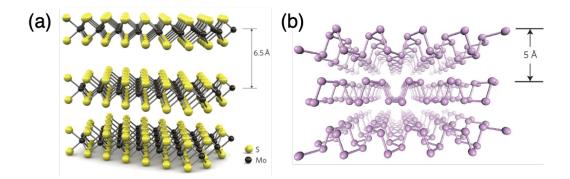

| 1.1 | Illustration of atomic structure of 2D materials. (a) Molybdenum disulfide (MoS <sub>2</sub> ). (b) Black phosphorus (BP). Reprinted with permission from B. Radisavljevic <i>et al.</i> , "Single-layer MoS <sub>2</sub> transistors", <i>Nature Nanotechnology</i> <b>6</b> , 147-150 (2011) & L. Li <i>et al.</i> "Black phosphorus field-effect transistors", <i>Nature Nanotechnology</i> <b>9</b> , 372-377 (2014). Copyright (2011 & 2014) Springer Nature.                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

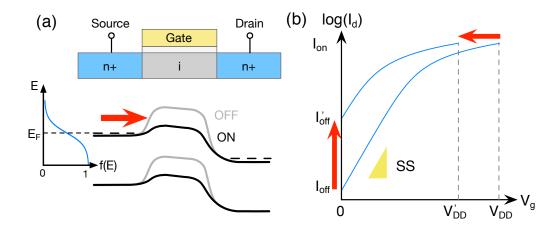

| 1.2 | (a) Schematic and band diagram of a MOSFET, showing the thermionic emission. (b) The impact of minimum SS on $\rm V_{DD}$ scaling and off-state current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 |

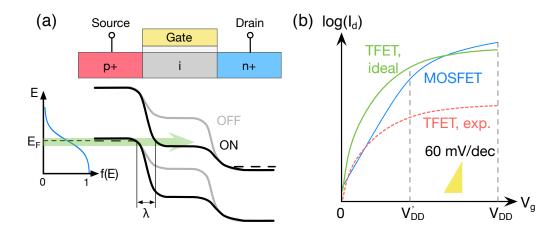

| 1.3 | (a) Schematic and band diagram of a TFET, showing the band-to-band tun-<br>neling current injection path. (b) A comparison of MOSFET and TFET<br>transfer characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32 |

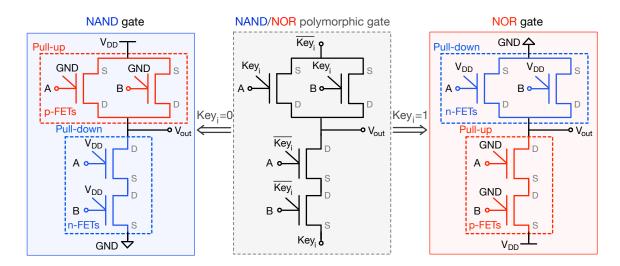

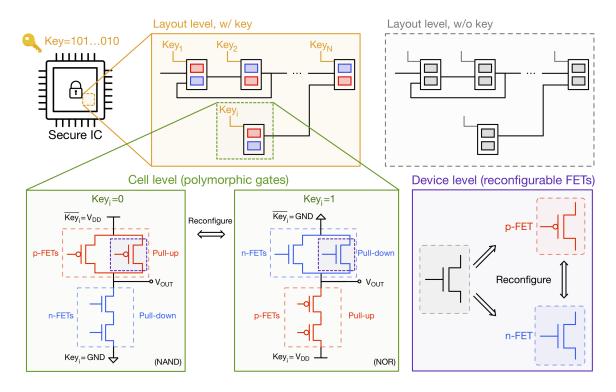

| 1.4 | Schematic of a NAND/NOR polymorphic gate built with reconfigurable nano-<br>transistors. Adapted with permission from P. Wu, D. Reis, X. S. Hu, J.<br>Appenzeller, "Two-dimensional transistors with reconfigurable polarities for<br>secure circuits," <i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer<br>Nature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |

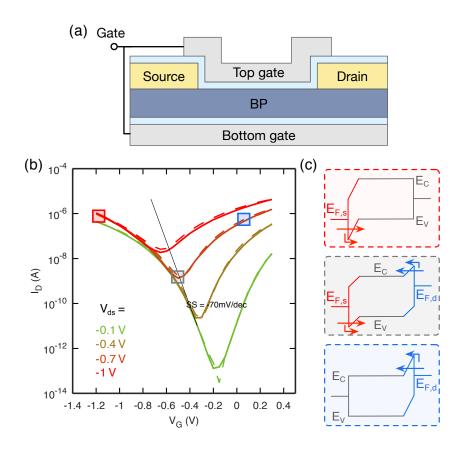

| 1.5 | An exemplary ambipolar BP transistor. (a) Schematic of an ambipolar BP transistor. (b) Transfer characteristics of the ambipolar BP transistor. Ambipolar characteristics are observed in the device. (c) Band diagrams of the BP ambipolar transistor corresponding to different gate voltages, showing the electron and hole injections. Adapted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," <i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer Nature.                                                                                                                                                                                                                                                                                                                      | 34 |

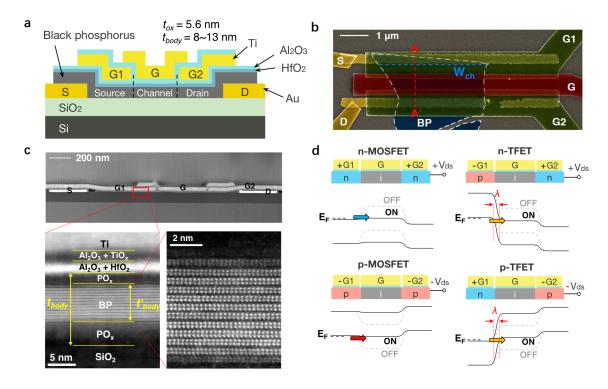

| 2.1 | Black phosphorus RED-TFET. (a) Schematic of the BP RED-TFET. (b) Representative false-colored SEM image of the BP RED-TFET. Scale bar: 1 $\mu$ m. (c) Representative cross-section HAADF-STEM image of the BP RED-TFET along A-A' in (b), showing the triple top-gate structure, the interface of BP and gate oxide, and crystal structure of BP. Notice that due to oxide formation on both sides of BP, the real body thickness $t'_{body}$ is smaller than the nominal body thickness $t_{body}$ . (d) Schematic illustration of the bands through the BP channel when reconfiguring the RED-TFET in the four operation modes, enabled by electrostatic doping as controlled by $V_{g1}$ and $V_{g2}$ . Reprinted with permission from P. Wu <i>et al.</i> , "Complementary Black Phosphorus Tunneling Field-Effect Transistors," ACS Nano 13, 377–385 (2019). Copyright (2019) American Chemical Society. | 40 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40 |

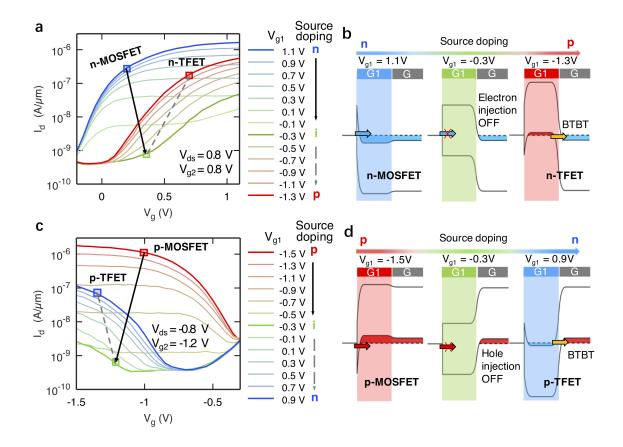

| 2.2 | Transfer characteristics and reconfiguration of the BP RED-TFET. (a, c)<br>Transfer characteristics of the BP RED-TFET in (a) n-type and (c) p-type<br>configurations under different source doping conditions, showing the transi-<br>tion from the MOSFET mode to the TFET mode. (b, d) Band diagrams<br>of the RED-TFET in (b) n-type and (d) p-type configurations corresponding<br>to different source doping conditions in (a, c) respectively. Reprinted with<br>permission from P. Wu <i>et al.</i> , "Complementary Black Phosphorus Tunneling<br>Field-Effect Transistors," <i>ACS Nano</i> <b>13</b> , 377–385 (2019). Copyright (2019)<br>American Chemical Society.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

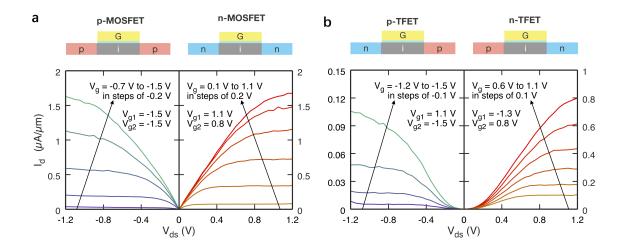

| 2.3 | Output characteristics of the BP RED-TFET. (a) Output characteristics of<br>the BP RED-TFET in the p-type and n-type MOSFET mode. The satu-<br>ration behavior indicates a good gate control on the channel. (b) Output<br>characteristics of the BP RED-TFET in the p-type and n-type TFET mode.<br>Non-linear output onsets are observed due to drain-induced-barrier thinning<br>(DIBT) effect. Reprinted with permission from P. Wu <i>et al.</i> , "Complemen-<br>tary Black Phosphorus Tunneling Field-Effect Transistors," <i>ACS Nano</i> <b>13</b> ,<br>377–385 (2019). Copyright (2019) American Chemical Society                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 44 |

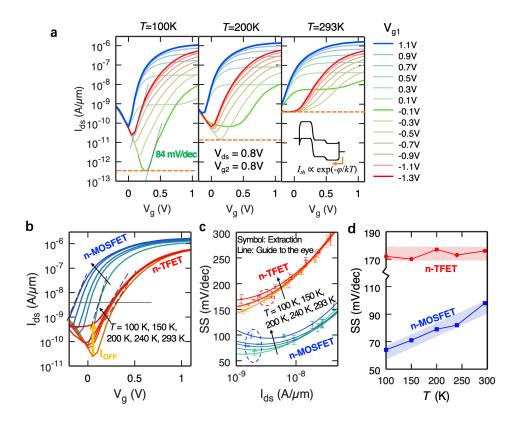

| 2.4 | Temperature-dependent measurements. (a) Comparison of transfer character-<br>istics of the BP RED-TFET at 100 K, 200 K and 293 K, showing increasing<br>OFF-current levels at elevated temperatures. Dashed orange lines indicate<br>thermionic current and trap-assisted current cut-off limits. The inset shows<br>a band diagram explaining the impact of thermionic injection from the drain<br>at higher temperatures. (b) Comparison of transfer characteristics of the<br>BP RED-TFET in the n-type MOSFET mode and the n-type TFET mode<br>at different temperatures. In the n-TFET mode, the transfer characteristics<br>show a weaker temperature dependence compared with the operation in the<br>n-MOSFET mode, except for a rise in the minimum OFF current level due to<br>thermal injection. (c) Comparison of experimental subthreshold swing (SS)<br>values versus drain current $I_d$ in the n-type MOSFET mode and the n-type<br>TFET mode at different temperatures. In the n-TFET mode, SS shows weaker<br>temperature dependence. (d) Comparison of experimental SS values versus<br>temperature for the n-type MOSFET mode and the n-type TFET mode.<br>Reprinted with permission from P. Wu <i>et al.</i> , "Complementary Black Phos-<br>phorus Tunneling Field-Effect Transistors," <i>ACS Nano</i> 13, 377–385 (2019).<br>Copyright (2019) American Chemical Society | 45 |

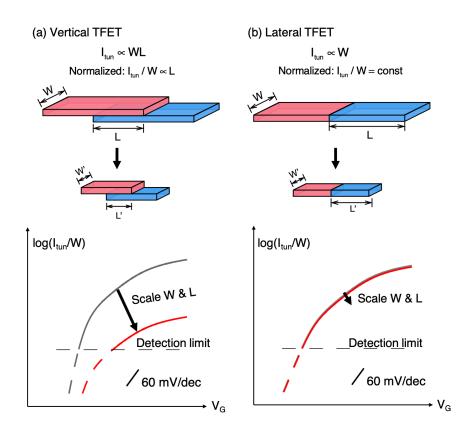

| 2.5 | Comparison of scaling for (a) a vertical TFET and (b) a lateral TFET.<br>Reprinted with permission from P. Wu <i>et al.</i> , "Complementary Black Phos-<br>phorus Tunneling Field-Effect Transistors," <i>ACS Nano</i> <b>13</b> , 377–385 (2019).<br>Copyright (2019) American Chemical Society.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 47 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

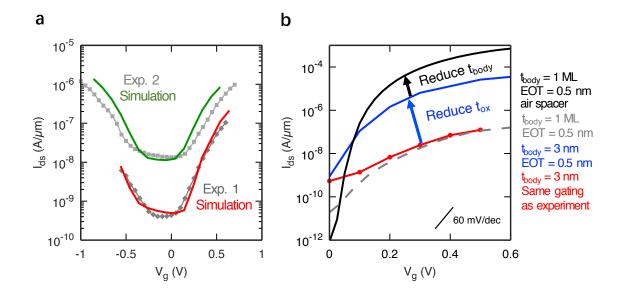

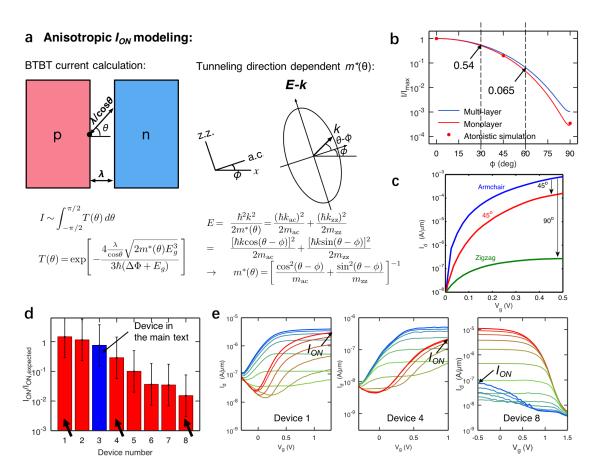

- 2.6Projections for BP TFET performance. (a) Atomistic simulations, solid lines, of  $I_d - V_q$  for two exemplary BP TFETs, showing good agreement with experimental data (gray dots). Exp. 1 refers to measurements performed on a device as shown in Fig. 2.1 with a nominal 8.3 nm body and with gate G1 and G2 having configurations (-1.3 V, 0.8 V). The simulation has been performed with a smaller BP thickness of 3 nm and a thicker oxide to account for the oxidation. Exp. 2 is a measurement of an earlier prototype device with a thicker BP flake of 12.8 nm that has been simulated with 7 nm to account for the oxidation. (b) Simulation of the fabricated BP TFET shown in red. Improving the electrostatics by using  $HfO_2$  with an EOT = 0.5 nm is expected to significantly improve steepness and current levels as shown in blue. Further improvements can be achieved by scaling down the channel into a mono-layer (ML) BP and incorporating air spacer as shown in black. Notice that due to the larger bandgap of ML BP, the current levels are lower without proper electrostatics enabled by an air spacer, as shown by the gray dashed line. Reprinted with permission from P. Wu et al., "Complementary Black Phosphorus Tunneling Field-Effect Transistors," ACS Nano 13, 377–385 (2019). Copyright (2019) American Chemical Society.

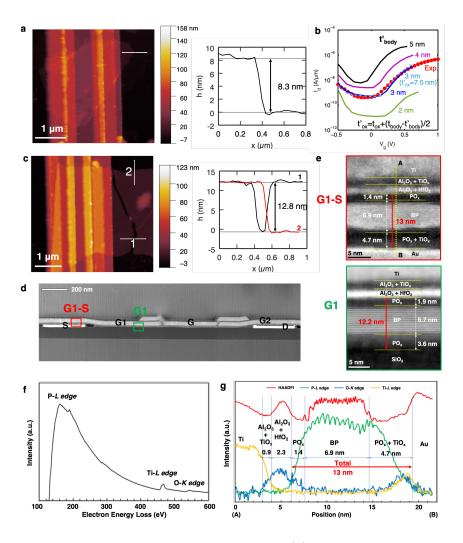

- Thickness determination of BP. (a) AFM image and line scan of the BP flake 2.7used in the electrical characterization  $(t_{body} = 8.3 \text{ nm})$ . (b) Comparison of measured  $I_d - V_g$  curve of BP TFET (dots) and simulated  $I_d - V_g$  curves for different body thicknesses  $t'_{body}$  (lines). The simulation with  $t'_{body} = 3$  nm matches best with the experiment. (c) AFM image and line scan of the BP flake used in the TEM analysis ( $t_{body} = 12.8 \text{ nm}$ ). (d) HAADF-STEM image showing the cross-section of the BP RED-TFET. (e) Higher magnification HAADF-STEM images from the regions defined by the red and green boxes in (d). (f) Background subtracted EELS spectra, showing the sum of all the spectra acquired along A-B line shown in (e). (g) Intensity profiles of HAADF image and EELS P-L, O-K and Ti-L edges along A-B line in (e), showing the thicknesses of crystalline BP and  $PO_x$  layers and total flake thickness. Reprinted with permission from P. Wu et al., "Complementary Black Phosphorus Tunneling Field-Effect Transistors," ACS Nano 13, 377–385 (2019). Copyright (2019) American Chemical Society.

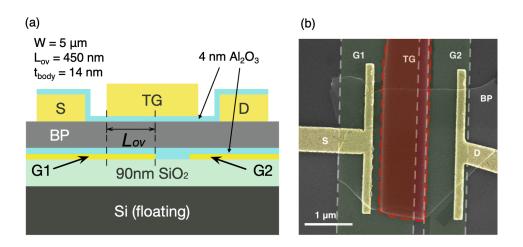

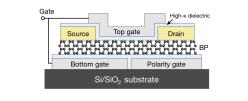

3.1 (a) Schematic of the black phosphorus vertical TFET. (b) Representative false-colored SEM image of a BP vertical TFET. Reprinted with permission from P. Wu, J. Appenzeller, "Reconfigurable Black Phosphorus Vertical Tunneling Field-Effect Transistor with Record High ON-Currents," *IEEE Electron Device Letters* 40, 6, 981-984 (2019). Copyright (2019) IEEE. ......

60

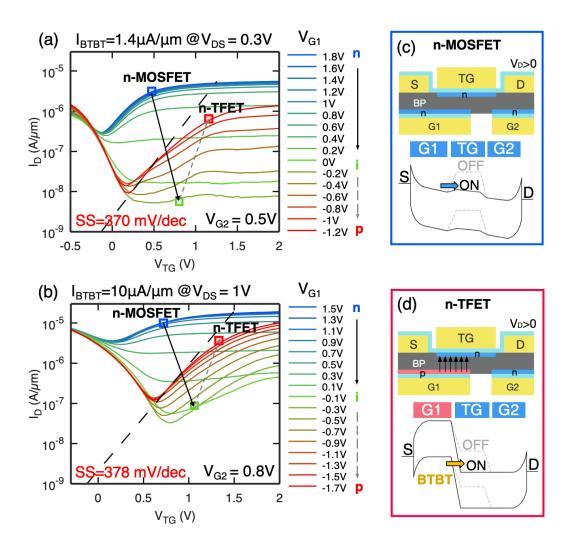

62

64

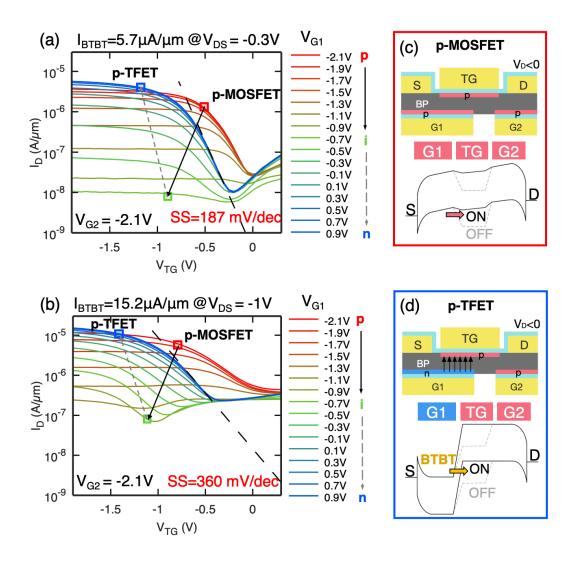

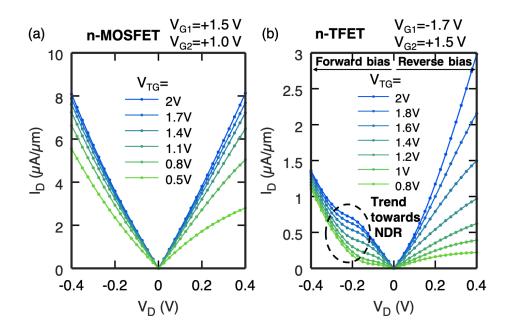

- 3.2 (a-b) Transfer characteristics of a BP vertical TFET in the p-type configuration at (a)  $V_{DS} = -0.3$  V. (b)  $V_{DS} = -1$  V. (c-d) Device schematics and band diagrams in the (c) p-MOSFET mode. (d) p-TFET mode. Reprinted with permission from P. Wu, J. Appenzeller, "Reconfigurable Black Phosphorus Vertical Tunneling Field-Effect Transistor with Record High ON-Currents," *IEEE Electron Device Letters* **40**, 6, 981-984 (2019). Copyright (2019) IEEE.

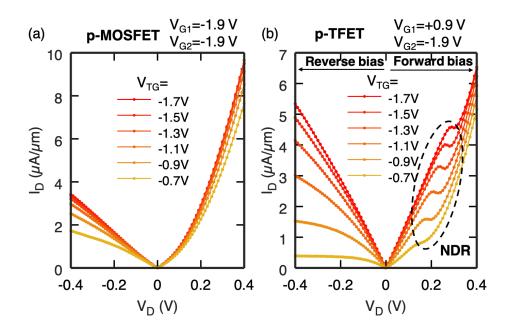

- 3.3 Output characteristics of a BP vertical TFET in the (a) p-MOSFET mode (b) p-TFET mode. NDR is observed at room temperature in forward bias direction in the p-TFET mode, but not in the p-MOSFET mode as expected. Reprinted with permission from P. Wu, J. Appenzeller, "Reconfigurable Black Phosphorus Vertical Tunneling Field-Effect Transistor with Record High ON-Currents," *IEEE Electron Device Letters* **40**, 6, 981-984 (2019). Copyright (2019) IEEE. .....

- 3.4 (a-b) Transfer characteristics of a BP vertical TFET in the n-type configuration at (a)  $V_{DS} = 0.3$  V. (b)  $V_{DS} = 1$  V. (c-d) Device schematics and band diagrams in the (c) n-MOSFET mode. (d) n-TFET mode. Reprinted with permission from P. Wu, J. Appenzeller, "Reconfigurable Black Phosphorus Vertical Tunneling Field-Effect Transistor with Record High ON-Currents," *IEEE Electron Device Letters* **40**, 6, 981-984 (2019). Copyright (2019) IEEE.

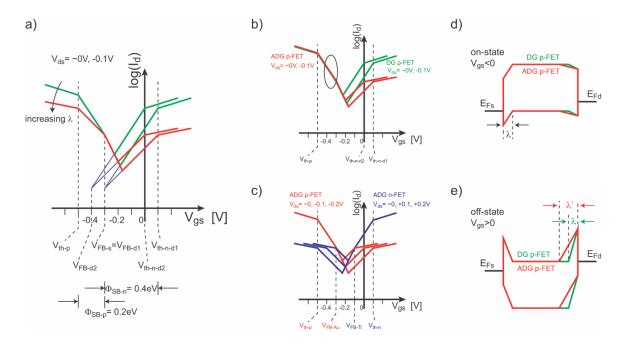

- 4.2 (a) Construction of ambipolar device characteristics as in Fig. 4.1, but for two drain voltages, showing a shift of the electron branch for negative drain voltages. Green vs red captures a uniform change of λ, e.g., by changing from a double gated to a single gated structure. (b) Improvement of device characteristics from the asymmetric double gate design by suppressing the electron injection from the drain without sacrificing on-state performance. (c) The expected outcome for a properly designed n-type and p-type ADG FET exhibiting the desired unipolar device characteristics. (d) Band diagrams of a p-type DG FET and a p-type ADG FET in the on-state. (e) Band diagrams of a p-type DG FET and a p-type ADG FET in the off-state. Reprinted from P. Wu, J. Appenzeller, "Towards CMOS like devices from two-dimensional channel materials," APL Materials 13, 377–385 (2019), under a Creative Commons Attribution (CC BY) license.

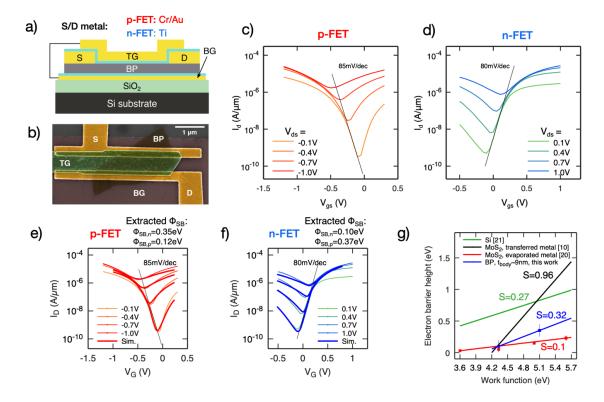

- 4.3 (a) Device structure of a BP DG-FET. (b) False-colored SEM image of a BP DG-FET. (c) Transfer characteristics of a BP DG p-FET. (d) Transfer characteristics of a BP DG n-FET. (e) Experimental and simulated characteristics of a p-type BP FET and the extracted barrier heights. (f) Experimental and simulated characteristics of an n-type BP FET and extracted barrier heights. (g) Schottky barrier heights vs metal work function in various metal-semiconductor systems. The data for Si and MoS<sub>2</sub> are derived from Refs. [81], [4], and [89]. Reprinted from P. Wu, J. Appenzeller, "Towards CMOS like devices from two-dimensional channel materials," APL Materials 13, 377–385 (2019), under a Creative Commons Attribution (CC BY) license.

77

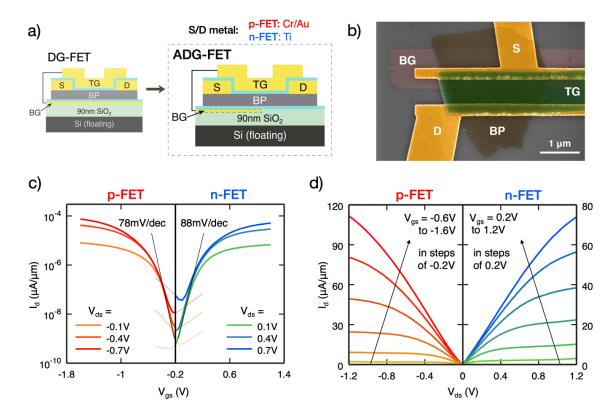

- 4.4 (a) Device structure of a BP ADG-FET, in comparison with a BP DG-FET.

(b) False-colored SEM image of a BP ADG-FET. (c) Transfer characteristics of a p-type and an n-type BP ADG-FET. (d) Output characteristics of a p-type and an n-type BP ADG-FET. Reprinted with permission from P. Wu, J. Appenzeller, *IEEE Device Research Conference* (IEEE, 2018). Copyright 2018 IEEE.

- 5.2 Design consideration for reconfigurable Schottky-barrier FET. (a) Schematic of a Schottky-barrier FET with 2D channel and the impact of bandgap on the device performance of a reconfigurable SB-FET with mid-gap Schottky barriers. (b) Impact of drain injection on the on-off ratio of a SB-FET in the n-FET mode. (c) Device structure of a double-gate BP SB-FET. (d) Transfer characteristics of the BP SB-FET in the p-FET and n-FET modes. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," Nature Electronics 4, 45-53 (2021). Copyright (2021) Springer Nature.

- 5.3 Black phosphorus transistors with reconfigurable polarities. (a) Schematic of the reconfigurable BP transistor with polarity gate. (b) Scanning electron microscopy image of a reconfigurable BP transistor (BG and PG stand for bottom gate and polarity gate, respectively). (c) Transfer characteristics of a reconfigurable BP transistor in the p-FET mode and n-FET mode. (d) Output characteristics of the transistor in the p-FET mode and n-FET mode. (e-f) Energy band diagrams of the transistor in the on-state and off-state of the (e) p-FET mode and (f) n-FET mode. The dashed lines illustrate the energy bands and corresponding drain injection current paths without polarity gate, which lead to higher  $I_{off}$ . Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," *Nature Electronics* 4, 45-53 (2021). Copyright (2021) Springer Nature.

89

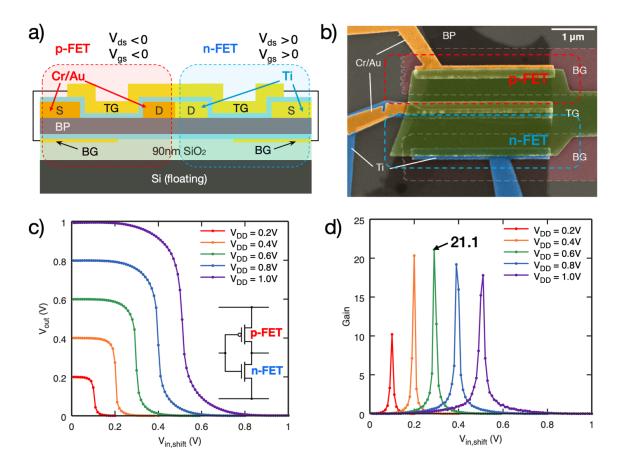

- 5.4 Inverter characteristics. (a) Schematic of an inverter formed by connecting two reconfigurable BP transistors together on chip, with one in the p-FET mode and the other in the n-FET mode. (b) Voltage transfer characteristics  $V_{out} - V_{in}$  of the inverter under different supply voltages  $V_{DD}$ . Note that the input voltage has been shifted by 0.27 V, *i.e.*,  $V_{in,shift} = V_{in} + 0.27$  V, to compensate for the non-zero  $V_{fb}$ . (c) Gain of the inverter under different supply voltages  $V_{DD}$ . Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," *Nature Electronics* 4, 45-53 (2021). Copyright (2021) Springer Nature.

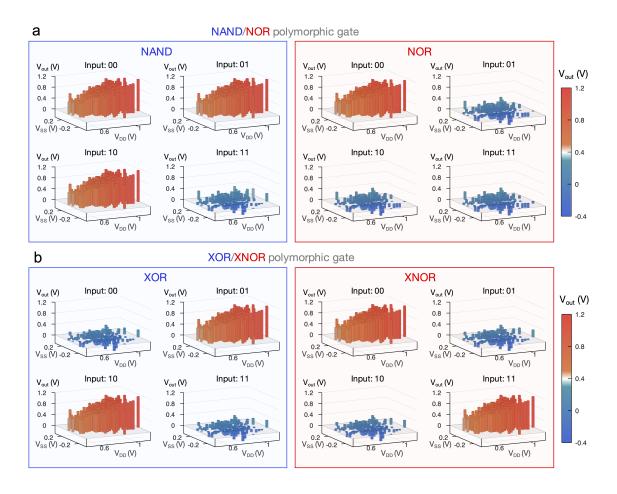

- 5.5 Demonstration of NAND/NOR and XOR/XNOR polymorphic gates. (a) Schematic of a NAND/NOR polymorphic gate leveraging the tunable polarities of the reconfigurable BP transistors. (b) Measured output voltages of the NAND/NOR polymorphic gate in the NAND and NOR configurations as a function of inputs A and B under different supply voltages V<sub>DD</sub> from 0.4 V to 1 V, showing the reconfigurability of the polymorphic gate and low-voltage operations. (c) Schematic of an XOR/XNOR polymorphic gate. (d) Simulated waveforms of the XOR/XNOR polymorphic gate based on experimental data. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," Nature Electronics 4, 45-53 (2021). Copyright (2021) Springer Nature. 95

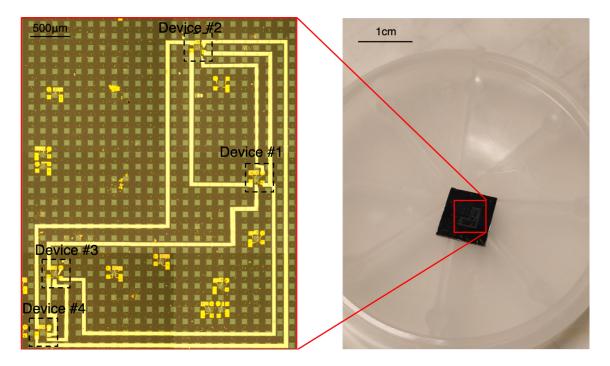

- 5.6 Optical image and photograph of the NAND/NOR polymorphic gate on a single chip, showing the connections between four individual reconfigurable BP devices. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," *Nature Electronics* 4, 45-53 (2021). Copyright (2021) Springer Nature.

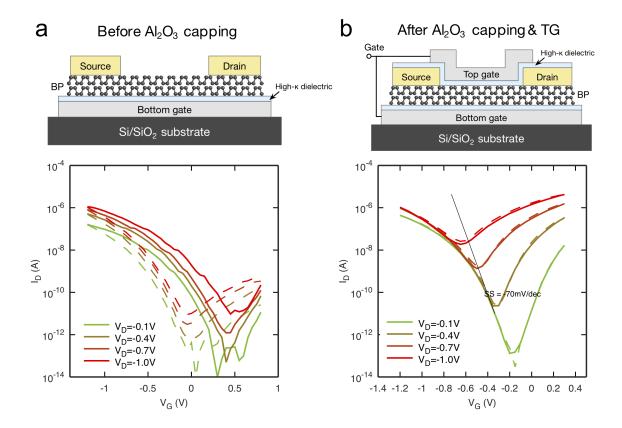

| 5.8  | Doping effect of ALD Al <sub>2</sub> O <sub>3</sub> . (a) Transfer characteristics of a BP SB-FET be-<br>fore Al <sub>2</sub> O <sub>3</sub> capping. (b) Transfer characteristics of the same device after Al <sub>2</sub> O <sub>3</sub><br>and top-gate fabrication. Reprinted with permission from P. Wu, D. Reis, X.<br>S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable po-<br>larities for secure circuits," <i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright<br>(2021) Springer Nature |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

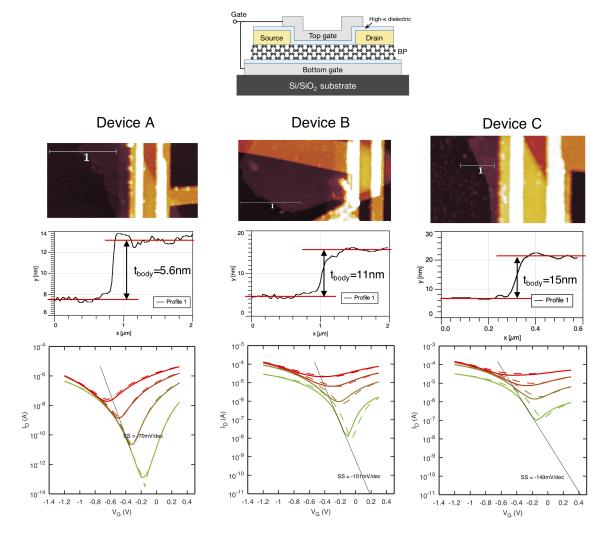

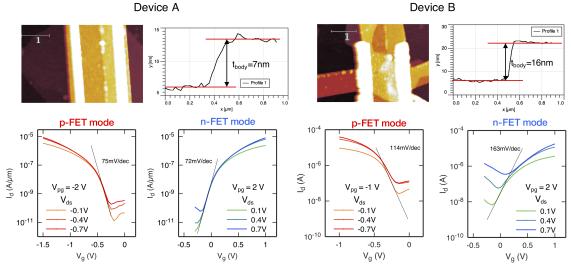

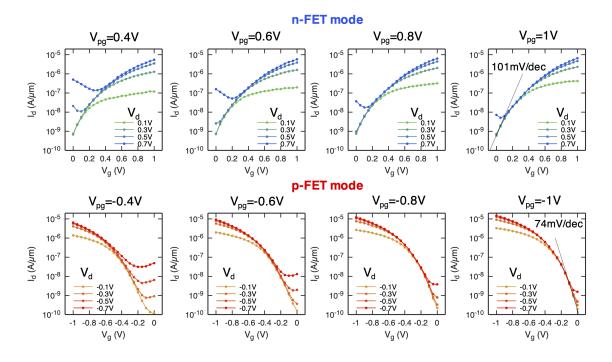

| 5.9  | Effect of BP body thickness on BP SB-FETs performance. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," <i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer Nature                                                                                                                                                                                                                             |  |

| 5.10 | Effect of BP body thickness on reconfigurable BP FETs performance. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," <i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer Nature                                                                                                                                                                                                                 |  |

| 5.11 | Voltage scan ranges for experimental measurement, in the format of "[start:step:end]".<br>Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller,<br>"Two-dimensional transistors with reconfigurable polarities for secure circuits,"<br><i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer Nature 103                                                                                                                                                                                |  |

| 5.12 | Measurement results of the reconfigurable BP FET used for modeling. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," <i>Nature Electronics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer Nature                                                                                                                                                                                                                |  |

| 5.13 | Simulated waveforms of NAND/NOR polymorphic gate. Reprinted with per-<br>mission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional<br>transistors with reconfigurable polarities for secure circuits," <i>Nature Electron-</i><br><i>ics</i> 4, 45-53 (2021). Copyright (2021) Springer Nature                                                                                                                                                                                                                      |  |

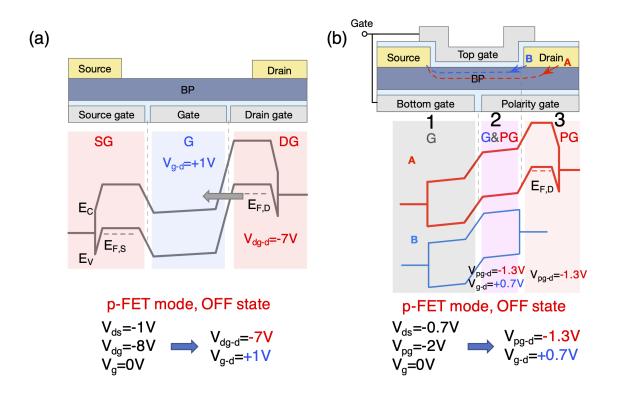

| 5.14 | Device schematics and band diagrams of two reconfigurable FET structures<br>in the OFF-state of p-FET mode. (a) Triple-gated structure in Ref. [62]. (b)<br>Device structure in our work. Reprinted with permission from P. Wu, D. Reis,<br>X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable<br>polarities for secure circuits," <i>Nature Electronics</i> 4, 45-53 (2021). Copyright<br>(2021) Springer Nature                                                                                         |  |

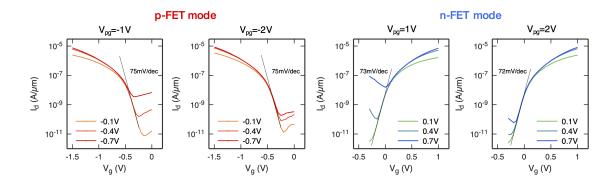

| 5.15 | Transfer characteristic of the reconfigurable BP FET in the p-FET mode and<br>the n-FET mode under different polarity gate voltages. Reprinted with per-<br>mission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional<br>transistors with reconfigurable polarities for secure circuits," <i>Nature Electron-</i><br><i>ics</i> <b>4</b> , 45-53 (2021). Copyright (2021) Springer Nature                                                                                                                           |  |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

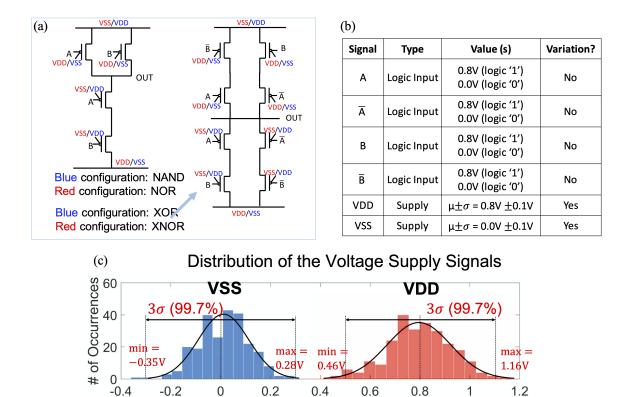

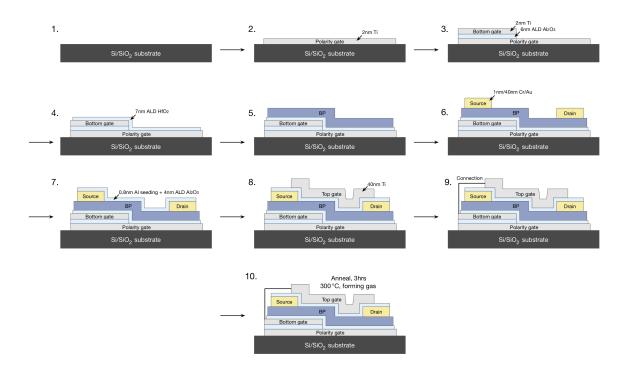

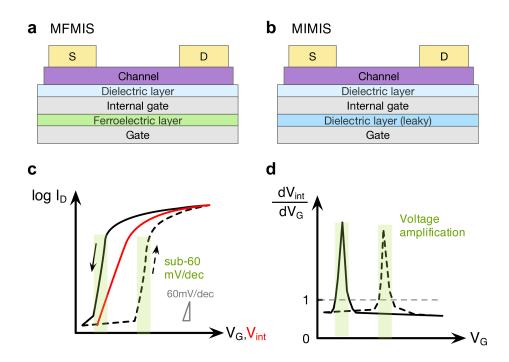

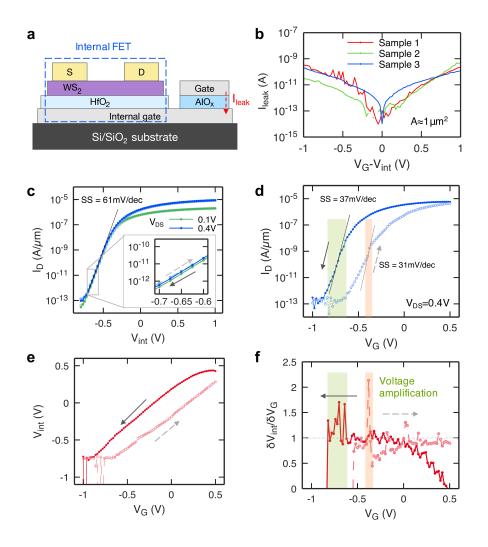

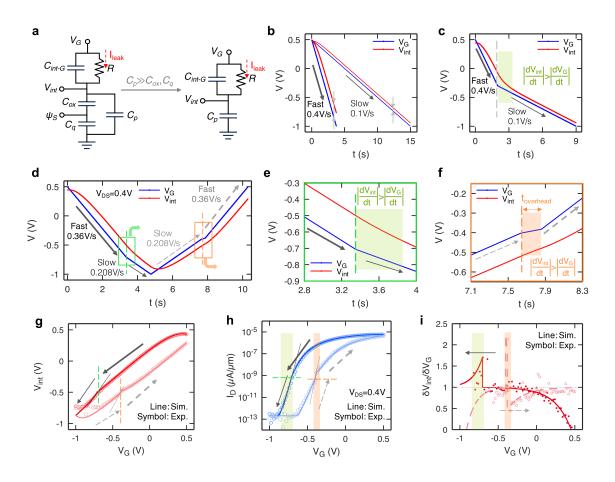

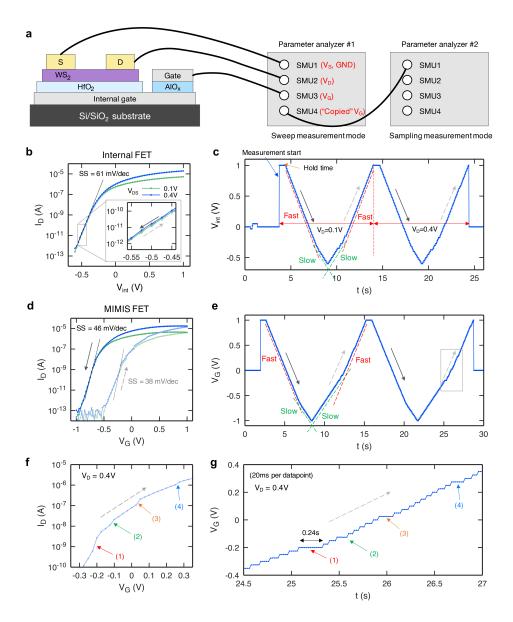

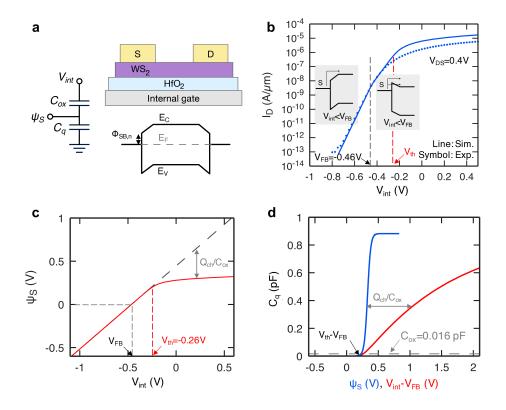

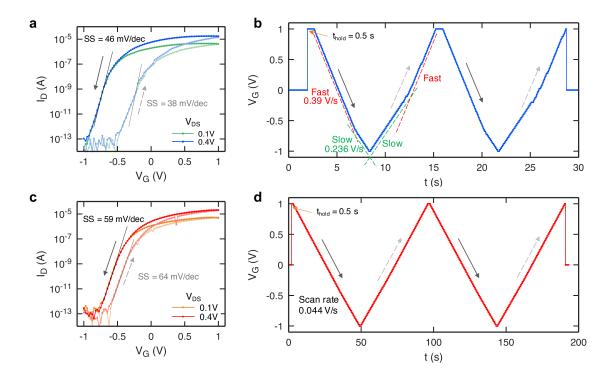

5.16 Setup of Monte Carlo Simulations. We assess the operation of the polymorphic NAND/NOR and XOR/XNOR gates under power supply variations. V<sub>DD</sub> and  $V_{SS}$  were sampled with a Gaussian distribution, where  $\mu$  ( $V_{DD}$ )=0.8 V and  $\mu(V_{SS})=0$  V,  $\sigma=100$  mV. Four logic inputs (A and B) patterns were tested for each gate, *i.e.*, '00', '01', '10', '11', without voltage variations. Considering the  $\mu(V_{DD})$ ,  $\mu(V_{SS})$ , and  $\sigma$  adopted in our simulations, there is no overlap between  $V_{DD}$  and  $V_{SS}$ . Furthermore, 99.7% (3 $\sigma$ ) of the voltage supply samples produced by the Gaussian distribution fall in the  $V_{DD} = [0.5 \ 1.1]$  V and  $V_{SS} = [-0.3 \ 0.3]$  V ranges. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," Nature Electronics 4, 45-53 (2021). Copyright 1095.17 Process flow of device fabrication. Reprinted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," Nature Electronics 4, 45-53 (2021). 111 Steep switching behavior in MFMIS and MIMIS structure. (a) Schematic of 6.1a metal-ferroelectric-metal-insulator-semiconductor (MFMIS) structure. (b) Schematic of a metal-insulator-metal-insulator-semiconductor (MIMIS) structure with a leaky dielectric layer between gate and internal gate. (c) Illustration of the transfer characteristics of a steep switching MFMIS or MIMIS device. (d) Illustration of internal voltage amplification of a steep switching MFMIS or MIMIS device. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society. 115 Experimental demonstration of sub-60 mV/dec switching in a MIMIS device. 6.2(a) Schematic of the MIMIS transistor structure with  $WS_2$  channel. (b) Leakage current  $I_{leak}$  through the leaky AlO<sub>x</sub> dielectric. (c)  $I_D - V_{int}$  characteristics of  $WS_2$  FET using the internal gate electrode, showing near-ideal 60 mV/dec switching. Inset: enlarged view of the subthreshold  $I_D - V_{int}$  characteristics, showing negligible hysteresis. (d)  $I_D - V_G$  characteristics of the  $WS_2$  MIMIS FET using the electrode labeled "gate", showing sub-60 mV/dec switching and anti-clockwise hysteresis. (e) Extracted  $V_{int} - V_G$  from the  $I_D$  $-V_G$  scan. (f) Extracted internal voltage gain  $\delta V_{int}/\delta V_G - V_G$  from the  $I_D$  - $V_G$  scan, showing internal voltage amplifications. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Fer-

| American Chemical Socie | tv | <br> | <br> | 117 |

|-------------------------|----|------|------|-----|

roelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021)

- 6.3Simulation of the charging dynamics in the  $I_D - V_G$  scan of the MIMIS device. (a) Circuit model of the MIMIS device. (b) Simulated  $V_{int}$  response to different  $V_G$  scan rates. (c) Simulated  $V_{int}$  response to  $V_G$  scan with varying scan rates, showing different transient voltage amplification during transition from fast scan to slow scan. (d) Simulated  $V_G$  scan and  $V_{int}$  response during the  $I_D - V_G$ scan of the WS<sub>2</sub> MIMIS FET. (e) Enlarged views of the  $V_G$  scan and (f)  $V_{int}$ response, showing different transient voltage amplification during transitions of scan rates. (g) Simulated  $V_{int} - V_G$  during the  $I_D - V_G$  scan. (h) Simulated  $I_D - V_G$  characteristics of the MIMIS device. (i) Simulated internal voltage gain  $\delta V_{int}/\delta V_G - V_G$  during the  $I_D - V_G$  scan. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society. 119. . . . . . . .

- 6.4 Measurement of waveforms of gate voltage. (a) Schematic of measurement setup for measuring testing signals using the sampling measurement of the parameter analyzer. (b)  $I_D - V_{int}$  characteristics of the internal FET. (c) Measured waveform of  $V_{int}$  as a function of time. (d)  $I_D - V_G$  characteristics of the MIMIS FET. (e) Measured waveform of  $V_G$  as a function of time. (f) Enlarged view of  $I_D - V_G$  characteristics of the MIMIS FET in the backward scan direction at  $V_D = 0.4$  V. (g) Enlarged view of measured waveform of  $V_G$ as a function of time. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society. 123

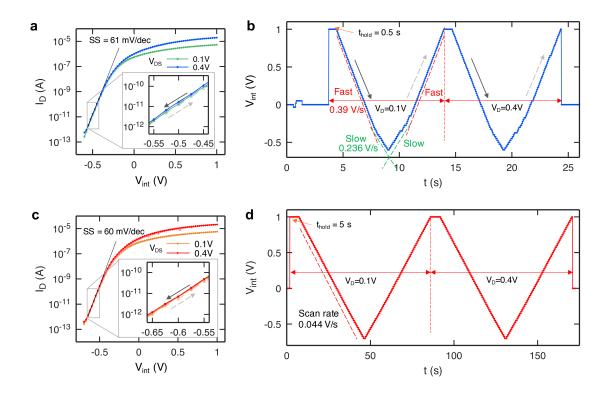

- 6.9 Measurement of internal FET with different scan rates. (a)  $I_D V_{int}$  characteristics of the internal FET with  $t_{delay} = 0$  s and  $t_{hold} = 0.5$  s. (b) Measured waveform of  $V_{int}$  as a function of time with  $t_{delay} = 0$  s and  $t_{hold} = 0.5$  s. (c)  $I_D V_{int}$  characteristics of the internal FET with  $t_{delay} = 0.5$  s and  $t_{hold} = 5$  s. (d) Measured waveform of  $V_{int}$  as a function of time with  $t_{delay} = 0.5$  s and  $t_{hold} = 5$  s. (d) Measured waveform of  $V_{int}$  as a function of time with  $t_{delay} = 0.5$  s and  $t_{hold} = 5$  s. (d) Measured waveform of  $V_{int}$  as a function of time with  $t_{delay} = 0.5$  s and  $t_{hold} = 5$  s. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society. . . . . . . . 135

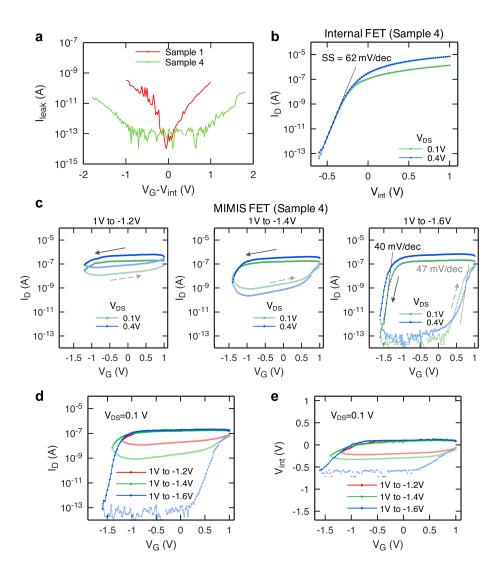

- 6.11 Measurement of MIMIS FET with large  $AlO_x$  layer leakage resistance. (a)  $I_{leak} - V_{diff}$  characteristics of the  $AlO_x$  capacitors in two different samples. (b)  $I_D - V_{int}$  characteristics of the internal FET. (c)  $I_D - V_G$  characteristics of the MIMIS FET with different voltage scan ranges. (d) A compilation of  $I_D - V_G$  characteristics of the MIMIS FET with different voltage scan ranges. (e) Extracted  $V_{int}$  as a function of  $V_G$  during  $I_D - V_G$  measurement with different voltage scan ranges. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society. 138

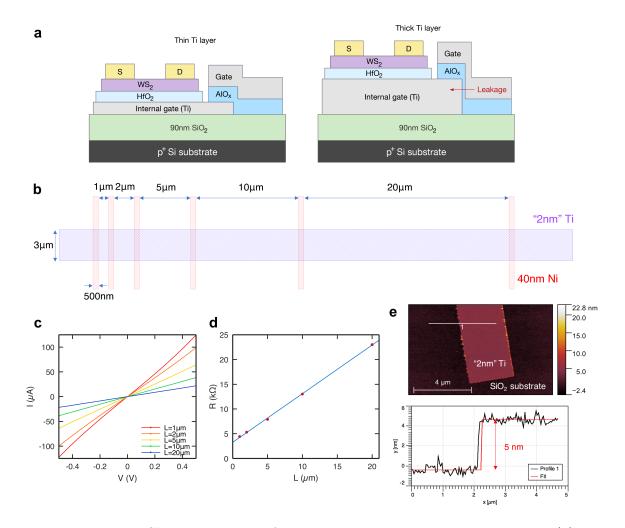

- 6.12 Characterization of thin Ti layer as internal gate electrode. (a) Schematic of step coverage of evaporated  $AlO_x$  with thin and thick Ti layers. (b) Schematic of the TLM structure. (c) I - V characteristics of the Ti stripes with different lengths. (d) TLM measurement results. (e) AFM scan of the Ti layer. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society. . . . . . . 140

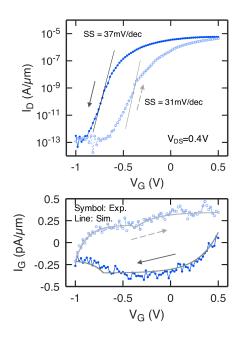

- 6.13 Measured and simulated  $I_G V_G$  during  $I_D V_G$  scan. Reprinted with permission from P. Wu, J. Appenzeller, "Artificial Sub-60 Millivolts/Decade Switching in a Metal-Insulator-Metal-Insulator-Semiconductor Transistor without Ferroelectric Component," ACS Nano 15, 5158-5164 (2021). Copyright (2021) American Chemical Society.

# LIST OF SYMBOLS

| $I_{ON}$                 | ON-state current        |

|--------------------------|-------------------------|

| $I_{OFF}$                | OFF-state current       |

| $V_G, V_{GS}$            | gate voltage            |

| $V_D, V_{DS}$            | drain voltage           |

| $\mathrm{V}_\mathrm{DD}$ | supply voltage          |

| GND                      | ground                  |

| $V_{th}$                 | threshold voltage       |

| $E_g$                    | bandgap                 |

| $E_F$                    | Fermi level             |

| $E_C$                    | conduction band minimum |

| $E_V$                    | valence band maximum    |

| $m^*$                    | effective mass          |

| $m_0$                    | free electron mass      |

| $\lambda$                | screening length        |

| $t_{ox}$                 | oxide thickness         |

| $t_{body}$               | body thickness          |

| $C_q$                    | quantum capacitance     |

| W                        | channel width           |

| $L_g, L_{ch}$            | gate/channel length     |

| $\Phi_{SB}$              | Schottky-barrier height |

# ABBREVIATIONS

| MOSFET              | metal-oxide-semiconductor field-effect transistor |

|---------------------|---------------------------------------------------|

| SB-FET              | Schottky-barrier field-effect ttransistor         |

| TFET                | tunneling field-effect transistor                 |

| NC-FET              | negative capacitance field-effect transistor      |

| CMOS                | complementary metal-oxide semiconductor           |

| IC                  | integrated circuit                                |

| $\mathbf{SS}$       | subthreshold swing, or inverse subthreshold slope |

| BP                  | black phosphorus                                  |

| TMD                 | transition metal dichalcogenides                  |

| 1D                  | one-dimensional                                   |

| 2D                  | two-dimensional                                   |

| $MoS_2$             | molybdenum disulfide                              |

| $WSe_2$             | tungsten diselenide                               |

| $WS_2$              | tungsten disulfide                                |

| CNT                 | carbon nanotube                                   |

| $\mathrm{SiO}_2$    | silicon dioxide                                   |

| $\mathrm{HfO}_{2}$  | hafnium oxide                                     |

| $Al_2O_3$           | aluminum oxide                                    |

| Al                  | aluminum                                          |

| Au                  | gold                                              |

| $\operatorname{Cr}$ | chromium                                          |

| Ni                  | nickel                                            |

| Ti                  | titanium                                          |

| Si                  | silicon                                           |

| $\mathrm{mV/dec}$   | milivolts per decade                              |

| eV                  | electron volt                                     |

| $\mu A/\mu m$       | micro ampere per micrometer                       |

| ALD                 | atomic layer deposition                           |

|                     |                                                   |

| SEM  | scanning electron microscopy              |

|------|-------------------------------------------|

| TEM  | transmission electron microscopy          |

| STEM | scanning transmission electron microscopy |

| FIB  | focused ion beam                          |

| AFM  | atomic force microscopy                   |

| DIBT | drain-induced barrier thinning            |

| BTBT | band-to-band tunneling                    |

| NDR  | negative differential resistance          |

| EOT  | equivalent oxide thickness                |

| WKB  | Wentzel-Kramer-Brillouin                  |

| TG   | top-gate                                  |

| BG   | back-gate, or bottom-gate                 |

| DG   | double-gate                               |

| ADG  | asymmetric double-gate                    |

#### ABSTRACT

Since the discovery of graphene, two-dimensional (2D) materials have attracted broad interests for transistor applications due to their atomically thin nature. This thesis studies nano-transistors based on 2D materials for several novel applications, including tunneling transistors for low-power electronics and reconfigurable transistors for hardware security.

The first part of the thesis focuses on tunneling field-effect transistors (TFETs). Since the current injection in a conventional MOSFET depends on thermionic injection over a gatecontrolled barrier, the subthreshold swing (SS) of MOSFET is fundamentally limited to 60 mV/dec at room temperature, hindering the supply voltage scaling of integrated circuits (ICs). Utilizing band-to-band tunneling (BTBT) as current injection mechanism, TFETs overcome the SS limit by filtering out the Fermi tail in the source and achieve steep-slope switching. However, existing demonstrations of TFETs are plagued by low on-currents and degraded SS, largely due to the large tunneling distances caused by non-scaled body thicknesses, making 2D materials a promising candidate as channel materials for TFETs. In this thesis, we demonstrate a prototype TFET based on black phosphorus (BP) adopting electrostatic doping that is tuned by multiple top-gates, which allows the device to be reconfigured into multiple operation modes. The band-to-band tunneling mechanism is further confirmed by source-doping-dependent and temperature-dependent measurements, and the performance improvement of BP TFETs with further body and oxide thicknesses scaling is projected by atomistic simulation. In addition, a vertical BP TFET with a large tunneling area is also demonstrated, and negative differential resistance (NDR) is observed in the device.

The second part of the thesis focuses on reconfigurable nano-transistors with tunable pand n-type operations and the implementation of hardware security based on such transistors. Polymorphic gate has been proposed as a hardware security primitive to protect the intellectual property of ICs from reverse engineering, and its operation requires transistors that can be reconfigured between p-type and n-type. However, a traditional CMOS transistor relies on substitutional doping, and thus its polarity cannot be altered after the fabrication. By contrast, 2D nano-transistors can attain both electron and hole injections. In this thesis, we review the Schottky-barrier injection in 2D transistors and demonstrate the feasibility of achieving complementary p-type and n-type transistors using BP as channel material by adopting metal contacts with different work functions. In this design, however, the discrepancy in the p-FET and n-FET device structures makes it unsuitable for reconfigurable transistors. Therefore, we continue to modify the device design to enable reconfigurable ptype and n-type operations in the same BP transistor. Finally, a NAND/NOR polymorphic gate is experimentally demonstrated based on the reconfigurable BP transistors, showing the feasibility of using 2D materials to enable hardware security.

In the last part, we demonstrate an artificial sub-60 mV/dec switching in a metalinsulator-metal-insulator-semiconductor (MIMIS) transistor. Negative capacitance FETs (NC-FETs) have attracted wide interest as promising candidates for steep-slope devices. However, the detailed mechanisms of the observed steep-slope switching are under intense debate. We show that sub-60 mV/dec switching can be observed in a WS<sub>2</sub> transistor with an MIMIS structure – without any ferroelectric component. Using a resistor-capacitor (RC) network model, we show that the observed steep-slope switching can be attributed to the internal gate voltage response to the chosen varying gate voltage scan rates. Our results indicate that the measurement-related artefacts can lead to observation of sub-60 mV/dec switching and that experimentalists need to critically assess their measurement setups.

### 1. INTRODUCTION

Over the past decades, the continuous scaling down of metal-oxide-semiconductor field-effect transistors (MOSFETs), widely known as Moore's Law [1], has been the driving force of the ubiquitous application of integrated circuits (ICs). However, in recent years, several issues, including short-channel effects and slowing down of supply voltage ( $V_{DD}$ ) scaling, are hindering the continuation of Moore' Law, and the industry and research community are seeking more innovative solutions to these issues. Among these solutions, introducing novel nano-materials, such as two-dimensional (2D) materials, is of particular interest.

Since the debut of graphene in 2004 [2], 2D materials have remained a hot topic in the research community. Notably, after the demonstration of single layer  $MoS_2$  transistors in 2011 [3], 2D semiconducting materials, such as transition metal dichalcogenides (TMDs) [3]–[6], black phosphorus [7]–[9] and silicene [10], have been extensively studied for transistor applications, since they have the potential to become the ultimate solution to the scaling problem, thanks to their atomically thin nature. While significant efforts have been spent in applying 2D materials in traditional MOSFET to continue the scaling trend, which is known as *More Moore*, there also have been efforts in seeking novel applications leveraging the unique properties of the new materials, known as *More than Moore*, or *Beyond-CMOS*. In this thesis, we study two-dimensional material-based nano-transistors for such novel applications, including low-power tunneling field-effect transistors (TFETs) and reconfigurable transistors for hardware security.

#### 1.1 Two-dimensional semiconducting materials

Since the discovery of graphene, the idea of using graphene as channel material in transistor applications has attracted extensive studies, due to its atomically thin body thickness and ultra-high electron mobility (~ 15000 cm<sup>2</sup>/V · s) [11]. However, since graphene is a gapless semi-metal, the on-off ratios of graphene field-effect transistors (FETs) are typically less than 100, which limits its application in digital integrated circuits (ICs). Therefore, 2D semiconducting materials with bandgaps, such as transition metal dichalcogenides (TMDs) and black phosphorus (BP), are more attractive for transistor applications. Fig. 1.1 shows the atomic structures of two representative 2D materials, molybdenum disulfide  $[MoS_2, Fig. 1.1(a)]$  and BP [Fig. 1.1(b)]. These 2D materials are composed of stacks of atomic layers that are held together by van der Waals force, and each layer is less than 1 nm thick. The atomically thin body thicknesses make 2D semiconductors attractive for applications in ultra-scaled transistors and continuing Moore's Law.

Figure 1.1. Illustration of atomic structure of 2D materials. (a) Molybdenum disulfide (MoS<sub>2</sub>). (b) Black phosphorus (BP). Reprinted with permission from B. Radisavljevic *et al.*, "Single-layer MoS<sub>2</sub> transistors", *Nature Nanotechnology* 6, 147-150 (2011) & L. Li *et al.* "Black phosphorus field-effect transistors", *Nature Nanotechnology* 9, 372-377 (2014). Copyright (2011 & 2014) Springer Nature.

Compared with replacing Si with 2D materials to allow aggressive scaling of MOSFETs and continue Moore's Law, it is more appealing to study novel transistor applications based on the unique properties of 2D materials as a complement to conventional Si CMOS transistors. In the next few sections, we continue to discuss the rationale of incorporating 2D materials in nano-transistors to enable such novel applications, including tunneling fieldeffect transistors for low-power devices and reconfigurable transistors for hardware security.

#### 1.2 Tunneling field-effect transistors

Over the past decades, integrated circuits are seeing more and more applications due to the continuous improvement of performance and reduction of cost, both of which are enabled by Moore's Law. The driving force behind Moore's Law is the the continuous scaling of MOSFETs, following the Dennard scaling [12], or constant-field scaling. Dennard scaling states that for each new process node of MOSFETs, the gate length and width, power supply voltage  $V_{DD}$  and gate oxide thickness  $t_{ox}$  scale by 0.7×. Such scaling rule ensures that the power density of a chip is kept constant for each generation. However, in recent years, Dennard scaling has stopped functioning as a result of the slowing down of  $V_{DD}$  scaling, which is due to a fundamental limit of conventional MOSFET, and the power consumption of ICs has becomes a major issue ever since. To understand the issue, we need to study the operation principle of a MOSFET.

Figure 1.2. (a) Schematic and band diagram of a MOSFET, showing the thermionic emission. (b) The impact of minimum SS on  $V_{DD}$  scaling and off-state current.

Fig. 1.2 shows the schematic and the band diagram of an n-type MOSFET. Since the current injection in a conventional MOSFET is governed by thermionic emission over a barrier, the subthreshold swing (SS), *i.e.*, the amount of gate voltage required to change the current by one order of magnitude, is fundamentally limited to at least  $\ln(10) \times k_B T/q$ , which is ~60 mV/dec at room temperature [13]–[16]. Because the limitation of SS, further decreasing V<sub>DD</sub> while maintaining the same on-state current (in order not to affect the clock frequency, or equivalently, the speed of the circuit) would result in an exponential increase of off-state current, as shown in Fig. 1.2(b). Since a large-scale digital IC require low leakage currents of its component devices in order not to burn itself, such exponential increase is intolerable. As a result, Dennard scaling has ended and V<sub>DD</sub> scaling has nearly stopped since ~2003 [17], and the heat dissipation has become the main limiting factor of the increase of

clock speed and performance of digital circuits. Such issue has been termed as "Boltzmann tyranny", named after the Boltzmann distribution of electrons (or the Boltzmann constant  $k_B$  in the formula  $\ln(10) \times k_B T/q)^1$ . Therefore, steep-slope devices that overcome the SS limit are highly sought after.

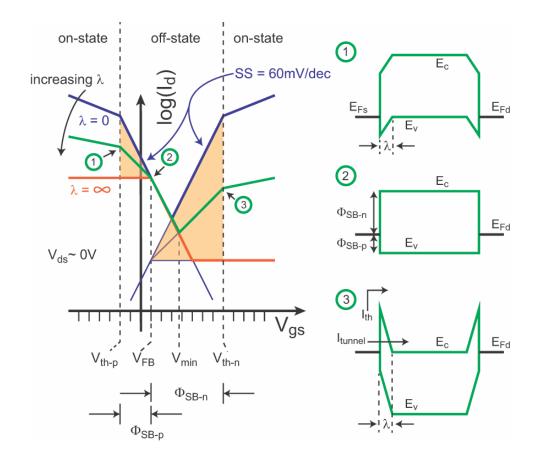

Tunneling field-effect transistors (TFETs) are proposed by J. Appenzeller *et al.* as a steep-slope device in 2004 [13], and in the same paper, a CNT TFET was demonstrated to exhibit a subthreshold swing of 40 mV/dec at 300 K.<sup>2</sup> TFET typically adopts a gated p-i-n structure (or n-i-p for p-type TFET), as shown in Fig. 1.3(a). The injection mechanism of a TFET is band-to-band tunneling (BTBT), instead of thermionic emission in conventional MOSFETs. The key for steep switching in TFETs is that the high energy part of the electron, or the Fermi tail, in the source is filtered out by the tunneling window, indicated by the green shade in Fig. 1.3(b), and thus the injected electrons into the channel are effectively "cooled down" by the band-pass filter [14], allowing an SS below 60 mV/dec. Fig. 1.3(b) shows a comparison of the transfer characteristics of a MOSFET and a TFET. In the ideal case, although the ON-current of a TFET may be lower than a MOSFET at large  $V_{DD}$  values due to the finite transmission of BTBT, after scaling to a lower supply voltage  $V'_{DD}$ , the ON-current of the TFET can be higher than the MOSFET due to a steeper SS.

In reality, however, most experimental TFETs exhibit low  $I_{on}$  values, as illustrated by the dashed red line in Fig. 1.3(b). Even though sub-60 mV/dec may be observed in the transfer characteristics, the corresponding current levels are too low for any practical applications. The reason behind the low currents is mainly due to a small transmission associated with the band-to-band tunneling through the barrier, which can be calculated based on the Wentzel-Kramer-Brillouin (WKB) approximation [27], [28]:

$$T_{BTBT}^{WKB} = \exp\left(\frac{-4\lambda\sqrt{2m^*E_g^3}}{3\hbar(\Delta\Phi + E_g)}\right)$$

(1.1)

<sup>&</sup>lt;sup>1</sup> $\uparrow$ In reality, Fermi-Dirac distribution should be used, yet Maxwell-Boltzmann distribution is a good approximation for the "tail" in the Fermi-Dirac distribution, which is responsible for the off-current in a MOSFET. <sup>2</sup> $\uparrow$ Before this work, several papers [18]–[26] already proposed the gated p-i-n structure, as some review articles of TFETs pointed out. However, it is worth mentioning that *none* of these early works mentioned the possibility of achieving sub-60 mV/dec operation using the structure – as a matter of fact, most of them were merely intended to propose a gated version of Esaki diode for a tunable NDR.

**Figure 1.3.** (a) Schematic and band diagram of a TFET, showing the bandto-band tunneling current injection path. (b) A comparison of MOSFET and TFET transfer characteristics.

The detailed analysis of the equation will be discussed in Chapter 2 of the thesis. Here, we are only focusing on the screening length  $\lambda$ . The tunneling probability has an exponential dependence on  $\lambda$ , which is in turn proportional to the square root of gate oxide thickness and body thickness, *i.e.*,  $\lambda \sim \sqrt{t_{ox}t_{body}}$ . Therefore, it is essential to decrease body thickness  $t_{body}$ in order to achieve a small  $\lambda$  and a large  $T_{BTBT}$ , which in turn leads a high on-current. Due to the atomically thin nature, 2D materials are a natural solution to the scaling problem in TFETs. In this thesis, we discuss the progress on demonstrating a prototype TFET with black phosphorus, an emerging 2D material, as channel material.

#### **1.3** Reconfigurable nano-transistors for hardware security

Hardware security has become a critical design consideration in modern IC industry besides the traditional metrics, such as performance, power consumption and cost. To prevent IP piracy, polymorphic gate [29] has been proposed as one of the hardware security measures that leverage emerging transistor technologies. As an example, Fig. 1.4 shows a NAND/NOR polymorphic gate built with nano-transistors that can be reconfigured between p-FET and n-FET operation modes. By swapping  $V_{DD}$  and GND, the pull-up network and the pull-down network can be interchanged, and thus the functionality of the circuit can be transformed between a NAND gate and a NOR gate. Without a prior knowledge to the circuit design, an extraction of the circuit layout via reverse engineering is unable to distinguish the intended functionality of the circuit. If N of such polymorphic gates are incorporated in an IC design, there are  $2^N$  combinations of possible functions in total, rendering the attacks extremely difficult with brute-force attacks. Such exponential increase ensures the security of the IC design from hardware level.

Figure 1.4. Schematic of a NAND/NOR polymorphic gate built with reconfigurable nano-transistors. Adapted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," *Nature Electronics* 4, 45-53 (2021). Copyright (2021) Springer Nature.

However, such implementation of the polymorphic gate cannot realized with traditional CMOS transistors, since the operation of CMOS transistors requires p-type or n-type substitutional doping in the source/drain regions for p-FETs and n-FETs, respectively, and as a result it is prohibitive to alter the polarity of a device post-fabrication. By contrast, 2D nano-transistors usually adopt doping-less structures and the current injection is governed by Schottky-barrier injection, of which the carrier type can be tuned by electrostatic doping [5], [8], [30]–[32]. Therefore, it is possible to achieve both electron and hole injection with good electrostatic gating and transparent enough Schottky barriers, both of which are attainable via proper device design. As an example, well-designed black phosphorus transistors exhibit ambipolar characteristics, as shown in Fig. 1.5. By applying a positive or negative gate voltage, either electron or hole can be allowed to be injected into the channel, and thus both pand n-branches can be observed in the device. Such operation requires a combination of the unique properties of BP, such as a moderate bandgap and near mid-gap Fermi level pinning from the metal-BP interface [8], [30], as well as an elaborate design of device structure, such as the correct selection of contact metal and a tight gate control ensured by the thin high- $\kappa$  dielectric and a double-gate structure. Details of the implementation will be discussed in the thesis.

Figure 1.5. An exemplary ambipolar BP transistor. (a) Schematic of an ambipolar BP transistor. (b) Transfer characteristics of the ambipolar BP transistor. Ambipolar characteristics are observed in the device. (c) Band diagrams of the BP ambipolar transistor corresponding to different gate voltages, showing the electron and hole injections. Adapted with permission from P. Wu, D. Reis, X. S. Hu, J. Appenzeller, "Two-dimensional transistors with reconfigurable polarities for secure circuits," *Nature Electronics* 4, 45-53 (2021). Copyright (2021) Springer Nature.

Having discussed the merits of the ambipolar BP transistors, an issue can also be identified from the characteristics shown in Fig. 1.5(b). As drain voltage  $V_d$  increases (or decreases for negative  $V_d$  values in a p-FET), the ambipolar injection from the drain is enhanced, leading to an increase in the off-state current. As discussed before, the merit of CMOS transistor is the low off-state current, which allows the integration of millions of devices without burning the chip. Therefore, the degradation of off-state current needs to be solved, and the solution will be discussed in details in the thesis.

#### 1.4 Organization

The organization of the thesis is as follows:

- Chapter 2 discusses BP tunneling field-effect transistors. Starting with a discussion of the unique properties that make BP an ideal candidate as channel materials for TFETs, we continue to demonstrate a prototype BP TFET, in which the electrostatic doping allows for reconfigurable operations between n-type and p-type conduction, as well as between MOSFET and TFET modes. Next, source-doping-dependent and temperature-dependent measurements confirm the band-to-band tunneling mechanism in the device. Finally, atomistic simulation is performed to project the performance improvement of BP TFETs by continue scaling down the body and oxide thicknesses.

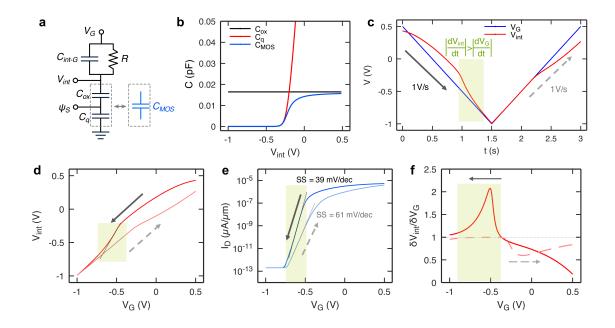

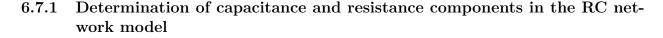

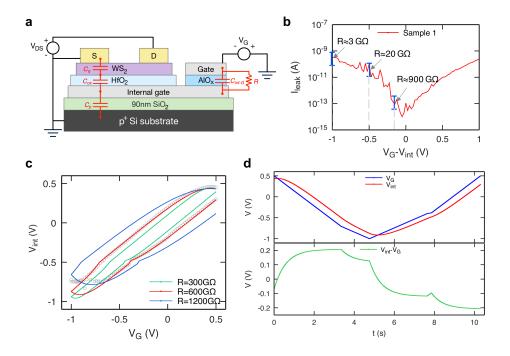

- Chapter 3 discusses vertical BP TFETs. We demonstrate a much larger tunneling current in the vertical structure compared with the lateral structure in Chapter 2, due to a larger tunneling area from the vertical overlapping region, and negative differential resistance (NDR) is observed in the vertical device. The vertical BP TFET also exhibits reconfigurable operations, similar to the lateral BP TFET in Chapter 2.