# SYSTEMS SUPPORT FOR DATA ANALYTICS BY EXPLOITING MODERN HARDWARE

by

Hongyu Miao

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana December 2021

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

Dr. Felix Xiaozhu Lin, Chair

Department of Computer Science, University of Virginia

## Dr. Kathryn S. McKinley

Google Inc.

## Dr. Mithuna S. Thottethodi

School of Electrical and Computer Engineering, Purdue University

## Dr. Y. Charlie Hu

School of Electrical and Computer Engineering, Purdue University

## Approved by:

Dr. Dimitrios Peroulis

School of Electrical and Computer Engineering, Purdue University

To my entire family.

## ACKNOWLEDGMENTS

I would like to thank my advisor, Prof. Felix Xiaozhu Lin, for his advice, help, and support. In addition to guidances in research, he also provided all resources I need to complete my PhD study, including equipments and fundings. As Felix's first PhD student, we fell into many traps and learned many lessons together in the first few years, which not only is a fortune for me but also paves the way for other/future PhD students in our group.

I would like to thank Dr. Kathryn S. McKinley for her advice, help, and support. In addition to guidance in research, her kindness, supportiveness, and responsiveness inspire me. If I had chances in the future, I would like to do the same thing to support junior people as what Kathryn did.

I would like to thank the rest of my committee, Prof. Y. Charlie Hu and Prof. Mithuna S. Thottethodi, for their feedback, questions, and discussions on my thesis work.

I would like to thank Prof. Gennady Pekhimenko and Prof. Myeongjae Jeon for their advice, help, and support through my MSR internship and follow-up collaborations.

Finally, I especially would like to thank my entire family for their long-term care, love, and support, so that I can focus on my PhD study. Without them, I could not have done it.

# Contents

| LI | ST O | <b>PF</b> TABLES                                  | 9  |

|----|------|---------------------------------------------------|----|

| LI | ST O | PF FIGURES                                        | 10 |

| A  | BSTR | RACT                                              | 12 |

| 1  | INT  | RODUCTION 1                                       | 14 |

|    | 1.1  | Data Analytics and Hardware Platforms             | 14 |

|    | 1.2  | Challenges to System Software (OS and Runtime)    | 15 |

|    | 1.3  | Thesis Overview                                   | 15 |

| 2  | STR  | EAMBOX: STREAM ANALYTICS ON A MULTICORE MACHINE 1 | 18 |

|    | 2.1  | Introduction                                      | 18 |

|    | 2.2  | Stream Model and Background                       | 19 |

|    | 2.3  | Design Goals and Criteria                         | 21 |

|    | 2.4  | System Overview                                   | 22 |

|    | 2.5  | Cascading Containers                              | 24 |

|    |      | 2.5.1 Container Implementation                    | 25 |

|    |      | 2.5.2 Single-input Transforms                     | 26 |

|    |      | 2.5.3 Multi-input Transforms                      | 28 |

|    |      | 2.5.4 Synchronized Access to Containers           | 30 |

|    | 2.6  | Pipeline Scheduling                               | 30 |

|    | 2.7  | Pipeline State Management                         | 31 |

|   |      | 2.7.1 Bundles                                         | 31 |

|---|------|-------------------------------------------------------|----|

|   |      | 2.7.2 Transform Internal State                        | 32 |

|   | 2.8  | Implementation                                        | 33 |

|   | 2.9  | Evaluation                                            | 34 |

|   |      | 2.9.1 Throughput and Scalability                      | 35 |

|   |      | 2.9.2 Validation of Key Design Features               | 38 |

|   | 2.10 | Related Work                                          | 40 |

|   | 2.11 | Summary                                               | 42 |

| 3 | STR  | EAMBOX-HBM: STREAM ANALYTICS ON HIGH BANDWIDTH HYBRID |    |

|   | MEN  | MORY                                                  | 44 |

|   | 3.1  | Introduction                                          | 44 |

|   | 3.2  | Background & Motivation                               | 46 |

|   |      | 3.2.1 Modern Stream Analytics                         | 47 |

|   |      | 3.2.2 Exploiting HBM                                  | 50 |

|   | 3.3  | System Overview                                       | 52 |

|   | 3.4  | KPA and Streaming Operations                          | 53 |

|   |      | 3.4.1 KPA                                             | 54 |

|   |      | 3.4.2 Streaming Operations                            | 56 |

|   |      | 3.4.3 Pipeline Execution Over KPAs                    | 59 |

|   | 3.5  | Dynamically Managing Hybrid Memory                    | 60 |

|   |                                                         | 3.5.1  | Memory Management and Resource Monitoring                                  | 63 |

|---|---------------------------------------------------------|--------|----------------------------------------------------------------------------|----|

|   | 3.6                                                     | Imple  | mentation and Methodology                                                  | 64 |

|   | 3.7                                                     | Evalua | ation                                                                      | 66 |

|   |                                                         | 3.7.1  | Comparing to Existing Engines                                              | 66 |

|   |                                                         | 3.7.2  | Throughput and Bandwidth                                                   | 69 |

|   |                                                         | 3.7.3  | Demonstration of Key Design Features                                       | 70 |

|   |                                                         | 3.7.4  | Impact of Data Parsing at Ingestion                                        | 72 |

|   | 3.8                                                     | Relate | ed Work                                                                    | 74 |

|   | 3.9                                                     | Summ   | ary                                                                        | 75 |

| 4 | SWAPNN: TOWARDS OUT-OF-CORE NEURAL NETWORKS ON TINY MI- |        |                                                                            |    |

|   | CRC                                                     | CONT   | ROLLERS                                                                    | 78 |

|   | 4.1                                                     | Introd | uction                                                                     | 78 |

|   | 4.2                                                     | Backg  | round and Motivations                                                      | 83 |

|   |                                                         | 4.2.1  | A Taxonomy of NN layers                                                    | 83 |

|   |                                                         | 4.2.2  | The System Model                                                           | 86 |

|   | 4.3                                                     | SwapN  | $IN$ : Automatically Scheduling IO/Compute Tasks in Parallel $\ .\ .\ .$ . | 88 |

|   |                                                         | 4.3.1  | Challenges                                                                 | 88 |

|   |                                                         | 4.3.2  | SwapNN Design                                                              | 89 |

|   | 4.4                                                     | Imple  | mentation & Methodology                                                    | 94 |

|   | 4.5                                                     | Findir | ıgs                                                                        | 96 |

|    |      | 4.5.1  | Software/Hardware Parameters and Their Tradeoffs                    | 96  |

|----|------|--------|---------------------------------------------------------------------|-----|

|    |      | 4.5.2  | Impact on Per-frame Delay                                           | 99  |

|    |      | 4.5.3  | Impact on NN Throughput                                             | 100 |

|    |      | 4.5.4  | Impact on Flash Durability                                          | 103 |

|    |      | 4.5.5  | Impact on System Energy                                             | 104 |

|    |      | 4.5.6  | Out-of-core Data Security and Safety                                | 105 |

|    | 4.6  | Relate | d Work                                                              | 106 |

|    | 4.7  | Summ   | ary                                                                 | 107 |

| 5  | CON  | ICLUSI | ON                                                                  | 108 |

|    | 5.1  | Thesis | Contributions                                                       | 108 |

|    |      | 5.1.1  | System Support for Stream Processing on Cloud Hardware              | 108 |

|    |      | 5.1.2  | System Support for Machine Learning Inference on Edge Hardware .    | 109 |

|    | 5.2  | Genera | al Lessons and Hints for Runtime System Designs                     | 111 |

|    |      | 5.2.1  | Apps: Algorithms Adapting to Hardware Changes                       | 111 |

|    |      | 5.2.2  | Runtime: Better Managing Resources than General Hardware and OS     | 112 |

|    |      | 5.2.3  | OS: Configuring Kernel Parameters Accordingly                       | 112 |

|    |      | 5.2.4  | Hardware: Choosing Hardware Based on Applications' Demand $\ . \ .$ | 113 |

| Rł | EFER | ENCES  | 5                                                                   | 114 |

# LIST OF TABLES

| 2.1 | Terminology                                                                                                                                                            | 19 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Test platforms used in experiments                                                                                                                                     | 34 |

| 3.1 | Selected compound (declarative) operators in StreamBox-HBM and their constituent streaming primitives.                                                                 | 47 |

| 3.2 | KPA primitives. $\mathscr{R}$ denotes a record bundle. $KPA(c)$ denotes a KPA with resident keys from column $c$ .                                                     | 55 |

| 3.3 | Selected compound (declarative) operators in StreamBox-HBM and their constituent streaming primitives.                                                                 | 56 |

| 3.4 | KNL and Xeon Hardware used in evaluation                                                                                                                               | 66 |

| 4.1 | Normalized arithmetic intensity $(N)$ on NN layers with MCU's common speed<br>range (64–480 MOPS [124], [125]) and IO bandwidth range (10–40 MB/s [126]).<br>NN: VGG16 | 83 |

| 4.2 | Number of IO-bound and compute-bound layers and quantized memory footprints of popular NNs [128]                                                                       | 84 |

# LIST OF FIGURES

| 1.1  | An overview of the thesis work                                                                                                                                                                                                   | 16 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | A transform in a StreamBox pipeline                                                                                                                                                                                              | 22 |

| 2.2  | An overview of cascading containers                                                                                                                                                                                              | 24 |

| 2.3  | The life cycle of a container                                                                                                                                                                                                    | 24 |

| 2.4  | A logic diagram of OOP temporal join                                                                                                                                                                                             | 27 |

| 2.5  | Unordered containers for Join and its downstream. For brevity, container watermarks are not drawn                                                                                                                                | 29 |

| 2.6  | Throughput of StreamBox as a function of hardware parallelism and latency. StreamBox scales well.                                                                                                                                | 34 |

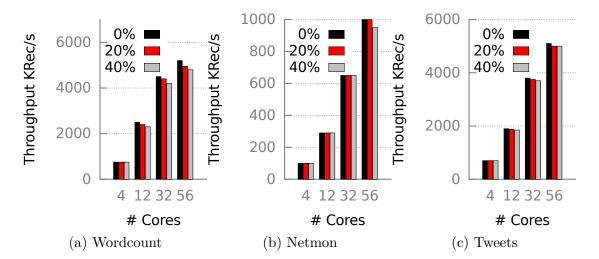

| 2.7  | StreamBox achieves high throughput even when a large fraction of records arrive out-of-order.                                                                                                                                    | 36 |

| 2.8  | StreamBox scales better than Spark and Beam with Wordcount on 56CM, with a 1-second target latency.                                                                                                                              | 37 |

| 2.9  | In-order processing reduces parallelism, scalability, and throughput                                                                                                                                                             | 38 |

| 2.10 | When records do not respect epoch boundaries, it limits parallelism, scalabil-<br>ity, and throughput.                                                                                                                           | 39 |

| 2.11 | Performance impact of watermark arrival rate for Wordcount on 56CM                                                                                                                                                               | 40 |

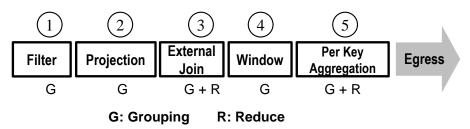

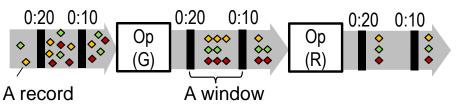

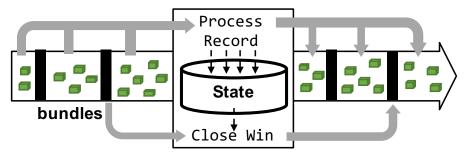

| 3.1  | Example streaming data and computations                                                                                                                                                                                          | 48 |

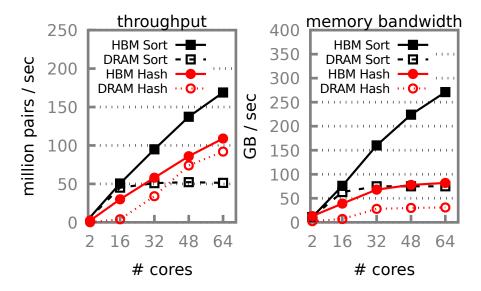

| 3.2  | GroupBy on HBM and DRAM operating on 100M key/value records with<br>about 100 values per key. Keys and values are 64-bit random integers. Sort<br>leverages HBM bandwidth with sequential access and outperforms Hash on<br>HBM. | 51 |

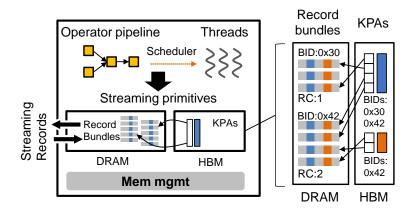

| 3.3  | An overview of StreamBox-HBM using record bundles and KPAs. RC: refer-                                                                                                                                                           |    |

| 0.0  | ence count; BID: bundle ID                                                                                                                                                                                                       | 53 |

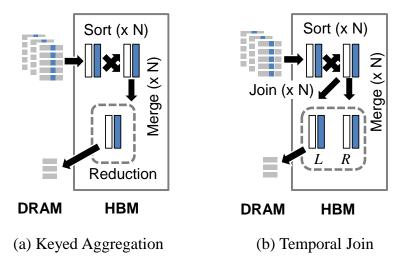

| 3.4  | Declarative operators implemented atop KPAs                                                                                                                                                                                      | 58 |

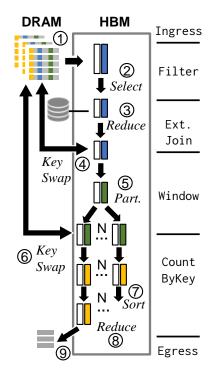

| 3.5  | Pipeline execution on KPAs for YSB [59]. Declarative operators shown on right.                                                                                                                                                   | 60 |

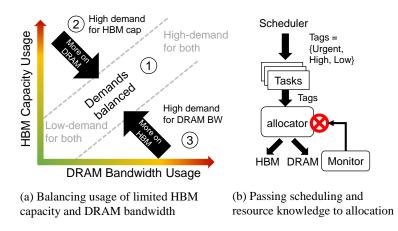

| 3.6  | StreamBox-HBM dynamically manages hybrid memory                                                                                                                                                                                  | 61 |

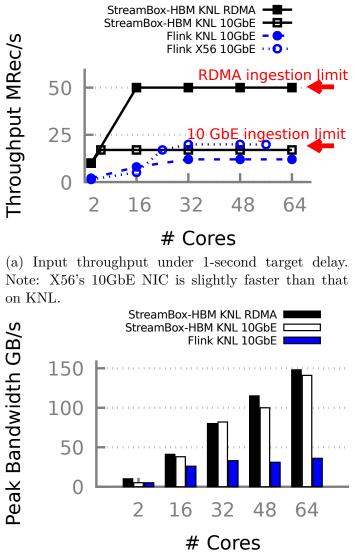

| 3.7  | StreamBox-HBM achieves much higher throughput and memory bandwidth usage than Flink, quickly saturating IO hardware. Legend format: "Engine Machine IO". Benchmark: YSB [59]                                                     | 68 |

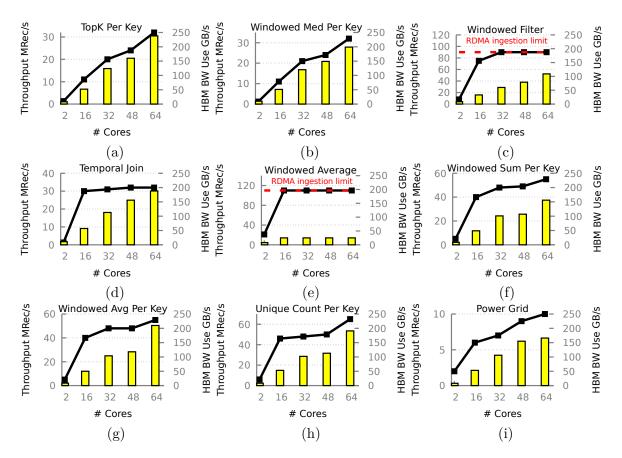

| 3.8  | StreamBox-HBM's throughput (as lines, y-axis on left) and peak bandwidth utilization of HBM (as columns, y-axis on right) under 1-second target output delay. StreamBox-HBM shows good throughput and high memory bandwidth usage                                                                        | 69  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

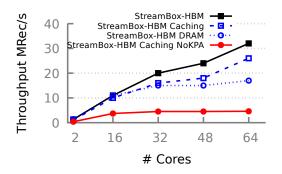

| 3.9  | StreamBox-HBM outperforms alternative implementations, showing the effic-<br>acy of KPA and its management of hybrid memory. Benchmark: TopK Per<br>Key                                                                                                                                                  | 71  |

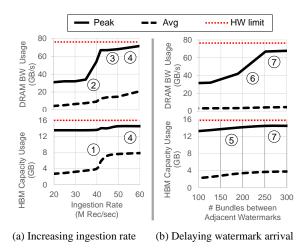

| 3.10 | StreamBox-HBM dynamically balances its demands for limited memory resources under varying workloads. Benchmark: TopK Per Key                                                                                                                                                                             | 71  |

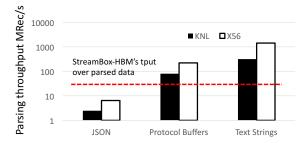

| 3.11 | Parsing at the ingestion shows varying impacts on the system throughput. All cores on KNL and X56 are in use. Parsers: RapidJSON [90], Protocol Buffers (v3.6.0) [91], and text strings to uint64 [92]. Benchmark: YSB                                                                                   | 73  |

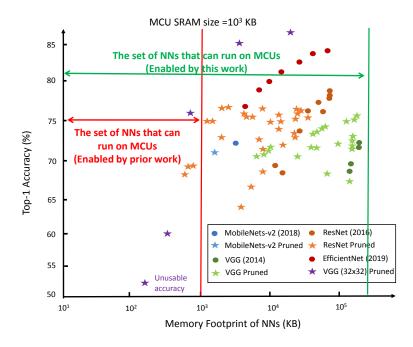

| 4.1  | Many popular NNs exceed the MCU memory size [110]                                                                                                                                                                                                                                                        | 79  |

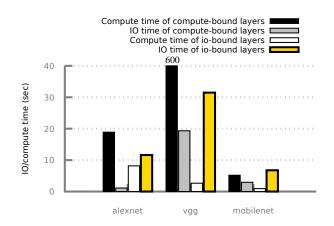

| 4.2  | Per-layer compute and IO delays in NNs. (1) Observation: NNs have a mix of IO-bound and compute-bound layers. (2) Insight: IO time can be hidden by compute time with parallel execution. (3) Configuration: MCU is ARM Cortex-M7 @ 216 MHz, tile/buffer size is 128 KB, Transcend SD card size is 32 GB | 84  |

| 4.3  | IO/compute delays in out-of-core NN execution. The total execution delay is dominated by compute in the compute-bound layers and IO in the IO-bound layers.                                                                                                                                              | 85  |

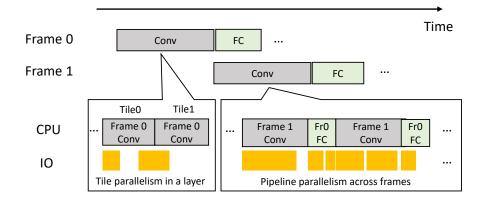

| 4.4  | An example of out-of-core NN execution, showing Conv (compute-bound) and FC (IO-bound) layers. Note: gray/green boxes show the computation of NN layers in NN layers/frames, and yellow boxes show the IO operation in NN layers/frames.                                                                 | 87  |

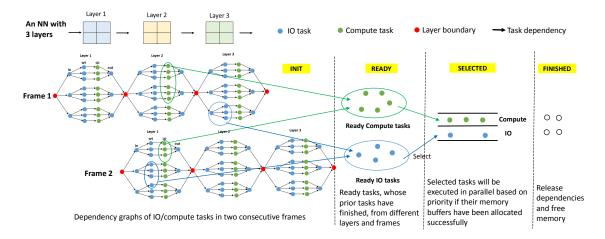

| 4.5  | Overview of SwapNN: scheduling IO/compute tasks across tiles, layers, and frames in parallel according to dependencies, priorities, and memory constraints.                                                                                                                                              | 88  |

| 4.6  | Swapping latency of NNs with different SRAM sizes and buffer sizes. Observation: swapping incurs negligible or modest delay in latency.                                                                                                                                                                  | 95  |

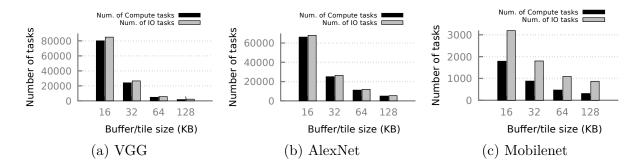

| 4.7  | Number of IO/compute tasks in NNs under different buffer/tile sizes. Observation: the number of IO/compute tasks drops significantly as the buffer/tile size increases.                                                                                                                                  | 97  |

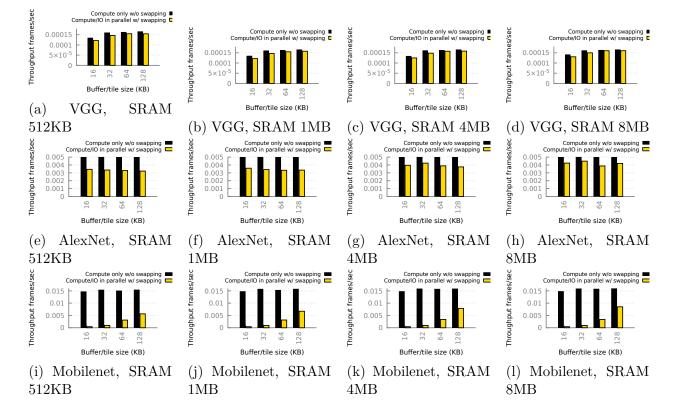

| 4.8  | Swapping throughput of NNs under differt SRAM sizes and buffer/tile sizes.                                                                                                                                                                                                                               | 101 |

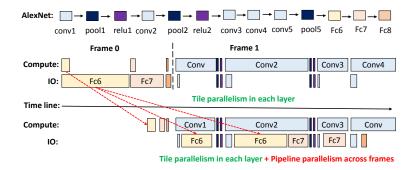

| 4.9  | AlexNet: tile parallelism for low delay and pipeline parallelism for high through-<br>put.                                                                                                                                                                                                               | 104 |

| 5.1  | Lessons on exploiting multicore and hybrid memory systems                                                                                                                                                                                                                                                | 110 |

## ABSTRACT

A large volume of data is continuously being generated by data centers, humans, and internet of things (IoT). In order to get useful insights, such enormous data must be processed in time with high throughput, low latency, and high accuracy. To meet such performance demands, a large body of new hardware is being shipped by vendors, such as multi-core CPUs, 3D-stacked memory, embedded microcontrollers, and other accelerators.

However, traditional operating systems (OSes) and data analytics frameworks, the key layer that bridges high-level data processing applications and low-level hardware, fails to deliver these requirements due to quickly evolving new hardware and increases in explosion of data. For instance, general OSes are not aware of the unique characters and demands of data processing applications. Data analytics engines for stream processing, e.g., Apache Spark and Beam, always add more machines to deal with more data but leave every single machine underutilized without fully exploiting underlying hardware features, which leads to poor efficiency. Data analytics frameworks for machine learning inference on IoT devices cannot run neural networks that exceed SRAM size, which disqualifies many important use cases.

In order to bridge the gap between the performance demands of data analytics and the new features of emerging hardware, in this thesis we exploit runtime system designs for high-level data processing applications by exploiting low-level modern hardware features. We study two important data analytics applications, including real-time stream processing and on-device machine learning inference, on three important hardware platforms across the Cloud and the Edge, including multicore CPUs, hybrid memory system combining 3Dstacked memory and general DRAM, and embedded microcontrollers with limited resources.

In order to speed up and enable the two data analytics applications on the three hardware platforms, this thesis contributes three related research projects. In project StreamBox, we exploit the parallelism and memory hierarchy of modern multicore hardware on single machines for stream processing, achieving scalable and highly efficient performance. In project StreamBox-HBM, we exploit hybrid memories to balance bandwidth and latency, achieving memory scalability and highly efficient performance. StreamBox and StreamBox-

HBM both offer orders of magnitude performance improvements over the prior state of the art, opening up new applications with higher data processing needs. In project SwapNN, we investigate a system solution for microcontrollers (MCUs) to execute neural networks (NNs) inference out-of-core *without losing accuracy*, enabling new use cases and significantly expanding the scope of NN inference on tiny MCUs.

We report the system designs, system implementations, and experimental results. Basing on our experience in building above systems, we provide general guidances on designing runtime systems across hardware/software stack for a wider range of new applications on future hardware platforms.

## 1. INTRODUCTION

#### **1.1 Data Analytics and Hardware Platforms**

#### Data analytics

Data is growing exponentially. Every day, about 2.5 quintillion bytes of date is continuously being produced by data centers, humans, and Internet of Things (IoT) devices. For instance, we post half a million Tweets and generate four petabytes of data on Facebook per day. The trend of data growing will continue, reaching 463 exabytes of data per day in 2025 [1]. In order to extract useful insights from the large volume of data, data analytics has become one of the most important workloads.

Stream processing is one of the central paradigms of modern data analytics. Stream data consists of unbounded numbers of records. Each record includes one or more data values and a time stamp which indicates when the record was generated. The use cases of stream processing span many domains, such as tweet sentiment analysis, fraud detection in businesses, and log monitoring in data centers. Stream processing has an insatiable demand for high throughput and low latency.

Machine learning (ML) inference is another central paradigm of modern data analytics. It is the process of using a trained machine learning algorithm to make a prediction. The more data, the better the accuracy of its predictions. For example, object detection, traffic monitoring, and self driving all benefit from more data.

#### Hardware platforms

To meet the performance demands of data analytics, a large body of new hardware platforms are being shipped by hardware vendors. These new hardware platforms are very diverse and they target different performance goals, such as computation speed, memory bandwidth, and energy efficiency. Based on deployment scenarios, they can be classified into two categories.

Cloud hardware: Cloud is one of the most important platforms for data analytics. Due to the large volume of data, new hardware in cloud focus on improving computation speed and memory speed. For instance, many-core CPUs have tens to hundreds of cores, which can speed up data analytics with high parallelism. 3D-stacked memory has 5 times higher bandwidth than general DRAM, so they can speed up data analytics by moving data faster.

Edge hardware: To avoid the costs of sending data to Cloud, there is a trend to push data analytics tasks to Edge IoT devices, driven by the new applications, such as smart homes, smart cities, and autonomous driving. On-device data analytics at the edge is attractive because it saves network bandwidth and preserves data privacy. Due to the constraints of cost and energy, IoT devices are resource-constraint and they focus on efficiency. For example, microcontrollers-based cameras and sensors have very tiny memory and battery.

### 1.2 Challenges to System Software (OS and Runtime)

The fast evolution in varying performance demands of data analytics applications and in varying new features of emerging hardware platforms brings significant challenges to existing system software, including operating systems and data analytics runtimes.

General operating systems are not aware of the unique characters and demands of data analytics applications. General OSes are designed for all kinds of applications and aim to achieve reasonable performance for all of them. They cannot adapt to the unique demands of one specific application. Therefore, the optimization space for specific data analytics in OSes is limited.

Existing data analytics systems are not aware of the unique features of underlying hardware. They are well optimized for fault tolerance, scalability, and consistency, like Spark Streaming and Apache Beam. They always try to add more machines to deal with more data, but neglect the optimization for single machine with new hardware features, which wastes resources.

#### 1.3 Thesis Overview

The theme of this thesis is to provide systems support for data analytics by exploiting modern hardware. The goal of the thesis is to achieve high performance for data analytics on

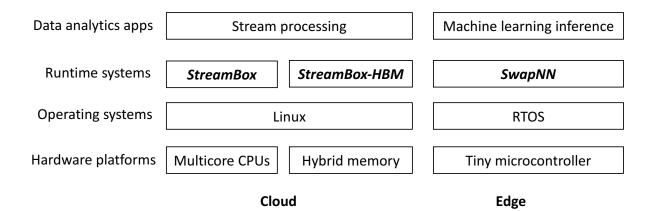

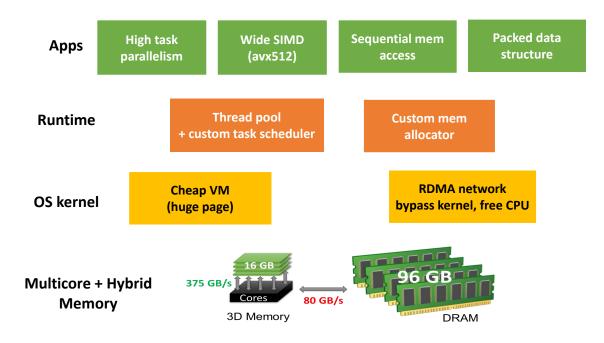

Figure 1.1. An overview of the thesis work

advanced hardware platforms in the Cloud and enable on-device data analytics on resourceconstraint hardware platforms at the Edge.

An overview of the thesis work is shown in Figure 1.1. We study two types of data analytics workloads, including stream processing and machine learning inference, on three types of hardware platforms across Cloud and Edge, including multicore CPUs, hybrid memory, and tiny microcontrollers.

Chapter 2 presents *StreamBox* [2], a stream analytics engine that exploits hardware parallelism of modern multicore machine, achieving scalable and highly efficient performance. We introduce a novel data structure called cascading containers to track dependences between epochs while at the same time processing any available records in any epoch. The key contribution of this work is a generalization of out-of-order record processing to out-of-order epoch processing that maximizes parallelism while minimizing synchronization overheads. Experimental results show our system scales to a large number of cores and out performs other state of the art engines. On the 56-core system, **StreamBox** reduces latency by a factor of 20 over Spark Streaming [3] and matches the throughput of results of Spark and Apache Beam [4] on medium-size clusters of 100 to 200 CPU cores for *grep* and *wordcount* queries.

Chapter 3 presents *StreamBox-HBM* [5], the first stream analytics engine that optimizes performance for hybrid memory combining high bandwidth memory (HBM) and DRAM, achieving memory scalability and highly efficient performance. Our design addresses the limited capacity of HBM and HBM's need for sequential-access and high parallelism. We introduce a novel dynamic key/record pointer extraction called KPA that minimizes the use of precious HBM capacity. We use sequential grouping algorithms on KPAs to balance limited capacity while exploiting high bandwidth. We design a runtime that manages parallelism and KPA placement in hybrid memories. Our system outperforms engines without KPA and with sequential-access algorithms by 7x and engines with random-access algorithms by an order of magnitude.

Chapter 4 presents *SwapNN* [6], the first system that enables high-accuracy neural network (NN) inference on extremely resource-constraint microcontrollers *without* losing accuracy, enabling new use cases and significantly expanding the scope of NN inference on tiny MCUs. Running neural networks (NNs) on microcontroller units (MCUs) is becoming increasingly important (e.g., tolerating poor networks and preserving data privacy), but is very difficult due to the tiny SRAM size of MCU. Prior work proposes many algorithm-level techniques to reduce NN memory footprints, but all at the cost of sacrificing accuracy and generality, which disqualifies MCUs for many important use cases. We investigate a system solution for MCUs to execute NNs out of core: dynamically swapping NN data chunks between an MCU's tiny SRAM and its large, low-cost external flash. Out-of-core NNs on MCUs raise multiple concerns: execution slowdown, storage wear out, energy consumption, and data security. We present a study showing that none is a showstopper; the key benefit – MCUs being able to run large NNs with full accuracy and generality – triumphs the overheads. Our findings suggest that MCUs can play a much greater role in edge intelligence.

Chapter 5 first summarizes the thesis work. It then presents the lessens we learned through building above systems and presents our general guidances on designing runtime systems across hardware/software stack for a wider range of new applications on future hardware platforms: (1) in application level, algorithms should adapt to hardware changes; (2) in runtime level, it's better managing resources than general hardware and OS, because runtime can leverage both applications' unique demand and hardware's unique features. (3) in OS level, kernel parameters should be configured accordingly to reduce OS overhead, e.g., enabling huge page and RDMA. (4) in hardware level, choosing hardware should be based on applications' demand.

# 2. STREAMBOX: STREAM ANALYTICS ON A MULTICORE MACHINE

### 2.1 Introduction

Stream processing is a central paradigm of modern data analytics. Stream engines process unbounded numbers of records by pushing them through a pipeline of *transforms*, a continuous computation on records [7]. Records have *event* timestamps, but they may arrive out-of-order, because records may travel over diverse network paths and computations on records may execute at different rates. To communicate stream progression, transforms emit timestamps called *watermarks*. Upon receiving a watermark  $w_{ts}$ , a transform is guaranteed to have observed all prior records with *event* time  $\leq ts$ .

Most stream processing engines are distributed because they assume processing requirements outstrip the capabilities of a single machine [3], [8], [9]. However, modern hardware advances make a single multicore machine an attractive streaming platform. These advances include (i) high throughput I/O that significantly improves ingress rate, e.g., Remote Direct Memory Access (RDMA) and 10Gb Ethernet; (ii) terabyte DRAMs that hold massive in-memory stream processing state; and (iii) a large number of cores. This work seeks to maximize streaming throughput and minimize latency on modern multicore hardware, thus reducing the number of required machines to process streaming workloads.

Stream processing on a multicore machine raises three major challenges. First, the streaming engine must extract parallelism aggressively. Given a set of transforms  $\{d_1, d_2, \dots, d_n\}$  in a pipeline, the streaming engine should exploit (i) pipeline parallelism by simultaneously processing all the transforms on different records in the data stream and (ii) data parallelism on all the available records in a transform. Second, the engine must minimize thread synchronization while respecting dependences. Third, the engine should exploit the memory hierarchy by creating sequential layout and minimizing data copying as records flow through various transforms in the pipeline.

| Term      | Definition                                    |

|-----------|-----------------------------------------------|

| Stream    | An unbounded sequence of records              |

| Transform | A computation that consumes and produces      |

|           | streams                                       |

| Pipeline  | A dataflow graph of transforms                |

| Watermark | A special event timestamp for marking         |

|           | stream progression                            |

| Epoch     | A set of records arriving between two water-  |

|           | marks                                         |

| Bundle    | A set of records in an epoch (processing unit |

|           | of work)                                      |

| Evaluator | A worker thread that processes bundles and    |

|           | watermarks                                    |

| Container | Data structure that tracks watermarks,        |

|           | epochs, and bundles                           |

| Window    | A temporal processing scope of records        |

Table2.1. Terminology

#### 2.2 Stream Model and Background

This section describes our out-of-order stream processing model and terminology, summarized in Table 2.1.

**Streaming pipelines** A stream processing engine receives one or more streams of *records* and performs a sequence of transforms  $\mathcal{D} = \{d_1, d_2, \cdots, d_n\}$  on the records  $\mathcal{R}$ . Each record  $r_{ts} \in \mathcal{R}$  has a timestamp ts for temporal processing. A record has an *event* timestamp defined by its occurrence (e.g., when a sensor samples a geolocation). Ingress of a record to the stream engine determines its *arrival* timestamp.

**Out-of-order streaming** Because data sources are diverse, records travel different paths, and transforms operate at different rates, records may arrive *out-of-order* at the stream processing engine or to individual transforms. To achieve low latency, the stream engine must *continuously* process records and thus cannot stall waiting for event and arrival time to align. We adopt the out-of-order processing (OOP) [10] paradigm based on *windows* to address this challenge.

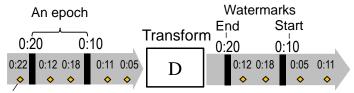

Watermarks and stream epochs Ingress and transforms emit strictly monotonic event timestamps called *watermarks*  $w_{ts}$ , as exemplified in Figure 2.1(a). A watermark guarantees no subsequent records will have an event time earlier than ts. At ingress, watermarks delimit ordered consecutive *epochs* of records. An epoch may have records with event timestamps greater than the epoch's end watermark due to out-of-order arrival. The stream processing engine may process records one at a time or in *bundles*.

We rely on stream sources and transforms to create watermarks based on their knowledge of the stream data [7], [11]. We do not inject watermarks (as does prior work [12]) to force output and manage buffering.

**Pipeline egress** Transforms define event-time windows that dictate the granularity at which to output results. Because we rely on watermarks to define streaming progression, the rate of egress is bounded by the rate of watermarks, since a transform can only close a window after it receives a watermark. We define the *output delay* in a pipeline from the time it first receives the watermark  $w_{ts}$  that signals the completion of the current window to the moment when it delivers the window results to the user. This critical path is implicit in the watermark timestamps. It includes processing any remaining records in epochs that precede  $w_{ts}$  and processing  $w_{ts}$  itself.

**Programming model** We use the popular model from timely dataflow [13], Google dataflow [7], and others. To compose a pipeline, developers declare transforms and define dataflows among transforms. This is exemplified by the following code that defines a pipeline for Windowed Grep, one benchmark used in our evaluation (§3.7).

```

// 1. Declare transforms

Source<string> source(/*config info*/);

FixedWindowInto<string> fwi(seconds(1));

WindowedGrep<string>wingrep(/*regexp*/);

Sink<string> sink();

// 2. Create a pipeline

Pipeline* p = Pipeline::create();

p->apply(source); //set source

// 3. Connect transforms together

connect_transform(source, fwi);

connect_transform(fwi, wingrep);

connect_transform(wingrep, sink);

// 4. Evaluate the pipeline

```

```

Evaluator eval(/*config info*/);

eval.run(p); // run the pipeline

```

To implement a transform, developers must define the following functions, as shown in Figure 2.1(b): (i) ProcessRecord(r) consumes a record r and may emit derived records. (ii) ProcessWm(w) consumes a watermark w, flushes the transform's internal state, and may emit derived records and watermarks. ProcessWm(w) is always invoked only after ProcessRecord(r) consumes all records in the current epoch.

### 2.3 Design Goals and Criteria

We seek to exploit the potential of modern multicore hardware with its abundant hardware parallelism, memory capacity, and I/O bandwidth for high throughput and low latency. A key contribution of this work is exploiting *epoch parallelism* by concurrently processing all available epochs in every transform, in addition to pipeline parallelism. Epoch parallelism generalizes the idea of processing the records in each epoch out-of-order by processing epochs out-of-order. The following two invariants ensure correctness:

(1) Records respect epoch boundaries Each epoch is defined by a start watermark  $w_{start}$  and an end watermark  $w_{end}$  that arrive at ingress at time start and end, and consists only of records  $r_{at}$  that arrive at ingress at time at, with start < at < end. Once an ingress record  $r_{at}$  is assigned an epoch, records never changed epochs, since this change might violate the watermark guarantee.

(2) Watermark ordering A transform D may only consume  $w_{end}$  after it consumes all the records r in the epoch. This invariant transitively ensures that watermarks and epochs are processed in order, and is critical to pipeline correctness, as it enforces the progression contract on ingress and between transforms.

Our primary design goal is to minimize latency by exploiting epoch and pipeline parallelism with minimal synchronization while maintaining these invariants. In particular, our engine processes unconsumed records using all available hardware resources regardless of record ordering, delayed watermarks, or epoch ordering. We further minimize latency by exploiting the multicore memory hierarchy (i) by creating sequential memory layout and minimizing data movement, and (ii) by mapping streaming data flows to the NUMA architecture.

### 2.4 System Overview

#### A record

(a) A logic view of a transform, which consumes and produces out-of-order records as delimited by watermarks

(b) A transform in StreamBox. It is executed to consume and produce records belonging to multiple epochs in parallel.

Figure 2.1. A transform in a StreamBox pipeline.

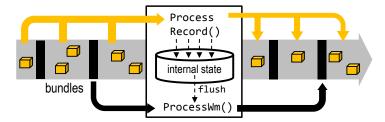

A StreamBox pipeline includes multiple transforms and each transform has multiple containers. Each container is linked to a container in a downstream transform or egress. Containers form a network pipeline organization, as depicted in Figure 2.2. Records, derived records, and watermarks flow through the network by following the links. A window consists of one or more epochs. The window size determines the output aggregation and memory layout, but otherwise does not influence how **StreamBox** manages epochs.

This dataflow pipeline network is necessary to exploit parallelism because parallelism emerges dynamically as a result of variation in record arrival times and the variation in processing times of individual records and watermarks for different transforms. For instance, records, based on their content, may require variable amounts of processing. Furthermore, it is typically faster to process a record than a watermark. However, exposing this abundant record processing parallelism and achieving low latency require prioritizing containers on the critical path through the network. StreamBox prioritizes records in containers with timestamps preceding the pipeline's upcoming output watermark. Otherwise, the scheduler processes records from transforms with the most open containers. StreamBox thus dynamically adds parallelism to the bottleneck transforms of the network to optimize latency.

StreamBox implements three core components:

Elastic pipeline execution StreamBox dynamically allocates worker threads (*evaluators*) from a pool to transforms to maximize CPU utilization. StreamBox pins each evaluator to a CPU core to limit contention. During execution, StreamBox dispatches pending records and watermarks to evaluators. An evaluator executes transform code (i.e., ProcessRecord() or ProcessWm()) and produces new records and watermarks that further drive the execution of downstream transforms.

When dispatching records, StreamBox packs them into variable sized *bundles* for processing to amortize dispatch overhead and improve throughput. Bundles differ from batches in many other streaming engines [3], [9], [12]. First, bundle size is completely orthogonal to the transform logic and its windowing scheme. StreamBox is thus at liberty to vary bundle size dynamically per transform, trading dispatch latency for overhead. Second, dynamically packing records in bundles does not delay evaluators and imposes little buffering delay. StreamBox only produces sizable bundles when downstream transforms back up the pipeline. Cascading containers Each container belongs to a transform and tracks one epoch, its state (*open, processing, or consumed*), the relationship between the epoch's records and its

state (*open, processing,* or *consumed*), the relationship between the epoch's records and its end watermark, and the output epoch(s) in the downstream consuming transform(s). Each transform owns a set of containers for its current input epochs. With this container state, executers may concurrently consume and produce records in *all* epochs without breaking or relaxing watermarks.

**Pipeline state management** StreamBox places records belonging to the same temporal windows (one or more adjacent epochs) in contiguous memory chunks. It adapts a bundle's internal organization of records, catering to data properties, e.g., the number of values per key. StreamBox steers bundles so that they flow mostly within their own NUMA nodes rather than across nodes. To manage transform internal state, StreamBox instantiates a contiguous

array of *slides* per transform, where each slide holds processing results for a given event-time range, e.g., a window. Evaluators operate on slide arrays based on window semantics, which are independent of the epoch tracking mechanism – cascading containers. The slide array realization incurs low synchronization costs under concurrent access.

### 2.5 Cascading Containers

Figure 2.2. An overview of cascading containers

Figure 2.3. The life cycle of a container

Cascading containers track epochs and orchestrate concurrent evaluators (i) to consume all of an epoch's records before processing its end watermark, (ii) to consume watermarks in stream order, and (iii) to emit records derived from an upstream epoch into the corresponding downstream epoch(s).

Figure 2.2 shows the cascading container design. Each transform owns a set of input stream containers, one for each potential epoch. When StreamBox creates a container uc, it

creates one downstream container dc (or more) for its output in the downstream transform(s) and links to it, causing a cascade of container creation. It puts all records and watermarks derived from the transform on uc into this corresponding downstream container dc. All these containers form a pipeline network. As stream processing progresses, the network topology evolves. Evaluators create new containers, establish links between containers, and destroy consumed containers.

#### 2.5.1 Container Implementation

StreamBox initializes a container  $D_{own}$  when the transform receives the first input record or bundle of an epoch. Each container includes any unclaimed bundles of the epoch. An *unconsumed* counter tracks the number of bundles that ever entered the container but are not fully consumed. After processing a bundle,  $D_{own}$  deposits derived output bundles in the downstream container and then updates the unconsumed counter.

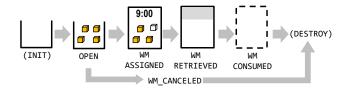

**Container state** StreamBox uses a container to track an epoch's life cycle as follows and shown in Figure 2.3.

- **open** Containers are initially empty. An open container receives bundles from the immediate upstream  $D_{up}$ . The owner  $D_{own}$  processes the bundles simultaneously.

- **wm\_assigned** When  $D_{up}$  emits an epoch watermark w, it deposits w in  $D_{own}$ 's dependent container. Eventually  $D_{own}$  consumes all bundles in the container and the *unconsumed* counter drops to zero, at which point  $D_{own}$  retrieves and processes the end watermark.

- **wm\_retrieved** A container enters this state when  $D_{own}$  starts processing the end watermark.

- **wm\_consumed** After  $D_{own}$  consumes the end watermark, it guarantees that it has flushed all derived state and the end watermark to the downstream container and  $D_{own}$  may be destroyed.

- **wm\_cancelled**  $D_{up}$  chooses not to emit the end watermark for the (potential) epoch. Section 2.5.2 describes how we support windowing transforms by cancelling watermarks and merging containers.

Lock-free container processing Containers are lock-free to minimize synchronization overhead. We instantiate the end watermark as an atomic variable that enforces acquirerelease memory order. It ensures that  $D_{own}$  observes all  $D_{up}$  evaluators' writes to the container's unclaimed bundle set before observing  $D_{up}$ 's write of the end watermark. The unclaimed bundle set is a concurrent data structure that aggressively weakens the ordering semantics on bundles for scalability. Examples of other such data structures include nonlinearizable lock-free queues [14] and relaxed priority queues [15]. We further exploit this flexibility to make the bundle set NUMA-aware, as discussed in Section 2.7.1.

#### 2.5.2 Single-input Transforms

If a transform has only one input stream, all its input epochs – and therefore the containers – are ordered, even though records are not.

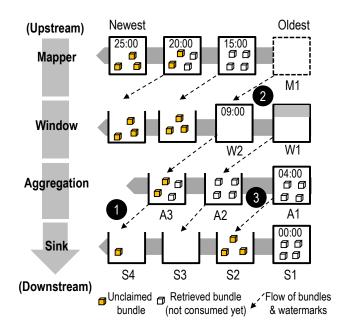

**Creating containers** The immediate upstream container  $D_{up}$  creates downstream containers on-demand and links to them. Figure 2.2 shows an example of container creation. When **StreamBox** processes the first bundle in A3, it creates S4 and any missing container that precedes it, in this case S3, and links A3 to S4 and A2 to S3. To make concurrent growth safe, **StreamBox** instantiates downstream links and containers using an atomic variable with strong consistency. Subsequent bundle processing uses the instantiated links and containers.

**Processing** To select a bundle to process, evaluators walk the container list for a transform, starting from the oldest container to the youngest, since the oldest container holds the most urgent work for state externalization. If an evaluator encounters containers in the wm\_consumed state, it destroys the container. Otherwise,

- 1. it retrieves an unclaimed bundle. If none exists,

- 2. it retrieves the end watermark when (i) the watermark is valid (i.e., the container has wm\_assigned), and (ii) all bundles are consumed (*unconsumed* == 0), and (iii) all watermarks in the preceding containers of  $D_{own}$  are consumed.

- 3. If the evaluator fails to retrieve a bundle or watermark from this container, it moves to the next younger container on  $D_{own}$ 's list.

Figure 2.2 shows an example. An evaluator starts from the oldest container W1 to find work **2**. Because W1 is in WM\_RETRIEVED (all bundles are consumed and the end

(a) A logic view of Join. The processing of two input streams progress independently, resulting in interleaved epochs in output

(b) Arbitrarily ordering Join's output epochs relaxes watermarks

Figure2.4. A logic diagram of OOP temporal join

watermark is being processed), the worker moves on to W2. Because all bundles in W2 are consumed but the end watermark is available, it retrieves the watermark (09:00) for processing. Section 2.6 describes how we prioritize transforms in the container network.

Merging containers for windowing For each input container, we create a *potential* downstream container, expecting each input epoch will correspond to an output epoch. However, when a transform D performs windowing operations, it often must wait for multiple watermarks to correctly aggregate records. In this case, we merge containers. Figure 2.2 3 shows an example of Aggregation on a 10-min window. After consuming container A1 with its 04:00 watermark, the Aggregation transform cannot yet emit a watermark and retire its current window (0:00-10:00). Our solution is to cancel watermarks and merge the downstream output containers until the windowing logic, which uses event time, is satisfied. This operation is cheap. StreamBox cancels watermarks by simply marking them  $w_{cancel}$ . As evaluators walk container lists and observe  $w_{cancel}$ , they logically treat adjacent containers as one, e.g., S2 and S3. When the transform receives a watermark  $ts \geq 10$ , it emits the watermark which will eventually close the container.

#### 2.5.3 Multi-input Transforms

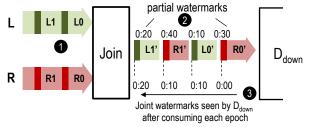

A multi-input transform, such as temporal Join and Union, takes multiple input streams and produces one stream. Figure 2.4 shows an example of out-of-order temporal join [10]. The left and right input streams progress independently (they share  $D_{join}$ 's internal state). The output stream consists of *interleaved* epochs resulting from processing either input stream. These epochs are delimited by *partial* watermarks ( $w_L$  or  $w_R$ ), which are also solely derived from the input streams. The downstream  $D_{down}$  derives a *joint* watermark as  $min(w'_L, w'_R)$ , where  $w'_L$  and  $w'_R$  are the most recent left and right partial watermarks.

The case for unordered containers A multi-input transform, unlike single-input transforms, cannot always have its downstream containers arranged on an *ordered* list (§2.5.2) because an optimal ordering of output epochs depends on their respective end (partial) watermarks. On the other hand, arbitrarily ordering output epochs may unnecessarily relax watermarks and delay watermark processing.

Figure 2.4(b) shows an example of arbitrarily ordering output epochs. While processing open input epochs L0/L1 and R0/R1  $\bigcirc$ , StreamBox arbitrarily orders the corresponding output as L1' $\rightarrow$ R1' $\rightarrow$ L0' $\rightarrow$ R0' without knowing the end watermarks. Later, these output epochs eventually receive their partial end watermarks O. Upon consuming them,  $D_{down}$  derives joint watermarks based on its subsequent observations of partial watermarks O. Unfortunately, the joint watermark is more relaxed than the partial watermarks. For instance, the partial watermark 00:30 of R0' guarantees that all records in R0' are later than 00:30. However, from the derived joint watermark,  $D_{down}$  only knows that they are later than 00:00. Relaxed watermarks propagate to all downstream transforms. To tighten a joint watermark, StreamBox should have placed L0' and L1' (and perhaps more subsequent left epochs) before R0' and R1'. However, it cannot make that decision before observing all these partial watermarks.

In summary, StreamBox must achieve two objectives in tracking epochs for multi-input transforms. (1) It must track output epochs with corresponding containers for epoch parallelism. (2) It must defer ordering these containers until it determines their end watermarks.

Figure 2.5. Unordered containers for Join and its downstream. For brevity, container watermarks are not drawn

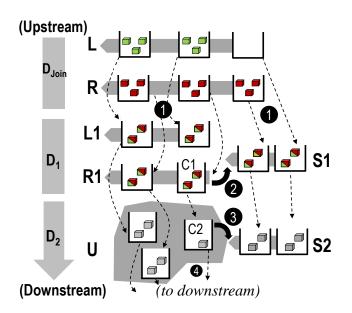

Solution StreamBox maintains *unordered* containers for a multi-input transform's output epochs and their downstream counterparts. Once StreamBox determines the ordering of one epoch, it appends the corresponding container to an ordered list and propagates this change downstream. Figure 2.5 shows an example.

•  $D_{\text{join}}$  owns two ordered container lists L and R.

•  $D_1$ , the immediate downstream transform of  $D_{join}$ , owns three ordered lists of containers. L1 and R1 are derived from  $D_{join}$ 's L and R, respectively. S1 holds merged containers from L1 and R1.

• With  $D_2$  downstream of  $D_1$ ,  $D_2$  owns an unordered set U and an ordered list S2.

As  $D_{join}$  processes its input streams L and R, it deposits the derived bundles and watermarks to containers on L1, R1, and S1 **1**.  $D_1$  selects the oldest container C1 on L1 and R1 to process and it appends C1 to S1 **2**. Processing C1, deposits records in container C2 (following the *down* link), which subsequently produces records in containers at S2 **3** and beyond **4**.

#### 2.5.4 Synchronized Access to Containers

In the cascading containers network, the concurrent evaluators dynamically modify the network topology by creating, linking, and destroying containers. Although the most frequent container operations, such as processing records, are lock-free as described in Section 2.5.1, modifying the container network must be synchronized. We carefully structure network modifications in reader and writer paths and synchronize them with one readers-writer lock for each container list. To retrieve work, an evaluator holds the container list's reader lock while walking the list. If the evaluator needs to modify the list (e.g., to destroy a container), it atomically upgrades the reader lock to a writer lock.

### 2.6 Pipeline Scheduling

A pipeline's latency depends on how fast the engine externalizes the state of the current window. To this end, **StreamBox**'s scheduler prioritizes upcoming state externalization.

StreamBox maintains a global notion of the *next externalization moment (NEM)*. The upcoming windowed output requires processing of all bundles and watermarks with timestamps prior to NEM. After each state externalization, **StreamBox** increments the NEM monotonically based on a prediction. In the common case where externalization is driven by temporal windows, the engine can accurately predict NEM as the end of the current window. In case windowing information is unavailable, the engine may predict NEM based on historical externalization timing. Mispredicting NEM may increase the output delay but will not affect correctness.

NEM guides work prioritization in StreamBox. All evaluators independently retrieve work (i.e., bundles or watermarks) from cascading containers. By executing StreamBox's dispatch function, an evaluator looks for work by traversing container lists from the oldest to the youngest, starting from the top of the network. It prioritizes bundles in containers with timestamps that precede NEM.

Watermark processing is on the critical path of state externalization and often entails substantial amount of work, e.g., reduction of the window state. To accelerate watermark processing, **StreamBox** creates a special *watermark task queue*. Watermark tasks are defined as lambda functions. StreamBox gives these tasks higher priority and executes them with the same set of evaluators – without oversubscribing the CPU cores. An evaluator first processes watermark tasks. After completing a task, evaluators return to the dispatcher immediately. Evaluators never wait on a synchronization barrier inside the watermark evaluator. This on-demand, extra parallelism accelerates watermark evaluation.

#### 2.7 Pipeline State Management

The memory behavior of a stream pipeline is determined by the bundles of records flowing among transforms and the transforms' internal states. To manage this state, **StreamBox** targets locality, NUMA-awareness, and coarse-grained allocation/free. We decouple state management from other key aspects, including epoch tracking, worker scheduling, and transform logic.

## 2.7.1 Bundles

Adaptive internal structure StreamBox adaptively packs records into bundles for processing.

StreamBox seeks to (i) maximize sequential access, (ii) minimize data movement, and (iii) minimize the *per-record* overhead incurred by bundling.

A bundle stores a "flat" sequence of records sequentially in contiguous memory chunks. This logical record ordering supports grouping records temporally in epochs and windows, and by keys. It achieves both because temporal computation usually executes on all the keys of specific windows, rather than on specific keys of all windows. This choice contrasts to prior work that simply treats <window, key> as a new key.

To minimize data movement, StreamBox adapts bundle internals to the transform algorithm. For instance, given a Mapper that filters records, the bundles include both records and a bitmap, where each bit indicates the presence of a record, so that a record can be logically filtered by simply toggling a bit. Databases commonly use this optimization [12] as well. StreamBox adapts bundle internals based on input data properties. The performance of keyed transforms, i.e., those consuming key-value pairs, is sensitive to the physical organization of these values. If each key has a large number of values, a bundle will hold a key's values using an array of pointers, each pointing to an array of values. This choice makes combining values produced by multiple workers as cheap as copying a few pointers. If each key only has a few values, **StreamBox** holds them in an array and copies them during combining. To learn about the input data, **StreamBox** samples a small fraction of it.

**NUMA-aware bundle flows StreamBox** explicitly steers bundles between transforms for NUMA locality by maximizing the chance that a bundle is both produced and consumed on the same NUMA node.

Each bundle resides in memory from one NUMA node and is labeled with that node. When an evaluator processes a container, it prefers unclaimed bundles labeled with its same NUMA node. It will process non-local bundles only when bundles from the local node are all consumed. To facilitate this process, an evaluator always allocates memory on its NUMA node, and later deposits the new bundle to the NUMA node of the downstream container. Notice that the NUMA-aware scheduling only affects the order among bundles within a container. It does not starve important work, e.g., containers to be dispatched by the next externalization moment.

#### 2.7.2 Transform Internal State

StreamBox organizes a transform's internal state as an array of temporal *slides*, forming a slide. Each slide corresponds to a window (for fixed windows) or a window's offset (for sliding windows). Note that the size of a slide is independent of an epoch size.

To access a transform's state, an evaluator operates on a range of slides: updating slides in-place for accumulating processing results; fetching slides for closing a window; and retiring slides for state flushing. Since concurrent evaluators frequently access the slide arrays, we need to minimize locking and data movement. To achieve this goal, **StreamBox** grows the array on-demand and atomically. It only copies pointers when fetching slides. It decouples the logical retirement of slides from their actual, likely expensive destruction. To support concurrent access to a single slide, the current **StreamBox** implementation employs off-theshelf concurrent data structures, as discussed below.

#### 2.8 Implementation

We implement StreamBox in 22K SLoC of C++11. The implementation extensively uses templates, static polymorphism, and C++ smart pointers. We implemented Windowing, GroupBy, Aggregation, Mapper, Reducer, and Temporal Join as our library transforms. Our scalable parallel runtime relies on the following scalable low-level building blocks.

C++ libraries We use boost [16] for timekeeping and locks, Intel TBB [17] for concurrent hash tables, and Facebook folly [18] for optimized vectors and strings. Folly improves the performance of some benchmarks by 20–30%. For scalable memory allocation, we use jemalloc [19], which scales much better than std::alloc and TBB [20] on our workloads.

**Concurrent hash tables** are hotspots in most statefull pipelines. We tested three opensource concurrent hash tables [17], [18], [21], but they either did not scale to a large core count or required pre-allocating a large amount of memory. Despite the extensive research on scalable hash tables [22], [23], we needed to implement an internally partitioned hash table. We wrapped TBB's concurrent hash map. This simple optimization improves our performance by 20–30%.

**Bundle size** is an empirical trade off between scheduling delay and overhead. StreamBox mainly varies bundle size at pipeline ingress. When the engine is fully busy, with all records in one ingress epoch, it produces as many bundles as evaluators, e.g., 56 bundles for 56 evaluators, to maximize the bundle size without starving any thread. The largest bundle size is around 80K records. When the ingress slows down, the system shrinks bundle sizes to reduce latency. We empirically determine that a  $2 \times$  reduction in bundle size balances a 10% drop in ingress data rate. We set the minimal bundle size at 1K records to avoid excessive per-record overhead.

Figure 2.6. Throughput of StreamBox as a function of hardware parallelism and latency. StreamBox scales well.

| Table2.2.         Test platforms used in experiments                                      |  |  |

|-------------------------------------------------------------------------------------------|--|--|

| <b>56CM</b> Dell PowerEdge R930<br>4x14 Xeon E7-4850v4 "Broadwell", 256GB DRAM, Linux 4.4 |  |  |

| <i>12CM</i> Dell PowerEdge R720<br>2x6 Xeon E5-2630v2 "Ivy Bridge", 256GB DRAM, Linux 4.4 |  |  |

#### 2.9 Evaluation

**Methodology** We evaluate **StreamBox** on the two multicore servers, summarized in Table 2.2. 56CM is a high-end server that excels at real-time analytics and 12CM is a mid-range server. Although 100 Gb/s Infiniband (RDMA) networks are available, our local network is only 10 Gb/s. However, 10 Gb/s is insufficient to test **StreamBox** and furthermore even if we used Infiniband, it will directly store stream input in memory. We therefore generate ingress streams from memory. We dedicate a small number of cores (1–3) to the pipeline source. We then replay these large memory buffers pre-populated with records and emit in-memory stream epochs continuously. We measure the maximum sustained throughput of up to 38 GB/s at the pipeline source when the pipeline delay meets a given target.

**Benchmarks** We use the following benchmarks and datasets. Unless stated otherwise, each input epoch contains 1 M records and spans 1 second of event time. (1) Windowed **Grep** (grep) searches the input text and outputs all occurrences of a specific string. We use Amazon Movie Reviews (8.7 GB in total) [24] as input, a sliding window of 30 seconds, and 1 second target latency. The input record size is 1 KB. (2) Word Count (wordcount) splits input texts into words and counts the occurrences of each word. We use 954 MB English books [25] as input, a sliding window of 30 seconds, and 1 second target latency. The input record size is 100 bytes. (3) **Temporal Join (join)** has two input streams, for which we randomly generate unique 64-bit integers as keys. The join window for each record is  $\pm 0.5$  seconds. (4) Counting Distinct URLs (distinct) [9] counts unique URL identifiers. We use the Yandex dataset [26] with 70 M unique URLs and a fixed window of 1 second. (5) Network Latency Monitoring (netmon) [9] groups network latency records by IP pairs and computes the average per group. We use the Pingmesh dataset [27] with 88 M records and a fixed window of 1 second. The source emits 500K records per epoch. (6) **Tweets Sentiment Analysis (tweets)** [9] correlates sentiment changes in a tweet stream to the most frequent words. It correlates results from two pipelines: one that selects windows with significant sentiment score changes, and the other that calculates the most frequent words for each window. We use a public dataset of 8 million English tweets [28] and a fixed window of 1 second. This benchmark is the most complex and uses 8 transforms.

#### 2.9.1 Throughput and Scalability

This section evaluates the throughput, scalability, and out-of-order handling of Stream-Box, and compares with existing stream processing systems.

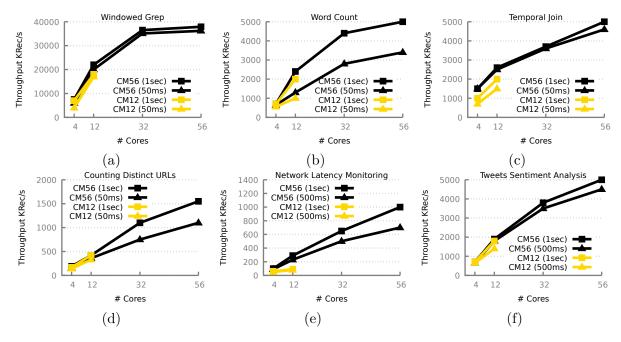

**Throughput** Figure 3.8 presents throughput on the y-axis for the six benchmarks as a function of hardware parallelism on the x-axis and latency as distinct lines. **StreamBox** has high throughput and typically processes millions of input records per second on a single machine, while delivering latencies as low as 50 ms. In particular, Grep achieves up to 38 M records per second, which translates to 38 GB per second. This outstanding performance is due to low overheads and high system utilization. Profiling shows that all CPU cores have

consistently high utilization (> 95%) and that most time is spent performing transform logic, e.g., processing stream data and manipulating hash tables.

Scalability Figure 3.8 shows that StreamBox scales well with core count for most benchmarks on both the 12-core and 56-core machines. When scalability diminishes in a few cases beyond 32 cores, as for Grep, it is a result of memory-bound computation saturating the machine.

Figure 2.7. StreamBox achieves high throughput even when a large fraction of records arrive out-of-order.

**Out-of-order records** By design, **StreamBox** efficiently computes on out-of-order records. To demonstrate this feature, we force a certain percent of records to arrive early in each epoch, i.e., the event time of these records is larger than the enclosing epoch's end watermark. Figure 2.7 shows the effect on throughput for 3 benchmarks. **StreamBox** achieves nearly the same throughput and latency as in in-order data processing. In particular, the throughput loss is as small as 7% even with 40% of records out-of-order. The minor degradation is due to early-arriving records that accumulate more windows in the pipeline. We attribute this consistent performance to (i) out-of-order epoch processing, since each transform continuously processes out-of-order records without delay, and (ii) prioritizing bundles and watermarks that decide the externalization latency of the current window in the scheduler.

**Comparing to distributed stream engines** We first compare **StreamBox** with published results of a few popular distributed stream processing systems and then evaluate two of

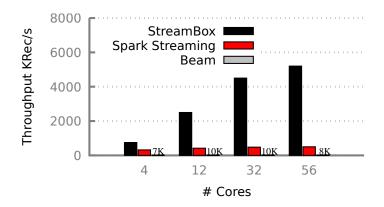

Figure 2.8. StreamBox scales better than Spark and Beam with Wordcount on 56CM, with a 1-second target latency.

them on our 56-core machine. Most published results are based on processing of in-order stream data. For out-of-order data, they either lack support (e.g., no notion of watermarks) or expect transforms to "hold and sort", which significantly degrades latency [29], [30].

Compared to existing systems, StreamBox jointly achieves low millisecond latency and high throughput (tens of millions of records per second). Very few systems achieve both. To achieve similar throughput, prior work uses at least a medium-size cluster with a few hundred CPU cores [3], [8]. For instance, under the 50-ms target latency, StreamBox's throughput on 56CM is  $40\times$  greater than StreamScope [8] running on 100 cores. Moreover, even under a 1-second target latency, StreamBox achieves much higher throughput per core. StreamBox can process 700K records/sec for Grep and 90K records/sec for Wordcount per core, which are  $4.7\times$  and  $1.5\times$  faster than the per-core processing rate reported by Spark Streaming on a 100-node cluster with a total of 400 cores.

We further experimentally compare StreamBox with Spark (v2.1.0) [3] and Apache Beam (v0.5.0, executing its Direct Runner) [7], on the same machine (56CM). Note that Beam's Direct Runner is known to be unoptimized for a single machine. We verify that they both utilize all cores. We set the the target latency to 1 second since they cannot achieve 50 ms as StreamBox does. Figure 2.8 shows that StreamBox achieves significantly higher throughput (by more than one order of magnitude) and it scales much better with core count.

Comparing to single-machine streaming engines A few streaming engines are designed for a single machine: Oracle CEP [31], StreamBase [32], Esper [33], and SABER (for CPU+GPU) [34]. With 4 to 16 CPU cores, they achieve throughput between thousands and a few million of records per second. None of them reports to scale beyond 32 CPU cores. In particular, we tested Esper [33] on 56CM with Wordcount. On four cores, Esper achieves around 900K records per second, which is similar to **StreamBox** with the same core count. However, we were unable to get Esper to scale even after applying recommended programming techniques, e.g., context partitioning [35]. As the core count increases, we observed the throughput drops.

In summary, StreamBox achieves better or similar per core performance than prior work. More importantly, StreamBox scales well to a large core count even with out-of-order record arrival.

#### 50000 8000 2000 StreamBox I StreamBox | StreamBox Throughput KRec/s In-order Throughput KRec/s In-order Throughput KRec/s In-order 40000 6000 30000 4000 1000 20000 2000 10000 0 0 0 32 56 32 56 32 56 # Cores # Cores # Cores (a) Grep (b) Wordcount (c) Distinct

# 2.9.2 Validation of Key Design Features

Figure 2.9. In-order processing reduces parallelism, scalability, and throughput.

This section evaluates the performance and scaling contributions of our key design features.

**Epoch parallelism for out-of-order processing** Epoch parallelism is fundamental to producing abundant parallelism and exploiting out-of-order processing. We compare with in-order epoch processing by implementing "hold and sort," in which each transform waits to process an epoch until all its records arrive. Note that this in-order epoch processing leaves out the high cost of sorting records. It processes records within an epoch out-of-order.

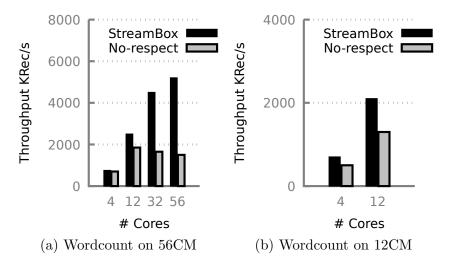

Figure 2.10. When records do not respect epoch boundaries, it limits parallelism, scalability, and throughput.

Figure 2.9 shows that in-order epoch processing reduces throughput by 25% - 87%. Profiling reveals the reduced parallelism causes poor CPU utilization.

Records must respect epoch boundaries .StreamBox enforces the invariant that records respect epoch boundaries by mapping upstream containers to downstream containers (§2.5). We compare this to an alternative design where a transform's output records always flow into the *most recently* opened downstream container. Records then no longer respect epoch boundaries, since later records may enter earlier epochs. Violating the epoch invariant leads to huge latency fluctuations in watermark externalization, degrading performance. Figure 2.10 shows that not respecting epoch boundaries reduces throughput by up to 71%.

**Prioritized scheduling** (§2.6) Prioritizing containers on the critical path is crucial to latency and throughput. To explore its effect, we disable prioritized scheduling such that evaluators freely retrieve available bundles anywhere in the pipeline starting from its curent source and sink container. In this configuration, evaluators tend to rush into one transform, drain bundles there, and then move to the next. We confirmed this behavior with profiling. Performance measurements show that the pipeline latency fluctuates greatly and sometimes overshoots the target latency by a factor of 10.

**NUMA-awareness** (§2.7) We find NUMA-awareness especially benefits memory-bound benchmarks. For example, grep without windowing achieves 54 GB/s on 56CM, which is 12.5% higher than a configuration with NUMA-unaware evaluators.

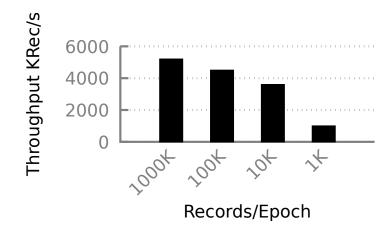

Watermark arrival rates. Frequent watermarks lead to shorter epochs and more containers, each with fewer records, thus increasing the maintenance cost of cascading containers. In general, as shown in Figure 2.11, containers are sufficiently lightweight so that frequent watermarks (e.g.,  $100 \times$  more watermarks in 10K records/epoch) result in only a minor performance loss (e.g., 20%). However, substantial performance degradation emerges for watermarks at the rate of 1 K records/epoch, because frequent container creation and destruction incur too much synchronization.

Figure 2.11. Performance impact of watermark arrival rate for Wordcount on 56CM.

# 2.10 Related Work

This section compares StreamBox to prior work that uses the out-of-order processing (OOP) model, distributed and single server stream engines, and on exploiting shared memory for streaming.

**OOP stream processing** A variety of classic streaming engines focus on processing in-order records with a single core (e.g., StreamBase [32], Aurora [36], TelegraphCQ [37], Esper [33], Gigascope [29], and NiagaraST [38]). Li et al. [10] advocate OOP stream processing that relies on stream progression messages, e.g. punctuations, for better throughput and efficiency. The notion of punctuations is implemented in many modern streaming engines [7], [8], [12].

These systems do exploit pipeline and batch parallelism, but they do not exploit out-of-order processing of epochs to expose and deliver highly scalable data parallelism on a single server. **Single-machine streaming engines** Trill [39] inspires **StreamBox**'s state management with its columnar store and bit-vector design. However, Trill's punctuations are generated by the engine itself in order to flush its internal batches, which limits parallelism. Furthermore, Trill assumes ordered input records, which limits it applicability. **StreamBox** has neither of these limitations. SABER [34] is a hybrid streaming engine for CPUs and GPGPUs. Similar to **StreamBox**, it exploits data parallelism with multithreading. However, SABER does not support OOP. It must recorder execution results from concurrent workers, limiting its applicability and scalability. Oracle CEP [31] exploits record parallelism by relaxing record ordering. However, it lacks the notion of watermarks and does not implement statefull OOP pipelines.