# ELECTRO-THERMAL AND RADIATION RELIABILITY OF POWER TRANSISTORS: SILICON TO WIDE BANDGAP SEMICONDUCTORS

by

Bikram Kishore Mahajan

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana December 2021

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

#### Dr. Muhammad Ashraful Alam, Chair

School of Electrical and Computer Engineering

### Dr. Mark S. Lundstrom

School of Electrical and Computer Engineering

## Dr. Peide Ye

School of Electrical and Computer Engineering

### Dr. Ali Shakouri

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

This thesis is dedicated to the loving memory of my father, Nirmal Mahajan

## ACKNOWLEDGMENTS

First of all, I would like to express my deepest gratitude to my adviser, Prof. Muhammad Ashraful Alam, for giving me an opportunity to join his group and fund me, despite having little experience in the reliability of transistors. This thesis would not have seen the light of the day without his constant inspiration, diligent mentoring and father-like care. I consider myself incredibly fortunate to have him as my adviser, and he has been a significant influence on me, both professionally and personally. He taught me how to admire a research work but think critically about it at the same time. His philosophy on "a problem should be timely, but the solution should be timeless" is the ideology I would try to follow throughout my career. I have interacted with him countless times in these years, but I am still amazed at how he takes a complicated problem and solves it in an effortless but elegant fashion. His anecdotes about his life, will always inspire me to a better researcher, and a better human being. Towards the end of this incredible journey, I have realized that he not only taught me the basics of a transistor but also several valuable life lessons, which have had a profound effect and will continue to have, throughout my lifetime.

I wish to thank Prof. Peide Ye, for discussions about research directions and providing his valuable inputs which helped me greatly. He generously provided us with the best samples from his lab, for our reliability studies and modeling. His group has always been supportive of my research and helped me, whenever I needed them. I also want to thank Prof. Mark S. Lundstrom for agreeing to serve on my doctoral committee and provide constructive comments to improve my research. Many people will agree with me that he is one of the best persons in the world to learn semiconductor physics from, and I consider myself very privileged to get the opportunity to work as a teaching assistant for a couple of courses, with him. Also, I have always admired his grand vision about the future of electronics. I wish to thank Prof. Ali Shakouri for agreeing to serve on my committee and providing invaluable insights about my research. His comments and suggestions helped me to improve my models, and decide a research direction which would manifest a great impact on the scientific community.

I want to extend my heartfelt appreciation to my collaborators at Texas Instruments, Dr. Dhanoop Varghese, Dr. Srikanth Krishnan, and Dr. Vijay Reddy, without whom this thesis would not have been completed. They provided us with the amazing LDMOS devices for reliability experiments and modeling. They also provided funding for the research, besides providing us feedback and research directions, on a monthly basis. Dr. Dhanoop Varghese, clarified my doubts even between these monthly meetings and always helped with advice and suggestions whenever I needed them. I also wish to acknowledge Semiconductor Research Corporation (SRC) for research funding.

I thank Prof. Souvik Mahapatra, and his group at IIT Bombay, India, for providing me with helpful suggestions and research directions. I am grateful to Prof. Biswajit Ray, from the University of Alabama at Huntsville, for his invaluable suggestions and assistance with the radiation experiments. He never hesitated to extend any help, beyond research, whenever I approached him. I also thank my friends and collaborators at Purdue from different research groups, Dr. Jinhyun Noh, Ulisses Alberto Heredia Rivera, Dr. Xufeng Wang, Dr. Yubo Sun, and Dr. Madan Kumar Sampath, for the stimulating research discussions and help, whenever I needed them.

I thank Matt Golden, Elisheba Van Winkle, Vicki Johnson and Lori Carte, for helping me with all the paper works, and other administrative aspects related to my Ph.D.

I am indebted to the past and current members of ALAM CEED Group, without whom this thesis would not have been completed. I thank my colleague and friend, Yen-Pu Chen, without whom most of the characterization done in this thesis would have been impossible. Dr. Nicolò Zagni and Dr. Ramachandran A. Vijayan, helped me with TCAD in my initial days in this group. Dr. Woojin Ahn, Dr. Xin Jin and Dr. Xingshu Sun, mentored me when I first joined the group and have always been helpful to me, whenever I approached them. Yen-Pu Chen, Muhammad Tahir Patel, Dr. Reza Asadpour, Marco Fratus, Md. Asaduz Zaman Mamun, Ajanta Saha, and other members of ALAM CEED group have made my tenure as a graduate student at Purdue, a truly gratifying experience. I will always relish the memories of our multitudinous banters over lunches, dinners, and our in-office cricket matches and pranks. I have enjoyed our discussions on everything under the sun, with my colleagues from other groups, Dr. Orchi Hassan, Shuvro Chowdhury, Mushfiqur Rahman, Jan Kaiser, Sarah Nahar Chowdhury, Abhishek Shankar, Sree Hari Sureshbabu, Dr. Evan Witkoske, which helped me navigate the difficult times of graduate school.

This thesis would not have been completed without the support of many people, who kept me motivated, despite the rigors of graduate school. Susmita Sarkar has been a wonderful support system for me all these years. I know that I could not have completed this journey without her help. I know that I can call up Dr. Mukul Parmananda and Dr. Hemanshul Garg anytime I need any help or motivation. I have always enjoyed the quirky sense of humor of my friends, Navneet Goswami and Soumyadeep Chandra. I will always cherish the Friday night board games, food, movies, and numerous road trips and hikes, with these people. Dr. Ratul Kumar Baruah, Dr. Muralikannan Maruthamuthu, Dr. Vidhya Selvamani, Dr. Srinivasan Swaminathan, and Dr. Minisha Mehta, invited me to their home numerous times, and I will treasure those wonderful memories of card games, food, and banter, my whole life. Vinay Kenny, Bhargav Ganguly, Pallabi Das and Dr. Avijit Karmakar have always been kind to me, and I have spent several memorable weekends with them. I have enjoyed numerous philosophical conversations, and food, with Dr. Debkalpa Goswami, Dr. Aniket Pal and Dr. Behnam Sadri. Saurabh Mishra, Dr. Aakrati Jain, Dr. Apoorv Maheshwari, Ruchita Mandhre and Dr. Gaurav Patankar, has been a great help during my initial days at Purdue. My high-school friends from India, called me up from time to time to check on me, and I am indebted to them for this. There are many other people I met at Purdue, and my alma maters (Missouri University of Science and Technology, Rolla, USA, National Institute of Technology, Agartala, India and Ramakrishna Mission Vidyalaya, Agartala, India) whom I couldn't name here, but I will be forever grateful for their help and support.

Finally, this thesis would not have been completed without the help and support of my family, and relatives. I am indebted to my father, Nirmal Mahajan, who couldn't see me start graduate school, but have always encouraged me to get a Ph.D. I am indebted to my mother, Aparna Mahajan, for supporting me in every career decision I took, among numerous other things. I am indebted to my sister, Sagarika Mahajan, for taking care of all needs, back at home, in my absense. I am indebted to my brother, Amartya Mahajan, for supporting and loving me unconditionally. My cousin, Dr. Prasenjit Shil, always supported me from my day 1 in the USA. He has been a big brother and a friend whom I can always turn to for inspiration. I also thank Suman Shil, Litoge Shil and Swarnali Ghosh-Dastider for their help, motivation, and support throughout these years.

# TABLE OF CONTENTS

| LI | ST O | F TAB  | LES                                                                                            | 13 |

|----|------|--------|------------------------------------------------------------------------------------------------|----|

| LI | ST O | F FIGU | JRES                                                                                           | 14 |

| A  | BSTR | ACT    |                                                                                                | 21 |

| 1  | INT  | RODU   | CTION                                                                                          | 23 |

|    | 1.1  | Backg  | round                                                                                          | 23 |

|    | 1.2  | Logic  | Transistor Scaling                                                                             | 24 |

|    |      | 1.2.1  | Self-Heating in Logic Transistors                                                              | 25 |

|    |      | 1.2.2  | Hot Carrier Degradation in Logic Transistors: Correlation with Self-                           |    |

|    |      |        | Heating                                                                                        | 27 |

|    | 1.3  | Power  | Transistors                                                                                    | 30 |

|    |      | 1.3.1  | Brief History of Power Transistors                                                             | 31 |

|    |      | 1.3.2  | Basic Principle of an LDMOS Transistor                                                         | 33 |

|    |      | 1.3.3  | Hot Carrier Degradation in LDMOS: Correlation with Self-Heating $% \mathcal{A}$ .              | 35 |

|    |      | 1.3.4  | Wide Bandgap Semiconductor Based Power Transistors                                             | 36 |

|    | 1.4  | Safe C | Operating Area                                                                                 | 39 |

|    | 1.5  | Radia  | tion $\ldots$ | 41 |

|    |      | 1.5.1  | Ionizing and Non-ionizing Radiation                                                            | 41 |

|    |      | 1.5.2  | Ionizing Radiation Sources                                                                     | 42 |

|    |      | 1.5.3  | Impact of Radiation on Transistors                                                             | 44 |

|   | 1.6 | Reliab | ility Concerns of a Power Electronic System                                       | 46 |

|---|-----|--------|-----------------------------------------------------------------------------------|----|

|   | 1.7 | Thesis | Organization                                                                      | 47 |

| 2 | SAF | E OPE  | RATING AREA OF WIDE BANDGAP SEMICONDUCTORS                                        | 49 |

|   | 2.1 | Introd | uction                                                                            | 49 |

|   | 2.2 | Limits | s of 'Intrinsic' Safe Operating Area                                              | 53 |

|   |     | 2.2.1  | Generalized On-Resistance                                                         | 53 |

|   |     |        | Counter-balancing the roles of self-heating in $R_{on,sp}$ and $V_{bd}$           | 55 |

|   |     |        | Substrate-Aware $R_{on,sp}$                                                       | 58 |

|   |     | 2.2.2  | Generalized $I_{max}$                                                             | 59 |

|   |     | 2.2.3  | Generalized $P_{max}$                                                             | 59 |

|   | 2.3 | Calcul | lating the <i>i</i> -SOA                                                          | 62 |

|   | 2.4 | Reliab | pility-Aware <i>i</i> -SOA                                                        | 64 |

|   | 2.5 | Summ   | ary                                                                               | 68 |

| 3 | ELE | CTRO-  | THERMAL PERFORMANCE LIMIT OF $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FIELD EFFECT |    |

|   | TRA | NSIST  | ORS                                                                               | 71 |

|   | 3.1 | Introd | uction                                                                            | 71 |

|   | 3.2 | Electr | othermal Modeling                                                                 | 72 |

|   |     | 3.2.1  | Device Modeling (TCAD)                                                            | 73 |

|   |     | 3.2.2  | Circuit Simulations (HSPICE)                                                      | 78 |

|   |     | 3.2.3  | Package Simulations (COMSOL)                                                      | 83 |

|   | 3.3 | Appro   | eaches to Improve the Performance                   | 84  |

|---|-----|---------|-----------------------------------------------------|-----|

|   |     | 3.3.1   | Device Modeling (TCAD)                              | 85  |

|   |     | 3.3.2   | Circuit Simulations (HSPICE)                        | 87  |

|   |     | 3.3.3   | Package Performance (COMSOL)                        | 87  |

|   | 3.4 | Summ    | ary                                                 | 87  |

| 4 | RED | DISCOV  | VERY OF THE UNIVERSAL SCALING OF HOT CARRIER DEGRA- |     |

|   | DAT | TION IN | N LDMOS TRANSISTORS                                 | 90  |

|   | 4.1 | Introd  | luction                                             | 90  |

|   | 4.2 | Existin | ng Models of HCD for Power Transistors              | 93  |

|   | 4.3 | Exper   | imental Details                                     | 95  |

|   |     | 4.3.1   | Device Structure and Dimensions                     | 95  |

|   |     | 4.3.2   | HCD Experiments                                     | 95  |

|   |     | 4.3.3   | TCAD Simulations                                    | 95  |

|   | 4.4 | '2 MO   | S Model' of an LDMOS                                | 96  |

|   |     | 4.4.1   | Calibration with Experiments and TCAD               | 97  |

|   |     | 4.4.2   | Analytical Model of Two-region Degradation          | 97  |

|   | 4.5 | Separa  | ating Region-Specific Degradation                   | 100 |

|   |     | 4.5.1   | Voltage-Dependent Degradation                       | 100 |

|   |     | 4.5.2   | Saturation of the Channel and the Drift Region      | 101 |

|   |     | 4.5.3   | Universal Scaling of Degradation                    | 103 |

|   | 4.6 | Summ    | ary                                                                                              | 105  |

|---|-----|---------|--------------------------------------------------------------------------------------------------|------|

| 5 | TCA | D SIM   | ULATIONS OF HOT CARRIER DEGRADATION IN LDMOS                                                     | 108  |

|   | 5.1 | Introd  | uction $\ldots$ | 108  |

|   | 5.2 | Hot Ca  | arrier Degradation in High Voltage Transistors                                                   | 109  |

|   |     | 5.2.1   | Obtaining the Electron Distribution by Solving BTE numerically $\ . \ .$                         | 111  |

|   |     | 5.2.2   | Analytical Approaches to Obtain the Electron Distribution                                        | 113  |

|   | 5.3 | Calibra | ation of the Simulation Deck                                                                     | 115  |

|   |     | 5.3.1   | Calibration of the Transfer and Output Characteristics $\hdots$                                  | 115  |

|   |     | 5.3.2   | Device Characteristics from TCAD                                                                 | 116  |

|   | 5.4 | TCAD    | Modeling of Hot Carrier Degradation                                                              | 120  |

|   |     | 5.4.1   | Hot Carrier Degradation Experiments                                                              | 121  |

|   |     | 5.4.2   | Hot Carrier - Safe Operating Area                                                                | 121  |

|   |     | 5.4.3   | TCAD Modeling                                                                                    | 122  |

|   |     | 5.4.4   | TCAD Calibration                                                                                 | 125  |

|   |     | 5.4.5   | Challenges Associated with TCAD Modeling of Hot Carrier Degradation                              | n126 |

|   | 5.5 | Summ    | ary                                                                                              | 132  |

| 6 | COR | RELAT   | TED EFFECTS OF RADIATION AND HOT CARRIER DEGRADA-                                                |      |

|   | TIO | N ON L  | DMOS                                                                                             | 133  |

|   | 6.1 | Introd  | uction $\ldots$ | 133  |

|   | 6.2 | Experi  | mental Setup                                                                                     | 135  |

|    | 6.3  | Impact  | t of Radiation in LDMOS Device Geometry          | 135 |

|----|------|---------|--------------------------------------------------|-----|

|    |      | 6.3.1   | Impact of Radiation on Drain Current             | 136 |

|    |      | 6.3.2   | Device Width Dependence                          | 139 |

|    |      | 6.3.3   | Location Dependence of Radiation-Induced Defects | 141 |

|    | 6.4  | Correla | ated Hot Carrier Degradation and TID             | 143 |

|    |      | 6.4.1   | TID followed by HCD: Threshold Voltage Shift     | 143 |

|    |      | 6.4.2   | HCD Followed by TID                              | 145 |

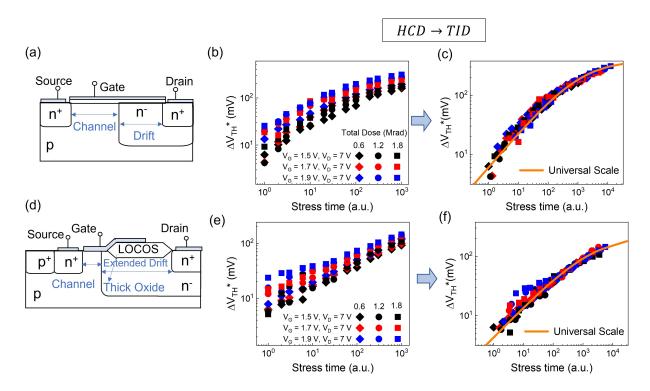

|    | 6.5  | Univer  | sal Scaling of HCD                               | 147 |

|    | 6.6  | Summa   | ary                                              | 148 |

| 7  | SUM  | IMARY   | AND FUTURE WORK                                  | 150 |

|    | 7.1  | Thesis  | Summary                                          | 150 |

|    | 7.2  | Future  | Work                                             | 154 |

| RI | EFER | ENCES   | 5                                                | 157 |

| А  | PAR  | AMET    | ERS USED IN CALCULATIONS                         | 184 |

| В  | DET  | ERMIN   | NING THERMAL RESISTANCE OF A BILAYER STRUCTURE   | 185 |

| С  | SEN  | TAURU   | US TCAD CODE FOR A LDMOS                         | 187 |

| VI | TA   |         |                                                  | 195 |

# LIST OF TABLES

| 1.1 | Average Radiation Dose by Lunar Landing Missions. This data is replotted from |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | [76]                                                                          | 41  |

| 2.1 | Average cost of wafers. This data is replotted from $[145]$ and $[146]$       | 69  |

| A.1 | Device Parameters used in calculations                                        | 184 |

| A.2 | Device Dimensions used in calculations.                                       | 184 |

# LIST OF FIGURES

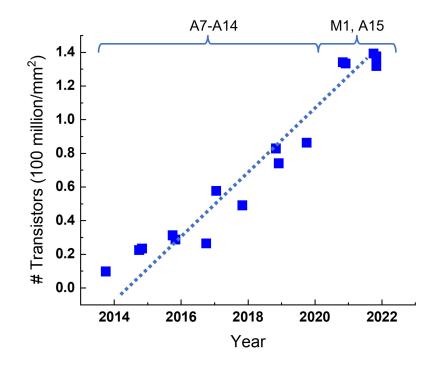

| 1.1  | Number of transistors in Apple processors: A series (A8 to A15 Bionic) and M series (M1, M1 Pro and M1 Max). This plot has been constructed from the data available in [4]                                                                                                                                                                                                                                                                                                         | 25 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

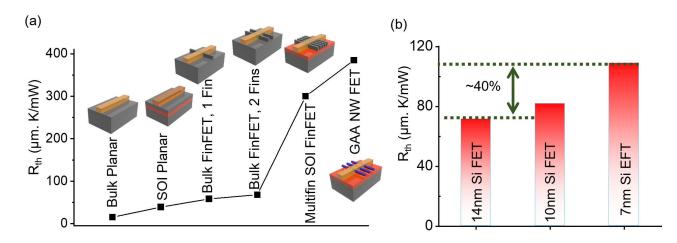

| 1.2  | (a) Thermal resistance of bulk, SOI planar and FinFETs with various configu-<br>rations and GAA nanowire FETs [Replotted from [2]]. (b) Thermal resistance<br>of a 14nm, 10 nm and 7nm bulk Si FinFET [Replotted from [8]]                                                                                                                                                                                                                                                         | 26 |

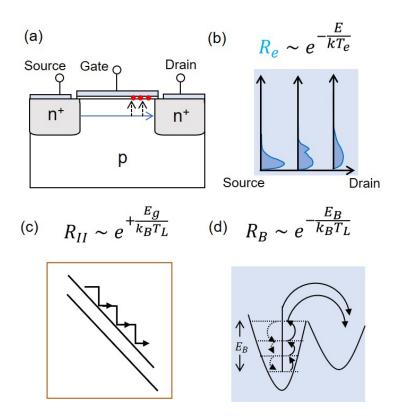

| 1.3  | (a) A schematic representing HCD in MOSFET. (b) A schematic of the evo-<br>lution of carrier distribution, from Boltzmann to heated Boltzmann distribu-<br>tion, as the electrons travel from the source to the drain. (c) A schematic<br>showing negative temperature coefficient of HCD, due to reduction in impact<br>ionization. (d) A schematic showing multiple-particle process due to increased<br>interfacial bond vibration, leading to positive temperature coefficient | 28 |

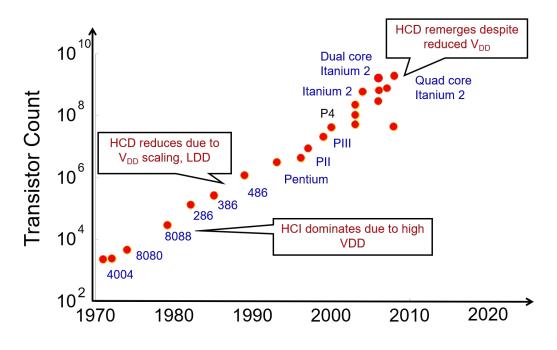

| 1.4  | Hot Carrier Degradation trends in Intel microprocessors [20]                                                                                                                                                                                                                                                                                                                                                                                                                       | 29 |

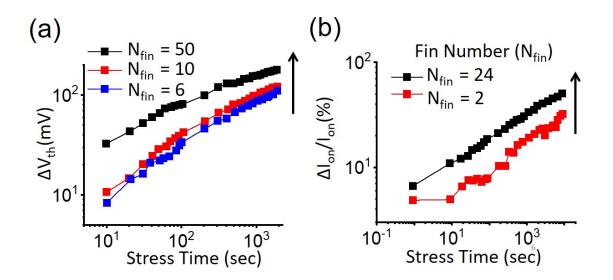

| 1.5  | (a) Threshold voltage degradation due to fin number variation is reported<br>in [24], and replotted here. (b) On-current degradation due to fin number<br>variation is reported in [25], and replotted here                                                                                                                                                                                                                                                                        | 30 |

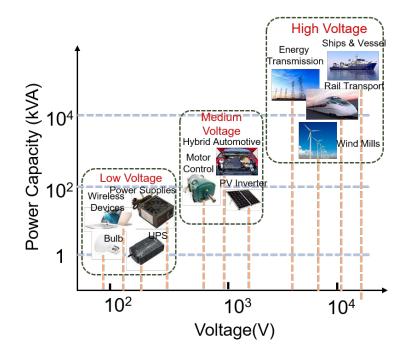

| 1.6  | A few of the many power electronics applications                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31 |

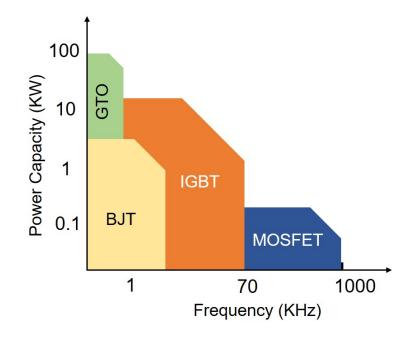

| 1.7  | Different power devices and their power and frequency ratings. Adapted from [27]                                                                                                                                                                                                                                                                                                                                                                                                   | 32 |

| 1.8  | Different power devices and their power and frequency ratings [Image Source: Google Images]                                                                                                                                                                                                                                                                                                                                                                                        | 33 |

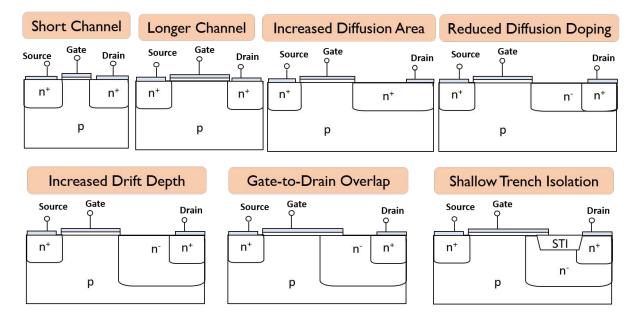

| 1.9  | A schematic representation of design schema from low to high voltage tran-<br>sistors, following the Poisson's equation, Eq.1.3. This figure is redrawn from<br>Ref. [32]                                                                                                                                                                                                                                                                                                          | 34 |

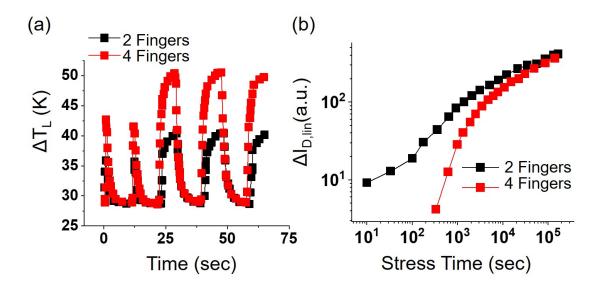

| 1.10 | (a) Temperature rise in a 2-finger vs. 4-finger LDMOS. b) Linear drain current degradation in a 2-finger vs. 4-finger, as reported in [36]                                                                                                                                                                                                                                                                                                                                         | 35 |

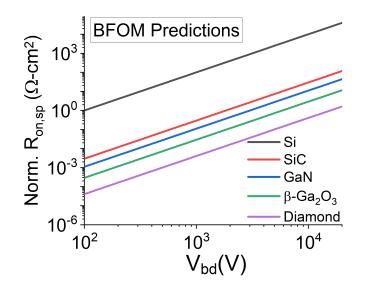

| 1.11 | The predictions by the Baliga Figure of Merit (BFOM) [41], for wide bandgap semiconductors.                                                                                                                                                                                                                                                                                                                                                                                        | 36 |

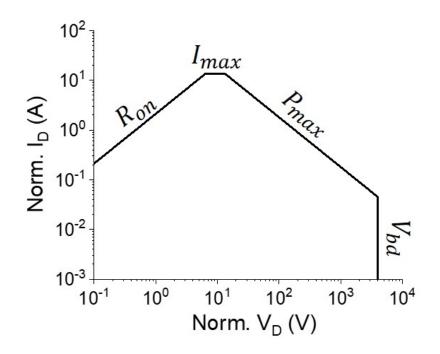

| 1.12 | A typical Safe Operating Area (SOA) plot for a power transistor                                                                                                                                                                                                                                                                                                                                                                                                                    | 40 |

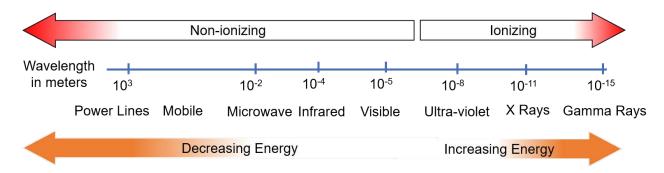

| 1.13 | A schematic of the regions of the electromagnetic spectrum, categorized as ionizing and non-ionizing radiation.                                                                                                                                                                                                                                                                                                                                                                    | 42 |

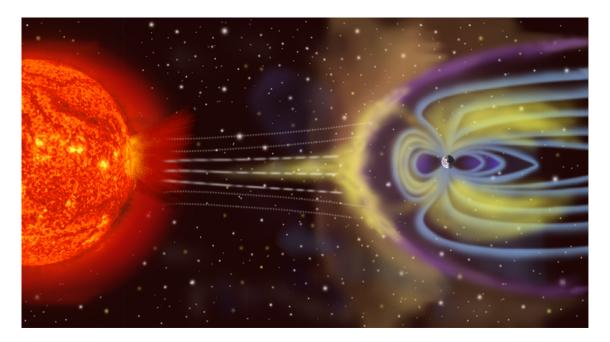

| 1.14 | An Artist's rendition of Earth's magnetosphere. Image Source: $[79]$                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |

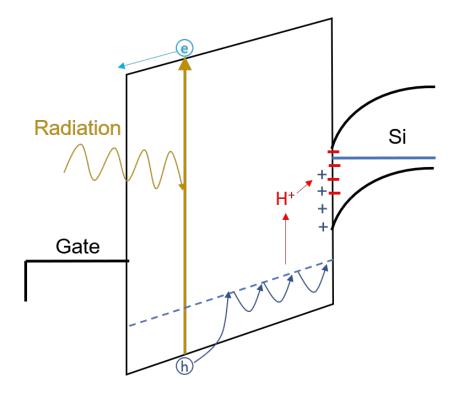

| 1.15 | Mechanism of Total Ionizing Dose (TID) in a transistor with a thick oxide.<br>The schematic is replotted from [91]                                                                                                                                                                                                                                                                                                                                                                 | 45 |

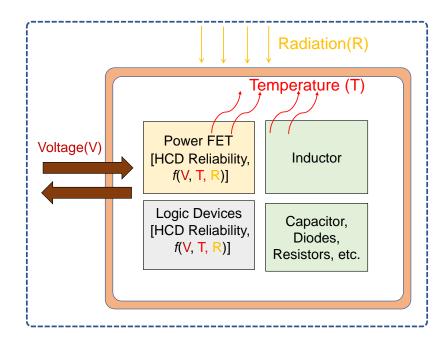

| 1.16 | Schematic of a general power electronic system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

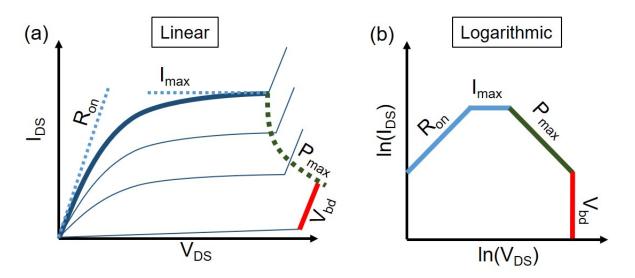

| 2.1  | A typical Safe Operating Area (SOA) plot for a MOSFET in (a) linear scale, and (a) logarithmic scale.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49 |

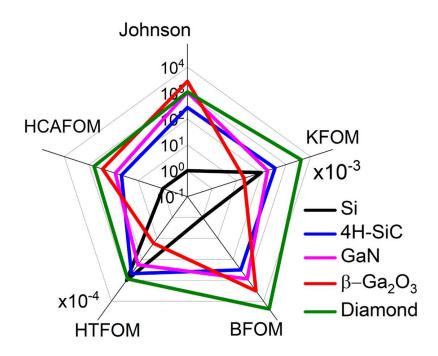

| 2.2  | Radar Chart showing FOM values of different FOMs: Johnson FOM (JFOM),<br>BFOM, Huang's Chip Area FOM (HCAFOM), Keyes FOM (KFOM) and<br>Huang's Thermal FOM (HTFOM). The FOMs values are scaled to that of<br>silicon. A constant factor scaling of KFOM and HTFOM allows a balanced<br>display of various FOMs                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51 |

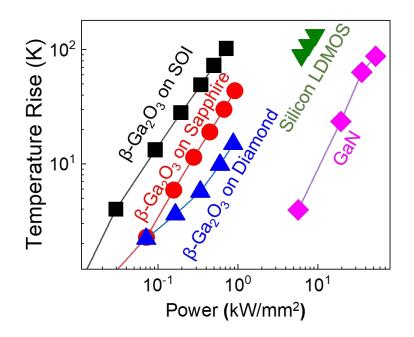

| 2.3  | Self-heating of $\beta$ - $Ga_2O_3$ transistors, depending on the substrate. Data from a GaN transistor and a silicon-based LDMOS is also plotted for reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 52 |

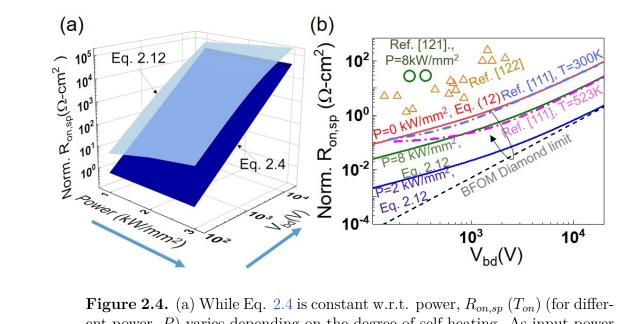

| 2.4  | (a) While Eq. 2.4 is constant w.r.t. power, $R_{on,sp}$ $(T_{on})$ (for different power, $P$ ) varies depending on the degree of self-heating. As input power increases in a silicon device, self-heating increases as reflected in the curved contour in $R_{on,sp}(T_{on})$ . The blue arrows indicate the direction of increasing values (b) $R_{on,sp}(T_{on})$ vs. $V_{bd}$ for Diamond. The solid lines show $R_{on,sp}$ $(T_{on})$ [Eq. 2.12] for different applied power. BFOM for Diamond is given as the black dotted line. At T=300 K and 523 K, Eq. 2.12 matches the numerical results from [111], shown as dashed-dotted lines. The black arrow shows the turn-around for Diamond. Data from [121] and [122] are plotted as well for reference. | 56 |

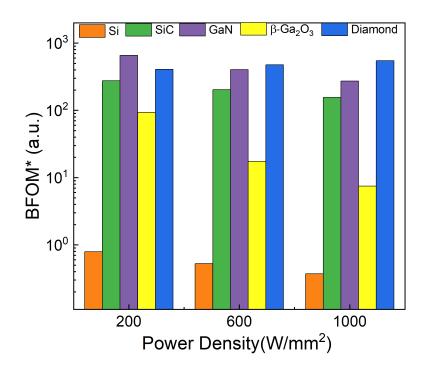

| 2.5  | $\operatorname{BFOM}^*$ calculated for different WBG materials at different power density.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57 |

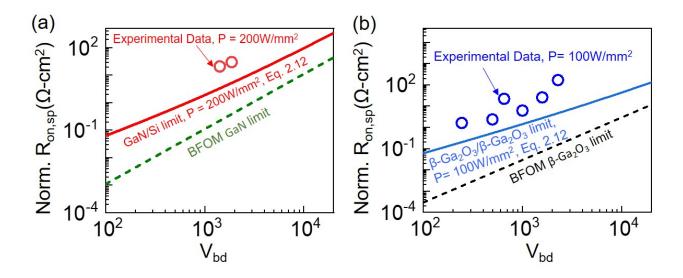

| 2.6  | $R_{on,sp}(T_{on})$ (Eq. 2.12) predicted for bilayer GaN and $\beta$ - $Ga_2O_3$ structures at $P = 1 \text{ kW/mm}^2$ in comparison to the experimental data on bilayer structures.<br>As an example, (a) GaN-on-Silicon [Data taken from [126]] and (b) $\beta$ - $Ga_2O_3$ -on- $\beta$ - $Ga_2O_3$ device have been shown here. Data taken from [127]                                                                                                                                                                                                                                                                                                                                                                                                    | 58 |

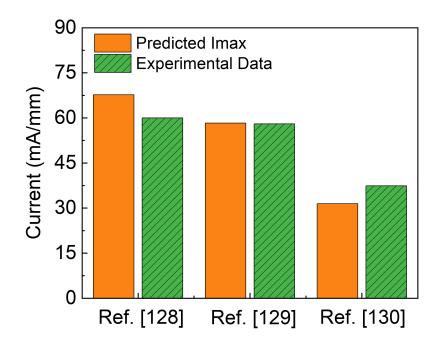

| 2.7  | Comparison of maximum current predicted by Eq. 2.13 with that of experi-<br>mental data from Refs. [128]–[130]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60 |

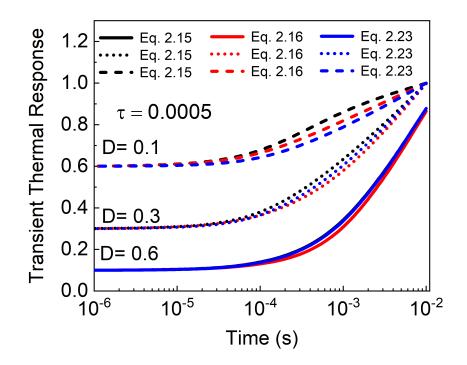

| 2.8  | Comparison of expressions for transient thermal responses of a packaged chip<br>derived using superposition principle ( $Z_1(\text{Eq. 2.15})$ and $Z_2(\text{Eq. 2.16})$ ) and<br>the closed form analytical solution derived in this chapter ( $Z_m$ (Eq. 2.23).<br>For the comparison, the thermal time constant, $\tau$ ( $\tau_{th}$ ) was taken as 0.0005,<br>which is a typical value for microchips. Although the curves are obtained for<br>three values of duty cycles ( $D = 0.1, 0.3$ and 0.6), matching of $Z_3$ with $Z_1$<br>and $Z_2$ has been confirmed at other values of duty cycles and thermal time<br>constants as well.                                                                                                               | 63 |

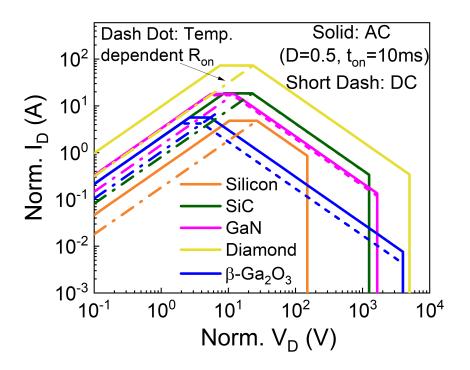

| 2.9  | <i>i</i> -SOA predicted for various bulk WBG materials                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

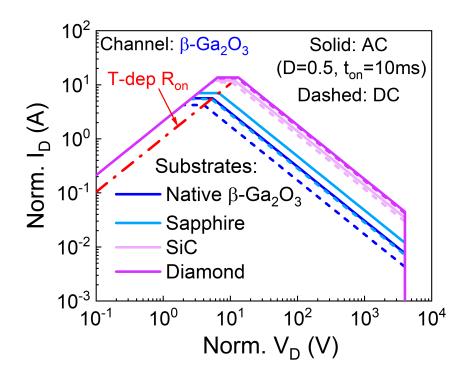

| 2.10 | <i>i</i> -SOA predicted for bilayer substrates. $\beta$ -Ga <sub>2</sub> O <sub>3</sub> on various substrates (native $\beta$ -Ga <sub>2</sub> O <sub>3</sub> , Sapphire, SiC, Diamond) are shown here as an example.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 65 |

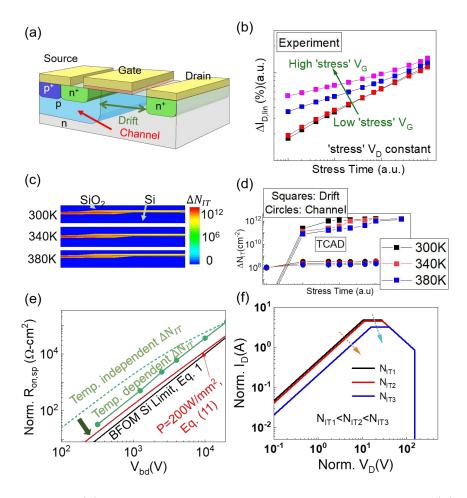

| 2.11 | (a) Schematic of the Si LDMOS used in the study. (b) TCAD calibration of<br>the temperature dependent HCD characteristics of the LDMOS. (c) The 2D<br>plots showing the Si/SiO <sub>2</sub> interface and trap generation in the interface, in a<br>Si LDMOS. (d) $\Delta N_{it}$ with increasing stress time at different temperatures. (e)<br>Reliability-aware $R_{on,sp}$ or $R^*_{on,sp}$ predicted for silicon power devices (LDMOS)<br>(f) Reliability-aware <i>i</i> -SOA predicted for LDMOS device at different interface<br>trap concentrations | 67 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

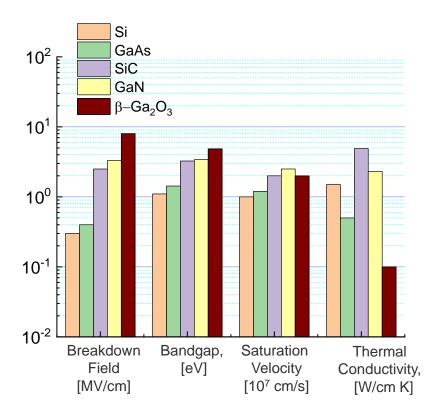

| 3.1  | Properties of wide bandgap semiconductors used in power electronics $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72 |

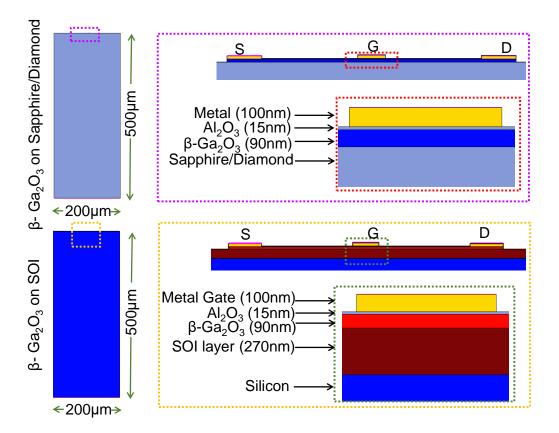

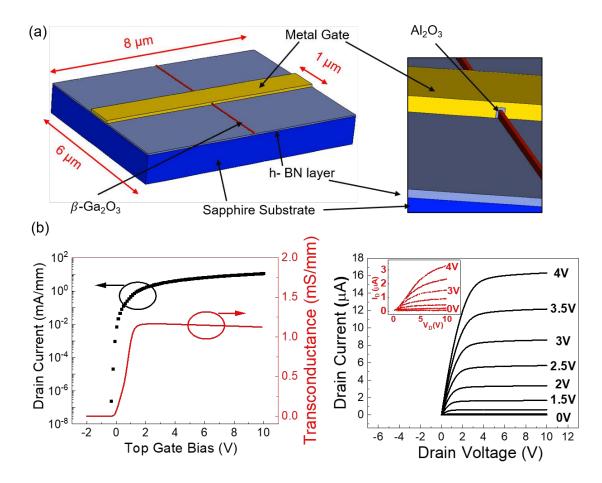

| 3.2  | Device structures in Synopsis TCAD Simulator. The dimensions of the device are taken from fabricated devices in Refs. [16] and [124]. The substrate was considered to be n-doped with concentration of $2.7 \times 10^{18}/\text{cm}^3$ . The electron mobilities were determined by fitting and it was found to be 49, 36 and 23 cm <sup>2</sup> /V-s in case of Diamond, Sapphire and SOI substrates respectively.                                                                                                                                       | 73 |

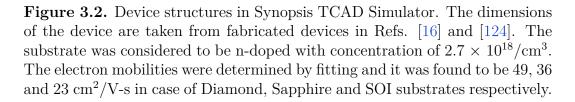

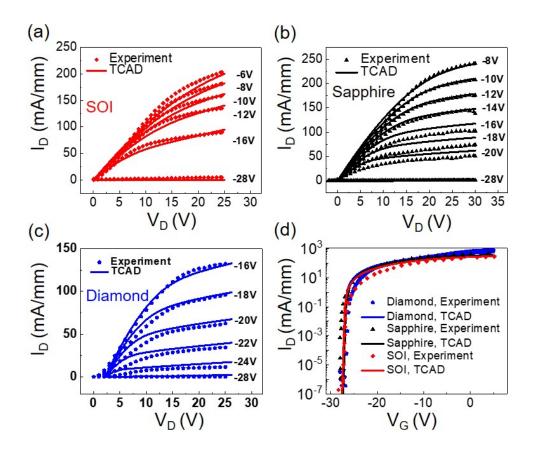

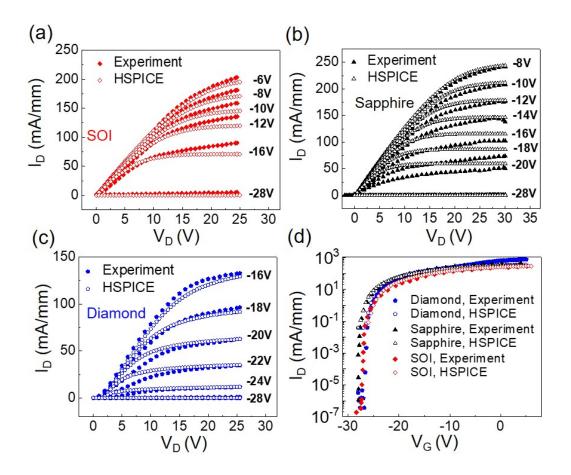

| 3.3  | Output characteristics obtained from experiments [16], [124], and TCAD and for (a) SOI (b) Sapphire (c) Diamond. (d) Transfer characteristics of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FETs on the three substrates and TCAD outputs. The TCAD model reproduces the experimental data accurately.                                                                                                                                                                                                                                                        | 74 |

| 3.4  | Output characteristics obtained from experiments [16], [124], and TCAD and for (a) SOI (b) Sapphire (c) Diamond. (d) Transfer characteristics of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FETs on the three substrates and TCAD outputs. The TCAD model reproduces the experimental data accurately.                                                                                                                                                                                                                                                        | 75 |

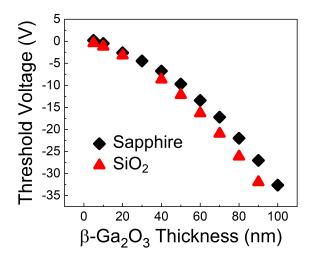

| 3.5  | The threshold voltage dependence on channel thickness. The standard D-<br>mode FETs must be pinched-off to be turned off, therefore thinner epitaxial<br>layer is required to fully deplete the channel at 0 V.                                                                                                                                                                                                                                                                                                                                            | 76 |

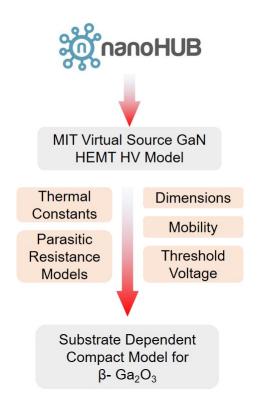

| 3.6  | A flow chart for the construction of the $\beta$ - $Ga_2O_3$ compact model for circuit simulation.                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77 |

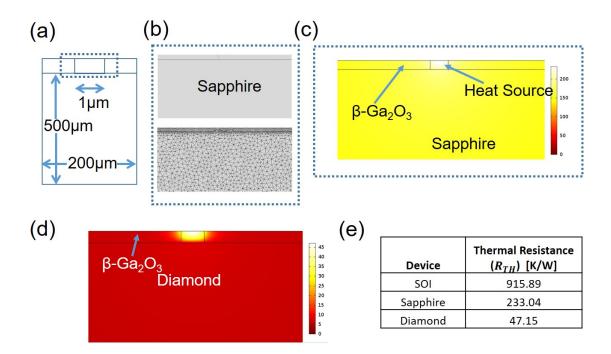

| 3.7  | (a) Simulation structure in COMSOL (not to scale). (b) A magnified image of the device and meshing. The temperature (thermal resistance) plots obtained for (c) Sapphire (d) Diamond. The peak values are tabulated in (e)                                                                                                                                                                                                                                                                                                                                 | 78 |

| 3.8  | Output characteristics obtained from experiments, [16], [124], and HSPICE compact model for (a) SOI (b) Sapphire (c) Diamond. (d) Transfer characteristics of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FETs on the three substrates and TCAD outputs. The TCAD model reproduces the experimental data accurately.).                                                                                                                                                                                                                                         | 79 |

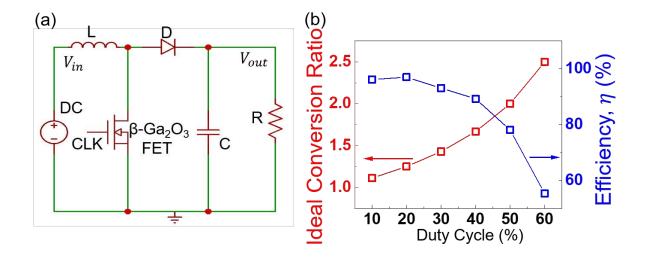

| 3.9  | The boost converter circuit used in our analysis. Circuit parameters: Induc-<br>tor, L = 3000 $\mu$ H, FET= $\beta$ -Ga <sub>2</sub> O <sub>3</sub> on SOI/Sapphire/Diamond, Capacitance,<br>C= 50 $\mu$ F, D = Diode, Load resistance, R= 2000 $\Omega$ , $V_{in}$ = Input Voltage, $V_{out}$<br>= Output Voltage. For the diode, SBR3U100LP with forward voltage drop,<br>$V_F$ = 0.79 V and total capacitance, $C_T$ = 800 $pF$ , has been used. (b) Ideal<br>conversion ratio and efficiency vs. duty cycle of the boost converter circuit.            | 80 |

|      | conversion ratio and enciency vs. duty cycle of the boost converter circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00 |

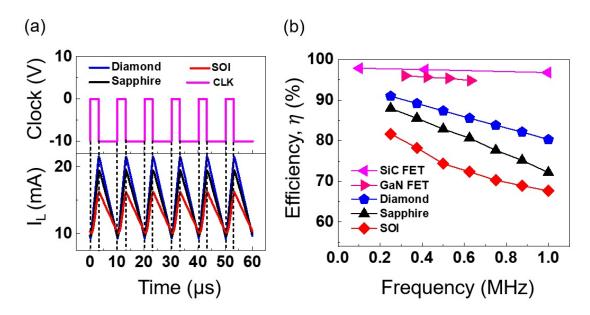

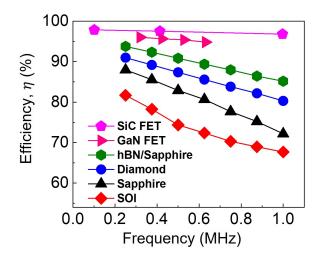

| 3.10 | (a) Inductor current $(I_L)$ of the boost converter circuit. The clock input is<br>with 30% duty cycle and the driving voltage is from 0 to -10 V. (b) Efficiency of<br>the circuit with a SiC FET [163], GaN FET [164], $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FET on Diamond<br>(500 $\mu$ m), Sapphire (500 $\mu$ m), and SOI (270nm/500 $\mu$ m). The mobility in<br>case of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FET on hBN (50nm)/ Si (100 $\mu$ m) is assumed to be three<br>times to that of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FET on Diamond (500 $\mu$ m) to account for improved<br>heat conduction. | 81 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

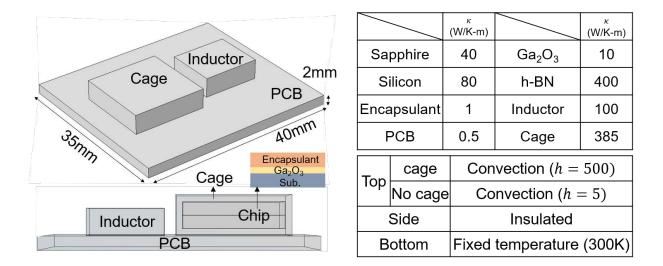

| 3.11 | (a) System level simulation schematic of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> FET on various substrates.<br>'Cage' refers a 'thermal Faraday Cage' which allows heat flux shielding. (b)<br>The table summarizes the material properties, and boundary conditions for<br>FEM simulations                                                                                                                                                                                                                                                                                                                               | 82 |

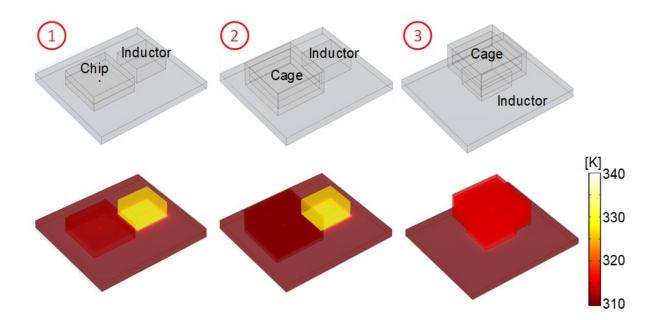

| 3.12 | Temperature distribution comparison among different packaging configura-<br>tion. Inductor temperature of vertical stack shows a considerable reduction<br>in mutual heating effect through the use of a thermal Faraday cage                                                                                                                                                                                                                                                                                                                                                                                             | 83 |

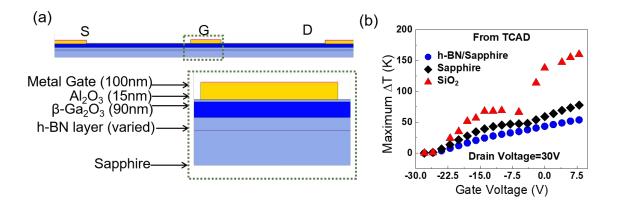

| 3.13 | (a) Proposed h-BN based FET. (b) Maximum $\Delta T$ rise for h-BN/Sapphire is almost half as that of Sapphire, and almost $1/6^{\text{th}}$ of that of SiO <sub>2</sub> ( $V_{DS} = 30$ V).                                                                                                                                                                                                                                                                                                                                                                                                                               | 84 |

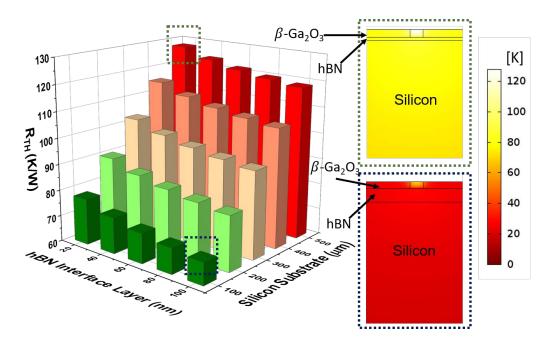

| 3.14 | A $\beta$ -Ga <sub>2</sub> O <sub>3</sub> /hBN/Si FET with various substrate (Silicon) thickness and interface layer (hBN) thickness. The plots on the right shows the temperature profile of FET at the respective Silicon and hBN layer thickness                                                                                                                                                                                                                                                                                                                                                                       | 85 |

| 3.15 | TCAD model of Enhancement mode wrap gate device on h-BN. (b) $I_D-V_G$ of the $\beta$ - $Ga_2O_3$ FET on h-BN coated Sapphire substrate, as obtained from TCAD simulation. (c). $I_D-V_D$ data with $\beta$ - $Ga_2O_3$ FET on h-BN coated Sapphire substrate, obtained from TCAD, which is about 500% more than the experimental data from [127], given in inset.                                                                                                                                                                                                                                                        | 86 |

| 3.16 | Efficiency of the boost converter circuit, with hBN/Sapphire configuration. $\ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87 |

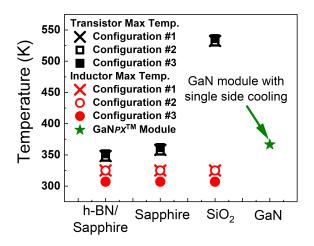

| 3.17 | Transistor and inductor temperature comparison among various packaging strategies. GaN data taken from [172]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 88 |

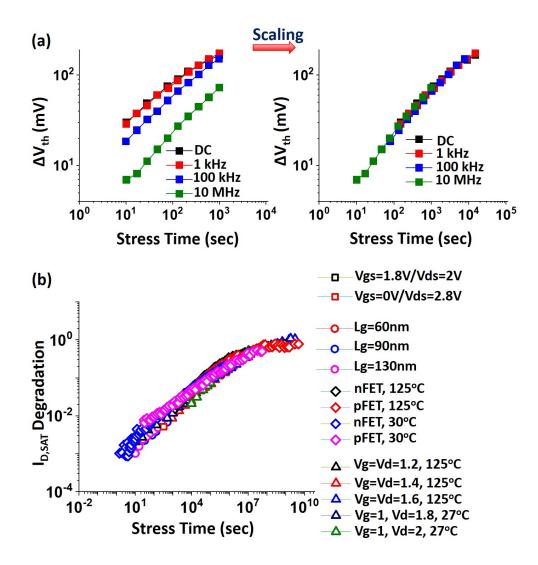

| 4.1  | <ul> <li>(a) Methodology of scaling the data to a universal curve, taken from [2].</li> <li>(b) Universal scaling curve obtained from various technologies (DMOS, Fin-FETs), gate lengths, operating voltages, temperatures, suggesting that the underlying mechanism of HCD is universal [2].</li> </ul>                                                                                                                                                                                                                                                                                                                 | 91 |

| 4.2  | (a) HCD data of a silicon LDMOS transistor. (b) The data from (a) are scaled laterally to see if they form a universal degradation curve (black solid line). Clearly, the data cannot be described by a single universal curve                                                                                                                                                                                                                                                                                                                                                                                            | 92 |

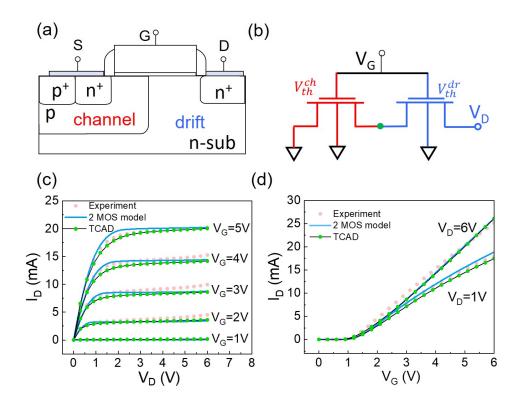

| 4.3  | (a) Representative cross-section of a Silicon LDMOS device (b) 2 MOS model.<br>S, G, D, $V_{th}^{ch}$ and $V_{th}^{dr}$ are the source, gate, drain, threshold voltage of channel MOSFET and drift MOSFET, respectively. The green dot is the metallurgical junction between the two MOS. Calibration of the model with TCAD and                                                                                                                                                                                                                                                                                          |    |

|      | Experiments is shown in (c) and (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

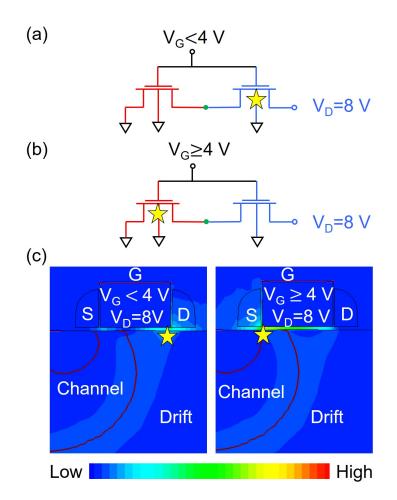

| 4.4  | Position of peak electric field (represented by a star) is the drift MOS for (a) $V_G < V_D/2$ and in the channel MOS for (b) $V_G \ge V_D/2$ . The corresponding electric field profiles are shown in (c)                                                       | 98   |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

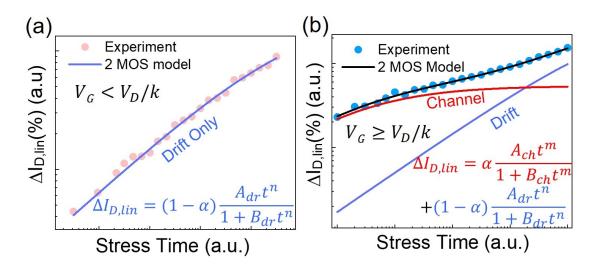

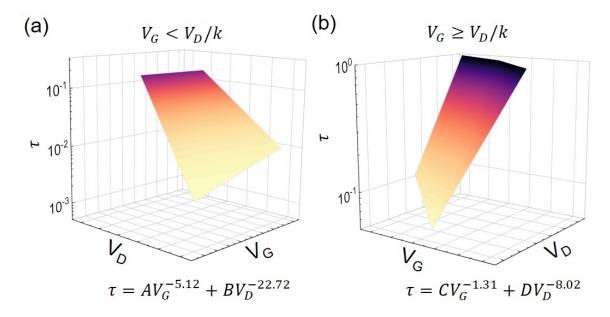

| 4.5  | Two sets of data from Fig. 4.1, fitted with Eq. 4.13 at (a) $V_G < V_D/k$ and (b) $V_G \ge V_D/k$ , where $k=2$ , for the device in consideration. The same time exponent $n \sim m$ was assumed for the fitting. For both cases $V_D$ is fixed at 8 V           | .101 |

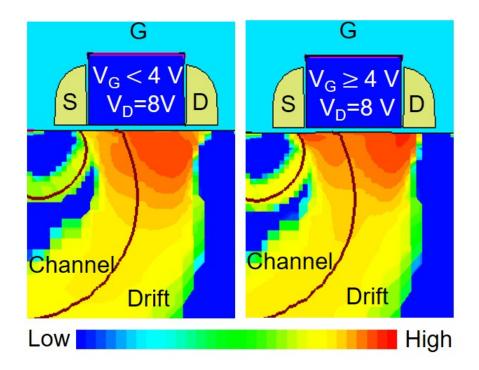

| 4.6  | Impact ionization profiles for $V_G < V_D/2$ (left) and $V_G \ge V_D/2$ (right). At high $V_G$ , significant amount of impact ionization is present in the channel and the drift region.                                                                         | 102  |

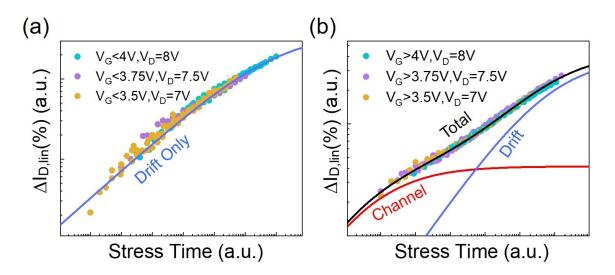

| 4.7  | Data from Fig. 4.1, replotted by two-component universal scaling at (a) $V_G < V_D/k$ and (b) $V_G \ge V_D/k$ , where $k = 2. \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                           | 104  |

| 4.8  | Voltage acceleration of the scaling factor, $\tau$ , for (a) $V_G < V_D/k$ and (b) $V_G \ge V_D/k$ , where $k = 2$ . The difference of the exponents reflects voltage partitioning between the channel and drift regions. A, B, C, and D are fitting parameters. | 105  |

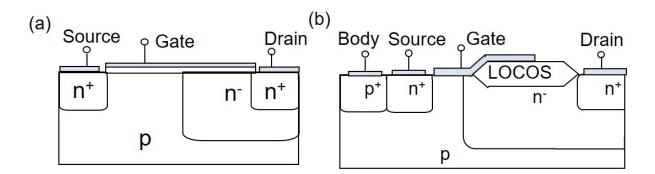

| 5.1  | A schematic of (a) non-LOCOS LDMOS, and a (b) LOCOS LDMOS                                                                                                                                                                                                        | 109  |

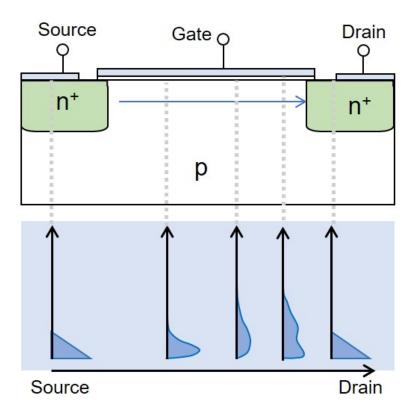

| 5.2  | Schematic representation of EEDF evolution, from source to drain in a MOS-FET                                                                                                                                                                                    | 111  |

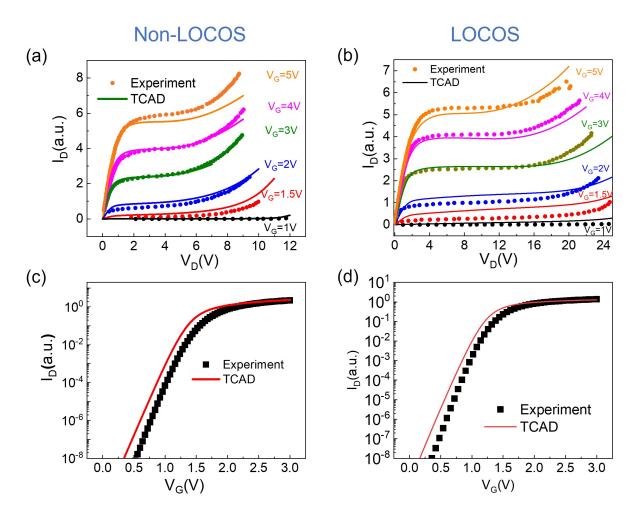

| 5.3  | TCAD Calibration of the output and transfer characteristics of a non-LOCOS LDMOS ((a) & (c)), and a LOCOS LDMOS ((b) & (d)), respectively                                                                                                                        | 116  |

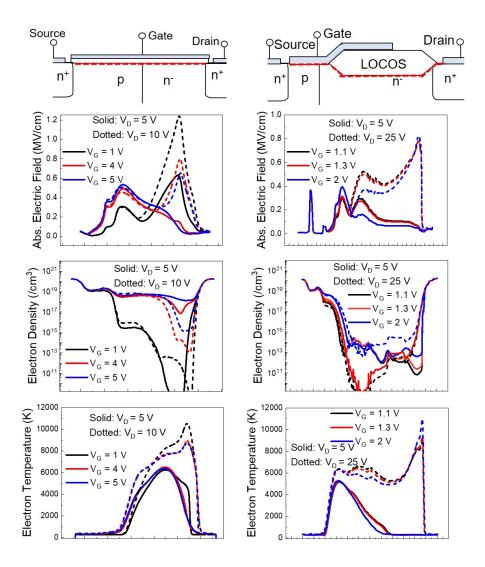

| 5.4  | Cutline plots for absolute electric field (MV/cm), electron density (cm <sup><math>-3</math></sup> ), and electron temperature (K) at the Si-SiO <sub>2</sub> interface, obtained from TCAD for a non-LOCOS LDMOS and a LOCOS LDMOS.                             | 118  |

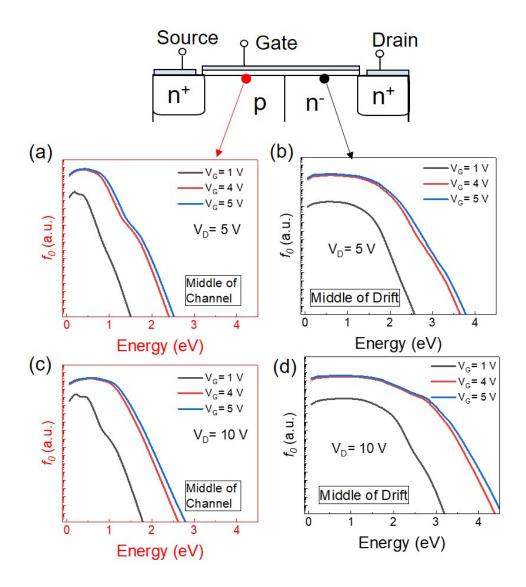

| 5.5  | EEDF of the non-LOCOS LDMOS. EEDF of a selected point in the middle of the channel at (a)low $V_D$ (5 V) and (c) high $V_D$ (10 V). EEDF of a selected point in the middle of the drift at (b)low $V_D$ (5 V) and (d) high $V_D$ (10 V).                         | 119  |

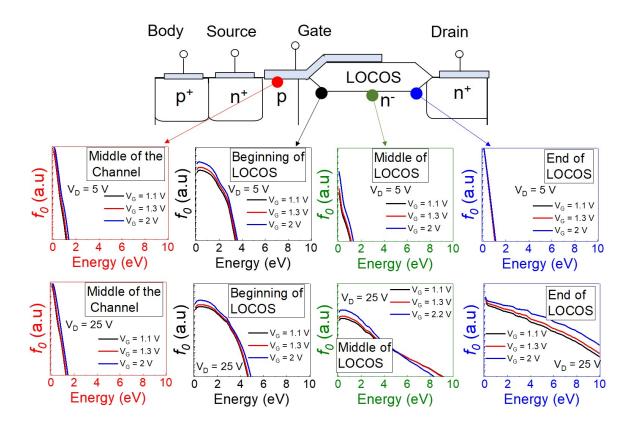

| 5.6  | The EEDF profiles of various selected points of LOCOS LDMOS                                                                                                                                                                                                      | 120  |

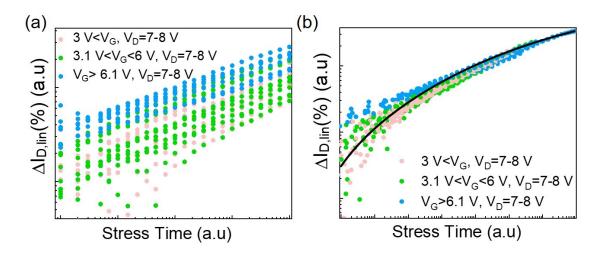

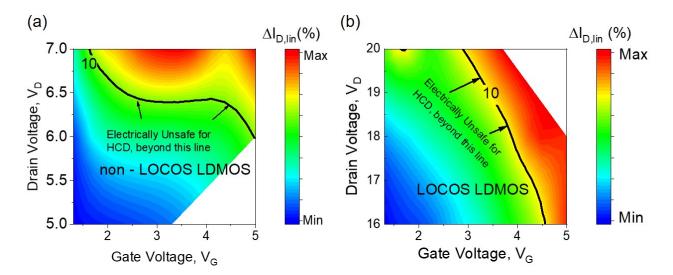

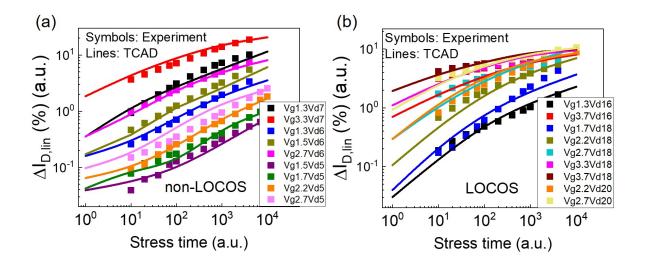

| 5.7  | Experimentally measured HC-SOA, obtained by monitoring $\Delta I_{D,lin}(\%)$ for<br>(a) non-LOCOS LDMOS and (b) LOCOS LDMOS, after stressing for an<br>arbitrary time.                                                                                          | 122  |

| 5.8  | TCAD Calibration of $\Delta I_{D,lin}(\%)$ using HCS degradation model in TCAD, for<br>(a) non-LOCOS LDMOS and (b) LOCOS LDMOS                                                                                                                                   | 126  |

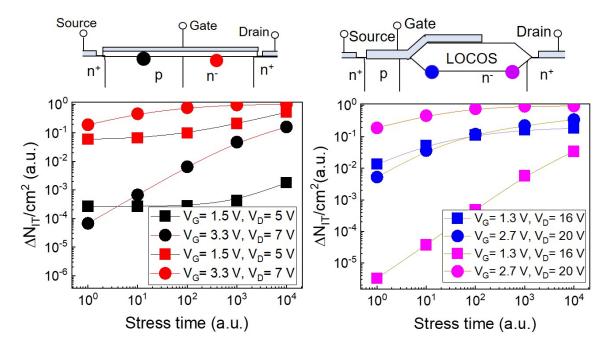

| 5.9  | Interface trap determination, at various points in non-LOCOS and (b) LO-COS LDMOS                                                                                                                                                                                | 127  |

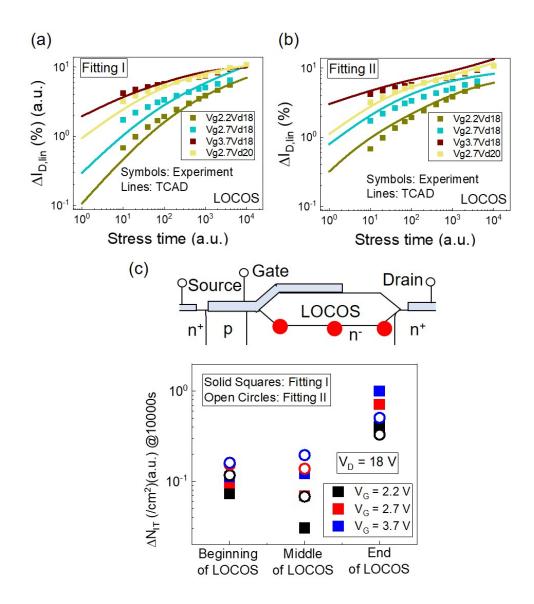

| 5.10 | Fitting of the experimental degradation curves using two different sets of parameters (a & b). (c) The $\Delta N_{it}$ values determined from two fittings appear to vary, but with similar trends.                                                              | 198  |

|      | vo vary, ouv wrun simmar uronus                                                                                                                                                                                                                                  | 140  |

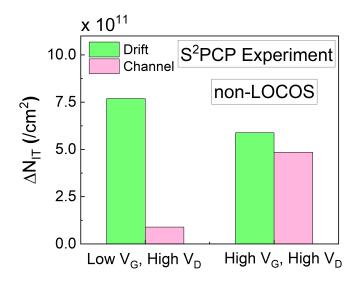

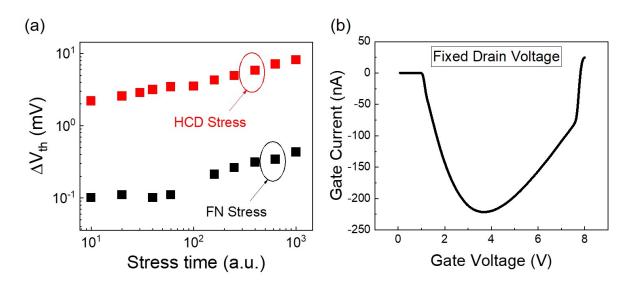

| <ul> <li>5.12 (a) Degradation due to FN stress and HCD stress in a non-LOCOS LDMOS. (b) Measured gate current at a fixed drain bias and varying gate bias</li></ul>                                                                                                                                                                                                                                               | 11 Determination of $\Delta N_{it}$ in the channel and the drift region, using S <sup>2</sup> PCP Technique                                                                                                                                                                                                                                                                                                       | 129 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

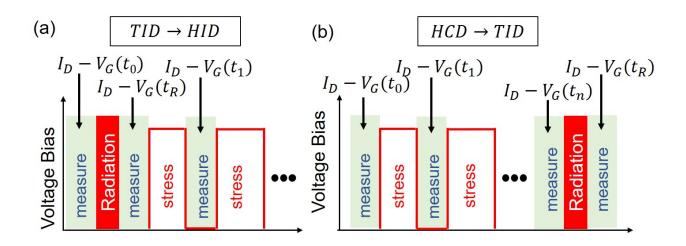

| <ul> <li>6.2 Experimental setups (a) TID followed by HCD (b) HCD followed by TID. I<sub>D</sub> - V<sub>G</sub>(t<sub>0</sub>), I<sub>D</sub> - V<sub>G</sub>(t<sub>R</sub>), and I<sub>D</sub> - V<sub>G</sub>(t<sub>R</sub>) is the pristine transfer characteristics, post-radiation transfer characteristics, and the final-time transfer characteristics of the device, respectively</li></ul>               |                                                                                                                                                                                                                                                                                                                                                                                                                   | 131 |

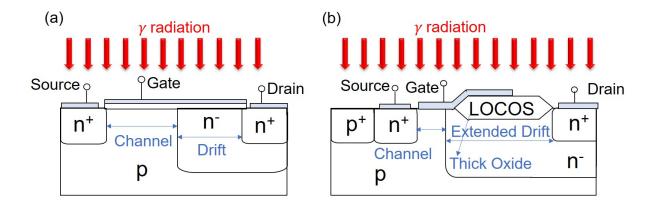

| $\begin{split} I_D - V_G(t_0), \ I_D - V_G(t_R), \ \text{and} \ I_D - V_G(t_n) \ is the pristine transfer characteristics, post-radiation transfer characteristics, and the final-time transfer characteristics of the device, respectively $                                                                                                                                                                     | 1 Schematic of (a) non-LOCOS and (b) LOCOS LDMOS, exposed to $\gamma$ radiation.                                                                                                                                                                                                                                                                                                                                  | 135 |

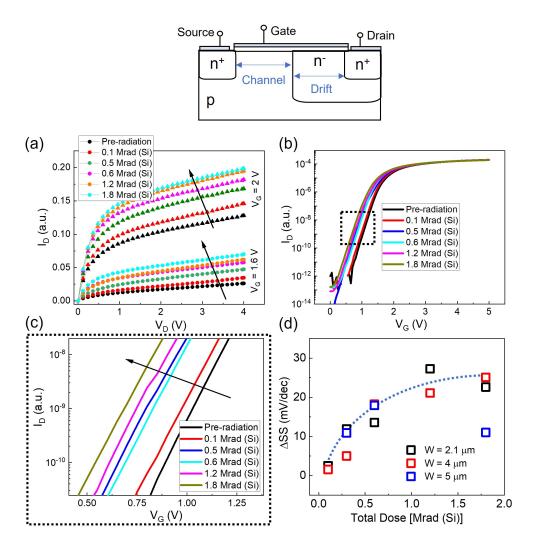

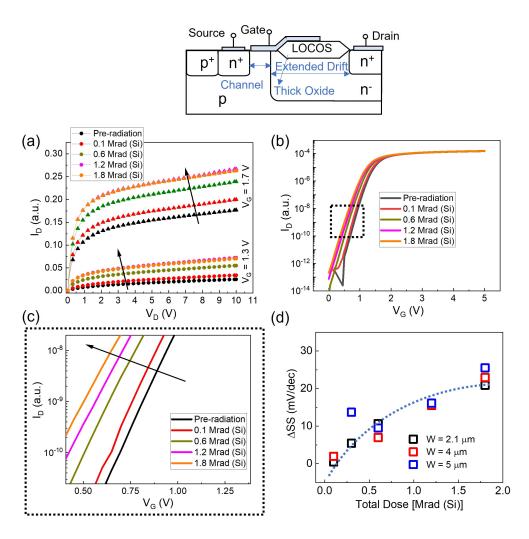

| TID: 0.1, 0.5, 0.6, 1.2 and 1.8 Mrad (Si). (b) Dose-dependent $I_D - V_G$ plot<br>of LDMOS devices. (c) A blown-up snapshot of the $I_D - V_G$ plot showing<br>the impact of $\Delta N_{ot}$ . (d) Change in subthreshold slope (SS) of the LDMOS<br>under different TID. An eye-guide (blue dotted lines) is added to visualize<br>the saturation trend                                                          | $I_D - V_G(t_0)$ , $I_D - V_G(t_R)$ , and $I_D - V_G(t_n)$ is the pristine transfer characteristics, post-radiation transfer characteristics, and the final-time transfer                                                                                                                                                                                                                                         | 136 |

| TID: 0.1, 0.6, 1.2 and 1.8 Mrad (Si). (b) Dose-dependent $I_D - V_G$ plot of<br>LDMOS devices. (c) A blown-up snapshot of the $I_D - V_G$ plot showing the<br>impact of $\Delta N_{ot}$ . (d) Change in subthreshold slope (SS) of the LDMOS un-<br>der different TID. An eye-guide (blue dotted lines) is added to visualize the<br>saturation trend                                                             | TID: 0.1, 0.5, 0.6, 1.2 and 1.8 Mrad (Si). (b) Dose-dependent $I_D - V_G$ plot<br>of LDMOS devices. (c) A blown-up snapshot of the $I_D - V_G$ plot showing<br>the impact of $\Delta N_{ot}$ . (d) Change in subthreshold slope (SS) of the LDMOS<br>under different TID. An eye-guide (blue dotted lines) is added to visualize                                                                                  | 137 |

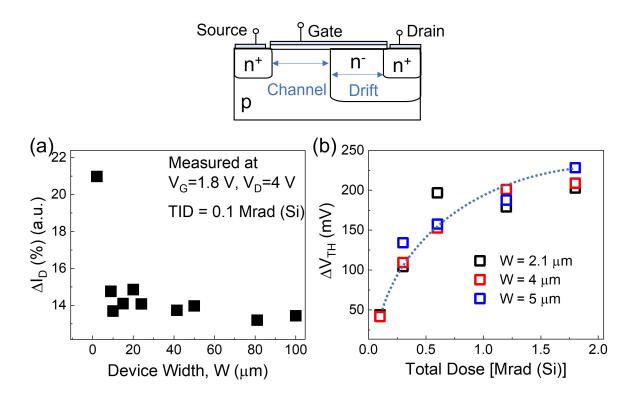

| <ul> <li>LDMOS devices. (b) Dose-dependent V<sub>TH</sub> variation. An eye-guide (blue dotted lines) is added to visualize the saturation trend</li></ul>                                                                                                                                                                                                                                                        | TID: 0.1, 0.6, 1.2 and 1.8 Mrad (Si). (b) Dose-dependent $I_D - V_G$ plot of LDMOS devices. (c) A blown-up snapshot of the $I_D - V_G$ plot showing the impact of $\Delta N_{ot}$ . (d) Change in subthreshold slope (SS) of the LDMOS under different TID. An eye-guide (blue dotted lines) is added to visualize the                                                                                            | 138 |

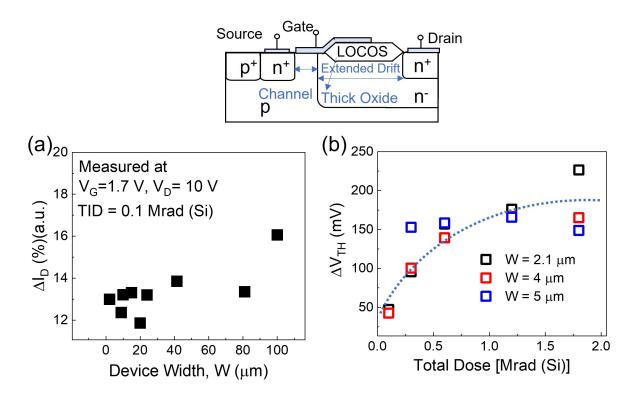

| <ul> <li>devices. (b) Dose-dependent V<sub>TH</sub> variation. An eye-guide (blue dotted lines) is added to visualize the saturation trend</li></ul>                                                                                                                                                                                                                                                              | LDMOS devices. (b) Dose-dependent $V_{TH}$ variation. An eye-guide (blue                                                                                                                                                                                                                                                                                                                                          | 139 |

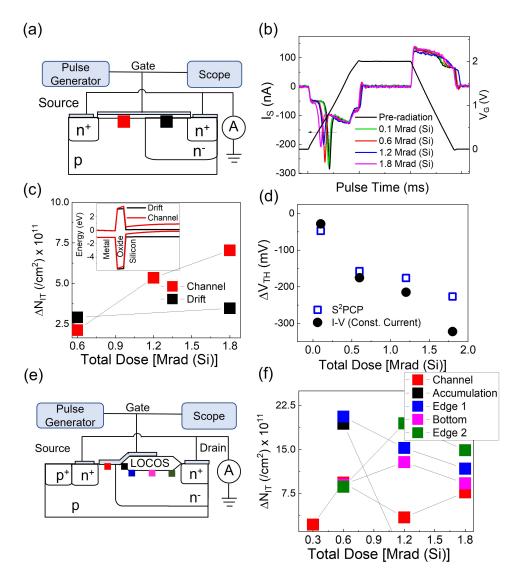

| dependent transient current, for floated source configuration. (c) Extraction<br>of $N_{it}(x)$ , using the transient current. (d) Threshold voltage shift measured<br>from the transient currents                                                                                                                                                                                                                | devices. (b) Dose-dependent $V_{TH}$ variation. An eye-guide (blue dotted lines)                                                                                                                                                                                                                                                                                                                                  | 140 |

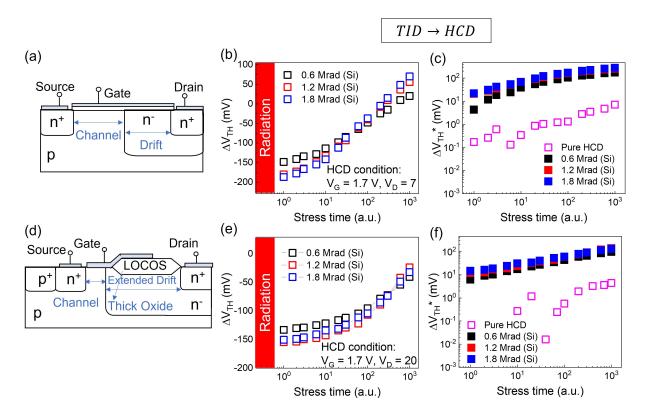

| degradation due to HCD, preceded by TID, for a non-LOCOS LDMOS. (c)<br>Extraction of $\Delta V_{TH}^*$ , after subtracting the initial shift due to TID. A pure<br>HCD curve is also plotted for comparison. (d) A schematic of the LOCOS<br>LDMOS. (e) Dose-dependent $\Delta V_{TH}$ degradation due to HCD, preceded by<br>TID, for a LOCOS LDMOS. (f) Extraction of $\Delta V_{TH}^*$ , after subtracting the | dependent transient current, for floated source configuration. (c) Extraction of $N_{it}(x)$ , using the transient current. (d) Threshold voltage shift measured                                                                                                                                                                                                                                                  | 142 |

| mulai shift due to 11D. A pure HCD curve is also plotted for comparison. 143                                                                                                                                                                                                                                                                                                                                      | degradation due to HCD, preceded by TID, for a non-LOCOS LDMOS. (c)<br>Extraction of $\Delta V_{TH}^*$ , after subtracting the initial shift due to TID. A pure<br>HCD curve is also plotted for comparison. (d) A schematic of the LOCOS<br>LDMOS. (e) Dose-dependent $\Delta V_{TH}$ degradation due to HCD, preceded by<br>TID, for a LOCOS LDMOS. (f) Extraction of $\Delta V_{TH}^*$ , after subtracting the | 143 |

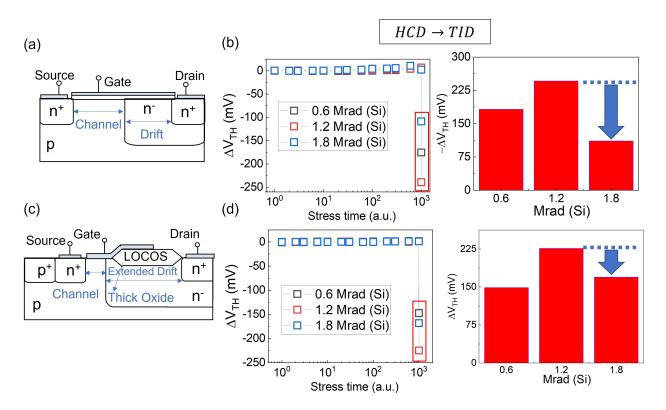

- 6.9 (a) Schematic of the non-LOCOS LDMOS (b)  $\Delta V_{TH}$  degradation due to HCD, followed by TID. A zoomed in image of the decrease in  $\Delta V_{TH}$  (or increase in  $-\Delta V_{TH}$ ) due to increased TID (right). (c) Schematic of the LOCOS LDMOS (d)  $\Delta V_{TH}$  degradation due to HCD, followed by TID. A zoomed in image of the decrease in  $\Delta V_{TH}$  (or increase in  $-\Delta V_{TH}$  due to increased TID (right). 146

### ABSTRACT

We are in the midst of a technological revolution (popularly known as *Industrie 4.0* or 4<sup>th</sup> Industrial Revolution) where our cars are being equipped with hundreds of sensors that make them safer, homes are becoming smarter, industry yields are at an all-time high, and internet-of-things is a reality. This was largely possible due to the developments in communication, electronics, motor controls, robotics, cyber security, software, efficient power distribution, etc. One of the major propellants of the 4<sup>th</sup> Industrial revolution is the ever-expanding applications of power electronics devices. All electrical energy will be provided, handled, and consumed through power electronics devices in the near future. Therefore, the reliability of power electronics devices will be instrumental in driving future technological advances.

A myriad of devices is categorized as power electronics devices, and in the heart of those devices are the transistors. Although Silicon-based transistors still dominate the power electronics market, a paradigm shift towards wide bandgap semiconductors, such as silicon carbide (SiC), gallium nitride (GaN), gallium oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>),etc., is underway. However, realizing the full potential of these devices demands unconventional design, layout, and reliability.

In this thesis, we try to establish a generalized model of reliability for power and logic transistors. We start by defining a comprehensive, substrate-, self-heating-, and reliability-aware safe operating area (SOA) that analytically establishes the optimum and self-consistent trade-off among breakdown voltage, power consumption, operating frequency, heat dissipation, and reliability before actual device fabrication. Then we take a deeper look into the reliability of individual transistors (a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor and a Silicon-based LDMOS), to test the predictions by the safe operating area, using both experiments and simulations. In the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistor, we studied its implementation in a DC-DC voltage converter and concluded that the self-heating is a performance bottleneck and suggested approaches to alleviate it. For the LDMOS transistor, we investigated the hot carrier degradation (HCD) using experiments and simulations. We established that the HCD degradation kinetics is universal, and physics is the same as a classical transistor, despite a complicated geometry.

Finally, we studied the correlation between HCD and radiation in LDMOS used in space shuttles, airplanes, etc., to determine its lifetime.

We have holistically analyzed the reliability of power transistors by extending the theories of logic transistors in this thesis. Therefore, this thesis takes us a step closer to a generalized reliability model for power transistors by developing a comprehensive and predictive model for the safe operating area, encompassing all sources of stresses (e.g., electrical, thermal, and radiation) it experiences during operation.

## 1. INTRODUCTION

#### 1.1 Background

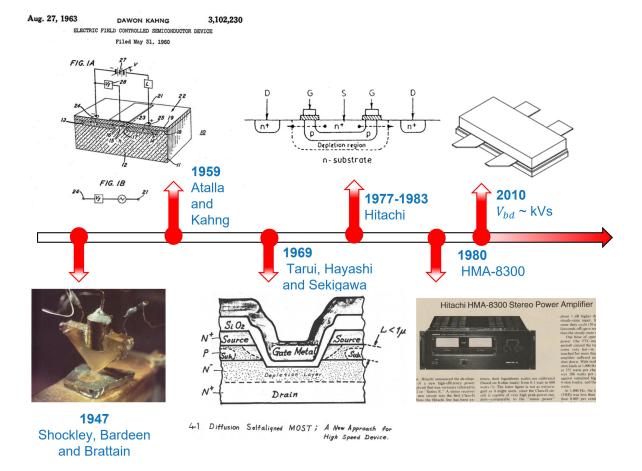

The 4<sup>th</sup> industrial revolution refers to the digitization of manufacturing and production processes in factories using robots, smart machinery, internet-of-things, and artificial intelligence to maximize the yield. This is built upon the 3<sup>rd</sup> industrial revolution, which started with the advent of transistors in the 1950s and transformed the electronics industry. Although conceptualized a few decades earlier, the first working transistor was invented by John Bardeen, Walter Brattain, and William Shockley at Bell Labs in 1947. However, the most widely used transistor, the MOSFET, was demonstrated in 1959 by Mohamed Atalla (a Purdue University alumni) and Dawon Kahng [1]. Since then, MOSFET has been the ubiquitous building block for modern electronics. The evolution of transistors, however, followed two contrasting different routes over the last few decades: (a) Low power transistors or 'Logic' transistors: scaling down the dimensions to accommodate more transistors in a single chip to enhance speed, power, and functionality; (b) High power transistors or simply 'Power' transistors: increasing the capacity of the transistors to handle high power. Although high and low power transistors are used together in an electronic device, the applied biases and operating regimes are incongruous. Consequently, the reliability mechanisms and concerns of logic and power transistors are not the same.

Hot carrier degradation (HCD) and radiation-induced degradation are among the common reliability issues in both logic and power transistors. The focus of this thesis to develop a generalized reliability model which can describe the reliability phenomena (HCD and radiation-induced degradation) in both logic and power transistors. HCD is the phenomenon where energetic electrons traveling from the source to the drain gain enough energy (> 1.5 eV) to break the passivated Si-H and Si-O bonds in the Silicon/oxide interface. Since the drain bias of power transistors is high, HCD is a prominent reliability concern. Historically, radiation-induced defects were a concern for electronics used in high radiation environments (e.g., military and space applications). However, with the heralding of projects like Google Loon, Amazon Prime Air (Drone Delivery), etc., and increasing sensitivity of the chips due to bit flips and single event effects, studies of the impact of radiation on power transistor lifetime are becoming increasingly important. It is of immense interest to study the impact of radiation on the traditional reliability mechanisms as well. In the end, all these degradation mechanism (i.e. HCD, radiation-induced degradation) collectively determine the safe operating area (SOA) of a transistor.

This introductory chapter<sup>1</sup> will discuss the trends of logic and power transistor scaling, basic principles and types of power transistors, the sources, and the effects of HCD and reliability-induced degradations. The current status and an in-depth analysis of these reliability mechanisms will be discussed in the subsequent chapters.

#### 1.2 Logic Transistor Scaling

Nowadays, the computational speed of personal electronics devices is in the gigahertz range and the storage capacity in the terabytes range. This has been possible due to aggressive scaling of the transistors, such that currently, a single chip comprises more than a billion transistors. Historically, transistor count in a chip has increased exponentially, keeping pace with the Moore's law [5]. To pack more and more transistors in a single chip, the dimensions are scaled down such that the power density remains constant, and proportional to the area while scaling both the voltage and current. This law is popularly known as the Dennard scaling law [6]. The chip manufacturers followed Dennard's scaling law until the 1990's by scaling the doping densities, voltages, dielectric thickness, while scaling down the other device dimensions. By the mid-1990s, the power dissipation started to increase as chip manufacturers ran out of options to further scale the parameters (such as the dielectric). This led to innovations like high-k/metal gate architectures to keep up the increasing demand of computational speed. While this led to a solution, for a few generations of transistors, the power dissipation was increasingly becoming a bottleneck until multicore processors were adopted in mid 2000s [7]. While this multicore approach helped manage the power dissipation, the frequency of operation became limited. Besides, the dielectric is already approaching its physical limit ( $\sim 1$  nm), and the transistor architecture is no longer planar. However, the numbers of transistors in a processor are still increasing to this day, as is evident from Fig

<sup>&</sup>lt;sup>1</sup>Some of the content of this chapter is based on Ref. [2], [3]

Figure 1.1. Number of transistors in Apple processors: A series (A8 to A15 Bionic) and M series (M1, M1 Pro and M1 Max). This plot has been constructed from the data available in [4]

1.1, which shows that the number of transistors in Apple processors. This trend has been possible due to constant improvement of fabrication processes, efficient thermal management, and innovative device architectures. Recent innovations like RibbonFET (Intel), Forksheet FET (IMEC), Multi-bridge channel FET (Samsung), Gate-All-Around (GAA) FET (IBM), etc., promises to keep the trend of increasing transistors in a processor, ongoing.

#### **1.2.1** Self-Heating in Logic Transistors

As Dennard scaling in the early 1990s reduced the supply voltage,  $V_D \rightarrow E_g \sim 1$ V, the selfheating made the lattice temperature  $(T_L)$  of the channel higher than that of the substrate  $(T_S)$ , such that  $T_L > T_S$ . The self-heating had already hindered the integration potential of two previous devices technologies (e.g., vacuum tubes and bipolar transistors), and was becoming an important performance metric. Briefly,  $T_L = T_A + (P \times \theta_{th})$  where P is the

**Figure 1.2.** (a) Thermal resistance of bulk, SOI planar and FinFETs with various configurations and GAA nanowire FETs [Replotted from [2]]. (b) Thermal resistance of a 14nm, 10 nm and 7nm bulk Si FinFET [Replotted from [8]].

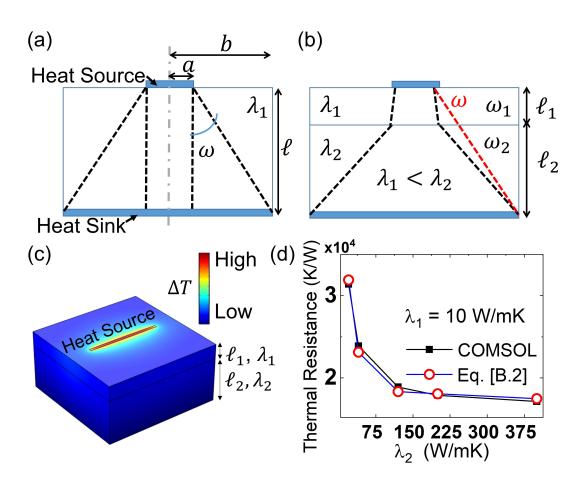

power dissipated by a transistor with area A and thermal resistance  $\theta_{th}$ . Dennard scaling requires  $P = P_0 \times A$ , where  $P_0$  is the power density of a transistor. Keyes calculated the elementary result that thermal resistance depends on effective thermal conductivity,  $\lambda$ , and transistor-substrate shape-factor,  $\alpha$ , such that i.e.  $\theta_{th} = \alpha/(\lambda \times \sqrt{A})$ . This gives [2],[3]:

$$T_L = T_A + P_0 \sqrt{A\alpha/\lambda} \tag{1.1}$$

While for a planar transistor technology,  $\alpha$  and  $\lambda$  are constants, effective  $\lambda$  reduces significantly in non-planar technologies like FinFET. This led to a dramatic increase in  $T_L$  [9]. This is illustrated in Fig 1.2. While FinFET helped manage the short-channel effects through improved electrostatic control, the channel is now surrounded by low-thermal conductivity oxides, which leads to a corresponding increase in the  $\theta_{th}$  and  $T_L$ . Careful modeling in [8] shows that  $\theta_{th}$  increase by more than 40% when fin width is reduced from 14nm to 7nm technology, as shown in Fig 1.2 (b).

While a precise calculation of  $T_L$  due to self-heating is difficult, several attempts has been made to quantify it since 1970s to quantify it. Sesnic and Craig reported  $T_L$  due to self-heating in MOSFETs at cryogenic temperatures (4.2 K) in 1972 [10]. Mautry and Trager reported  $T_L$  due to self-heating in sub- $\mu$ m MOSFETS using dynamic drain current measurements with a time-resolution of 3 ns, in 1989 [11]. Eventually, multiple techniques such as four-terminal gate resistance [12], pulsed I-V [13], AC output conductance [14], etc., have been used to measure average channel temperature. Among them, thermoreflectance is one of the most sophisticated techniques, which uses sub-micrometer illumination sources (~400-800 nm) offering a higher resolution compared to other methods and also enabling mapping of transient heating and cooling kinetics with 50-ns resolutions [15]. Thermoreflectance was used to measure average channel temperature in junction-less transistors ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>), [16], InGaAs GAA FETs [17], extremely thin SOI (ETSOI) [18], etc., which not only provided an accurate  $T_L$  due to self-heating, but also a closer look into the kinetics of reliability mechanisms, like HCD.

## 1.2.2 Hot Carrier Degradation in Logic Transistors: Correlation with Self-Heating

During MOSFET operation, the carriers get accelerated due to applied gate  $(V_G)$  and drain voltage  $(V_D)$ . Some of these carriers, generated during impact ionization at high fields, become energetic (hot) enough to dissociate the passivated Si-H bonds in the semiconductor/oxide interface when injected into the gate, as shown in Fig 1.3 (a). This phenomenon is known as hot carrier degradation (HCD) and has been observed since the early days of MOSFETs [2]. HCD in a classical MOSFET peaked when  $V_G \sim V_D/2$ . This is because, at  $V_G \sim V_D/2$ , barrier height is low enough to inject a significant amount of electrons in the channel, and at the same time, the vertical field at the gate/drain edge is high enough to cause injection into the gate.

The rate of bond dissociation due to HCD is given by [2]:

$$\frac{dN_{it}(E_B, x, t)}{dt} = \sum_{E_B, x} k_f(E_B, T_e, T_L) \left[ (N_0(E_B, x) - N_{it}(E_B, x, t)) \right]$$

(1.2)