## ACCELERATING EMERGING NEURAL WORKLOADS

by

Jacob R. Stevens

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana December 2021

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

#### Dr. Anand Raghunathan, Chair

School of Electrical and Computer Engineering

## Dr. Vijay Raghunathan

School of Electrical and Computer Engineering

## Dr. Kaushik Roy

School of Electrical and Computer Engineering

### Dr. Timothy G. Rogers

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitri Peroulis

## ACKNOWLEDGMENTS

First, I would like to thank my advisor, Dr. Anand Raghunathan, for his guidance and support throughout the past five years. His insights, curiosity, and drive have shaped me as a researcher; his eye for detail, writing feedback, and emphasis on intuitive explanations have improved my skills as a scientific communicator. Moreover, I am also deeply grateful for his care for my personal life, allowing me the flexibility necessary to complete my PhD journey.

I would also like to thank all of the members of my doctoral advisory committee: Dr. Vijay Raghunathan, Dr. Kaushik Roy, and Dr. Timothy Rogers. Their feedback, comments, and suggestions have helped me to deliver the best possible version of my research and thesis. I am thankful for the time that they dedicated to this end.

Next, I would like to thank the members, past and present, of the Integrated Systems Laboratory (ISL), including Dr. Ashish Ranjan, Dr. Shubham Jain, Dr. Younghoon Kim, Dr. Sanchari Sen, Manik Singhal, Sarada Krithivasan, Vinod Ganesan, Sourjya Roy, Shrihari Sridharan, Reena Elangovan, Amrit Nagarajan, Christin David Bose, Surya Selvam, and Aradhana Mohan Parvathy. I appreciate not only the research discussions and collaborations we have had, but also the conversations and fun.

In terms of other influences on my Purdue computer engineering career, I would like to thank Dr. Mark Johnson and Dr. Matthew Swabey for igniting my passion for computer hardware; those late-night, hours-long SoCET meetings were a truly formative time in my academic development. I would also like to thank my lab partner-in-crime for many of these years, Manik Singhal, as well as Everett P. Berry, for their numerous discussions of various technical interests.

Finally, I must thank my family: my parents, Keith and Katharine Stevens, whose hard work and sacrifice laid the foundation that allowed me to end up where I am today and whose love and support gave me the freedom to pursue my dreams. My sister, Allison Stevens, for believing in me and supporting me. And finally, I want to express my love and gratitude to my wife Julia Stevens, for navigating the up and downs of graduate school with me and without whom I could not have gotten through this journey.

# TABLE OF CONTENTS

| LI | ST O | F TAB  | LES                           | <br>10 |

|----|------|--------|-------------------------------|--------|

| LI | ST O | F FIGU | URES                          | <br>11 |

| AI | BSTR | ACT    |                               | <br>13 |

| 1  | INTI | RODUC  | CTION                         | <br>15 |

|    | 1.1  | Feed F | Forward Neural Networks       | <br>16 |

|    | 1.2  | Memo   | bry Augmented Neural Networks | <br>17 |

|    | 1.3  | Transf | former Networks               | <br>19 |

|    | 1.4  | Graph  | n Neural Networks             | <br>19 |

|    | 1.5  | Learne | ed DNN Performance Estimators | <br>20 |

|    | 1.6  | Thesis | s outline                     | <br>21 |

| 2  | REL  | ATED   | WORK                          | <br>22 |

|    | 2.1  | Deep I | Neural Networks               | <br>22 |

|    |      | 2.1.1  | Algorithmic optimizations     | <br>22 |

|    |      | 2.1.2  | Specialized accelerators      | <br>23 |

|    | 2.2  | Memo   | ory-Augmented Neural Networks | <br>24 |

|    |      | 2.2.1  | Algorithmic optimizations     | <br>24 |

|    |      | 2.2.2  | Specialized accelerators      | <br>25 |

|    | 2.3  | Transf | former Networks               | <br>25 |

|    |      | 2.3.1  | Algorithmic optimizations     | <br>25 |

|   |     | 2.3.2  | Specialized accelerators                      | 26 |

|---|-----|--------|-----------------------------------------------|----|

|   | 2.4 | Graph  | Neural Networks                               | 26 |

|   |     | 2.4.1  | Algorithmic optimizations                     | 27 |

|   |     | 2.4.2  | Specialized accelerators                      | 27 |

|   | 2.5 | DNN I  | Performance Estimation                        | 28 |

|   | 2.6 | Thesis | contributions                                 | 28 |

| 3 | BAC | CKGRO  | UND                                           | 31 |

|   | 3.1 | Deep I | Neural Networks                               | 31 |

|   | 3.2 | Memo   | ry-Augmented Neural Networks                  | 32 |

|   |     | 3.2.1  | Neural Turing Machines Overview               | 32 |

|   |     | 3.2.2  | Neural Turing Machines Computational Behavior | 35 |

|   | 3.3 | Transf | former-based Networks                         | 39 |

|   |     | 3.3.1  | Transformers                                  | 39 |

|   |     | 3.3.2  | Softmax Bottlenecks                           | 41 |

|   | 3.4 | Graph  | Neural Networks                               | 41 |

|   |     | 3.4.1  | Graph Definition                              | 42 |

|   |     | 3.4.2  | Graph Sharding                                | 42 |

|   |     | 3.4.3  | Graph Neural Networks                         | 42 |

|   |     | 3.4.4  | GNN Computational Behavior                    | 45 |

|   | 3.5 | DNN I  | Performance Estimators for Edge Devices       | 47 |

|   |     | 3.5.1  | Heterogeneous Edge Devices                     | 48 |

|---|-----|--------|------------------------------------------------|----|

|   |     | 3.5.2  | DNN Performance Estimators                     | 48 |

| 4 |     |        | N ACCELERATOR FOR MEMORY-AUGMENTED NEURAL NET- | 50 |

|   | 4.1 | Introd | uction                                         | 50 |

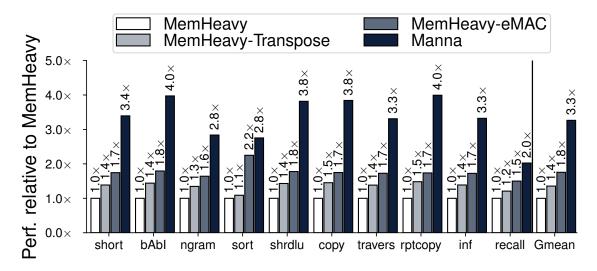

|   | 4.2 | Manna  | a Architecture                                 | 53 |

|   |     | 4.2.1  | Overview                                       | 53 |

|   |     | 4.2.2  | DiffMem Tiles                                  | 54 |

|   |     | 4.2.3  | Controller Tiles                               | 55 |

|   |     | 4.2.4  | Implementing MANNs on Manna                    | 56 |

|   | 4.3 | Manna  | a Software                                     | 62 |

|   |     | 4.3.1  | Execution Model and ISA                        | 62 |

|   |     | 4.3.2  | Compiler                                       | 63 |

|   |     |        | Code Mapping                                   | 63 |

|   |     |        | Code Generation                                | 64 |

|   | 4.4 | Exper  | imental Setup                                  | 65 |

|   | 4.5 | Result | S                                              | 67 |

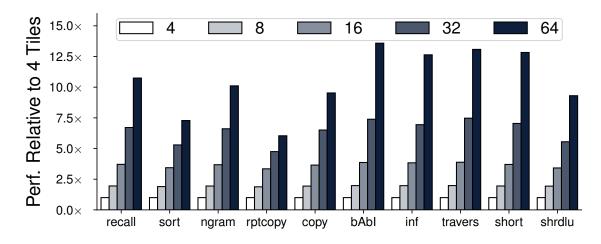

|   |     | 4.5.1  | Inference Performance                          | 67 |

|   |     | 4.5.2  | Energy Efficiency                              | 69 |

|   |     | 4.5.3  | Manna Scaling                                  | 70 |

|   |     | 4.5.4  | Ablation Study                                                      | 72 |

|---|-----|--------|---------------------------------------------------------------------|----|

|   | 4.6 | Conclu | usion                                                               | 72 |

| 5 |     |        | AX: HARDWARE/SOFTWARE CO-DESIGN OF AN EFFICIENT<br>FOR TRANSFORMERS | 74 |

|   | 501 | IMAA   |                                                                     | 14 |

|   | 5.1 | Introd | uction                                                              | 74 |

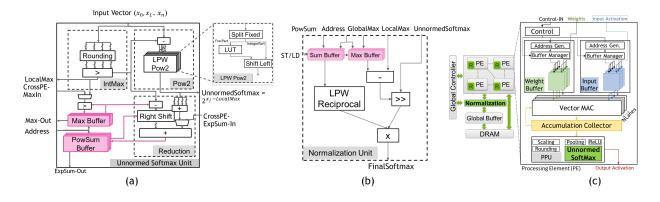

|   | 5.2 | Softe  | rmax Software                                                       | 76 |

|   |     | 5.2.1  | Base Replacement                                                    | 76 |

|   |     | 5.2.2  | Low-precision Softmax Operations                                    | 77 |

|   |     | 5.2.3  | Hardware-friendly Online Normalization                              | 78 |

|   | 5.3 | Softe  | rmax Hardware                                                       | 79 |

|   |     | 5.3.1  | Unnormed Softmax Unit                                               | 79 |

|   |     | 5.3.2  | Normalization Unit                                                  | 81 |

|   |     | 5.3.3  | Accelerator Integration                                             | 81 |

|   | 5.4 | Exper  | imental Setup                                                       | 81 |

|   | 5.5 | Evalua | ation                                                               | 82 |

|   |     | 5.5.1  | Impact on Accuracy                                                  | 82 |

|   |     | 5.5.2  | Impact on Hardware Efficiency                                       | 83 |

|   | 5.6 | Conclu | usion                                                               | 85 |

| 6 | GNN | JERAT  | OR: A HARDWARE/SOFTWARE FRAMEWORK FOR ACCELER-                      |    |

|   |     |        | APH NEURAL NETWORKS                                                 | 86 |

|   | 6.1 | Introd | uction                                                              | 86 |

| 6.2 | GNNe   | erator Architecture                                    | 89 |

|-----|--------|--------------------------------------------------------|----|

|     | 6.2.1  | Dense Engine Overview                                  | 89 |

|     | 6.2.2  | Graph Engine Overview                                  | 90 |

|     | 6.2.3  | GNNerator Controller                                   | 92 |

|     | 6.2.4  | ISA                                                    | 92 |

| 6.3 | GNNe   | erator Execution Model                                 | 93 |

|     | 6.3.1  | Graph Execution Model Overview                         | 93 |

|     | 6.3.2  | Dense Execution Model Overview                         | 98 |

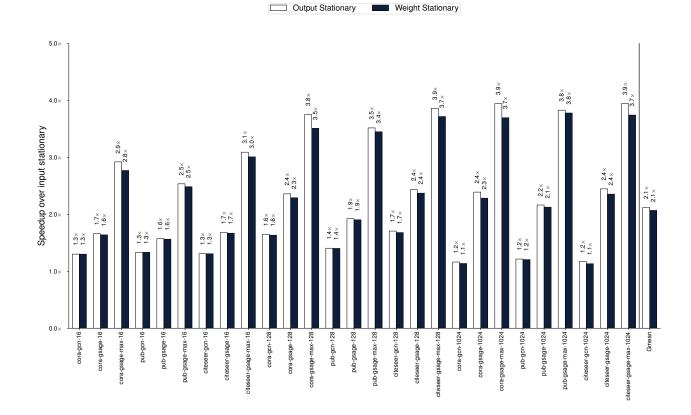

|     | 6.3.3  | GNN Accelerator Design Space                           | 98 |

| 6.4 | Progra | amming GNNerator                                       | 99 |

|     | 6.4.1  | Compiler                                               | 99 |

|     |        | Edge Layout Optimization                               | 01 |

|     |        | Feature Memory Layout Optimization                     | 02 |

| 6.5 | Metho  | dology                                                 | 02 |

| 6.6 | Evalua | $\operatorname{ation}$                                 | 04 |

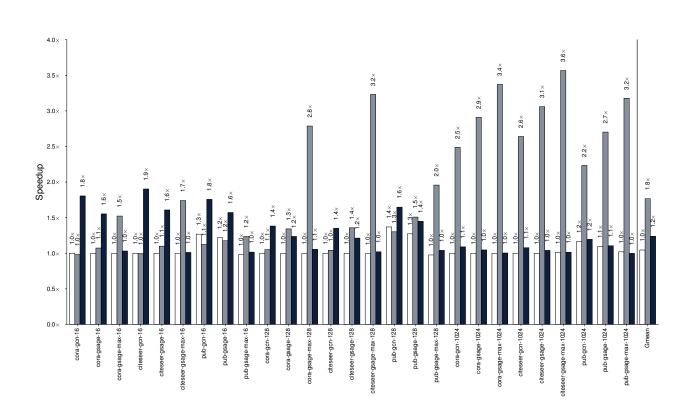

|     | 6.6.1  | Performance                                            | 04 |

|     | 6.6.2  | Scaling                                                | 06 |

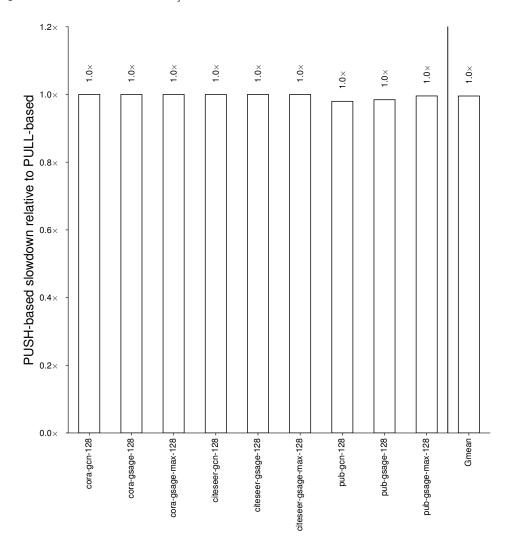

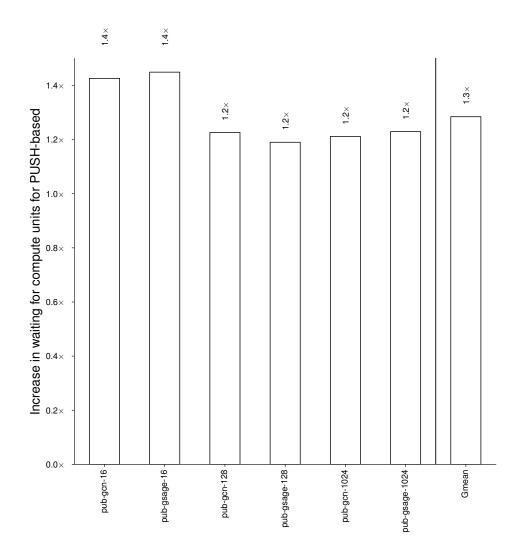

|     | 6.6.3  | Architecture Design Space Exploration                  | 09 |

| 6.7 | Conch  | usion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ | 12 |

| 7  | HAR  | DWAR   | E-AWARE PERFORMANCE ESTIMATORS FOR HETEROGENEOUS                                                                                           |   |

|----|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | EDG  | E SYS  | $TEMS \dots \dots$                   | 4 |

|    | 7.1  | Introd | $\mathrm{uction}$                                                                                                                          | 4 |

|    | 7.2  | Learne | ed Performance Estimators for DNNs: A Taxonomy                                                                                             | 6 |

|    |      | 7.2.1  | Estimation Hierarchy                                                                                                                       | 6 |

|    |      | 7.2.2  | Layer-level Performance Estimators                                                                                                         | 7 |

|    |      | 7.2.3  | Layer-level vs Network-level Features                                                                                                      | 8 |

|    | 7.3  | Perfor | mance Estimators for Heterogeneous Edge Devices                                                                                            | 9 |

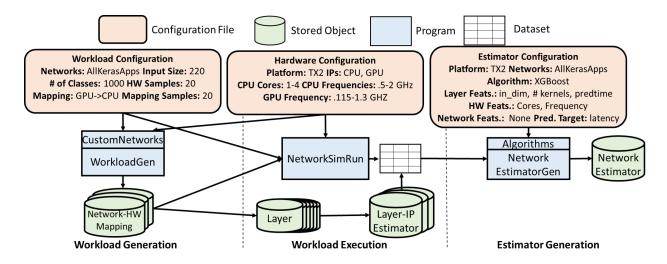

|    | 7.4  | Estima | ation Framework                                                                                                                            | 0 |

|    |      | 7.4.1  | Workload Generation                                                                                                                        | 1 |

|    |      | 7.4.2  | Workload Execution                                                                                                                         | 2 |

|    |      | 7.4.3  | Estimator Generation                                                                                                                       | 2 |

|    | 7.5  | Experi | imental Setup                                                                                                                              | 2 |

|    | 7.6  | Evalua | $12^{4}$                                                                                                                                   | 4 |

|    |      | 7.6.1  | Latency Estimators                                                                                                                         | 4 |

|    |      | 7.6.2  | Power Estimators                                                                                                                           | 6 |

|    | 7.7  | Conclu | $1 sion \ldots 12'$ | 7 |

| 8  | CON  | CLUSI  | ON                                                                                                                                         | 8 |

|    | 8.1  | Thesis | Summary                                                                                                                                    | 9 |

| RI | EFER | ENCES  | 8                                                                                                                                          | 1 |

## LIST OF TABLES

| 3.1 | Summary of kernels in Neural Turing Machines                                                                                                                  | 36  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1 | Area breakdown of different compute platforms                                                                                                                 | 54  |

| 4.2 | Summary of ISA.                                                                                                                                               | 63  |

| 4.3 | Summary of benchmarks.                                                                                                                                        | 66  |

| 4.4 | Summary of platforms.                                                                                                                                         | 66  |

| 5.1 | Summary of Softermax Bitwidths, Q(Int., Frac.)                                                                                                                | 82  |

| 5.2 | Experimental Setup                                                                                                                                            | 83  |

| 5.3 | Accuracy results for Softermax vs an eight-bit quantized baseline                                                                                             | 83  |

| 5.4 | Softermax comparison to DesignWare-based softmax baseline for SQUAD dataset                                                                                   | 84  |

| 6.1 | Costs for SRC/DST stationary dataflows                                                                                                                        | 96  |

| 6.2 | Summary of Graph Datasets                                                                                                                                     | 103 |

| 6.3 | Summary of Graph Neural Networks 1                                                                                                                            | 103 |

| 6.4 | Summary of Compute Platforms 1                                                                                                                                | 104 |

| 6.5 | Speedups of HyGCN and GNNERATOR relative to a V100                                                                                                            | 105 |

| 7.1 | The networks are obtained from the Keras model zoo. The GPU training set contains all of the networks; the CPU training set contains only the bolded networks | 123 |

| 7.2 | Summary of the range of available values for the hardware knobs present in the TX2 platform                                                                   | 123 |

| 7.3 | MAPE for latency prediction in a heterogeneous execution case study 1                                                                                         | 124 |

| 7.4 | MAPE and Spearman coefficient for latency prediction in the network variant context                                                                           | 125 |

| 7.5 | MAPE and Spearman coefficient for latency prediction in the novel network context.                                                                            | 26  |

# LIST OF FIGURES

| 1.1  | FLOPS for SOTA CNNs                                                     | 17 |

|------|-------------------------------------------------------------------------|----|

| 1.2  | Number of parameters for SOTA CNNs                                      | 18 |

| 3.1  | A high-level representation of the Neural Turing Machine                | 33 |

| 3.2  | Runtime breakdown of different NTM kernels                              | 37 |

| 3.3  | Relative mix of operations in runtime-intensive NTM kernels             | 38 |

| 3.4  | Overview of a Transformer Layer                                         | 40 |

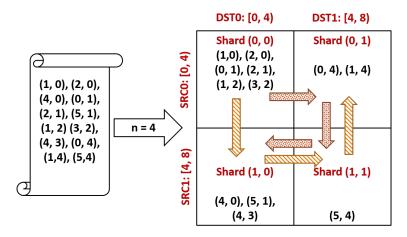

| 3.5  | Visualization of two-dimensional graph sharding algorithm               | 43 |

| 3.6  | Forward pass of one layer in a GraphSagePool network                    | 44 |

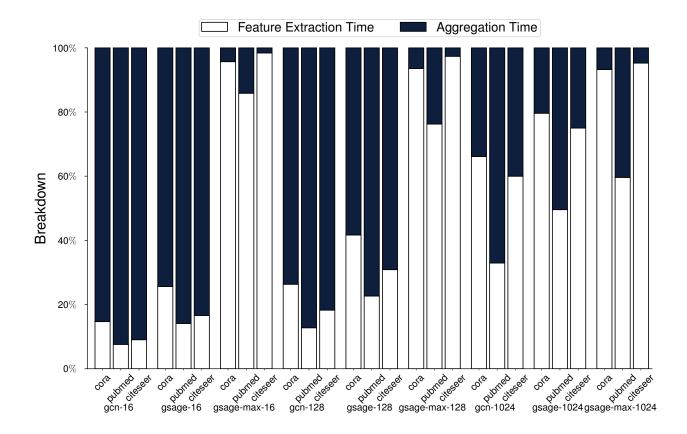

| 3.7  | Breakdown between feature extraction and aggregation                    | 47 |

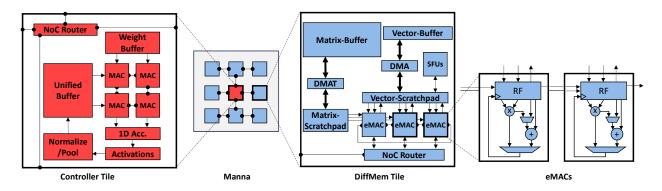

| 4.1  | Overview of Manna                                                       | 53 |

| 4.2  | DiffMem distribution across tiles                                       | 56 |

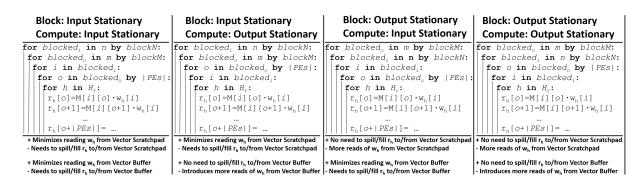

| 4.3  | Overview of possible loop orderings for soft read                       | 57 |

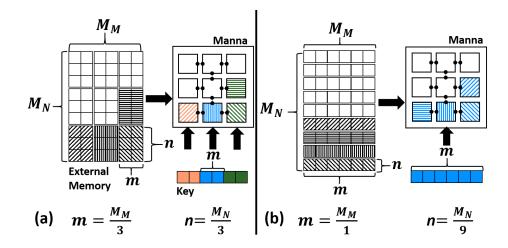

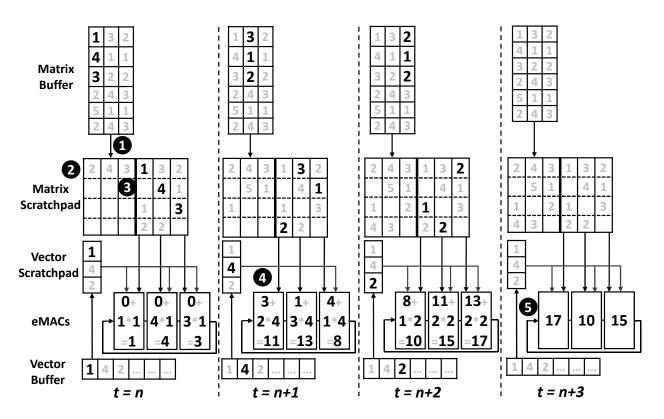

| 4.4  | Improving memory accesses in Manna                                      | 60 |

| 4.5  | Efficient, conflict-free transpose                                      | 61 |

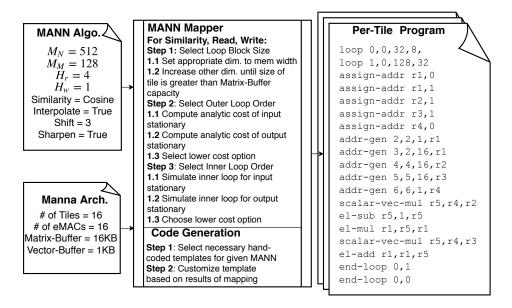

| 4.6  | Overview of Phases of Manna Compiler                                    | 65 |

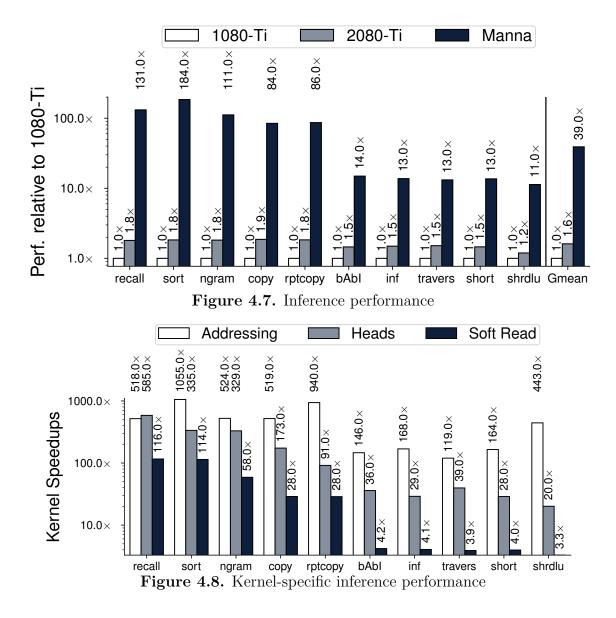

| 4.7  | Inference performance                                                   | 68 |

| 4.8  | Kernel-specific inference performance                                   | 68 |

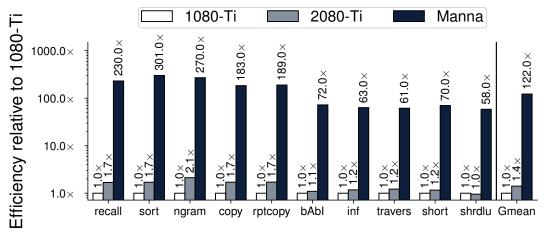

| 4.9  | Energy efficiency compared to GPU baselines                             | 69 |

| 4.10 | PE Utilization for the three platforms                                  | 69 |

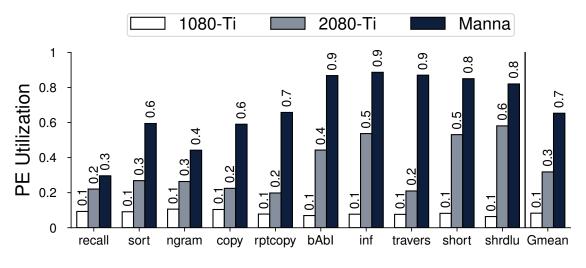

| 4.11 | MANNA performance trends with strong scaling                            | 70 |

| 4.12 | MANNA performance trends with weak scaling                              | 71 |

| 4.13 | Impact of Manna's architectural features.                               | 73 |

| 5.1  | Softmax contributes more to runtime as sequence length increase         | 75 |

| 5.2  | Overview of Proposed Hardfriendly-algorithm                             | 77 |

| 5.3  | Diagram for All Units                                                   | 78 |

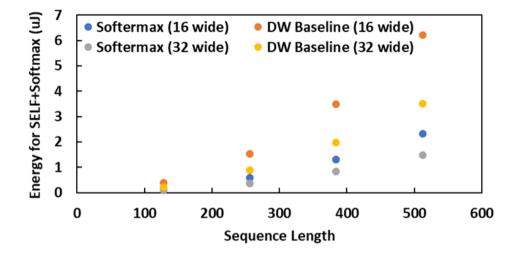

| 5.4  | Softmax-based PEs are much more energy-efficient                        | 84 |

| 6.1  | GNNERATOR architecture overview                                         | 90 |

| 6.2  | Example of GraphSage mathematically, in DGL, and in <b>GNNERATOR</b> IR | 94 |

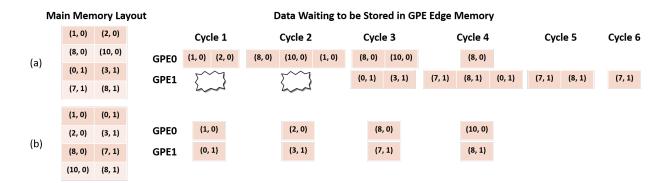

| 6.3  | Optimizing edge layouts in <b>GNNERATOR</b>                      | 101 |

|------|------------------------------------------------------------------|-----|

| 6.4  | An overview of the simulation framework used                     | 102 |

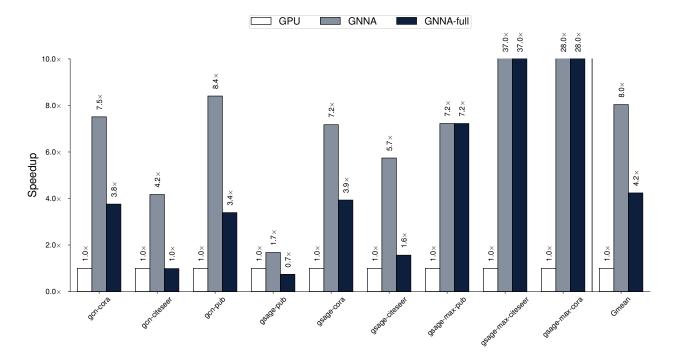

| 6.5  | GNNerator speedup                                                | 105 |

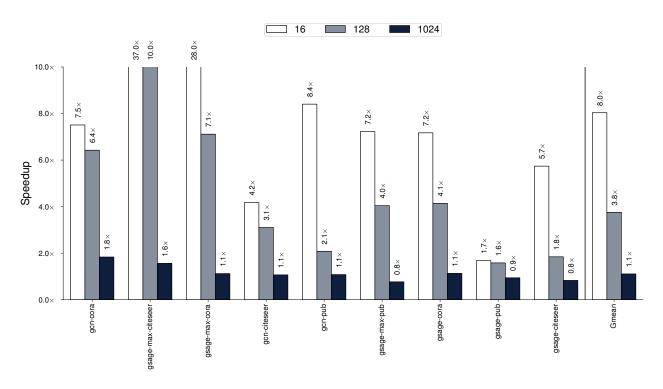

| 6.6  | Hidden dimension sweep results                                   | 106 |

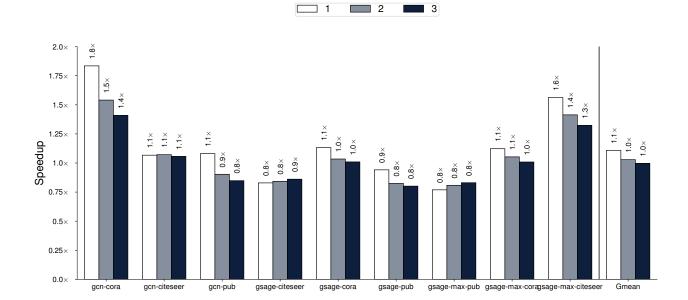

| 6.7  | Hidden layer number sweep results                                | 107 |

| 6.8  | Scaling up GNNerator                                             | 109 |

| 6.9  | DNN dataflow analysis                                            | 110 |

| 6.10 | Push-based dataflow end-to-end results                           | 111 |

| 6.11 | Push-based dataflow compute stall increase                       | 112 |

| 7.1  | Representation of the DNN-HW Mapping Search Space                | 115 |

| 7.2  | One-level vs Two-level                                           | 117 |

| 7.3  | Representation of a Layer-IP Estimator                           | 118 |

| 7.4  | Layer vs Network Feature Based Representations                   | 119 |

| 7.5  | A taxonomy for the design space of DNN-HW performance estimators | 119 |

| 7.6  | Overview of the Softermax framework                              | 121 |

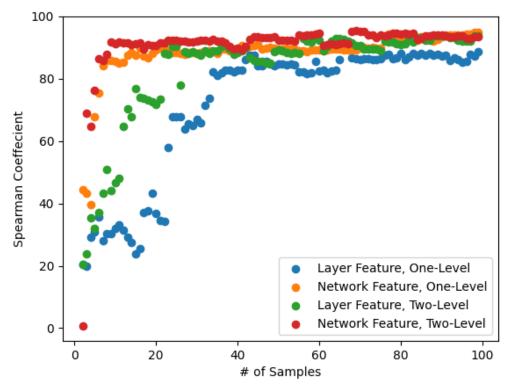

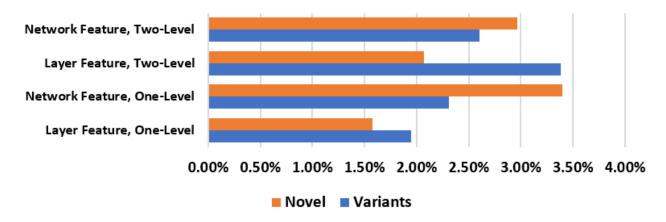

| 7.7  | Spearman Sweep                                                   | 126 |

| 7.8  | Power model MAPE                                                 | 127 |

## ABSTRACT

Due to a combination of algorithmic advances, wide-spread availability of rich data sets, and tremendous growth in compute availability, Deep Neural Networks (DNNs) have seen considerable success in a wide variety of fields, achieving state-of-the art accuracy in a number of perceptual domains, such as text, video and audio processing. Recently, there have been many efforts to extend this success in the perceptual, Euclidean-based domain to nonperceptual tasks, such as task planning or reasoning, as well as to non-Euclidean domains, such as graphs. While several DNN accelerators have been proposed in the past decade, they largely focus on traditional DNN workloads, such as Multi-layer Perceptions (MLPs), Convolutional Neural Networks (CNNs), and Recurrent Neural Networks (RNNs). These accelerators are ill-suited to the unique computational needs of the emerging neural networks. In this dissertation, we aim to fix this gap by proposing novel hardware architectures that are specifically tailored to emerging neural workloads.

First, we consider memory-augmented neural networks (MANNs), a new class of neural networks that exhibits capabilities such as one-shot learning and task planning that are well beyond those of traditional DNNs. MANNs augment a traditional DNN with an external differentiable memory that is used to store dynamic state. This dissertation proposes a novel accelerator that targets the main bottleneck of MANNs: the soft reads and writes to this external memory, each of which requires access to all the memory locations.

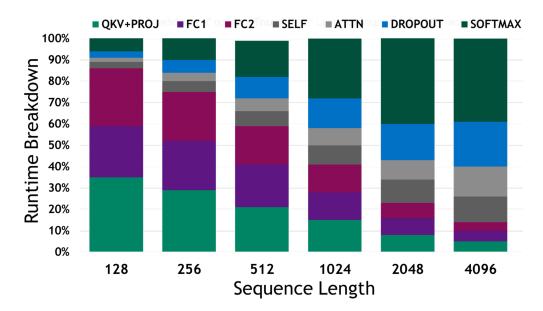

We then focus on Transformer networks, which have become very popular for Natural Language Processing (NLP). A key to the success of these networks is a technique called self-attention, which employs a softmax operation. Softmax is poorly supported in modern, matrix multiply-focused accelerators since it accounts for a very small fraction of traditional DNN workloads. We propose a hardware/software co-design approach to realize softmax efficiently by utilize a suite of approximate computing techniques.

Next, we address graph neural networks (GNNs). GNNs are achieving state-of-the-art results in a variety of fields such as physics modeling, chemical synthesis, and electronic design automation. These GNNs are a hybrid between graph processing workloads and DNN workloads; they utilize DNN-based feature extractors to form hidden representations for each node in a graph and then combine these representations through some form of a graph traversal. As a result, existing hardware specialized for either graph processing workloads or DNN workloads is insufficient. Instead, we design a novel architecture that balances the needs of these two heterogeneous compute patterns. We also propose a novel feature dimensionblocking dataflow to further increase performance by mitigating the memory bottleneck.

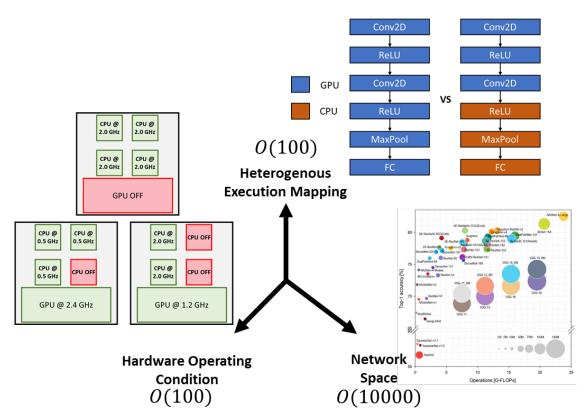

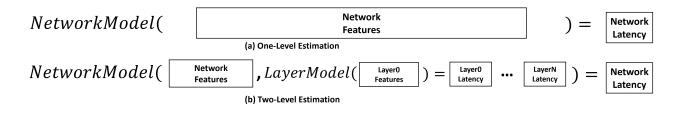

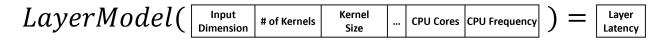

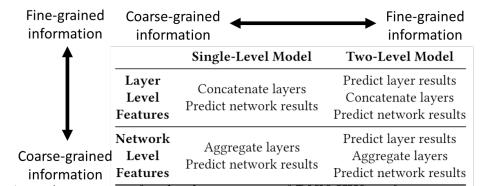

Finally, we address the growing difficulty in tightly coupling new DNNs and a hardware platform. Given the extremely large DNN-HW design space consisting of DNN selection, hardware operating condition, and DNN-to-HW mapping, it is infeasible to exhaustively search this space by running each sample on a physical hardware device. This has led to the need for highly accurate, machine learning-based performance models which can *predict* the latency/power/energy even faster than direct execution. We first present a taxonomy to characterize the possible approaches to these performance estimators. Based on the insights from this taxonomy, we present a new performance estimator that combines coarsegrained and fine-grained to achieve superior accuracy with a limited number of training samples. Finally, we propose a flexible framework for creating these DNN-HW performance estimators.

In summary, this dissertation identifies the growing gap between current hardware and new emerging neural networks. We first propose three novel hardware architectures that address this gap for MANNs, Transformers, and GNNs. We then propose a novel hardwareaware DNN estimator and framework to ease addressing this gap for new networks in the future.

## 1. INTRODUCTION

Deep Neural Networks (DNN) have become increasingly ubiquitous as they continue to improve upon the state-of-the-art results in a wide variety of domains. These DNNs power many popular services, including Apple's Siri, Google Translate, and Amazon's Alexa. The success of DNNs in recent years stems in large part from a virtuous cycle, wherein increases in compute power drive larger and larger models which in turn drive a demand for even more compute power. For example, the famous AlexNet [1] architecture that won the 2012 ImageNet competition handily and kicked off the deep learning revolution was comprised of roughly 60M weights. The recently released Megatron-Turing NLG [2], by contrast, has 530B parameters, a nearly 9,000x increase in model size in just nine years. NVIDIA's K20x, also released in 2012, had a peak single precision performance of 2.90 TFLOPs. Eight years later, NVIDIA's A100 has a peak performance for neural networks of 624 TFLOPs for training and 2496 TFLOPs for inference– an increase of 200x-800x. It is important to note that this increase in performance for executing neural networks resulted from careful hardware/software co-design; the A100 contains features tailored for deep neural networks such as specialized cores, low precision compute units, and sparsity-aware hardware. However, despite this impressive increase in compute, there is still a large gap in the growth of DNN models versus the growth in compute. This is further exacerbated by the emergence of new classes of DNNs– such as memory-augmented neural networks (MANNs), Transformers, and graph neural networks (GNNs) – for which existing commodity hardware is not specialized and thus cannot be executed at peak performance. Attempting to close this gap between the demands of software and the capabilities of hardware, particularly in the face of novel neural network workloads, is the main focus of this thesis.

In the following sections, we discuss the computational challenges of traditional DNNs, the unique challenges posed by emerging DNNs, our proposals to address those unique challenges through the development of novel specialized hardware architectures, and our effort to facilitate hardware/software co-design for future networks and platforms. Finally, we outline the remaining chapters of this dissertation.

#### 1.1 Feed Forward Neural Networks

Feed-forward networks (FFNN), in which layers of neurons are stacked together with strictly forward connections (*i.e.*, no backward or recurrent connections), are an extremely popular class of networks. The two most popular types of FFNNs are multilayer perceptions (MLPs), which consist of only fully-connected layers, and convolutional neural networks (CNNs), which consist of a mix of fully-connected layers and convolutional layers. Convolutional layers exhibit local weight sharing, wherein neurons located near each other in space have their weights tied together in order to reduce the number of parameters needed. While the focus of this thesis is on emerging classes of neural networks specifically, rather than FFNNs, we believe that it is important to highlight the recent trends in FFNN performance and computational demands, as these networks are often used as the backbone of the more complex emerging classes of networks. Thus, these emerging workloads are likely to face a similar trajectory and will suffer from some of the same bottlenecks in addition to the unique bottlenecks posed.

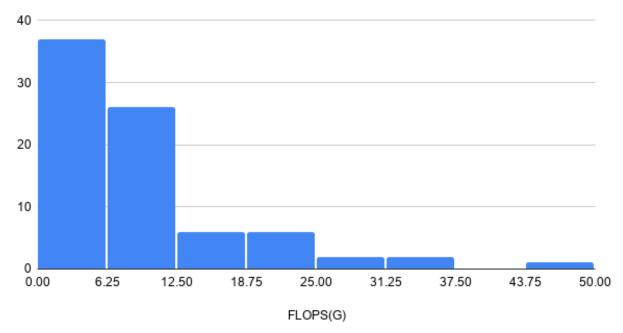

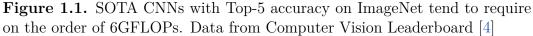

To illustrate the high level of compute and memory needed for modern state-of-the-art FFNNs, we investigate a large set of networks that have achieved Top-5 accuracy over 90% on the challenging ImageNet [3] dataset. While there is a large amount of variability in the metrics of these SOTA networks, a few trends emerge. In Figure 1.1, we see that these networks tend to require roughly 6 GFLOPs per 224x224-sized image input, with networks requiring more FLOPs being less common. In Figure 1.2, we see that SOTA networks tend to have roughly 25M parameters.

Note that although this is already a considerable amount of compute and memory, image recognition CNNs are one of the smallest classes of FFNs thanks to the limited use of fullyconnected layers. Other classes of networks, such as those used in recommendation systems like Facebook's Deep Learning Recommendation Model (DLRM) [5], can have an order of magnitude more FLOPs and parameters– for example, DLRM requires 540 M parameters.

To address the large compute and memory requirements for modern FFNNs, a wide array of accelerators with large amounts of compute as well as memory hierarchies specialized to the specific, fixed data access patterns of FFNNs have been proposed [6]–[11]. Further efficiency

## Distribution of FLOPS (in billions) in SOTA CNNs

gains in hardware can be realized through exploiting sparsity [12]–[18] and low-precision [16], [19]–[22].

#### 1.2 Memory Augmented Neural Networks

Memory-augmented neural networks (MANNs)– which augment a traditional Deep Neural Network (DNN) such as the feed-forward network described above with an external, differentiable memory– are emerging as a promising direction in machine learning. MANNs have been shown to achieve one-shot learning and complex cognitive capabilities that are well beyond those of classical DNNs. However, these increased capabilities come at an increased computational and memory cost; in order to keep accesses to the external memory differentiable– and therefore, allow accesses to be learnable– every single memory location must be read (written) to each time. Further, unlike many DNN workloads, there is extremely little reuse in these so-called *soft reads* and *soft writes* of the external memory. These accesses thus present a unique challenge that results in poor performance of MANNs on modern CPUs, GPUs, and other accelerators. In this thesis, we first provide a detailed

## Distribution of # of Parameters (in millions) in SOTA CNNs

investigation of the computation and memory characteristics of the soft read and soft write kernels, as well as other MANN-specific kernels. We use this analysis to guide our development of MANNA, a specialized hardware inference accelerator for MANNs. MANNA is a memorycentric design that focuses on maximizing performance in an extremely low FLOPS/Byte context. The key architectural features from which MANNA derives efficiency are: (i) investing most of the die area and power in highly banked on-chip memories that provide ample bandwidth rather than large matrix-multiply units that would be underutilized due to the low reuse, (ii) a hardware-assisted transpose mechanism for accommodating the diverse memory access patterns observed in MANNs, (iii) a specialized processing tile that is equipped to handle the nearly-equal mix of MAC and non-MAC computations present in MANNs, and (iv) methods to map MANNs to MANNA that minimize data movement while fully exploiting the little reuse present.

#### **1.3** Transformer Networks

An important subclass of MANNs are Transformer networks, which are currently transforming the field of natural language processing (NLP) through their impressive accuracy on a variety of tasks. The key aspect of Transformers is their use of "self-attention" layers, which consist mainly of matrix multiplies and softmax operations. These self-attention layers are repeated to form a full a network. Due to this heavy use of attention, the softmax operation accounts for a significant fraction of the total run-time of Transformers. This is in contrast to standard DNNs where the softmax operation is used only as the last classification layer and accounts for very little run-time. As a result, DNN accelerators typically do not optimize this operation, leading to a new bottleneck in these Transformer-based networks. To address this, we propose **Softermax**, a hardware-friendly softmax design that exploits approximate computing to enable the softmax logic to be more tightly coupled with the MAC operation, allowing for higher softmax throughput and alleviating the bottleneck. Softermax consists of four parts: (i) reducing the overhead of exponentiation by replacing the expensive natural number base with the lower cost base two, (ii) implementing low-precision softmax computations by leveraging the natural resiliency of these networks in contrast to the highperformance scientific computing applications that these special functions typical target, (iii) an online, integer-based normalization calculation which reduces the number of passes through the matrix needed to compute the softmax and (iv) Softermax-aware fine-tuning, which virtually eliminates the accuracy degradation that may have been introduced through these approximations.

#### 1.4 Graph Neural Networks

Graph Neural Networks (GNNs) brings the success of deep learning from the Euclidean domain (*e.g.*, images, video, audio, *etc.*) to the non-Euclidean domain (*e.g.*, graphs); GNNs have achieved state-of-the-art results in a wide variety of application domains, such as social network recommendation systems and chemical synthesis. There are two major kernels used across all GNNs. One is a *feature extraction* step, which passes the features of a graph's nodes (and/or edges) through a fully-connected layer in order to obtain a new representation.

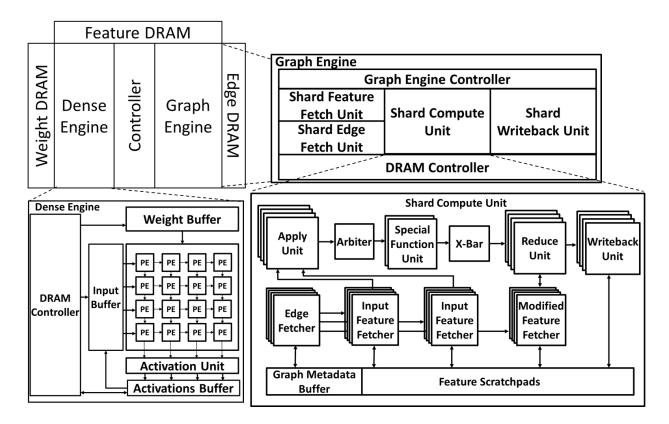

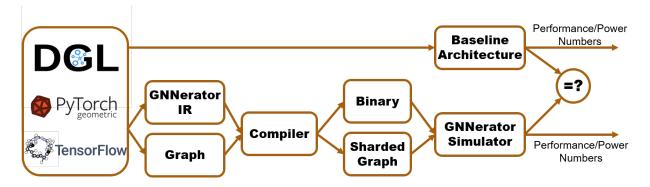

The second is an *aggregation* step, which combines the features within a given node's graph neighborhood, thereby incorporating information based on graph structure. These two steps are stacked to form multiple layers of a network. The final node (edge) features created via these layers can then be used for various tasks, such as node-, edge-, or graph-level classification. This heterogeneity in compute kernels introduces new, unique challenges that current computing platforms– CPUs, GPUs, and special purpose deep learning accelerators - do not address. Architectures such as GPUs and DNN accelerators that are typically targeted at dense, regular computations can perform the feature extraction step efficiently, but are ill-suited to the irregular memory access patterns present in the aggregation step. In contrast, architectures specialized for graph analytics workloads can perform the aggregation step efficiently, but are ill-suited for the large amount of regular computation needed to perform the feature extraction step. To address this shortcoming, we propose GNNERATOR, a graph neural network accelerator that utilizes two heterogeneous compute engines, one optimized for feature extraction and one optimized for feature aggregation. We also propose feature-blocking, a novel dataflow for GNNs that increases the number of nodes that can be held on-chip during GNN processing, helping to address the memory bottleneck inherent in GNNs. We provide hardware support for this dataflow in GNNERATOR. We develop a simulation framework to evaluate the performance benefits of the proposed architecture, to explore previously unexplored areas in the architecture design space for GNNs, and to analyze the potential bottlenecks for GNN accelerators as GNNs continue to increase in size.

#### 1.5 Learned DNN Performance Estimators

Given the explosion in the number of DNN models proposed, combined with the increasing number of hardware devices on which to run them, it is becoming more and more difficult to optimally map a given DNN to a given hardware platform. This is particularly true for modern edge platforms, which typically integrate multiple heterogeneous hardware IPs and allow for the configuration of the operating condition of those IPs (*i.e.*, number of cores active, operating frequency, *etc*). It is infeasible to run every model directly on physical hardware, due the latency of the networks, the overhead of loading the networks on the device, and the physical number of devices acting as a bottleneck. As a result, there has been recent interest in developing sample efficient predictive *performance estimators*, which can then be used in downstream applications such as hardware-aware neural architecture search.

To this end, we first analyze the design space of DNN performance estimators, synthesizing this information into a design taxonomy. Using the insights from this taxonomy, we propose a novel hardware-aware DNN performance estimator specifically designed for the unique challenges of heterogeneous edge devices, which presents a reasonable trade-off between fine-grained and coarse-grained information. We develop a flexible framework for the rapid development of these performance estimators, and demonstrate the accuracy of the estimators produced on a variety of use cases.

#### 1.6 Thesis outline

The rest of the thesis is organized as follows. Chapter 2 details the related research efforts in accelerating different types of DNNs. Chapter 3 provides the necessary background on DNNs, emerging classes of DNNs, and DNN-HW performance models. Chapter 4 proposes Manna, a memory-augmented neural network accelerator. Chapter 5 proposes Softermax, a set of hardware/software techniques for accelerating Transformers. Chapter 6 proposes GNNERATOR, a graph neural network accelerator. Chapter 7 describes our performance estimator design taxonomy, our novel hardware-aware performance model designed for heterogeneous edge devices, and our framework for generating these estimators. Finally, Chapter 8 concludes the thesis by summarizing its main contributions.

## 2. RELATED WORK

Deep neural networks have become a topic of increasing interest for computer system designers, as they have continued to achieve state-of-the-art results in a wide variety of tasks such as image recognition and speech translation through the use of more and more complex networks with greater and greater computational and memory requirements. In order to address these increasing demands of both traditional as well as emerging neural network architectures, there has been a wide array of research efforts. In this chapter, we categorize and discuss a variety of these efforts. Specifically, we first discuss research efforts addressing traditional neural networks that we believe are of particular interest for also addressing emerging neural networks. We next discuss research efforts specifically addressing memoryaugmented neural networks (including Transformer-based networks) as well as graph neural networks, and identify the key differences with our work. Finally, we discuss the relation of previous efforts in DNN performance estimators to our proposal.

#### 2.1 Deep Neural Networks

As discussed in Chapter 1, existing hardware and software optimizations for traditional Deep Neural Networks are insufficient for emerging neural workloads such as memoryaugmented neural networks and graph neural networks. However, these emerging neural networks still use traditional DNNs as the backbone for some of their computations (*i.e.*, the controller in MANNs and the feature extractors in GNNs). Thus, it is instructive to explore the state of the field in optimizing DNNs.

#### 2.1.1 Algorithmic optimizations

Due to the immense popularity of DNNs in recent years, there is an extremely large body of work on algorithmic optimizations for DNNs. For the sake of brevity, we focus mainly on the families of optimizations that we believe are the most likely to be relevant for MANNs and GNNs: quantization and sparsity optimizations. **Quantization.** Originally, computations for DNNs were done using 32-bit floating point representations. However, DNNs are intrinsically quite resilient and can be performed using far fewer bits. [23] proposed using a quantized forward pass with low-precision weights and activations, with a full-precision backwards pass using a straight-through estimator (STE) along with stochastic rounding. A variety of other techniques have been proposed since, including learning various quantization parameters [24], quantization-aware training [25], per-layer mixed-precision quantization [26], and blocked precision scaling [22].

**Sparsity.** Modern DNN workloads exhibit considerable *sparsity* in various data structures of the network, such as activations and weights. DNN sparsity can either be static or dynamic. Static sparsity results from pruning low-valued (and therefore, insignificant) weights from a network, in a process referred to as network pruning. Network pruning has shown to be very effective in modern CNNs [27] as well as other architecture types such as RNNs [28]. To exploit static sparsity, weights are stored in a sparse format, allowing more of them to fit on-chip and avoiding expensive DRAM accesses. Exploiting dynamic sparsity, which typically results from use of the ReLU activation function, is more difficult in software.

#### 2.1.2 Specialized accelerators

Specialized accelerators for deep neural networks is an extremely robust field of research, for both inference [8], [10], [29], [30] as well as training [6], [9]. DNN accelerators typically fall into two categories: systolic-array based [8] and SIMD-based [6], [9], [10], [29], [30]. Both categories of accelerators typically provide the compute units with access to small register files to store inputs, weights, or partial sums, as well as relatively larger on-chip buffers for an additional level of memory foor the same.

In order to fully exploit the benefits derived from the algorithmic optimizations described above (*i.e.*, enable performance benefits in addition to the compression benefits), many DNN accelerators, including commercial products [16], have also begun to integrate hardware support for quantized and sparse computations.

**Quantization.** On top of reducing memory storage requirements, quantization also provides performance benefits by enabling low-precision arithmetic, increasing the amount of compute in a given area budget as well as increasing the effective bandwidth. While many accelerators simply directly implement low-precision (typically eight-bit) arithmetic [8], other accelerators propose further specializations, such as precision-scaling computation [19], [22], [31] or compensation support [21] in order to enable efficient computation at even lower precisions.

**Sparsity**. Like quantization, sparsity also offers benefits beyond reducing memory storage requirements; by skipping the ineffectual computations introduced by sparsity, sparsity-aware accelerators can realize large performance gains. There has been much interest in recent years in techniques to efficiently exploit sparsity while minimizing the area and power overheads [12]–[15], [17], [32]. One key challenge is load balancing [13], as unstructured sparsity can result in uneven distribution of work across processing elements. Another key challenge is efficiently computing intersections of sparse representations [33], often used to determine which computations are actually effective.

#### 2.2 Memory-Augmented Neural Networks

Memory-augmented neural networks utilize a form of self-attention, realized through a so-called external differentiable memory, in order to provided capabilities well beyond traditional DNNs. The accesses to this differentiable memory, as well as the addressing schemes used to determine the accesses, constitute a large fraction of the run-time of MANNs. As a result, both the algorithmic optimizations and specialized accelerators for MANNs target these kernels.

#### 2.2.1 Algorithmic optimizations

Algorithmic optimizations have been proposed to address the large overhead associated with the differentiable memory. [34] uses a K-nearest neighbor scheme to update only the k most relevant memories, instead of all locations. A concurrent work explores a similiar idea, but introduces additional levels of hierarchy [35]. Finally, Q-MANN [36] addresses the differentiable memory bottleneck through the use of quantization. By replacing the cosine similarity with a Hamming distance, Q-MANN is able to perform the soft memory operations using eight-bit fixed-point calculations without a catastrophic loss in accuracy.

#### 2.2.2 Specialized accelerators

Given the memory-intensive nature of MANNs, many of the hardware-specific research efforts have focused on processing-in-memory (PiM), often using emerging devices. [37] replaces the cosine-based similarity computation often used in MANNs with a fixed-point, hardware-friendly approximation, allowing the computation to be executed using efficient ternary content addressable memory (TCAM) look-ups. Similarly, X-MANN [38] also replaces the similarity computation with a lower-cost alternative, allowing the differentiable memory operations to be realized using resistive crossbars.

There have also been efforts outside of PiM-based architectures. [39], a FPGA-based architecture, introduces Bayesian-based inference thresholding, allowing the architecture to stop soft reads early if a certain confidence level is met. MnnFast [40] proposes two key hardware-software co-design strategies for MANNs. Column-based "lazy softmax" allows for greater parallelization of a fused key similarity and soft read kernel, while an embedding cache provides dedicated memory for the memory intensive embedding operation of a MemNN (a variant of MANN) to reduce cache-thrashing of the other data structures.

#### 2.3 Transformer Networks

An important subclass of MANNs that warrant specific attention are Transformer networks

#### 2.3.1 Algorithmic optimizations

Most recent algorithmic works have tried to make Transformers more efficient by targeting their large number of parameters, rather than targeting the softmax operation. This is commonly performed through the creation of smaller networks through techniques such as knowledge distillation [41], inductive biases [42], or approximations [43]. These optimizations are orthogonal to our effort, as **Softermax** can still be used in these smaller, more efficient networks. There have also been a few efforts towards more efficient Transformers through the use of lower-precision computation [41], [44], with the most recent efforts also targeting quantization of the softmax operation [45], [46]. However, as these works are software-only, there are no actual gains in performance from their softmax quantization techniques. This is because full-precision special function units are still used for the exponential and division calculations– in fact, there may actually be a slight performance penalty due to overheads in casting between data types. Our work, in contrast, is able to exploit low-precision in both software and hardware, unlocking actual performance gains.

#### 2.3.2 Specialized accelerators

There have been efforts to provide specialized accelerators for Transformer networks as a whole. A3 [47] provides hardware support for a lower cost attention mechanism , while SpAtten [48] allows for hardware-aware pruning of Transformers. EdgeBERT [49] provides hardware support for voltage-scaled early exit from Transformer networks. There have also been a few recent efforts that offer specialized hardware that target the softmax operation specifically [47], [50]–[52]. These efforts propose various low-precision exponential and division units, such as a variable precision softmax unit generator [52], a group lookup tablebased exponential unit [51], a split high-bits/low-bits exponential unit [47], and approximate units [50]. This allows for exploiting low-precision within the special functions, unlike in the software only approaches.

#### 2.4 Graph Neural Networks

There are two main kernels of GNNs with vastly different needs: the feature extraction stage and the aggregation stage. Since software packages for accelerating feature extraction on GPUs are already quite robust, most algorithmic-focused work has been on optimizing for the memory requirements of the aggregation stage. Specialized accelerators have also been proposed to meet the heterogenous requirements of GNNs.

#### 2.4.1 Algorithmic optimizations

As GNNs are still a relatively new area, most of the focus on software optimizations has been on simply providing optimized implementations for existing hardware. For example, the popular DGL framework [53] utilizes fused message passing in order to reduce the memory overhead associated with the aggregation step of GNNs by replacing the defined computations with equivalent Sparse-Dense Matrix operations. Note that this sparsity is due to the underlying graph structure of the input and is orthogonal to the potential sparsity in the feature extraction layers (*i.e.*, fully connected layers). Roc [54] provides a distributed GPU framework, allowing users to scale to extremely large real-world graphs that would be infeasible on a single GPU due to memory constraints. GNNAdvisor [55] proposes a runtime that sets GPU-related parameters based on characteristics of the input graph (*e.g.*, node degree) in order to maximize performance. [56] provides detailed insights into the specific bottlenecks when running GNNs on Intel hardware and proposed optimizations for the identified bottleneck, the aggregation stage. More recently, algorithmic optimizations have expanded to include techniques like quantization [57] and eliminating redundant computations [58].

#### 2.4.2 Specialized accelerators

There have been a few recent works directly targeting graph neural networks. Similar to GNNERATOR, HyGCN [59] proposes two heterogeneous compute engines, one optimized for the feature extraction stage and one for the aggregation stage. Unlike in our work, HyGCN only exploits intranode parallelism, processing a single node's entire feature across all cores before moving on to the next node, while we exploit both intranode and internode parallelism—that is, the parallelism within a node due to feature dimensions and the parallelism between nodes. GNNA [60] uses smaller compute engines as a base element, and connects multiple of these tiles in a NoC. Unlike HyGCN, the engines do not share on-chip storage, but rather communicate over an on-chip cross-bar switch. Finally, EnGN [61] proposes a unified GNN accelerator architecture, in which the feature extraction and aggregation computations are performed using the same register file and compute units. Much of EnGN's performance comes from two sources: dimension-aware stage re-ordering and a degree-aware vertex cache.

The dimension-aware stage re-ordering is a simple software optimization and is indeed actually standard in GNN frameworks such as DGL, while the degree-aware vertex cache is orthogonal to our architecture and can be integrated into GNNERATOR.

#### 2.5 DNN Performance Estimation

One popular method of designing estimators [62]–[65] relies on the composability of DNNs– the fact that DNNs are composed from a relatively small number of types of layers (Convolutional, Fully-Connected, ReLU, *etc.*). These works create estimators for each layer, which are then aggregated together to predict for the entire network. The other main approach [66], [67] predicts the performance of a network directly, instead of on a layer-by-layer basis.

The efforts described above are largely agnostic to the underlying hardware. [68] addresses this by building hardware-aware estimators that generalize across different hardware platforms by using a suite of networks as a "hardware fingerprinting" set. Each hardware platform is still treated as a fixed platform, however, ignoring the ability to vary the hardware operating condition. Further, these works all ignore the heterogeneity of new edge platforms, wherein the DNN may be partitioned across multiple hardware IPs. Finally, these estimators are created in an ad-hoc manner, with little justification for the chosen estimation strategy, input features, *etc*.

#### 2.6 Thesis contributions

The primary contributions described throughout this thesis are different or complementary to the prior work described above in the following ways.

Specialized accelerators for MANNs. [37] and [38] rely on emerging device technologies that are not widely available. Further, these works are also not an end-to-end solution since they do not accelerate the addressing kernels or the DNN controller. MANNA, by contrast, is a CMOS-based architecture and implements all MANN kernels. The other proposed architectures, MnnFast [40] and [39], are fixed-function architectures that are specialized for a specific class of MANNs, end-to-end memory networks (MemNets), whereas MANNA has sufficient programmability to realize a broad class of MANNS (*e.g.*, NTMs and DNCs from Google DeepMind), which is important given the evolving nature of MANNS. Moreover, since MemNets do not require soft writes, these accelerators are not designed to support non-MAC operations that constitute a key kernel in soft writes. Consequently, these architectures suffer from reduced throughput for such element-wise operations, resulting in inefficient soft writes. Besides, since MemNets do not update the differentiable memory, these efforts store a copy of the memory in its transposed form and do not provide any support for on-chip transpose. For the variants of MANNs that do require soft writes, hardware support is crucial; our ablation study indicates that support for element-wise operations and on-chip transpose lead to speedups of 2.8x and 1.4x, respectively.

**Software optimizations for Transformers.** We are the first to propose the use of a different, more hardware-friendly base in the softmax operation of Transformers. Further, we propose a more efficient, *integer-based* online normalization scheme, mitigating the overheads present in other online normalization methods.

**Specialized accelerators for Transformers.** Many of the accelerators previously proposed for Transformers [47]–[49] are orthogonal to Softermax, as these efforts do not target the softmax operation specifically. Within the softmax operation specifically, low-precision hardware has been explored before [50]–[52]. None of these efforts, however, use our other approximate computing techniques, such as base substitution and integer-based online normalization. These techniques work in concert with our low-precision hardware to maximize hardware efficiency. Further, our Softermax-aware finetuning process allows for the use of a smaller LUT than in previous efforts.

Software optimizations for GNNs. While we are mostly focused on specialized accelerators, we note that many of the software optimizations proposed for GNNs are either indeed present in our accelerator or are orthogonal and can be incorporated. As a result of our architecture, which consists of an Apply Unit that feeds directly into the Reduce Units, we can fuse nearly all message passing kernels, not just those which map cleanly into sparse-dense matrix operations as in DGL.

**Specialized accelerators for GNNs.** There have been a few recent accelerators for GNNs proposed: HyGCN [59], EnGN [61], and GNNA [60]. All three of these works require

entire features to be resident on-chip at once, reducing the size of the subgraph that can be processed. Further, none of the three have support for operations that modify features through a vector-vector operation before aggregations— for example, by multiplying a feature by a weight for attention-based networks or by an error gradient for training. **GNNERATOR** supports this through the Apply Engine and its corresponding instructions. This limits the usage of these accelerators in emerging GNN workloads, as well as a base architecture for training hardware.

**Predictive performance estimators for DNNs.** There have been a number of different performance estimators proposed that use a variety of different techniques (layer-wise vs direct network) and different features (layer details, number of MACs, memory footprint, *etc.*). It is difficult to understand the impacts of these different hyperparameters. To address this, we step back and provided a principled look at the DNN performance estimator design space, providing a taxonomy of the various designs. Further, we provide a flexible framework for quickly generating different performance estimators and comparing them with iso-conditions. Furthermore, unlike previous efforts, we consider the full capabilities of heterogeneous hardware platforms, allowing for predictions across the range of operating conditions of a device, as well as across different DNN-to-IP mapping strategies.

### 3. BACKGROUND

In this chapter, we provide a brief background on traditional DNNs, as well as the emerging MANN and GNN workloads.

#### 3.1 Deep Neural Networks

In this work, we refer to traditional Deep Neural Networks (DNNs) as encompassing two major families of architectures: feed-forward neural networks (FFNNs) and recurrent neural networks (RNNs).

**Feed-forward neural networks.** The simplest FFNN is the perceptron [69], which consists of a layer of input and ouputs units called neurons. These neurons are connected in an all-to-all pattern and the importance of these connections are defined by the connection's *weight*. To train the perceptron, the error between the predicted output and the correct, labeled output is computed and used to update the weights in a process referred to as gradient descent. Multilayer perceptrons build upon this by adding multiple *hidden* layers, which are layers of neurons between the input and output layers. A similiar training process is followed for multilayer networks, with the exact updates required for each layer determined in reverse order through a process known as backpropogation. Convolutional layers introduce weight sharing, which builds spatial-based priors into the network. Additional layer types can include pooling layers, which downsample the network, and activation layers.

**Recurrent-neural networks.** Recurrent Neural Networks extend FFNNs by introducing a recurrent connection, thus introducing memory to the network by allowing dynamic state to persist across iterations of the network. However, RNNs can be difficult to train because the error gradients through the RNN tend to either explode or vanish when using backpropagation through time (BPTT). In practice, this means that RNNs tend to either be susceptible to noisy input or have difficulty learning long-term dependencies [70]. To overcome this limitation, [71] proposed Long Short-Term Memory networks (LSTMs). LSTMs build upon a basic recurrent unit by adding a memory cell (C) that stores state. LSTMs also add a forget gate (f), an input gate (i), and an output gate (o) that control the retaining, addition, and outputting of this stored state, respectively. Later, [72] proposed a Gated Recurrent

Unit (GRU) that is similar to LSTMs, but slightly simplified. An additional memory cell is not used; instead, the flow of information of the hidden state is directly modulated through the use of gates. The GRU retains analogs to the input and forget gates, but eliminates the output gate, exposing the entire state instead. RNNs and its variants have resulted in recent success in some domains, such as neural machine translation [73], [74] and speech recognition [75], [76]. However, there exists a fundamental constraint on the use of RNNs for storing dynamic state. The dynamic state is intrinsically coupled to the design of the network. As a result, the amount of information that can be stored in the network cannot be increased without increasing the size of the underlying network, thereby increasing the total number of parameters that must be trained.

#### 3.2 Memory-Augmented Neural Networks

To address the aforementioned scaling problem, memory-augmented neural networks (MANNs) have been proposed, wherein the dynamic state is explicitly decoupled from the neural network in an external memory. Several variations of MANNs have been proposed [77]–[83] to tackle a diverse variety of tasks such as question answering, route planning, scene understanding, and language transduction. These MANNs have also been used as building blocks for goal-directed agents in reinforcement learning settings [84].

#### 3.2.1 Neural Turing Machines Overview

While several variants of MANNs exist in the literature, we will focus on DeepMind's Neural Turing Machine (NTM) [81] for our exposition. In this section, we provide a detailed description of NTMs.

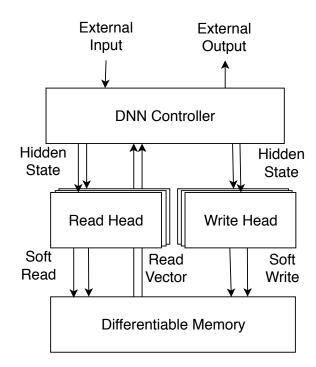

As shown in Figure 3.1, NTMs are composed of three main components: a neural networkbased controller, a differentiable external memory, and the read and write heads that control the interaction between the two. To ensure the external memory is differentiable, NTMs use soft read and write operations. These soft operations differ from traditional read and write operations in that the soft operations require access to all the locations in memory.

Figure 3.1. A high-level representation of the Neural Turing Machine

Attention mechanisms are used to determine how the values of all of the different locations are combined (read) or updated (write).

**Controller.** NTMs employ a standard DNN as a controller that generates both the final output vector as well as the hidden state vector for the read and write heads. A wide range of DNNs, *viz.*, MLPs of varying depths, RNNs, CNNs, *etc.*, can be utilized as the controller. Even with a feedforward network-based controller, NTMs are intrinsically sequential algorithms. At each time step t, the controller network receives as inputs an external input vector and the read vectors  $(\mathbf{r}_h^{t-1})$  from each read head (h) corresponding to the previous time step t - 1. The controller then produces an output vector that is sampled at the end of execution of the NTM, and a hidden state vector that is used by the read/write heads to interact with the external memory state at the same time step. Throughout this thesis, we define  $\mathbf{M}^t$  as the differentiable external memory M at time t.  $\mathbf{M}^t$  is composed of  $M_N$  row vectors, where each row vector  $\mathbf{M}^t(\mathbf{i})$  consists of  $M_M$  words (dimensions). Thus,  $\mathbf{M}^t$  comprises of  $M_N$  rows and  $M_M$  columns.

Soft Read. A soft read is a weighted summation over all the locations in  $\mathbf{M}^t$  at time t, producing one read vector,  $\mathbf{r}_h^t$ , for each read head h. This can be formulated as a vectormatrix multiplication between the transpose of the weight column vector  $\mathbf{w}_h^t$  and  $\mathbf{M}^t$  for each read head h, as shown in Equation 3.1. The column vector  $w_h^t$  reflects the contribution of the corresponding rows to the final soft read vector, and is obtained by the attention mechanism described below.

$$\mathbf{r}_{h}^{t} = \mathbf{w}_{h}^{t\,T} \mathbf{M}^{t}, \forall \ h \in H_{r}$$

$$(3.1)$$

Soft Write. A soft write involves two steps: an *erase* and an *add* operation shown in Equations 3.2 and 3.3. In the erase step, an erase row vector  $\mathbf{e}_h^t$  produced by the write head h is multiplied with the corresponding scalar from the weight column vector  $\mathbf{w}_h^t$ . The resulting vector is next subtracted from 1 (a vector of length  $M_M$  containing all 1s). Finally, the subtracted vector is multiplied in an element-wise fashion with  $\mathbf{M}^t(\mathbf{i})$ , resulting in a modified external memory  $\mathbf{M}^t$ . After erasing, the modified external memory is then updated by adding a similarly weighted add vector  $\mathbf{a}_h^t$ . The erase and add steps are repeated for each row in  $\mathbf{M}$ , as well as for each write head h, in order to complete the soft write operation.

$$\mathbf{M}^{t}(\mathbf{i}) = \mathbf{M}^{t}(\mathbf{i}) \odot [\mathbf{1} - \mathbf{w}_{h}^{t}(\mathbf{i}) \cdot \mathbf{e}_{h}^{t}]$$

(3.2)

$$\mathbf{M}^{t+1}(\mathbf{i}) = \mathbf{M}^{t}(\mathbf{i}) + \mathbf{w}_{h}^{t}(\mathbf{i}) \cdot \mathbf{a}_{h}^{t}, \forall \mathbf{i} \in M_{N}, \forall h \in H_{w}$$

(3.3)

**Read/Write Heads.** Each read and write head h consists of a weight matrix  $W_h$ . In each head, the hidden state from the controller is multiplied by the weight matrix to produce a set of vectors and scalars (*e.g.*, the key vector, erase vector, *etc.*) that are used as inputs to the attention mechanisms present in NTMs.

Attention Mechanism. To determine the weights for soft read and write operations, NTMs use a series of attention mechanisms that consume the output of the read and write heads. First, content-based weighting produces a weight vector  $\mathbf{w}_{ch}^{t}$  of length  $M_{N}$  for each read and write head h. Each element of the content weight column vector for a given head is based on the similarity between the corresponding row of  $\mathbf{M}^t$  and the key row vector  $\mathbf{k}_h^t$  emitted by that head (Equation 3.4).

$$Sim[\mathbf{k}_{h}^{t}, \mathbf{M}^{t}(\mathbf{i})] = \frac{\mathbf{k}_{h}^{t} \cdot \mathbf{M}^{t}(\mathbf{i})}{||\mathbf{k}_{h}^{t}|| \cdot ||\mathbf{M}^{t}(\mathbf{i})||}$$

(3.4)

$$\mathbf{w_{c}}_{h}^{t}(\mathbf{i}) = \frac{\exp(\beta_{h}^{t} Sim[\mathbf{k}_{h}^{t}, \mathbf{M}^{t}(\mathbf{i})])}{\sum_{\mathbf{j}}^{M_{N}} \exp(\beta_{h}^{t} Sim[\mathbf{k}_{h}^{t}, \mathbf{M}^{t}(\mathbf{j})])}$$

(3.5)

After obtaining the similarity for all  $M_N$  memory vectors in  $\mathbf{M}^t$ , the similarities are then amplified (attenuated) by a scalar  $\beta_h^t$  and a softmax function is applied to obtain  $\mathbf{w}_{ch}^t$  (Equation 3.5). Next, a scalar interpolation gate  $g_h^t$  is used to blend the current weighting with the weighting produced at the previous time step of the algorithm (Equation 3.6). The result of the interpolation is then convolved with a rotation vector  $\mathbf{s}_h^t$  (Equation 3.7). Finally, the result of this convolution is sharpened by a scalar  $\lambda_h^t$  and normalized in order to combat the blurring that may occur as a result of the shifting (Equation 3.8). This produces the final weight vector  $\mathbf{w}_h^t$  corresponding to each read and write head key vector, which are then used in the soft read and write operations.

$$\mathbf{w}_{\mathbf{g}_h}^t(\mathbf{i}) = g_h^t \mathbf{w}_{\mathbf{c}_h}^t(\mathbf{i}) + (1 - g_h^t) \mathbf{w}_{\mathbf{c}_h}^{t-1}(\mathbf{i})$$

(3.6)

$$\mathbf{w}_{\mathbf{s}h}^{t}(\mathbf{i}) = \sum_{\mathbf{j}}^{M_{N}-1} \mathbf{w}_{\mathbf{g}h}^{t}(\mathbf{j}) \mathbf{s}_{h}^{t}(\mathbf{i}-\mathbf{j})$$

(3.7)

$$\mathbf{w}_{h}^{t}(\mathbf{i}) = \frac{\mathbf{w}_{\mathbf{s}_{h}^{t}}(\mathbf{i})^{\lambda_{h}^{t}}}{\sum_{\mathbf{j}}^{M_{N}} \mathbf{w}_{\mathbf{s}_{h}^{t}}(\mathbf{j})^{\lambda_{h}^{t}}}$$

(3.8)

#### 3.2.2 Neural Turing Machines Computational Behavior

For the following experiments, we use the copy task from the original NTM paper [81] as an illustrative example and execute it on an NVIDIA Turing GPU and an Intel Skylake Xeon CPU.

|                         |                    | 0                                                                                  |             |             |

|-------------------------|--------------------|------------------------------------------------------------------------------------|-------------|-------------|

| Kernel Name             | Key Primitive      | Mem. Accesses                                                                      | FLOPs/Byte  | Reduction   |

| Key Similarity          | Vector-Matrix Mul. | $\mathcal{O}(\mathbf{M_N} \cdot \mathbf{M_M} \cdot (\mathbf{H_r} + \mathbf{H_w}))$ | $H_w + H_r$ | Row-wise    |

| Content-based Weighting | Normalization      | $\mathcal{O}(M_N \cdot (H_r + H_w))$                                               | 3           | -           |

| Location Interpolation  | Elwise Mul/Add/Sub | $\mathcal{O}(M_N \cdot (H_r + H_w))$                                               | 2           | -           |

| Shift Weighting         | Circular Conv.     | $\mathcal{O}(M_N \cdot (H_r + H_w))$                                               | S           | -           |

| Weight Sharpening       | Normalization      | $\mathcal{O}(M_N \cdot (H_r + H_w))$                                               | 3           | -           |

| Soft Read               | Vector-Matrix Mul. | $\mathcal{O}(\mathbf{M_N}\cdot\mathbf{M_M}\cdot\mathbf{H_r})$                      | $H_r$       | Column-wise |

| Soft Write              | Elwise Mul/Add/Sub | $\mathcal{O}(\mathbf{M_N}\cdot\mathbf{M_M}\cdot\mathbf{H_w})$                      | $H_w$       | -           |

**Table 3.1.** Summary of kernels in Neural Turing Machines

Memory access characteristics. Table 3.1 categorizes the various NTM kernels depending on their computational primitives and identifies the number of memory accesses associated with each kernel. There are three distinct groups of kernels: the controller kernel that consists of a classical DNN, the addressing kernels that determine how the external memory is accessed, and the kernels that actually access the external memory. The addressing kernels– content-based weighting, location interpolation, shift weighting, and weight sharpening– involve  $\mathcal{O}(M_N)$  memory accesses per head, since they are used to create and modify the weight column vectors  $\mathbf{w}_h$ . These kernels also have a relatively low FLOPs/Byte ratio (two or three).

On the other hand, the access kernels– key similarity, soft write, and soft read– are extremely memory-intensive kernels with many more memory accesses ( $\mathcal{O}(M_N \cdot M_M)$ ) since each of these kernels involve accessing every single element in the differentiable memory at least once for each of the read (write) heads. Furthermore, these kernels exhibit very little reuse, accessing the external memory in a streaming fashion. Note that the only opportunity for reuse in such kernels is across multiple heads, which is usually less than a factor of five. This combination of large memory footprint and extremely low FLOPs/Byte ratio cannot be mitigated through the standard techniques for DNNs, *viz.*, compression and batching. Since the differentiable memory content is dynamic, the memory footprint cannot be reduced by using weight compression techniques [85]. Moreover, the external memory is unique to each input sequence to the NTM, and therefore it cannot be shared across input batches similar to RNNs and MLPs. Thus, accelerating NTMs requires designing hardware specifically for low FLOPs/Byte ratios. It is also important to note that while both key similarity and soft reads involve vector-matrix multiplications, the external memory access patterns for the constituent dot products are fundamentally different. Specifically, dot products for key similarity are performed across the rows, while dot products for soft read are performed across the columns. Therefore, it is also important to enable efficient access along both rows and columns.

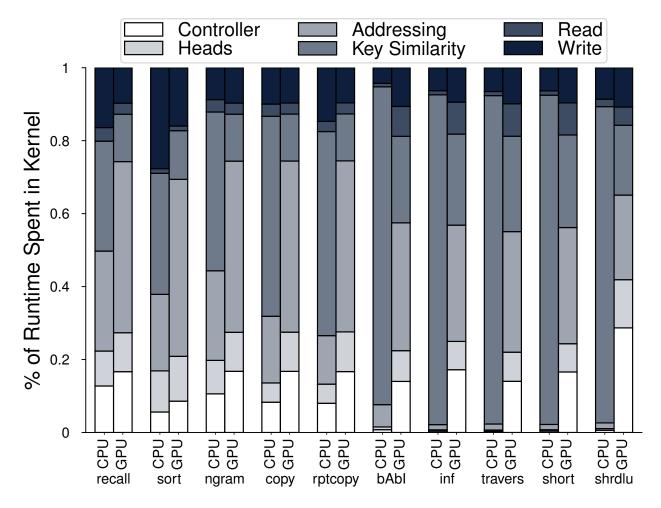

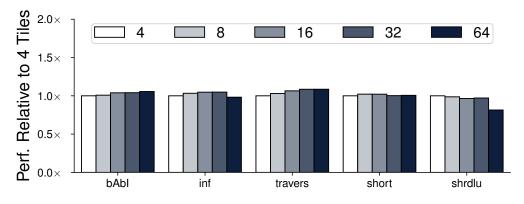

Figure 3.2. Runtime breakdown of different NTM kernels

Kernel breakdown. Figure 3.2 presents a breakdown of the runtime spent during inference in different MANN kernels across a suite of ten benchmarks. These benchmarks use differentiable memories that have been scaled to be larger, but still fit in a reasonably-sized on-chip memory (40MiB). For clarity, the read and write head kernels have been grouped together, as have all of the addressing kernels. As shown in the figure, the non-controller kernels, *viz.*, heads, addressing, key similarity, soft reads, and soft writes, dominate the runtime, making up roughly 80% of the total. This is particularly true for benchmarks that require higher differentiable memory capacity (bAbI, inference, traversal, shortest, and shrdlu). This behavior is expected, since MANNs decouple the dynamic state from the network itself, allowing the amount of dynamic state stored to grow dramatically without significantly increasing the size of the controller network. Hence, efficiently realizing these kernels is key to high performance in MANNs.

Interestingly, the kernels that dominate the total runtime within these runtime-intensive kernels vary depending on the platform. For the CPU platforms, the dominant kernels, particularly at larger differentiable memory sizes, are key similarity, soft write, and soft read. This is because these kernels are extremely memory-intensive compared to the remaining kernels as shown in Table 3.1. However, on GPUs, the vector-only addressing kernels represent an unexpectedly large portion of the runtime, comparable to the memory-intensive access kernels. This is because the memory-heavy access kernels (*e.g.*, key similarity) are large enough to fully utilize the GPU. The addressing kernels, on the other hand, are much smaller, resulting in so-called "narrow tasks" that exhibit poor GPU utilization [86] and thus poor performance due to the GPU kernel call overheads. CPUs, on the other hand, have fewer cores and thus exhibit good utilization even for limited parallelism in the addressing kernels. In order to efficiently perform all of the NTM kernels, an accelerator therefore must be able to efficiently execute both the large, extremely parallel matrix operations as well as the comparatively smaller vector operations.

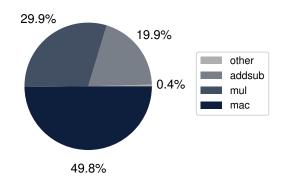

Figure 3.3. Relative mix of operations in runtime-intensive NTM kernels

**Operation breakdown.** Finally, we analyze the relative mix of operations that constitute the runtime-intensive kernels by analytically modeling the number of operations of each type that would be executed when running the **copy** benchmark. As shown in Figure 3.3, we found that, unlike traditional DNN kernels, the non-controller kernels are roughly equally comprised (49.8% each) of fused multiply-and-accumulate operations and element-wise vector operations, specifically multiplication, addition, and subtraction. Thus, an accelerator for MANNs cannot solely emphasize MAC or dot-product performance but rather a high throughput is required on a wider variety of operations.

In summary, we make several observations for desiderata in a MANN accelerator. First, as demonstrated by Figure 3.2, MANN-specific kernels dominate the runtime and therefore a MANN-specific accelerator is warranted. In particular, such an accelerator should: (i) balance the on-chip compute and memory resources for extremely low FLOPs/Byte workloads to maintain high utilization; (ii) provide support for efficient dot products across both rows and columns of the external memory; and (iii) accommodate the higher use of non-MAC compute elements.

## 3.3 Transformer-based Networks

Transformer-based networks can be considered a sub-type of MANNs. Specifically, these networks also utilize an analogue of the *soft attention* reading mechanism found in MANNs (though they do not emply soft write). However, it is useful to examine these networks in depth.

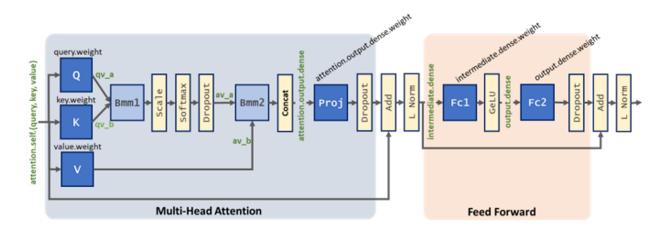

# 3.3.1 Transformers

A Transformer network is a deep neural network (DNN) that consists of one or more embedding layers, followed by multiple Transformer layers, and finally a task-specific final layer that is added when fine-tuning for the given task. The Transformer layer is the main algorithmic innovation in Transformer networks; for brevity, we will mainly focus on this layer, although our experimental evaluations are performed on complete networks. Transformer layers consist of a multi-headed attention block followed by a feed-forward block, as shown in Figure 3.4.

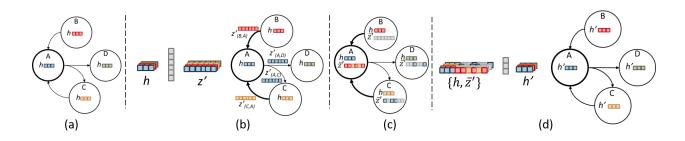

Figure 3.4. A Transformer layer consists of a multi-headed self attention block and a feedforward block. Of particular note is the use of softmax as a crucial operation in self-attention.