## TOWARDS TRUSTWORTHY ON-DEVICE COMPUTATION

by

Heejin Park

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana May 2022

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Felix Xiaozhu Lin, Chair

School of Electrical and Computer Engineering

## Dr. Y. Charlie Hu

School of Electrical and Computer Engineering

## Dr. Saurabh Bagchi

School of Electrical and Computer Engineering

## Dr. Tim Rogers

School of Electrical and Computer Engineering

## Approved by:

Dr. Dimitrios Peroulis

## ACKNOWLEDGMENTS

This long journey would not have been successfully completed without the support from many people in my life. First and foremost, I am most grateful to my advisor, Professor Felix Xiaozhu Lin, for his careful guidance during my time of Ph.D. study. He has been an exemplary advisor in conducting systems research, but also a great life mentor.

I would also like to thank the rest of my committee members, Professor Y. Charlie Hu, Professor Saurabh Bagchi, and Professor Tim Rogers, for their responsiveness and insightful comments on this work. Undoubtedly, their feedback have improved my idea and the dissertation.

It was my pleasure to be a member of system research group, XSEL. I would like to thank all my colleagues Hongyu Miao, Liwei Guo, Tiantu Xu, and Shuang Zhai, for useful discussion and companionship throughout this long journey. I shall not forget the great time we had together in XSEL and at Purdue.

Last but not least, I am grateful to all my family members, particularly my parents, for their unconditional love and support. I would like to dedicate my dissertation to my family.

# TABLE OF CONTENTS

| LI | ST O                                                            | F TAB  | LES                                                                  | 9  |  |  |  |  |

|----|-----------------------------------------------------------------|--------|----------------------------------------------------------------------|----|--|--|--|--|

| LI | ST O                                                            | F FIGU | URES                                                                 | 10 |  |  |  |  |

| A] | BSTR                                                            | ACT    |                                                                      | 12 |  |  |  |  |

| 1  | INT                                                             | RODU   | CTION                                                                | 13 |  |  |  |  |

|    | 1.1                                                             | Motiv  | ation                                                                | 13 |  |  |  |  |

|    | 1.2                                                             | Disser | tation Statement                                                     | 14 |  |  |  |  |

|    |                                                                 | 1.2.1  | StreamBox-TZ: Secure Stream Analytics at the Edge with TrustZone     | 14 |  |  |  |  |

|    |                                                                 | 1.2.2  | GPURip: A 50-KB GPU Stack for Client ML                              | 15 |  |  |  |  |

|    |                                                                 | 1.2.3  | GPU Acceleration in TrustZone via Safe and Practical Recording $~$ . | 15 |  |  |  |  |

|    | 1.3                                                             | Disser | tation Organization                                                  | 16 |  |  |  |  |

| 2  | 2 STREAMBOX-TZ: SECURE STREAM ANALYTICS AT THE EDGE WITH TRUST- |        |                                                                      |    |  |  |  |  |

|    | ZON                                                             | VE     |                                                                      | 17 |  |  |  |  |

|    | 2.1                                                             | Introd | luction                                                              | 17 |  |  |  |  |

|    | 2.2                                                             | Backg  | round & Motivation                                                   | 20 |  |  |  |  |

|    |                                                                 | 2.2.1  | ARM for Cloud Edge                                                   | 20 |  |  |  |  |

|    |                                                                 | 2.2.2  | Stream Analytics                                                     | 21 |  |  |  |  |

|    |                                                                 | 2.2.3  | Security Threats & Design Objectives                                 | 22 |  |  |  |  |

|    | 2.3                                                             | Securi | ty Approach Overview                                                 | 23 |  |  |  |  |

|    |                                                                 | 2.3.1  | Scope                                                                | 23 |  |  |  |  |

|      | 2.3.2   | Approach and Security Benefits       | 24 |

|------|---------|--------------------------------------|----|

| 2.4  | Design  | n Overview                           | 26 |

|      | 2.4.1   | Challenges                           | 26 |

|      | 2.4.2   | StreamBox-TZ in a Nutshell           | 28 |

| 2.5  | Truste  | ed Primitives and Optimizations      | 30 |

| 2.6  | TEE ]   | Memory Management                    | 31 |

|      | 2.6.1   | Unbounded Array                      | 31 |

|      | 2.6.2   | Placing uArrays in uGroups           | 32 |

| 2.7  | Attest  | tation for Correctness and Freshness | 34 |

| 2.8  | Imple   | mentation                            | 37 |

| 2.9  | Evalu   | ation                                | 38 |

|      | 2.9.1   | TCB Analysis                         | 38 |

|      | 2.9.2   | Performance & Overhead               | 39 |

|      | 2.9.3   | Validation of Key Design Features    | 45 |

| 2.10 | Relate  | ed Work                              | 47 |

| 2.11 | Concl   | usions                               | 48 |

| GPU  | JRIP: A | A 50-KB GPU STACK FOR CLIENT ML      | 49 |

| 3.1  | Introd  | luction                              | 49 |

| 3.2  | Motiv   | rations                              | 52 |

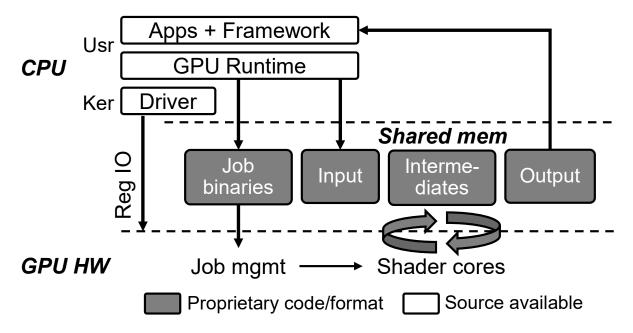

|      | 3.2.1   | The GPU stack and its problems       | 52 |

|     | 3.2.2  | GPU Trends We Exploit                     | 54 |

|-----|--------|-------------------------------------------|----|

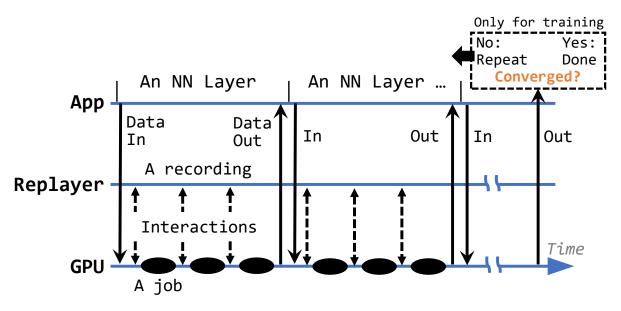

| 3.3 | GPUF   | Rip                                       | 55 |

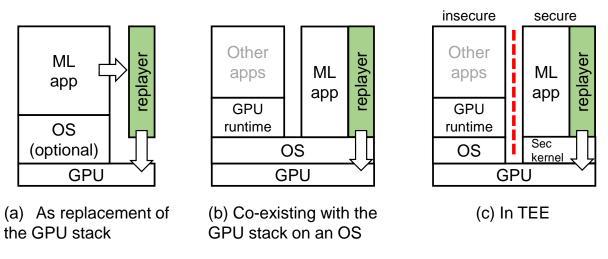

|     | 3.3.1  | Using GPURip                              | 55 |

|     | 3.3.2  | The GPU Model                             | 58 |

| 3.4 | Recor  | d                                         | 60 |

|     | 3.4.1  | Interface Knowledge and Instrumentation   | 60 |

|     | 3.4.2  | Register access                           | 61 |

|     | 3.4.3  | Dumping proprietary job binaries          | 61 |

|     | 3.4.4  | Locating input and output for a recording | 62 |

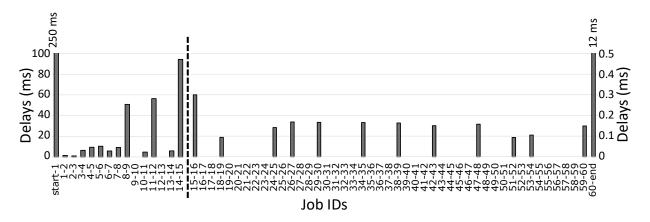

|     | 3.4.5  | Pace replay actions                       | 63 |

| 3.5 | Replay | y                                         | 65 |

|     | 3.5.1  | Verification of security properties       | 65 |

|     | 3.5.2  | The nano GPU driver                       | 66 |

|     | 3.5.3  | GPU handoff and preemption                | 66 |

|     | 3.5.4  | Handling replay failures                  | 66 |

| 3.6 | Imple  | mentations and Experiences                | 67 |

|     | 3.6.1  | The recorder for Arm Mali                 | 68 |

|     | 3.6.2  | The recorder for Broadcom v3d             | 68 |

|     | 3.6.3  | Replayers in various environments         | 68 |

|     | 3.6.4  | Reusing recordings across GPU models      | 70 |

|   | 3.7 | Evalua | ation                                                 | 70 |

|---|-----|--------|-------------------------------------------------------|----|

|   |     | 3.7.1  | Analysis                                              | 71 |

|   |     | 3.7.2  | Validation of replay correctness                      | 72 |

|   |     | 3.7.3  | Memory overheads                                      | 74 |

|   |     | 3.7.4  | Replay speed                                          | 75 |

|   |     | 3.7.5  | Validation of Key Designs                             | 77 |

|   | 3.8 | Relate | ed Work                                               | 79 |

|   | 3.9 | Concl  | uding Remarks                                         | 80 |

| 4 | GPU | J ACCE | ELERATION IN TRUSTZONE VIA SAFE AND PRACTICAL RECORD- | -  |

|   | ING |        |                                                       | 81 |

|   | 4.1 | Introd | luction                                               | 81 |

|   | 4.2 | Motiv  | ations                                                | 85 |

|   |     | 4.2.1  | Mobile GPUs                                           | 85 |

|   |     | 4.2.2  | Prior Approaches                                      | 86 |

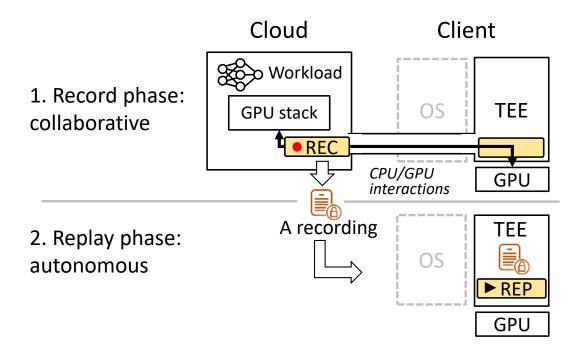

|   |     | 4.2.3  | GPURip in TrustZone                                   | 86 |

|   |     | 4.2.4  | The Problem of Recording Environment                  | 87 |

|   | 4.3 | CoDry  | y                                                     | 89 |

|   |     | 4.3.1  | The Approach                                          | 89 |

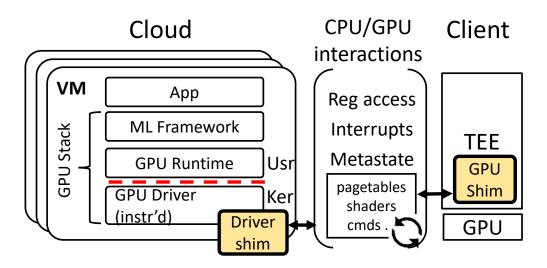

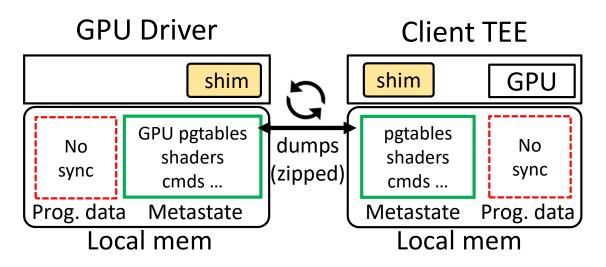

|   |     | 4.3.2  | The CoDry architecture                                | 91 |

|   |     | 4.3.3  | Challenge: long network delays                        | 91 |

|    | 4.4  | Hiding Register Access Delays                                                                                                                                   |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

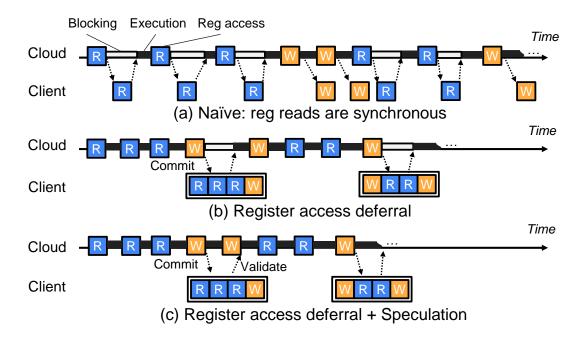

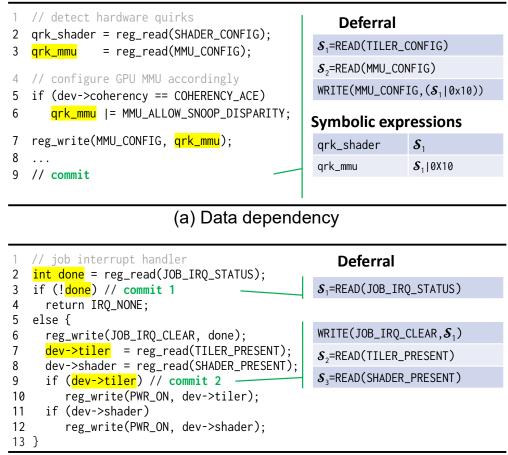

|    |      | 4.4.1 Register Access Deferral                                                                                                                                  |

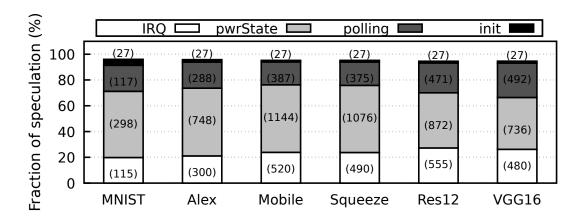

|    |      | 4.4.2 Speculation $\dots \dots \dots$                           |

|    |      | 4.4.3 Offloading polling loops                                                                                                                                  |

|    | 4.5  | Memory Synchronization                                                                                                                                          |

|    | 4.6  | Implementations $\ldots \ldots \ldots$          |

|    | 4.7  | Evaluation $\ldots$                                                            |

|    |      | 4.7.1 Security Analysis                                                                                                                                         |

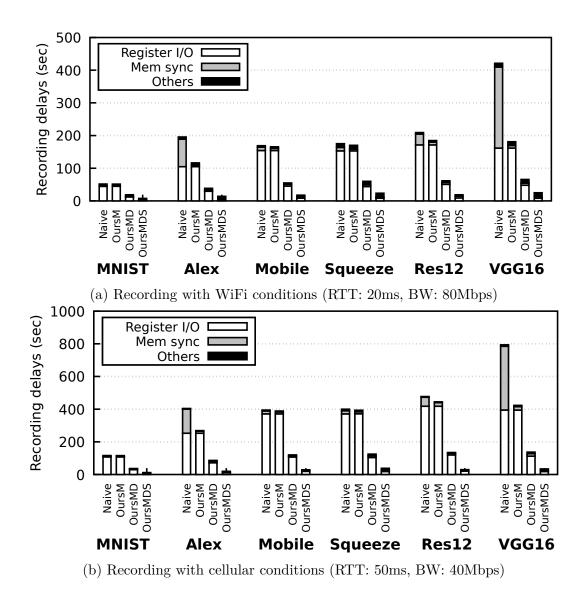

|    |      | 4.7.2 Performance $\ldots \ldots \ldots$        |

|    |      | 4.7.3 Validation of key designs                                                                                                                                 |

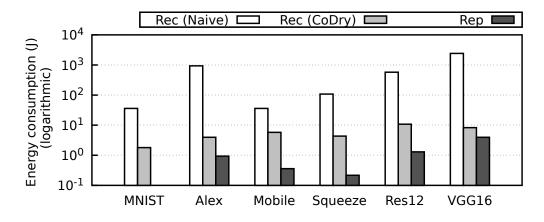

|    |      | 4.7.4 Energy consumption $\ldots \ldots \ldots$ |

|    | 4.8  | Related Work                                                                                                                                                    |

|    | 4.9  | Conclusions                                                                                                                                                     |

| 5  | CON  | CLUSIONS 113                                                                                                                                                    |

| RI | EFER | ENCES $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $115$                                                                                                        |

# LIST OF TABLES

| 2.1 | Comparison to existing secure processing systems                                                                                                                                                                                                                | 29  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Selected trusted primitives (23 in total) and operators they constitute. These operators cover most listed in the Spark Streaming documentation [93]                                                                                                            | 29  |

| 2.3 | The test platform used in experiments                                                                                                                                                                                                                           | 39  |

| 2.4 | A breakdown of the StreamBox-TZ source, of which 5K SLoC are in TCB. Binary code sizes shown in parentheses                                                                                                                                                     | 39  |

| 2.5 | Engine versions for comparison (plots in Figure 2.8)                                                                                                                                                                                                            | 40  |

| 3.1 | Our GPU model fits popular integrated GPUs. *= To enforce sync job submission: Mali: reduce the job queue length; TegraX1: inject synchronization points to a command buffer; Adreno: check submitted job completion before a new command flush. NC: no changes | 58  |

| 3.2 | Replay actions in a recording                                                                                                                                                                                                                                   | 61  |

| 3.3 | GPURip implementations. $* =$ used in evaluation. See Table 3.5 for evaluated recordings                                                                                                                                                                        | 67  |

| 3.4 | Codebase comparisons. Binaries are stripped.                                                                                                                                                                                                                    | 70  |

| 3.5 | NN inference for evaluation. Choices of NNs for Mali vs. v3d are slightly different because their ML frameworks do not implement exactly the same set of NNs $$ .                                                                                               | 73  |

| 4.1 | Statistics of record runs, showing CoDry significantly reduces network round trips that block the recording and the memory synchronization traffic                                                                                                              | 107 |

| 4.2 | Replay delays of CoDry (OursMDS) are similar to Native, which executes benchmarks on the GPU stack in the normal world of the same device                                                                                                                       | 107 |

# LIST OF FIGURES

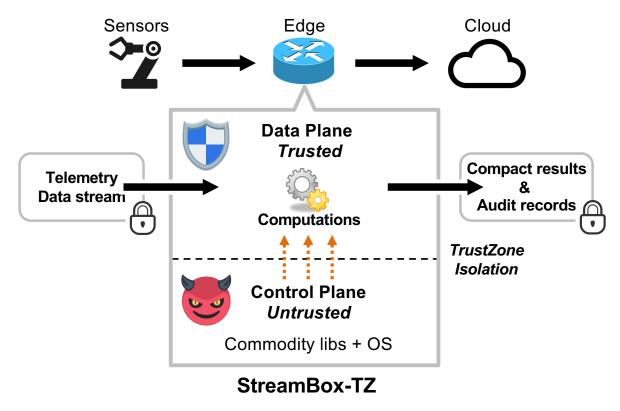

| 2.1  | An overview of StreamBox-TZ                                                                                                                                                                                                                         | 19 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

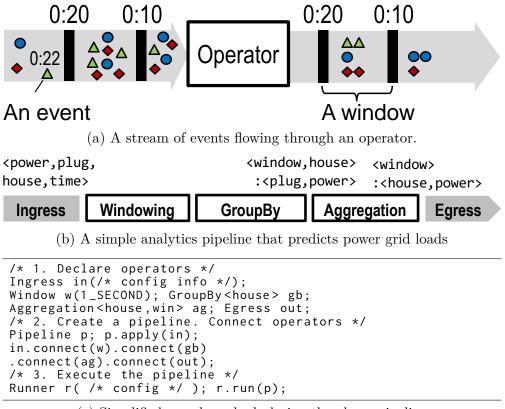

| 2.2  | Example stream data, operators, and a pipeline                                                                                                                                                                                                      | 21 |

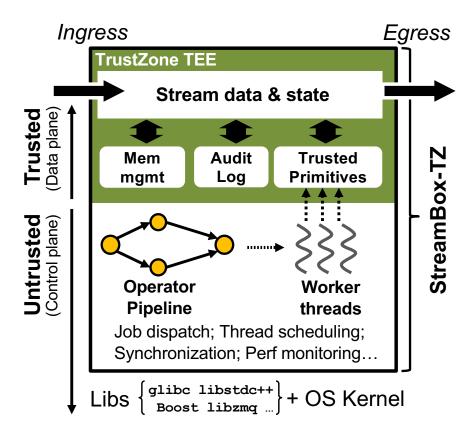

| 2.3  | SBT on an edge platform with ARM TrustZone. Bold arrows show the pro-<br>tected data path                                                                                                                                                           | 25 |

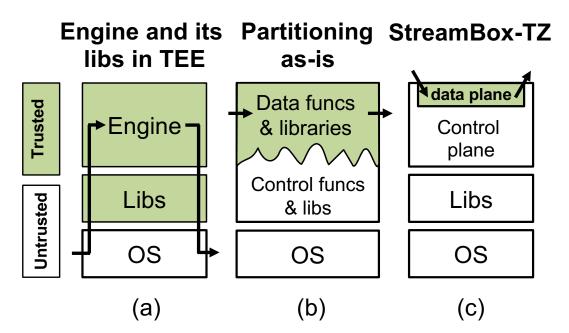

| 2.4  | Among alternative architectures for secure stream analytics, StreamBox-TZ (c) leads to the smallest TCB and the most optimized data plane. Arrows indicate data flows                                                                               | 27 |

| 2.5  | The uArrays in one uGroup                                                                                                                                                                                                                           | 33 |

| 2.6  | Audit records: fields (top) and layout (bottom)                                                                                                                                                                                                     | 35 |

| 2.7  | Sample audit records for the pipeline in Figure 2.2. Format is simplified. ts means processing timestamp.                                                                                                                                           | 36 |

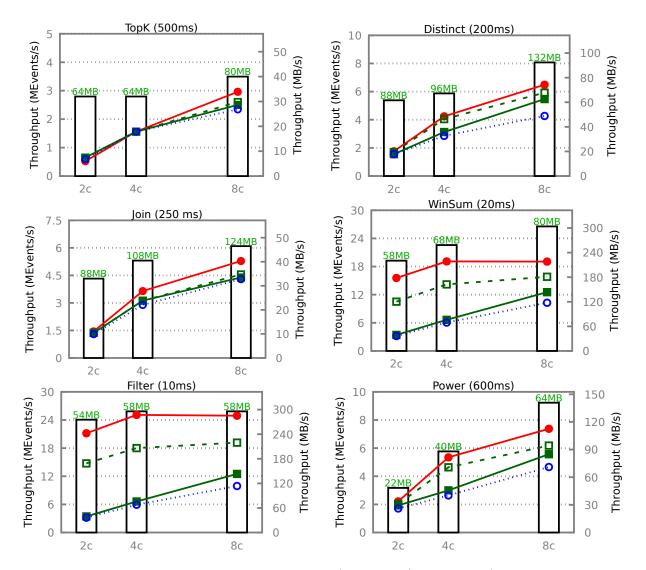

| 2.8  | StreamBox-TZ throughput (lines, left/right y-axes) as a function of CPU cores (x-axis) under given output delays (above each plot). Steady consumptions of TEE memory as columns with annotated values. See Table 2.5 for legends and explanations. | 42 |

| 2.9  | StreamBox-TZ achieves much higher throughput than commodity insecure engines [51], [57], [92] on HiKey. Benchmark: windowed aggregation; target output delay: 50ms.                                                                                 | 43 |

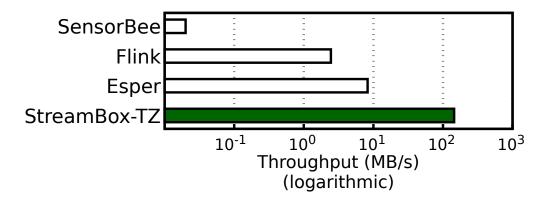

| 2.10 | Run time breakdown of operator GroupBy under different input batch sizes.<br>The control plane runs 8 threads to execute GroupBy in parallel. Total execu-<br>tion time is normalized to 100%.                                                      | 44 |

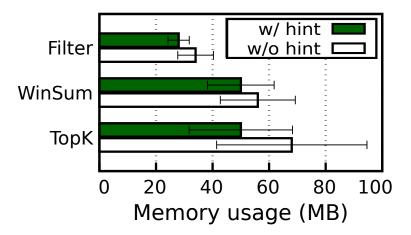

| 2.11 | Without consumption hints, the allocator uses more TEE memory. Since<br>memory usage fluctuates at run time, the error bars show two standard devi-<br>ations below and above the average                                                           | 45 |

| 2.12 | On-demand growth of uArrays vs. std::vector                                                                                                                                                                                                         | 46 |

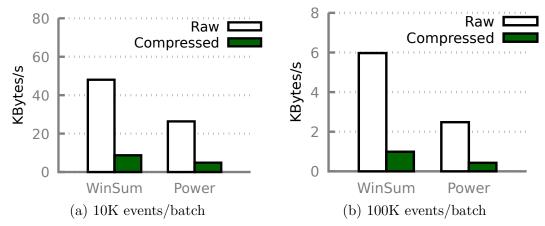

| 2.13 | Compression of audit records saves uplink bandwidth substantially                                                                                                                                                                                   | 47 |

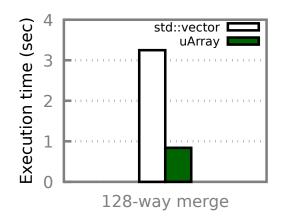

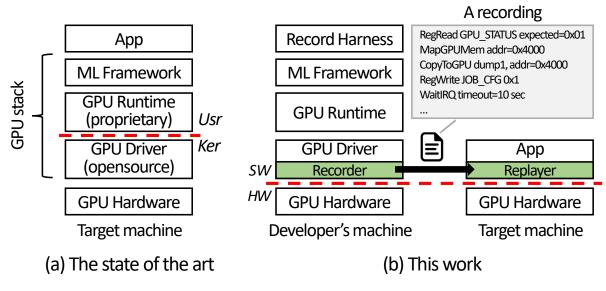

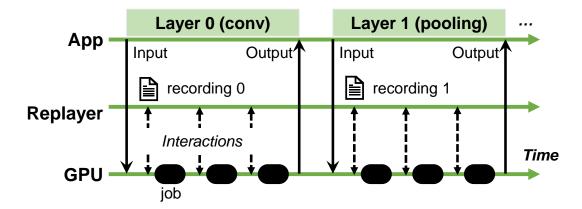

| 3.1  | The overview of GPURip                                                                                                                                                                                                                              | 50 |

| 3.2  | The software/hardware for an integrated GPU                                                                                                                                                                                                         | 53 |

| 3.3  | Replaying NN execution with GPURip                                                                                                                                                                                                                  | 55 |

| 3.4  | The different ways to deploy a GPURip replayer                                                                                                                                                                                                      | 57 |

| 3.5  | Intervals between CPU/GPU interactions, accumulated by GPU job. Intervals among earlier jobs are longer than later ones. Workload: AlexNet inference. ACL [148] on Mali G71. Excluded: GPU busy time; parameters loading | C 4 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | IO                                                                                                                                                                                                                       | 64  |

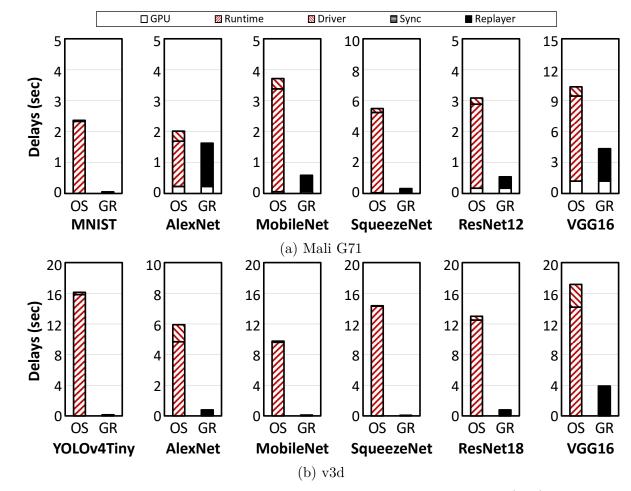

| 3.6  | Startup delays prior to NN inference. The replayer (GR) takes much less time than the original GPU stack (OS).                                                                                                           | 74  |

| 3.7  | NN inference delays. The replayer (GR) incurs similar delays as compared to the original GPU stack (OS).                                                                                                                 | 75  |

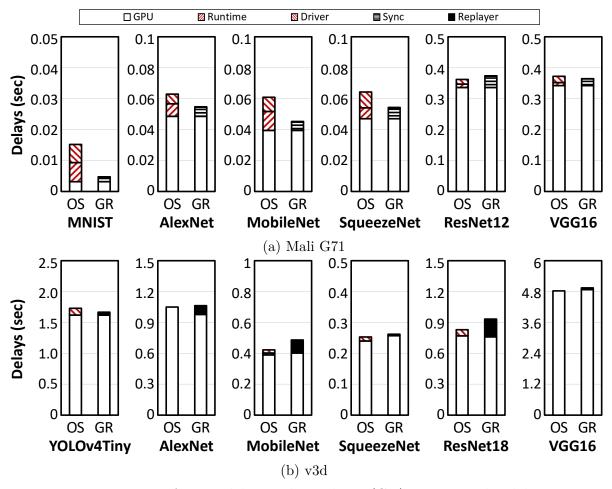

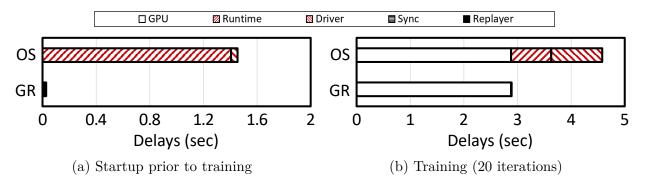

| 3.8  | NN training delays. Benchmark: MNIST training atop DeepCL + OpenCL on Mali G71 (OS: orig stack; GR: GPURip)                                                                                                              | 77  |

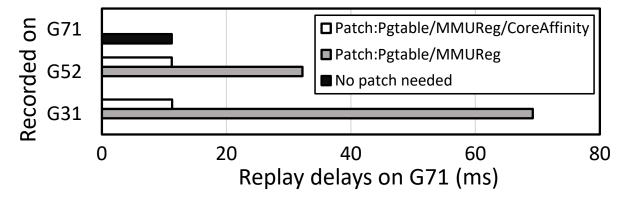

| 3.9  | Mali G71 can replay recordings from other GPUs at full hardware speed.<br>Benchmark: 16M elements <b>vecadd</b>                                                                                                          | 77  |

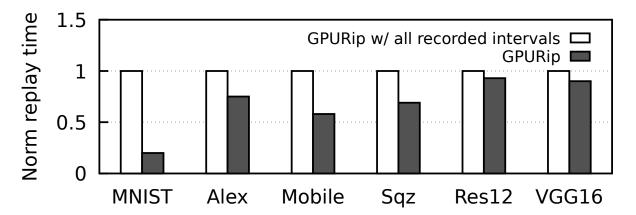

| 3.10 | GPURip removes unnecessary intervals between replay actions. Benchmark:<br>ACL NN inference atop Mali G71                                                                                                                | 78  |

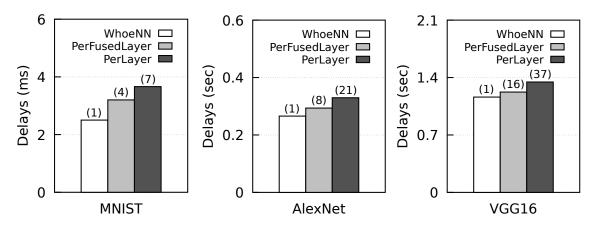

| 3.11 | NN inference delays (including startup) with various granularities. The count of recordings is annotated.                                                                                                                | 78  |

| 4.1  | System overview. Shaded components belong to CoDry                                                                                                                                                                       | 82  |

| 4.2  | A timeline for replaying NN inference                                                                                                                                                                                    | 87  |

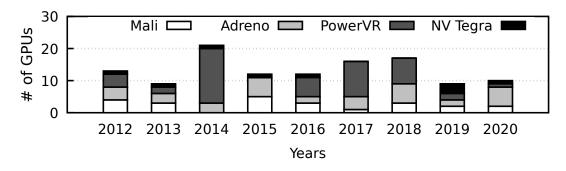

| 4.3  | Numbers of mobile GPU models per year [241]                                                                                                                                                                              | 88  |

| 4.4  | CoDry's online recording. The cloud VM collaboratively runs GPU stack with the client GPU.                                                                                                                               | 89  |

| 4.5  | CoDry's strategies for hiding long RTTs                                                                                                                                                                                  | 93  |

| 4.6  | Selective memory synchronization of GPU metastate but not program data .                                                                                                                                                 | 100 |

| 4.7  | Recording delays of CoDry(OursMDS) are significantly lower than other versions                                                                                                                                           | 106 |

| 4.8  | Breakdown of speculation; the actual number of commits for each segment are shown in parentheses.                                                                                                                        | 108 |

| 4.9  | Energy consumption for record and replay                                                                                                                                                                                 | 109 |

## ABSTRACT

Driven by breakthroughs in mobile and IoT devices, on-device computation becomes promising. Meanwhile, there is a growing concern over its security: it faces many threats in the wild, while not supervised by security experts; the computation is highly likely to touch users' privacy-sensitive information. Towards trustworthy on-device computation, we present novel system designs focusing on two key applications: stream analytics, and machine learning training and inference.

First, we introduce Streambox-TZ (SBT), a secure stream analytics engine for ARMbased edge platforms. SBT contributes a data plane that isolates only analytics' data and computation in a trusted execution environment (TEE). By design, SBT achieves a minimal trusted computing base (TCB) inside TEE, incurring modest security overhead.

Second, we design a minimal GPU software stack (50KB), called GPURip. GPURip allows developers to record GPU computation ahead of time, which will be replayed later on client devices. In doing so, GPURip excludes the original GPU stack from run time eliminating its wide attack surface and exploitable vulnerabilities.

Finally, we propose CoDry, a novel approach for TEE to record GPU computation remotely. CoDry provides an online GPU recording in a safe and practical way; it hosts GPU stacks in the cloud that collaboratively perform a dryrun with client GPU models. To overcome frequent interactions over a wireless connection, CoDry implements a suite of key optimizations.

## 1. INTRODUCTION

### 1.1 Motivation

A recent support of powerful processors expedites on-device computation in mobile/edge environments, which directly processes sensor data on low-end (client) devices not a cloud server. The key application is mobile/edge intelligence including stream analytics and machine learning. In such applications, system security including data and computation is crucial. (1) They are often parts of mission-critical systems [1]–[3], e.g. aircraft control, electricity grid and emergency communication systems. Hence, a corrupted computation may lead to a critical result on the entire system. (2) As being processed, the data potentially include confidential information [4]–[6], e.g. proprietary sensor data or video frames.

However, a security issues over on-device computation have been constantly reported [7]– [9], raising concerns of end users. Fundamentally, the on-device computation faces following security threats. (1) Unlike a cloud which is well supervised by security professionals [10], [11], a client device is managed by end users who are often non-experts. Hence, the device may suffer from a weak security configuration, a late security update, or a slow countermeasure to a new attacks. (2) The data flows through a set of sophisticated components that exposes a wide attack surface. For example, the client device should host a complex software stack for stream analytics or GPU stack for machine learning workloads, where exploitable vulnerabilities are not uncommon [12], [13]. (3) With data including privacy-sensitive information, e.g. user's health activities, voice records, and photos, a client device is easily considered as a high-value target to adversaries.

For these reasons, we claim that a new system design is necessary to achieve trustworthy on-device computation with strong security guarantees. Once attackers compromise devices, they not only access confidential data but also may fabricate the result, threatening the integrity of an entire system.

## 1.2 Dissertation Statement

This dissertation aims at addressing security concerns over on-device computation. Towards trustworthy on-device computation, we draw new system designs taking applicationspecific security properties into account. Our first objective is to enable a secure stream analytics on an edge platform, which safeguards data confidentiality and integrity, supports verifiable results, and ensures high throughput with low output delay. Our second objective is to enable a secure GPU acceleration on client devices, eliminating a complex, vulnerable GPU stack at run time. Our last objective is to provide a cloud service for a secure GPU acceleration on client devices in safe and practical ways. To achieve the above goals, we consider the following approaches.

- Analyzing key applications and minimizing corresponding software stacks

- Leveraging a hardware-supported trusted execution environment, e.g. ARM TrustZone

- Involving a trustworthy cloud in the computation.

We demonstrate the efficacy of our approaches with the three main projects.

## 1.2.1 StreamBox-TZ: Secure Stream Analytics at the Edge with TrustZone

To achieve our first objective, we present StreamBox-TZ, a secure analytics engine at an edge platform. StreamBox-TZ isolates the data and its computation in a trusted execution environment (TEE) on the edge, shielding them from the remaining edge software stack which is deemed untrusted. StreamBox-TZ offers strong data security, verifiable results, and good performance. It contributes a data plane designed and optimized for a TEE based on ARM TrustZone. It supports continuous remote attestation for analytics correctness and result freshness while incurring low overhead. StreamBox-TZ only adds 42.5 KB executable to the TCB (16% of the entire TCB). On an octa core ARMv8 platform, it delivers the state-of-the-art performance by processing input events up to 140 MB/sec (12M events/sec) with sub-second delay. The overhead incurred by StreamBox-TZ's security mechanism is less than 25%.

## 1.2.2 GPURip: A 50-KB GPU Stack for Client ML

We accomplish our second objective with GPURip, a novel way for deploying GPUaccelerated computation on mobile and embedded devices. It addresses high complexity of a modern GPU stack for deployment ease and security. The idea is to record GPU executions on the full GPU stack ahead of time and replay the executions on new input at run time. We address key challenges towards making GPURip feasible, sound, and practical to use. The resultant replayer is a drop-in replacement of the original GPU stack. It is tiny (50 KB of executable), robust (replaying long executions without divergence), portable (running in a commodity OS, in TEE, and baremetal), and quick to launch (speeding up startup by up to two orders of magnitude). We show that GPURip works with a variety of integrated GPU hardware, GPU APIs, ML frameworks, and 33 neural network (NN) implementations for inference or training.

## 1.2.3 GPU Acceleration in TrustZone via Safe and Practical Recording

We attain our final objective with CoDry, a holistic design for GPU-accelerated computation in TrustZone TEE. Without pulling the complex GPU software stack into the TEE, we follow a simple approach: record the CPU/GPU interactions ahead of time, and replay the interactions in the TEE at run time. This paper addresses the approach's key missing piece – the recording environment, which needs both strong security and access to diverse mobile GPUs. To this end, we present a novel architecture called CoDry, in which a mobile device (which possesses the GPU hardware) and a trustworthy cloud service (which runs the GPU software) exercise the GPU hardware/software in a collaborative, distributed fashion. To overcome numerous network round trips and long delays, CoDry contributes optimizations specific to mobile GPUs: register access deferral, speculation, and metastateonly synchronization. With these optimizations, recording a compute workload takes only tens of seconds, which is up to 95% less than a naive approach; replay incurs 25% lower delays compared to insecure, native execution.

## 1.3 Dissertation Organization

This dissertation is organized as follows. Chapter 2 describes StreamBox-TZ, a secure stream analytics leveraging ARM TrustZone. Chapter 3 presents GPURip, which squeezes attack surfaces and removes vulnerabilities from GPU stack by record and replay GPU computation. Chapter 4 proposes CoDry, a cloud service for collaborative dryrun to record GPU computation with client TEE. Chapter 5 summarizes the dissertation.

# 2. STREAMBOX-TZ: SECURE STREAM ANALYTICS AT THE EDGE WITH TRUSTZONE

## 2.1 Introduction

Many key applications of Internet of Things (IoT) process a large influx of sensor<sup>1</sup> data, i.e. telemetry. Oil producers track tank status, pump pressure, and fluid temperatures to see if wells work at ideal operating operating points [14], [15]; an oil rig is reported to produce 1–2TB of data per day [16]. Smart grid aggregates power telemetry to detect supply/demand imbalance and power disturbances [17]; a power sensor is reported to produce up to 140 million samples per day [18], [19]. Manufacturers routinely monitor vibration and ultrasonic energy of industrial equipment to discover anomalies and do predictive maintenance; a monitored machine is reported to create PBs of data in a matter of days.

The large telemetry data streams must be processed in time. The high cost and long delay in transmitting the data necessitate edge processing [20], [21]: sensors send the data to nearby gateways dubbed "cloud edge"; the edge runs a pipeline of continuous computations to cleanse and summarize the telemetry data and reports the results to cloud servers for deeper analysis. The hardware at the edge is often optimized for cost and efficiency. According to a 2018 survey [22], modern ARM machines are typical choices for edge platforms. Such a platform often has 2–8 CPU cores and several GB DRAM.

Unfortunately, edge processing exposes the IoT data to significant security threats. i) Deployed in the wild, the edge suffers from common IoT weaknesses such as lack of professional supervision [23], [24], weak configurations [25], [26], and delayed security updates [23], [27]. ii) On the edge, the IoT data flows through a set of sophisticated components that expose a wide attack surface. These components include a commodity OS (e.g. Linux or Windows), a set of user libraries, and a runtime framework called *stream analytics engine* [28]–[30]. They reuse much code developed for servers and workstations. It is not uncommon for them to have exploitable misconfigurations [31] and vulnerabilities [32]–[34] iii) As data aggregated from various sources, the edge become a high-value target to adversaries. For these reasons,

<sup>&</sup>lt;sup>1</sup>Recognizing that IoT data sources range from small sensors to large equipment, we refer to them all as *sensors* for brevity.

edge is even *more vulnerable* than sensors, which run much simpler software with narrower attack surfaces. Once attackers compromise the edge, they can not only obtain confidential data but also remove or fabricate data transmitted to the cloud, threatening the integrity of an entire IoT deployment.

Towards secure stream analytics on an edge platform, our goal is to safeguard IoT data confidentiality and integrity, support verifiable results, and ensure high throughput with low output delay. Following the principle of least privilege [35], we protect the analytics data and computations in a trusted execution environment (TEE) and limit their interface; we leave out the remaining edge software stack which we deem untrusted. In doing so, the trusted computing base (TCB) is reduced to only the protected functionalities, the TEE, and the hardware. We hence significantly enhance data security.

We face three challenges: i) what functionalities should be secured in TEE and behind what interfaces? ii) how to execute stream analytics on a TEE's low TCB and limited physical memory while still delivering high throughput and low delay? iii) as both trusted and untrusted edge components participate in stream analytics, how to verify the outcome?

Existing solutions are inadequate: pulling entire stream analytics engines to TEE [36]– [38] would result in a large TCB with a wide attack surface; the systems securing distributed operators [39]–[41] often lack stream semantics or optimizations for efficient execution in a single TEE, which are crucial to the edge; only attesting TEE integrity [42] or data lineages [39], [40], [43], [44] is insufficient to verify stream analytics. We will show more evidences in the paper.

Our response is SBT, a secure engine for analytics over telemetry data streams. As shown in Figure 2.1, SBT builds on ARM TrustZone [45] on an edge platform. SBT contributes the following notable designs:

(1) Architecting a data plane for protection SBT provides a data plane exposing narrow, shared-nothing interfaces to untrusted software. SBT's data plane encloses i) all the analytics data; ii) a new library of low-level stream algorithms called *trusted primitives* as the only allowed computations on the data; iii) key runtime functions, including memory management and cache-coherent parallel execution of trusted primitives. SBT leaves thread scheduling and synchronization out of TEE.

Figure 2.1. An overview of StreamBox-TZ

(2) Optimizing data plane performance within a TEE In contrast to many TEE-oblivious stream engines that operate numerous small objects, hash tables, and generic memory allocators [46]–[48], SBT embraces unconventional design decisions for its data plane. i) SBT implements trusted primitives with array-based algorithms and contributes new optimizations with handwritten ARMv8 vector instructions. ii) To process high-velocity data in TEE, SBT introduces a new abstraction called uArrays, which are contiguous, virtually unbounded buffers for encapsulating all the analytics data; SBT backs uArrays with on-demand paging in TEE and manages uArrays using a dedicated allocator. For the compact memory layout, the allocator leverages hints from untrusted software. iii) SBT takes advantage of TrustZone's lesser-explored hardware features: ingesting data straightly through trusted IO without a detour through the untrusted OS; avoiding relocating streaming data by leveraging the large virtual address space dedicated to a TEE.

(3) Verifying edge analytics execution SBT provides cloud verifiers to attest analytics correctness, result freshness, and the untrusted hints received during execution. SBT captures coarse-grained dataflows and generates audit records. A cloud verifier replays the audit records for attestation. To save the edge-cloud uplink bandwidth, SBT compresses the records with domain-specific encoding.

We implement SBT to offer a generic stream model [49] with a broad arsenal of stream operators. The TCB of SBT contains as little as 267.5 KB of executable code, of which SBT only constitutes 16%. On an octa core ARMv8 platform, SBT processes up to 12M events (144 MB) per second at sub-second output delays. Its throughput on this platform is an order of magnitude higher than an SGX-based secure stream engine running on a small x86 cluster with richer hardware resources [41]. SBT's security mechanisms incur less than 25% throughput loss with the same output delay; decrypting ingress data, when required, results in 4%–35% throughput loss with the same output delay. In most benchmarks, SBT consumes up to 130 MB of physical memory while sustaining high throughput.

The key contributions of SBT are: i) a stream engine architecture with strongly isolated data and a lean TCB; ii) a data plane built from the ground up with computations and memory management optimized for a single TrustZone-based TEE; iii) remote attestation for stream analytics on the edge with domain-specific compression of audit records. To our knowledge, SBT is the first system designed and optimized for data-intensive, parallel computations inside ARM TrustZone. Beyond stream analytics, the SBT architecture should aid in secure other important analytics on the edge, e.g. machine learning inference. The SBT source can be found at http://github.com/edgeflow-dev.

## 2.2 Background & Motivation

### 2.2.1 ARM for Cloud Edge

Recent ARM platforms are typically preferred as hardware for IoT gateways [22], because of competitive performance at low power, which suits edge as well. Most modern ARM cores are equipped with TrustZone [45], a security extension for TEE enforcement. TrustZone logically partitions a platform's hardware resources, e.g. DRAM and IO, into a normal (insecure) and a secure world. CPU cores independently switch between two worlds. A

(c) Simplified pseudo code declaring the above pipeline

Figure 2.2. Example stream data, operators, and a pipeline

TEE atop TrustZone owns dedicated channel called *trusted IO*, a unique feature that TEE technologies e.g. Intel SGX [50] lack.

## 2.2.2 Stream Analytics

**Stream Model** We focus on stream analytics over sensor data. A data stream comprises of sensor events that carry timestamps defined by event occurrence, as illustrated in Figure 2.2(a). Programmers define a pipeline of continuous computations called *operators*, e.g. Filter, Count, and GroupBy, that are widely used for telemetry analytics [51], [52]. As data arrives at the edge, a stream analytics engine ingests the data at the pipeline ingress, pushes the data through the pipeline, and externalizes the results at the pipeline egress.

We follow a generic stream model [46], [48], [53]–[55]. Operators execute on event-time scopes called *windows*. Data sources emit special events called *watermarks*. A watermark

ensures that no subsequent events in the stream will have event times earlier the watermark timestamp. A pipeline's *output delay* is defined as the elapsed time starting from the moment the ingress receives the watermark signaling the completion of the current window to the moment the egress externalizes the window results [47]. A pipeline may maintain its internal states organized by windows at different operators. See prior work [56] for a formal stream model.

Analytics example: Power load prediction Figure 2.2(b-c) depicts an example derived from an IoT scenario [52]: it forecasts future household power loads based on the current loads reported by smart power plugs. The example pipeline ingests a stream of power samples and groups them by 1-second fixed windows and by houses. For each house in each window, it aggregates all the loads and predicts the next-window load as an exponentially weighted moving average over the recent windows. At the egress, the pipeline emits a stream of per-house load prediction for each window.

**Stream analytics engines** Stream pipelines are executed by a runtime framework called a stream analytics engine [28]–[30], [47], [51], [57]. A stream analytics engine consists of two types of function: *data functions* for data move and computations; *control functions* for resource management and computation orchestration, e.g. creating and scheduling tasks. The boundary between the two is often blurry. To amortize overheads, control functions often organize data in *batches* and invoke data functions to operate on the batches.

## 2.2.3 Security Threats & Design Objectives

The edge faces common security threats in IoT deployment. First, IT expertise is weak. Edge platforms are likely managed by field experts (such as farmers [27], firefighters [24], and petroleum engineers [23]) rather than IT experts. Such lack of professional supervision is known to result in weak configurations [25], [26]. Second, the infrastructure is weak. Deployed in the field (e.g. farms [27], fireground [24], and offshore oil rigs [23]), the edge often experiences slow uplinks to the cloud and hence much delayed software security updates. For cost saving, edge analytics may need to share OS and hardware with other high-risk, untrusted software [27] such as web browsers. Apart from the common threats, conventional edge software stacks entrust IoT data with commodity operating systems, analytics engines, and language runtimes (e.g. JVM). However, such components are unable to provide strong security guarantees due to their complexity and wide interfaces. Each of them is likely to contain more than several hundreds of KSLoC [58]. A number of vulnerabilities are constantly reported [32], [33], [59]–[61], making these components untrusted in recent research [62]–[65]. By exploiting these vulnerabilities, a local adversary as an edge user program may compromise the kernel through the wide user/kernel interfaces [66], [67] or attack an analytics engine through IPC [68]; a remote adversary, through the edge's network services, may compromise analytics engines [69] or the OS [70]. A successful adversary may expose IoT data, corrupt the data, or covertly manipulate the data. Taking the application in Figure 2.2(b) as an example, the adversary gains access to the smart plug readings, which may contain residents' private information, and injects fabricated data.

**Objectives** We aim three objectives for stream analytics over telemetry data on an edge platform: i) confidentiality and integrity of IoT data, raw or derived; ii) verifiable correctness and freshness of the analytics results; iii) modest security overhead and good performance.

### 2.3 Security Approach Overview

### 2.3.1 Scope

**IoT scenarios** Our target is an edge platform that collects and analyzes telemetry data. We recognize the significance of mission-critical IoT with tight control loops, but do not target it. In our target scenario, there are source sensors, edge platforms, and a cloud server that we dub "cloud consumer". All the raw IoT data and analytics results are owned by one party. The sensors produce trusted events, e.g. by using secure sensing techniques [71]–[73]. The cloud consumer is trustworthy; it defines analytics pipelines to the edge and consumes the results from the edge. We consider *untrusted* source-edge links (e.g. public networks) which requires data encryption by the source, as well as *trusted* source-edge links (e.g. direct IO bus or on-premise local networks), and will evaluate the corresponding designs (§2.9). We assume untrusted edge-cloud links, which require encryption of the uploaded data.

**In-scope Threats** We assume malicious adversaries interested in gaining access to IoT data, tampering with edge processing outcome, or obstructing processing progress. We consider powerful adversaries who can control the entire OS and all applications on the edge by exploiting weak weak configuration or vulnerabilities in the edge software.

**Out-of-scope Threats** We do not protect the confidentiality of stream pipelines, in the interest of including only low-level compute primitives in a lean TCB. We do not defend the following attacks.

- i) Attacks to non-edge components assumed trusted above, e.g. sensors [74].

- ii) Exploitation of TEE kernel bugs [75]-[77].

- iii) Side channel attacks: by observing hardware usage outside TEE, adversaries may learn the properties of protected data, e.g. key skew [78]. Note that controlled-channel attack [79] cannot be applied to ARM TrustZone as it has separate page management within a separate secure OS unlike Intel SGX.

- iv) Physical attacks, e.g. sniffing TEE's DRAM access [80], [81]. Note that many of these attacks are mitigated by prior work [40], [82]–[84] orthogonal to SBT.

## 2.3.2 Approach and Security Benefits

As depicted in Figure 2.3, SBT protects its data functions in a trusted *data plane* in TEE. SBT runs its untrusted *control plane* in the normal world. The control plane invokes the data plane via narrow, shared-nothing interfaces. As a result, the engine's TCB only contains the TEE (including the data plane) and the hardware.

Streaming data always flows in TEE where the data plane ingests the data through TrustZone's trusted IO. After ingestion, the data plane returns *opaque references* of the data batches to the control plane. The opaque references are long, random integers. The control plane then requests computations over the protected data via invoking the data plane with the opaque references. The data plane keeps track of all active opaque references, validates incoming opaque references, and only accept those that genuine. At the pipeline egress, the data plane encrypts, signs, and delivers the result to the cloud.

Figure 2.3. SBT on an edge platform with ARM TrustZone. Bold arrows show the protected data path.

The analytics execution is continuously attested. SBT collects comprehensive and deterministic dataflows of the stream analytics as well as execution timing; it sends periodic reports to the cloud server. The cloud server then verifies if all the ingested data correctly flow through the given pipeline (correctness,) and if the processing incurs low delay (freshness).

**Thwarted attacks** SBT defeats the following attacks.

i) **Breaking IoT data confidentiality or integrity.** Adversaries on the edge cannot touch, drop, or inject data since raw and derived data enters and leaves the dge TEE via trusted IOs. When data is sent off the edge over untrusted networks, it is encrypted and hence protected against network-lever adversaries.

ii) *Breaking the data plane integrity.* As all opaque references are validated before in use, any fabricated opaque reference passed to the data plane will be denied. An adversary

may exploit bugs in the data plane and compromise it through the data plane's interface. However, SBT substantially reduces the data plane's attack surface and potential exploitable bugs by minimizing the data plane codebase and hardening its interface.

iii) **Breaking analytics correctness.** A compromised control plane may request computations deviating from pipeline declarations or the stream model. It may, for example, invoke trusted computations on partial data, incorrect windows, or legitimate but undesirable opaque references. SBT defeats these attacks by remote attestation: the cloud verifier can detect such correctness violation and rejects the edge analytics results since it processes complete knowledge on ingested data and pipelines.

iv) Attacks on analytics performance or availability. A compromised control plane may pause or delay invocation of trusted computations, violating the freshness guarantee. However, the cloud verifier can detect such attacks by attesting the execution timing of trusted computation. When the attack is detected, it can choose to prompt further investigation.

v) Attempting to trigger data race or deadlock. By design, data race and deadlocks will never occur inside the data plane: the trusted computations do not share state concurrently and all locking takes place outside of the TEE.

## 2.4 Design Overview

### 2.4.1 Challenges

Our approach raises three challenges. i) Architecting the engine with a proper protection boundary. This is dependent on a key trade-off among TEE functional richness, overhead of TEE entry/exit, and TCB size. ii) Optimizing data functions within a TEE. To process high-velocity data in a TEE, simple algorithms and compact memory are significantly favored. Existing stream engines, on the other hand, often use a large number of short-lived objects indexed in hash tables or trees [46]–[48], [51], [55], e.g. for grouping events by key. To manage these these objects, they use generic memory allocators [47] or garbage collectors [46], [85]. Such designs are unsuitable for a TEE's small TCB and limited DRAM portion, e.g. typically tens of MB for a TrustZone TEE and up to 128 MB for

Figure 2.4. Among alternative architectures for secure stream analytics, StreamBox-TZ (c) leads to the smallest TCB and the most optimized data plane. Arrows indicate data flows.

an Intel SGX enclave [86]. iii) *Verifying stream analytics results*. This necessitates tracking unbounded data flows in stream pipelines, validating that operators respect the temporal properties, e.g. windows, and minimizing the resultant overhead in execution and communication.

Why are existing systems inadequate? First, many TEE-based systems [36]–[38] pull entire user applications and libraries to the TCB, as illustrated in Figure 2.4(a). A modern analytics engine and its libraries, on the other hand, are huge, complex, and potentially vulnerable as we discussed in Section 2.2.2. Second, partitioning applications to fit a TEE, as shown in Figure 2.4(b) [87]–[89], is unsuitable for existing stream engines: partitioning does not change their hash-based data structures and algorithms, which by design mismatch a TEE. Similarly, recent secure processing engines disfavor partitioning [90], [91]. Third, recent systems deploy TEE to protect data in analytics or network packet processing. As summarized in Table 2.1, they lack support for stream analytics, key computation optimizations, or specialized memory allocation, that we will demonstrate as vital to our objective. To assert analytics correctness, attesting TEE integrity [42], [90] is insufficient. VC3 [39] and Opaque [40] check the history of compute results, i.e. their data lineage [43], [44], to verify correctness of *batch* analytics. Without tracking data as it is continually ingested and without a stream model, data lineages cannot assert whether *all* ingested data processed correctly according to pipeline declarations, temporal windows, and watermarks, which are crucial to stream analytics.

## 2.4.2 StreamBox-TZ in a Nutshell

SBT builds on TrustZone [45] because of ARM's popularity for the edge and trusted IO, which benefits stream analytics ( $\S2.2$ ).

**Programmability** SBT provides a similar programmability like what commodity engines like Spark Streaming [46] and Flink [92] support. Analytics programmers build pipelines using declarative high-level operators as exemplified in Figure 2.2(c). These stream operators are commonly used for analytics over telemetry data [51], [52]. SBT supports the majority of the common operators supplied by commodity engines, as summarized in Table 2.2. These operators are commonly used for analytics over telemetry data [51], [52]. SBT also offers User Defined Functions (UDFs) certified by a trusted party, that is a common requirement in TEE-based systems [90].

**SBT architecture** SBT's data plane incarnates as a TrustZone module, as shown in Figure 2.3, SBT runs its control plane as a parallel runtime in the normal world. The control plane invokes the data plane through a narrow interface (details in Section 2.9). The control plane orchestrates the execution of analytics pipelines. It generates abundant parallelism among and within operators, that is elastically mapped to a poll of threads it maintains. At a given moment, all threads may work concurrently on one operator as well as different operators over different data.

**Data plane & design choices** SBT's data plane consists of only the trusted primitives and a runtime for them.

i) Trusted primitives are stateless, single-threaded functions that are oblivious to synchronization. In the data plan, we do not enclose entire stream pipelines, since a pipeline

| System                   | TEE | Analytics | SG    | Compute in TEE                     | Memory     | Attestation   |  |  |  |

|--------------------------|-----|-----------|-------|------------------------------------|------------|---------------|--|--|--|

| VC3 [39]                 | SGX | Batch     | CIVA- | Mapper/reducer                     | Heap       | Data lineage  |  |  |  |

| Opaque [40]              | SGX | Batch     | CIVAO | Query plans                        | unreported | Data lineage  |  |  |  |

| EnclaveDB [90]           | SGX | Batch     | CI-A- | Pre-compiled queries               | unreported | TEE integrity |  |  |  |

| SafeBricks [91]          | SGX | Pkt proc. | CI-A- | Net func. operators <sup>*</sup>   | unreported | TEE integrity |  |  |  |

| SecureStream [41]        | SGX | Stream    | CI-   | Lua programs                       | unreported | TEE integrity |  |  |  |

| StreamBox-TZ             | TZ  | Stream    | CIV-  | Vectorized primitives <sup>*</sup> | uArray     | Log replay    |  |  |  |

| SG: security guarantees. |     |           |       |                                    |            |               |  |  |  |

Table 2.1. Comparison to existing secure processing systems

C: data confidentiality; I: data integrity; V: verifiability; A: analytics confidentiality; O: obliviousness \* TEE encloses only low-level computations; otherwise TEE encloses whole analytics.

Table 2.2. Selected trusted primitives (23 in total) and operators they constitute. These operators cover most listed in the Spark Streaming documentation [93].

| Trusted Primitives              | Popular Spark Streaming Operators                     |

|---------------------------------|-------------------------------------------------------|

| Sort, Merge, Segment, SumCnt,   | GroupByKey, Windowing, AvgPerKey, Distinct, SumByKey, |

| TopK, Concat, Join, Count, Sum, | AggregateByKey, SortByKey, TopKPerKey, CountByKey,    |

| Unique, FileterBand, Median,    | CountByWindow, Filter, MedianByKey, TempJoin, Union,  |

must be dynamically scheduled for parallel processing over high-velocity data. We do eschew wrapping whole declarative operators in the data plane, as one operator instance contains internal thread-level parallelism and hence requires thread management logic. Our decision keeps the data plane lean, leaving out all control functions including threading and scheduling. In contrast, may other engines shown in Table 2.1 pull entire analytics to TEE. Our choice of exporting low-level primitives entails more TEE switches. Yet, the costs are smaller on modern ARM [75], [94] and can be amortized by batching, data batching, as will be discussed soon.

ii) The data plane incorporates minimum runtime functions: memory management and paging, which are vital to TEE integrity; cache coherence of parallel primitives, which is critical to parallelism. The data plane is agnostic to declarative operators and pipelines being executed.

For attestation, the data plane generates audit records on data ingress/egress, primitive executions, and watermarks. It curtails overhead through data batching and record compression. **Coping with secure memory shortage** SBT may suffer from out of secure memory when the compute cost or data ingestion rate is excessive. SBT avoids data loss in such a situation by adding backpressure to source sensors, slowing down data ingestion. In our current implementation, SBT activates backpressure when ingestion exceeds a user-defined threshold; we leave an automatic flow control as our future work, i.e. online threshold tuning based on available secure memory and backlog.

## 2.5 Trusted Primitives and Optimizations

**Parallel execution inside a TEE** SBT utilizes task parallelism keeping a lean TEE without a threading library. The control plane invokes numerous primitives with worker threads, which then enter the TEE to execute the primitives in parallel. In TEE, all trusted primitives share a single cache-coherent memory address space, which makes data sharing easier and eschews copy costs. This contrasts to existing secure analytics engines that leave task parallelism untapped in a single TEE [39], [41].

Array-based algorithms to suit TEE Unlike common stream engines that use hashbased algorithms to reduce algorithmic complexity, we make a new design choice. We firmly favor algorithms with straightforward logic and little memory overhead, despite of their higher algorithmic complexity. Corresponding to contiguous arrays as the universal data containers in TEE, most primitives employ sequential-access algorithms over contiguous arrays, e.g, executing Merge-Sort across event arrays and scanning the resultant array to get the average value per key.

**Trusted primitives and vectorization** The trusted primitives in SBT are generic. They constitute most declarative stream operators, often referred to as Select-Projection-Join-GroupBy (SPJG) families, shown in Table 2.2. These stream operators are deemed representative in prior research [95].

To speed up the array-based up without causing TCB bloat, our insight is to map their internal data parallelism to ARM's vector instructions [96]. To our knowledge, the vector instructions are barely employed to accelerate data analytics *within* TEEs, in spite of

their well-known performance gain. Vectorization results in low code complexity since the performance benefit stems from a CPU feature which is already part of the TCB.

Our optimization focuses on two core primitives, Sort and Merge, as they dominate the execution of stream analytics in our observation. Inspired by vectorized sort and merge on x86 [97], [98], we implement the ones with hand-writing ARMv8 NEON vector instructions for SBT. Our sort outperforms the ones in the C/C++ standard libraries by more than  $2\times$ , as will be shown in evaluation. This optimization is vital to the engine's overall performance.

### 2.6 TEE Memory Management

Facing high-velocity streams in a TEE, SBT's memory allocator addresses two challenges: *space efficiency*: it must construct a compact memory layout and reclaim memory timely due to limited physical memory; *lightweight*: the allocator must be simple to suit a low TCB. The challenges disqualify popular engines organizing events in hash tables (e.g. for grouping events by key) and depend on generic memory allocators [46]–[48], [51], [55]. The rationales are two: a hash table's principle that trade space for time mismatches TEE's limited memory; generic allocators are typically heavy due to complex optimization, which adds tens of KSLoC to TCB [99], [100].

SBT offers a special memory management for stream computations: it provides virtually unbounded buffers as the universal memory abstraction ( $\S2.6.1$ ); it places data by using (untrusted) consumption hints and large virtual address space ( $\S2.6.2$ ).

## 2.6.1 Unbounded Array

We device contiguous and virtually unbounded arrays called *uArrays*, the universal data containers used by computations within TEE. uArrays encapsulate all of the data flowing among trusted primitives in a pipeline; they also store operator states conventionally kept in hash tables.

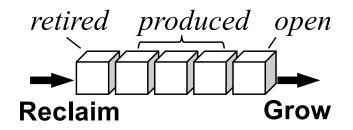

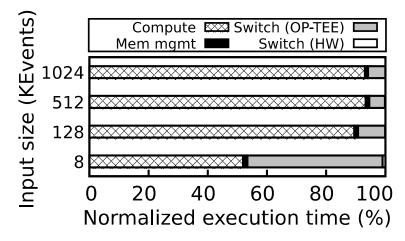

An uArray is an append-only buffer in a contiguous memory region for same-type data objects. The lifecycle of uArray closely map to the producer/consumer pattern in streaming computations. One uArray can be in the following three different states. *Open*: after created,

an uArray grows dynamically as the producer primitive appends data objects to it. *Produced*: when data production is finished, the uArray's end position is finalized; it becomes read-only and no more data can be appended. *Retired*: the uArray is no longer needed and its memory is subject to reclamation. According to their states, the memory allocator places or reclaims uArrays, as will be discussed in Section 2.6.2.

**Types** uArrays fall into different types depending on their scopes and enclosed data. A *streaming uArray* encapsulates data flowing from a producer primitive to a consumer primitive. A *state uArray* encapsulates operator state that outlives the lifespans of individual primitives. A *temporary uArray* live within a trusted primitive's scope.

Low abstraction overhead An uArray transparently grows spanning a contiguous virtual memory region. Its growth is backed by the data plane's on-demand paging which happens entirely inside TEE. Growing an uArray simply necessitates updating an integer index for most of the time. Compared to a manual buffer management, this mechanism allows the compiler to build more compact loops by waiving bounds checking of uArray in computation code. uArrays always grow in place. This contrasts to typical sequence containers (such as C++ std::vector and java.util.ArrayList) that grow transparently but require costly relocation. In Section 2.9, we will experimentally compare uArray against std::vector.

## 2.6.2 Placing uArrays in uGroups

**Co-locating uArrays** The memory allocator co-locates multiple uArrays as an uGroup to reclaim them consecutively. Spanning a contiguous virtual memory region, a uGroup consists of multiple *produced* or *retired* uArrays and optionally an *open* uArray at its end, as shown in Figure 2.5. The grouping is purely physical: it is at the discretion of the allocator, orthogonal to stream computations, and hence transparent to the trusted primitives and the control plane.

As shown in Figure 2.5, the allocator reclaims *consumed* uArrays by always starting from the beginning of an uGroup. When placing a new uArray, the allocator decides whether to create a new uGroup for the uArray, or append the uArray to an existing uGroup. In

Figure 2.5. The uArrays in one uGroup

doing so, the allocator seeks to i) assure that each uGroup holds a sequence of uArrays to be consumed consecutively in the future; ii) minimize the total number of live uGroups, in order to compact TEE memory layout and minimizes the cost in tracking uGroups. To this end, our key is to guide placement with the control plane's data consumption plan, as will be presented below.

**Consumption hints** Upon invoking a trusted primitive T, the control plane may provide two optional hints concerning the future consumption order for the output of T:

• Consumed-in-parallel ( $||_k$ ): the control plane will schedule k worker threads to consume a set of uArrays in parallel.

• Consumed-after  $(b_1 \Leftarrow b_2)$ : the control plane will schedule worker threads for consuming uArray  $b_2$  after uArray  $b_1$ . The consumed-after relation is transitive. uArrays may form multiple consumed-after chains.

The control plane may specify these relations between new output uArrays (yet to be created) and existing uArrays.

**Hint-guided placement** The hints assist the data plane to generate compact memory layout and reclaim memory effectively. Upon allocating a uArray, the allocator examines the existing hints regarding to the uArray.

( $\Leftarrow$ ) prompts the allocator to place the uArrays on the same *consumed-after* chain in the same uGroup. Starting from the new uArray *b* under question, the allocator tracks back on its consumed-after chain, and places *b* after the first uArray that is both in state *produced* (i.e. its growth has finished) and is located at the end of an uGroup. If no such uArray is available on the chain, the allocator creates a new uGroup for *b*.

$(||_k)$  prompts the allocator to place uArrays  $b_{1..k}$  in separate uGroups, so that delay in consuming any of the uArrays will not block the allocator from reclaiming the other uArrays. Our rationale is that despite  $b_{1..k}$  are created at the same time, they are often consumed at different moments in the future: i) since SBT's control plane threads independently fetch new uArrays for processing as they become available (§2.4), the starting moments for processing  $b_{1..k}$  may vary widely, especially when the engine load is high; ii) even when k worker threads start processing  $b_{1..k}$  simultaneously, straggling workers are not uncommon, due to non-determinism of a modern multicore's thread scheduling and memory hierarchy [101].

The impacts of misleading hints SBT detects misleading hints in retrospect through remote attestation ( $\S2.7$ ). Since hints only influence TEE memory placement *policy* on the edge, misleading hints never cause data loss ( $\S2.4.2$ ) or violation of data security and TEE integrity. However, such hints may result in violation of result freshness slowing down analytics.

Managing virtual addresses All uGroups grow *in place* within one virtual address space. To avoid collision and costly relocation, the allocator places them far apart using the huge virtual address space dedicated to a TrustZone TEE. The space is 256TB on ARMv8,  $10,000 \times$  larger than the physical DRAM (a few GBs). As a result, the allocator simply reserves a virtual address range as large as the entire TEE DRAM for each uGroup We will validate such choice in Section 2.9.

## 2.7 Attestation for Correctness and Freshness

SBT collects evidences for cloud consumers to verify two properties: *correctness*, i.e. all ingested data is processed according to the stream pipeline declaration; *freshness*, i.e. the pipeline has low output delays.

The above objective has several notable aspects. i) We verify the behaviors of untrusted control plane, i.e., *which* primitives it invokes on *what* data and at *what* time. We do not verify trusted primitives, e.g. if a Sort primitive indeed produces ordered data. ii) Verifying data lineages at the pipeline's intermediate operators or egress [43], [44] is insufficient to guarantee correctness, i.e. all data ingested so far is processed according to the stream

| Field                                            | Description Length          |            |        |        |         |        |       |      |         |  |

|--------------------------------------------------|-----------------------------|------------|--------|--------|---------|--------|-------|------|---------|--|

| Ts                                               | Data plane timestamp32 bits |            |        |        |         |        |       |      |         |  |

| Op Primitive type, including ingress/egress 16 b |                             |            |        |        |         |        |       |      | oits    |  |

| WinNo Monotonic window sequence number 16 bi     |                             |            |        |        |         |        |       | oits |         |  |

| Data An uArray ID or a watermark value 32 b      |                             |            |        |        |         |        |       | oits |         |  |

| Hint                                             | An c                        | optional c | onsur  | npti   | on hi   | nt     |       | 64 ł | oits    |  |

| Count                                            | Nun                         | nber of da | ta/hir | nt fie | elds tl | nat fo | ollow | 16 ł | 16 bits |  |

| In/Egress                                        | Ор                          | Ts         | Da     | ta     |         |        |       |      |         |  |

| Windowing                                        | Ор                          | Ts         | Da     | ta     | WinNo   | Da     | ata   |      |         |  |

| Execution                                        | Ор                          | Ts         | Cnt    | Da     | ta      | Cnt    | Data  | Cnt  | Hints   |  |

Figure 2.6. Audit records: fields (top) and layout (bottom)

pipeline. iii) The windows of stream computations and watermarks triggering the computations must be attested, which are keys to stream model (§2.2). iv) As the volume of evidences can be substantial, evidences must be compacted to save uplink bandwidth [27], [102].

Therefore, SBT provides the following verification mechanism. Agnostic to the pipeline being executed, the data plane monitors dataflows among primitive instances at the TEE boundary, and then generates audit records. For low overhead, it eschews building data lineages on-the-fly unlike much prior work [39], [43], [103]. The data plane compresses audit records and flushes to the cloud both periodically and upon externalizing any analytics result. We describe details below.

Audit records As being invoked by the control plane, the data plane generates *audit* records. As illustrated in Figure 2.6, the records track i) ingested and externalized uArrays, ii) associations between uArrays and windows, and iii) primitive executions (with optional hints supplied by the control plane) which establish *derived-from* relations among uArrays. The records further include ingested watermark values, which are crucial for determining output delays as will be discussed below. The data plane timestamps all the records. It generates monotonically increasing identifiers for recorded uArrays. We will evaluate the overhead of audit records in Section 2.9.

```

ts= 1 INGRESS data=0xF0

ts= 5 WND data_in=0xF0 win_no=0 data_out=0xF1

ts=10 SORT data_in=0xF1 data_out=0xF3

ts=15 INGRESS data=0xF4 (watermark=100)

ts=25 SUM data_in=0xF3,0xF4 data_out=0xF5

ts=28 WND data_in=0xF0 win_no=1 data_out=0xF6

ts=30 EGRESS data=0xF5

```

Figure 2.7. Sample audit records for the pipeline in Figure 2.2. Format is simplified. ts means processing timestamp.

Attesting analytics correctness The cloud verifier checks if all ingested uArrays flow through the expected trusted primitives. Such dataflows are deterministic given the arrivals of input data (including their windows), the watermarks, and the pipeline declaration. Hence, the verifier replays all ingestion records on its local copy of the same pipeline. It checks if all the records resulting from the replay match the ones reported by the edge (except timestamps). The replay is symbolic without actual computations and hence fast.

Note that the verification works for stateful operators as well. The state of a stream operator (e.g. temporal join) is only determined by all the inputs the operator has ever received. Since the cloud can verify that all the ingested uArrays correctly flow through the expected trusted primitives and thus stream operators, it knows that the operator's current state must be correct, and then all results derived from the operator state must be correct. Attesting result freshness The key for the verifier to calculate the delay of an output result R is to identify the watermark that triggers the externalization of R, according to the delay definition in Section 2.2.2. From the egress record of R, the verifier traces backward following the *derived-from* chain(s) until it reaches an execution record indicating that a watermark W triggers the execution. The verifier looks up the ingress record of W. It calculates the difference between W's ingress time and R's egress time to be the delay of R. Example In Figure 2.7, an uArray with identifier 0xF0 is ingested and segmented into two uArrays (0xF1 and 0xF2) for window 0 and 1 respectively. Sort consumes uArray 0xF1 and produces uArray 0xF3. A watermark with value 100 arrives and completes window 0. Triggered by the watermark, SUM consumes uArray 0xF3 of window 0 and produces uArray 0xF5 as the result of window 0.

The cloud verifier replays the ingress records on its local pipeline copy and learns that uArray 0xF1 is processed adhering to the pipeline declaration while uArray 0xF2 is yet to be processed. It will assert analytics incorrectness if 0xF2 remains unprocessed until a future watermark completes window 1 (not shown). To verify result freshness, the verifier traces result 0xF5 backward to find its trigger watermark 0xF4 and calculates the output delay to be 15 (30 - 15).

**Columnar compression of records** The data plane compresses audit records by exploiting locality within one record field and known data distribution in each field. The data plane produces raw audit records in memory (with the format shown in Figure 2.6) and in a row order, i.e. one record after the other. Before uploading a sequence of records, it separates the record fields (i.e. columns) and applies different encoding schemes to individual columns: i) Huffman encoding for primitive types and data counts, the two columns likely contain skewed values; ii) delta encoding for timestamps, uArray identifiers, and window numbers, which increment monotonically. Our compression is inspired by columnar databases [104]. We will evaluate the efficacy of compression in Section 2.9.

### 2.8 Implementation

We build SBT for ARMv8 and atop OP-TEE [105] (v2.3). SBT reuses most control functions of StreamBox [47], an open-source research stream engine for x86 servers. Yet, as StreamBox mismatches a TEE (§2.4.1), SBT contributes a new architecture and a new data plane. SBT communicates with source sensors and cloud consumers over ZeroMQ TCP transport [106] which is known for good performance. The new implementation of SBT includes 12.4K SLoC.

**Input batch size**, a key parameter of SBT, trades off between delays in executing individual primitives, the rate of TEE entry/exit, and attestation cost. We empirically determine it as 100K events and will evaluate its impact (§2.9).

**Opaque references** for uArrays are 64-bit random integers generated by the data plane. It keeps the mappings from references to uArray addresses in a table, and validates opaque references by table lookup. This incurs minor overhead, as live opaque references are often no more than a few thousands.

### 2.9 Evaluation

We answer the following questions through evaluation:

- Does SBT result in a small TCB? (§2.9.1)

- What is SBT's performance and how is it compared to other engines? What is the overhead? (§2.9.2)

- How do our key designs impact performance (§2.9.3)?

#### 2.9.1 TCB Analysis

**TCB size** Table 2.4 shows a breakdown of the SBT source code. Despite a sophisticated control plane, the data plane only adds 5K SLoC to the TCB. SBT's memory management is in 740 SLoC,  $9\times$  fewer than glibc's malloc and  $20\times$  fewer than jemalloc [100]. The size of data plane is 42.5 KB, a small fraction (16%) of the entire OP-TEE binary.

**TCB interface** The SBT's data plane exports only four entry functions: two for data plane initialization/finalization, one for debugging, and one shared by all 23 trusted primitives. The last function accepts and returns opaque references (§2.4). No state is shared across the protection boundary.