# SCALABLE AND ENERGY-EFFICIENT SIMT SYSTEMS FOR DEEP LEARNING AND DATA CENTER MICROSERVICES

by

Mahmoud Khairy A Abdallah

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana August 2022

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Timothy G. Rogers, Chair

Department of Electrical and Computer Engineering

## Dr. Mithuna S Thottethodi

Department of Electrical and Computer Engineering

### Dr. Milind Kulkarni

Department of Electrical and Computer Engineering

# Dr. David Nellans NVIDIA

# Approved by:

Dr. Dimitrios Peroulis

## ACKNOWLEDGMENTS

I have many people to thank who have supported me during my Ph.D. journey over the last five years. First and foremost, I would like to express my deepest and sincere gratitude to my advisor, Professor Tim Rogers. I really appreciate his expert guidance, meaningful mentorship, constant care, and support throughout my Ph.D.

I thank my committee members, Professor Mithuna S. Thottethodi, Professor Milind Kulkarni, and Dr. David Nellans, for supervising this thesis. Your feedback is integral to improving both the thesis and its constituent works. In particular, I would like to thank David for providing me with incredible technical support, valuable discussions, and countless pieces of critical advice during the LADM project.

I would like to thank my colleagues at AALP group who directly helped me with my research projects and social life, including Mengchi Zhang, Tsung Tai, Akshay Jain, Roland Green, Aaron Barnes, Ahmad Alawneh, Yechen Liu, Abhishek Bhaumick, Cesar Avalos, Junrui Pan, Fanjia Shen, Vadim Nikiforov, Jason Shen, Christin Bose, Ni Kang, and Weili An.

And last but not least, I would like to express my profound gratitude to my family for their unconditional and continued love and support. I am most grateful to my parents and brothers for enabling me to pursue my passion for learning and for being by my side at each step of this journey. I would also like to thank my friends in the Egyptian community at Purdue: Mohamed Zahran, Ashraf Youssef, Mostafa Abdallah, Tarek Ameen, Amr Ebid and my roommates Nour Hendy and Mohamed Saad.

Finally, I would like to acknowledge the funding sources that made my research possible: National Science Foundation, Purdue Graduate Fellowship, and Sandia National Labs.

## PREFACE

The following is a list of my publications that have been incorporated into this dissertation in chronological order:

- Mahmoud Khairy, Jason Shen, Tor M. Aamodt, and Timothy G. Rogers, "Accel-Sim: An Extensible Simulation Framework for Validated GPU Modeling," In The 47th International Symposium on Computer Architecture (ISCA 2020), Virtual Event, May 2020, (Acceptance rate: 77/421 = 18%)

- Mahmoud Khairy, Vadim Nikiforov, David Nellans, and Timothy G. Rogers, "Locality-Centric Data and Threadblock Management for Massive GPUs," In The 53rd IEEE/ACM International Symposium on Microarchitecture (MICRO 2020), Virtual Event, October 2020 (Acceptance rate: 82/422 = 18%)

- Mahmoud Khairy, Ahmad Alawneh, Aaron Barnes, and Timothy G. Rogers, "SIMR: Single Instruction Multiple Request Processing for Energy-Efficient Data Center Microservices", In The 55th IEEE/ACM International Symposium on Microarchitecture (MICRO 2022), Chicago, October 2022 (Acceptance rate: 86/348 = 22%)

# TABLE OF CONTENTS

| LIST ( | OF TAE | BLES                                                                                                         | 11 |

|--------|--------|--------------------------------------------------------------------------------------------------------------|----|

| LIST ( | OF FIG | URES                                                                                                         | 13 |

| ABBR   | EVIATI | IONS                                                                                                         | 16 |

| ABST   | RACT   |                                                                                                              | 18 |

| 1 IN7  | rodu   | CTION                                                                                                        | 20 |

| 1.1    | Challe | enges                                                                                                        | 21 |

|        | 1.1.1  | Inaccurate Out-of-date Academic Simulators                                                                   | 21 |

|        | 1.1.2  | Post-Moore Multi-GPU Multi-Chiplet Scaling                                                                   | 22 |

|        | 1.1.3  | Data Center Energy Efficiency Crisis and Microservices Evolution                                             | 23 |

| 1.2    | My A   | pproach                                                                                                      | 24 |

|        | 1.2.1  | Building for Flexibility and Modularity: An Accurate and Extensible<br>Simulation Framework                  | 25 |

|        | 1.2.2  | Optimizing for Locality: Transparent Multi-GPU Scaling for DL and HPC Workloads                              | 26 |

|        | 1.2.3  | Exploiting Microservices Similarity and Eliminate Redundancy: Single Instruction Multiple Request Processing | 26 |

| 1.3    | Thesis | s Statement                                                                                                  | 27 |

| 1.4    | Contr  | ibutions                                                                                                     | 27 |

| 1.5    | Orgar  | nization                                                                                                     | 29 |

| 2 | ACC | EL-SIM: AN EXTENSIBLE SIMULATION FRAMEWORK FOR VALIDATED |   |

|---|-----|----------------------------------------------------------|---|

|   | GPU | MODELING                                                 | 0 |

|   | 2.1 | Background                                               | 2 |

|   | 2.2 | Accel-Sim Simulation Framework                           | 3 |

|   |     | 2.2.1 Flexible Frontend                                  | 4 |

|   |     | 2.2.2 Flexible and Detailed Performance Model            | 5 |

|   |     | 2.2.3 Tuner and Targeted Microbenchmarks                 | 7 |

|   |     | 2.2.4 Correlator                                         | 8 |

|   |     | 2.2.5 Simulation Rate                                    | 9 |

|   | 2.3 | Workloads                                                | 9 |

|   | 2.4 | Modeling Different GPU Generations                       | 0 |

|   | 2.5 | A Detailed Correlation Analysis                          | 3 |

|   |     | 2.5.1 Overall System Correlation                         | 6 |

|   |     | 2.5.2 Achieved Bandwidth Correlation                     | 0 |

|   |     | 2.5.3 L1 Cache Correlation                               | 1 |

|   |     | 2.5.4 L2 Cache Correlation                               | 2 |

|   |     | 2.5.5 DRAM Correlation                                   | 2 |

|   | 2.6 | Case Studies                                             | 3 |

|   | 2.7 | Summary                                                  | 5 |

| 3 | LAD | M: A SCALABLE AND TRANSPARENT MULTI-GPU SYSTEM FOR DL    |   |

|   | ANI | HPC WORKLOADS    5'                                      | 7 |

| 3.1 | Backg  | ground                                       | 59 |

|-----|--------|----------------------------------------------|----|

|     | 3.1.1  | NUMA Locality in CPUs vs GPUs                | 60 |

|     | 3.1.2  | Existing NUMA-GPU Optimizations              | 62 |

| 3.2 | Locali | ity-Aware Data Management                    | 66 |

|     | 3.2.1  | LADM System Design                           | 66 |

|     | 3.2.2  | Threadblock-centric Locality Patterns        | 68 |

|     | 3.2.3  | Static Locality and Sharing Detection        | 70 |

|     | 3.2.4  | Locality-Aware Scheduling and Page Placement | 73 |

|     |        | LASP Data Placement                          | 73 |

|     |        | LASP Threadblock Scheduling                  | 74 |

|     | 3.2.5  | Compiler-assisted Remote Request Bypassing   | 76 |

| 3.3 | Exper  | rimental Methodology                         | 77 |

|     | 3.3.1  | Simulation Methodology                       | 77 |

|     | 3.3.2  | Workload Selection and Characterization      | 78 |

|     | 3.3.3  | Hardware Validation of LASP Principles       | 79 |

| 3.4 | Exper  | rimental Results                             | 80 |

|     | 3.4.1  | Simulation Results of LADM                   | 80 |

|     | 3.4.2  | Remote Request Bypassing Analysis            | 82 |

| 3.5 | Summ   | nary                                         | 84 |

| 4 | SIN | GLE IN | STRUCTION MULTIPLE REQUEST PROCESSING FOR DATA CEN- |

|---|-----|--------|-----------------------------------------------------|

|   | TEF | R MICR | OSERVICES                                           |

|   | 4.1 | Backg  | round and Motivation                                |

|   | 4.2 | SIMR   | System                                              |

|   |     | 4.2.1  | RPU Hardware                                        |

|   |     |        | CPU vs GPU vs RPU                                   |

|   |     |        | An Examination of SMT vs SIMT                       |

|   |     | 4.2.2  | SIMR Software Stack                                 |

|   |     |        | SIMR-Aware Batching Serve                           |

|   |     |        | Stack Segment Coalescing                            |

|   |     |        | Batch Size Tuning and Memory Contention 102         |

|   |     |        | SIMR-Aware Memory Allocation                        |

|   |     |        | System-Level Batch Splitting 105                    |

|   | 4.3 | Exper  | imental Setup                                       |

|   | 4.4 | Exper  | imental Results                                     |

|   |     | 4.4.1  | Chip-Level Results                                  |

|   |     |        | Sensitivity Analysis                                |

|   |     |        | Service Latency Analysis                            |

|   |     |        | GPU Performance 113                                 |

|   |     | 4.4.2  | System-Level Results                                |

|   | 4.5 | Discussion                                                                   |

|---|-----|------------------------------------------------------------------------------|

|   |     | 4.5.1 RPU vs CPU's SIMD                                                      |

|   |     | 4.5.2 Multi-threaded vs Multi-process Services                               |

|   |     | 4.5.3 Security Implications                                                  |

|   |     | 4.5.4 GPGPU Workloads on RPU                                                 |

|   |     | 4.5.5 RPU vs GPU Terminology                                                 |

|   | 4.6 | Summary 118                                                                  |

| 5 | REL | ATED WORK                                                                    |

|   | 5.1 | GPU Simulation                                                               |

|   | 5.2 | NUMA-aware Management for CPUs and GPUs                                      |

|   | 5.3 | Webservices Acceleration on GPUs 122                                         |

| 6 | CON | ICLUSIONS AND FUTURE WORK 124                                                |

|   | 6.1 | Conclusions                                                                  |

|   |     | 6.1.1 Other Collaboration Work                                               |

|   |     | 6.1.2 Potential Impact                                                       |

|   | 6.2 | Future Research Directions:                                                  |

|   |     | 6.2.1 Enabling Efficient Multi-Trillion Model Training                       |

|   |     | Identifying Bottlenecks with Heterogeneous Memory $\ldots \ldots \ldots 127$ |

|   |     | Model vs Data Parallelism Trade-off                                          |

|   |     | 6.2.2 Phase-Aware Thread Scheduling for Micro-Second-Scale Latency 128       |

| 6.2.3      | Physical Design of RPU with RISC-V Prototyping | 128 |

|------------|------------------------------------------------|-----|

| REFERENCES | 5                                              | 130 |

# LIST OF TABLES

| 2.1 | Landscape of open-source GPU simulation. Accuracy numbers are taken from each simulator's respective publication.                                                                                                                                                                                                                                                 | 32  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | Example demonstrating how mISA instruction traces and vISA instructions trans-<br>late into the ISA-independent intermediate representation used by the perfor-<br>mance model. In traces, the mapping between opcode and execution unit is<br>provided by the <i>ISA def</i> file in Figure 2.1.* <i>indicates these values are computed</i><br>using emulation. | 34  |

| 2.3 | Workloads used in our study. Table 2.8 lists the hardware cycles for each workload.                                                                                                                                                                                                                                                                               | 40  |

| 2.4 | Accel-Sim modeling properties across four different GPU generations. SPU:<br>Single-Precision Floating Point Unit. DPU: Double-Precision Unit. SFU: Special<br>Function Unit.                                                                                                                                                                                     | 41  |

| 2.5 | Accel-Sim cycle error and correlation factor across four different GPU generations.                                                                                                                                                                                                                                                                               | 43  |

| 2.6 | Volta GPU configuration for GPGPU-Sim 3.x vs Accel-Sim. INT: Integer oper-<br>ation unit.                                                                                                                                                                                                                                                                         | 44  |

| 2.7 | Error and correlation rates of GPGPU-Sim 3.x versus Accel-Sim when modeling an NVIDIA Volta.                                                                                                                                                                                                                                                                      | 44  |

| 2.8 | Cycle mean absolute error per workload in GPGPU-sim 3.x, Accel-Sim [PTX Mode] and Accel-Sim for SDK, Rodinia and Parboil                                                                                                                                                                                                                                          | 48  |

| 2.9 | Cycle mean absolute error per workload in GPGPU-sim 3.x, Accel-Sim [PTX Mode] and Accel-Sim for Polybench, Microbenchmark, and CUTLASS                                                                                                                                                                                                                            | 56  |

| 3.1 | LADM vs state-of-the-art techniques                                                                                                                                                                                                                                                                                                                               | 62  |

| 3.2 | Index analysis and taken actions. $bx = blockIdx.x$ , $by = blockIdx.y$ , $gDimx = gridDim.x$ , m is an induction variable. For the <i>loopInvariant</i> function, if one of $bx$ or $by$ is not listed, then none of the terms in the equation contain that variable. For the <i>loopVariant</i> function, if $gDimx$ is not listed, then none of the terms in   |     |

|     | the equation contain $gDimx$                                                                                                                                                                                                                                                                                                                                      | 69  |

| 3.3 | Multi-GPU Configuration                                                                                                                                                                                                                                                                                                                                           | 79  |

| 3.4 | Workloads used to evaluate LADM in simulation.                                                                                                                                                                                                                                                                                                                    | 79  |

| 4.1 | CPU vs RPU vs GPU Key Metrics                                                                                                                                                                                                                                                                                                                                     | 87  |

| 4.2 | CPU vs RPU vs GPU Architecture Differences                                                                                                                                                                                                                                                                                                                        | 95  |

| 4.3 | CPU inefficiencies in the data center                                                                                                                                                                                                                                                                                                                             | 96  |

| 4.4 | CPU vs RPU Simulated Configuration                                                                                                                                                                                                                                                                                                                                | 108 |

| 4.5 | Per-component area and peak power estimates                                                                                                                                                                                                                                                                                                                       | 109 |

| 4.6 | GPU vs RPU Terminology |  |  | • |  |  |  | • | • | • | • |  |  | • | • |  |  | • |  | • |  |  |  | • |  | • |  | • | 11 | 8 |

|-----|------------------------|--|--|---|--|--|--|---|---|---|---|--|--|---|---|--|--|---|--|---|--|--|--|---|--|---|--|---|----|---|

|-----|------------------------|--|--|---|--|--|--|---|---|---|---|--|--|---|---|--|--|---|--|---|--|--|--|---|--|---|--|---|----|---|

# LIST OF FIGURES

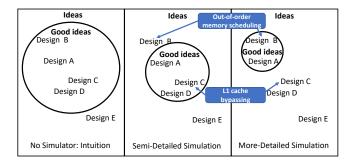

| 1.1 | The architecture design and simulation process represented as a collection of good and ineffective ideas. As the level of simulation detail increases, the space of effective ideas shrinks and potentially moves.                     | 22 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

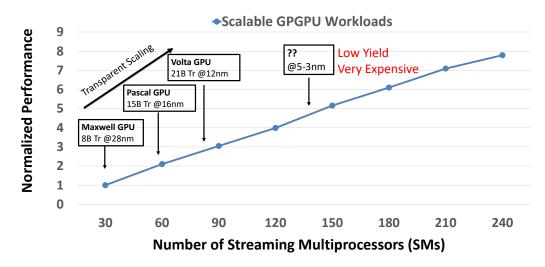

| 1.2 | Performance of GPU workloads in a hypothetical monolithic GPU, where all resources scale proportionally.                                                                                                                               | 23 |

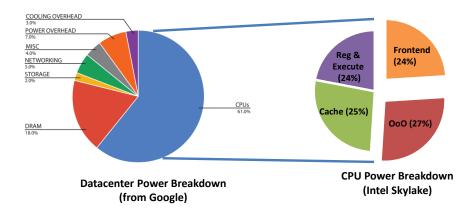

| 1.3 | Data center power consumption breakdown. Source: $[11]$ – $[13]$                                                                                                                                                                       | 24 |

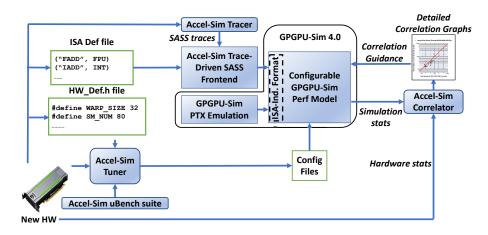

| 2.1 | Accel-Sim's end-to-end flow.                                                                                                                                                                                                           | 34 |

| 2.2 | Updated GPGPU-Sim 4.0 performance model                                                                                                                                                                                                | 36 |

| 2.3 | L1 latency microbenchmark                                                                                                                                                                                                              | 37 |

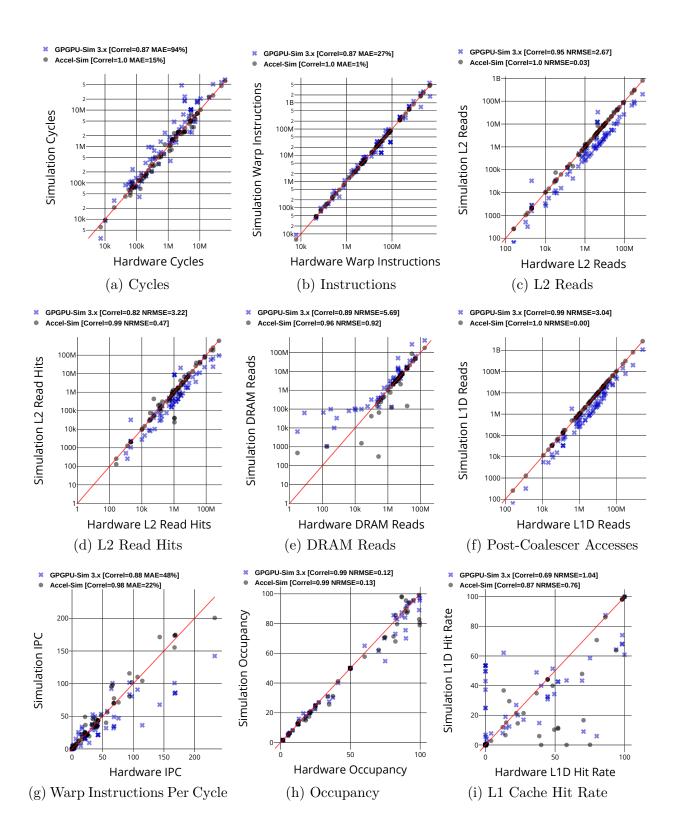

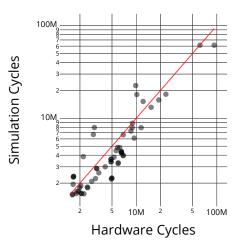

| 2.4 | Correlation of key metrics from Accel-Sim versus GPGPU-Sim 3.x over the 80 workloads. These workloads are listed in Tables 2.8 and 2.9                                                                                                 | 45 |

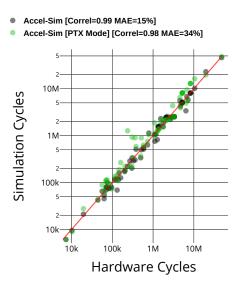

| 2.5 | Cycle correlation of Accel-Sim in execution-driven PTX mode versus Accel-Sim in trace-driven SASS mode                                                                                                                                 | 46 |

| 2.6 | Accel-Sim cycle correlation when executing deepbench workloads, which cannot be executed by GPGPU-Sim 3.x or Accel-Sim [PTX Mode]. 60 workloads (comprised of 11,440 kernel instances).                                                | 47 |

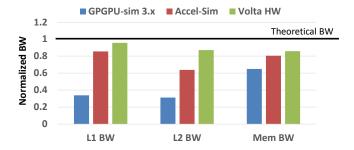

| 2.7 | Measured cache and memory bandwidth for Accel-sim, GPGPU-sim 3.x and Volta hardware                                                                                                                                                    | 51 |

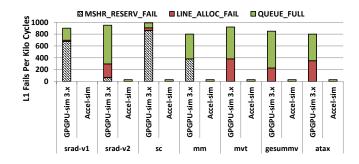

| 2.8 | L1 cache reservation fails per kilo cycles for cache sensitive workloads in both Accel-Sim and GPGPU-sim 3.x.                                                                                                                          | 54 |

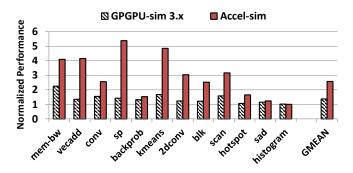

| 2.9 | FR_FCFS performance normalized to the FCFS in Accel-Sim and GPGPU-<br>sim 3.x for memory intensive workloads in Volta.                                                                                                                 | 54 |

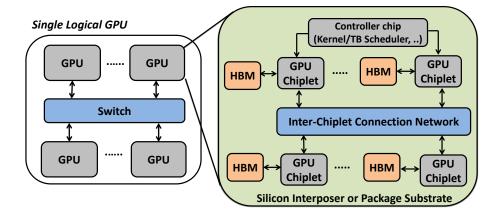

| 3.1 | Future massive logical GPU containing multiple discrete GPUs, which are themselves composed of chiplets in a hierarchical interconnect.                                                                                                | 58 |

| 3.2 | OpenMP vs CUDA thread mapping for sgemm [74]                                                                                                                                                                                           | 61 |

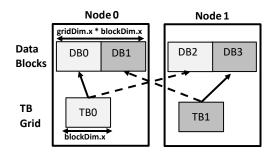

| 3.3 | Behavior of kernel-wide partitioning in a 2-node system with 2 threadblocks that access a 4 datablock data structure with a stride of one datablock                                                                                    | 63 |

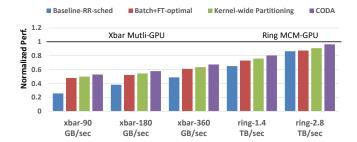

| 3.4 | Bandwidth sensitivity analysis of state-of-the-art techniques normalized to a hypothetical monolithic GPU with the same number of SMs. Performance is averaged over the applications listed in Section 3.3.1.                          | 65 |

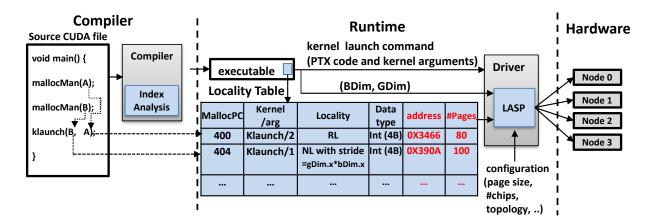

| 3.5 | End-to-end overview of our proposed Locality-Aware Data Management Sys-<br>tem. In the locality table: MallocPC, the kernel/arg tuple, the locality type<br>and data type are filled statically, whereas memory address and #pages are |    |

|     | filled dynamically.                                                                                                                                                                                                                    | 66 |

| 3.6  | Matrix multiplication indices analysis                                                                                                                                       | 67  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

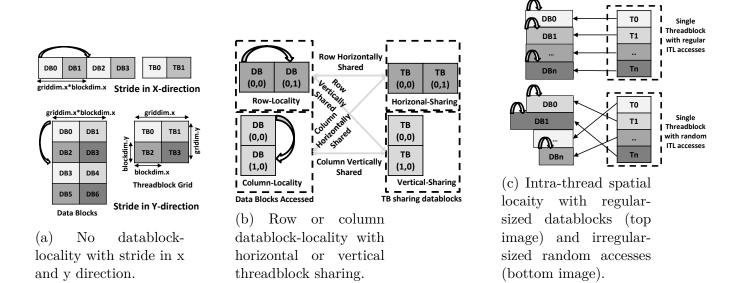

| 3.7  | Common locality types found in GPU workloads. Arrows indicate threadblock motion and datablocks are shaded based on the shade of the threadblock (TB) that accesses them.    | 68  |

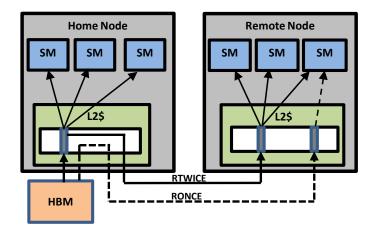

| 3.8  | llustration of existing NUMA caching policy <i>cache-remote-twice</i> (the solid line) and our proposed <i>cache-remote-once</i> cache management strategy (the dashed line) | 76  |

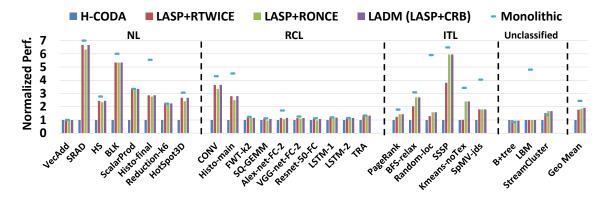

| 3.9  | Performance of H-CODA, LASP with RTWICE and RONCE, LADM and hypothetical monolithic GPU. The data are normalized to H-CODA performance.                                      | 81  |

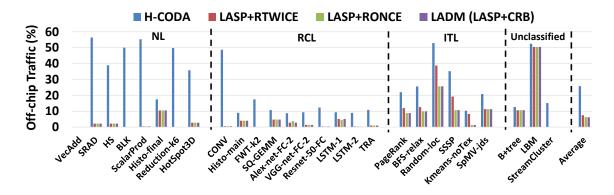

| 3.10 | Percentage of total memory traffic that goes off-node for H-CODA vs LASP vs LADM.                                                                                            | 81  |

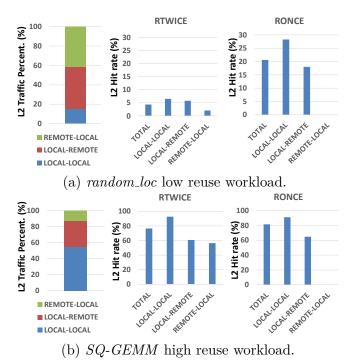

| 3.11 | Case study of RONCE cache policy effectiveness on high and low reuse work-loads                                                                                              | 83  |

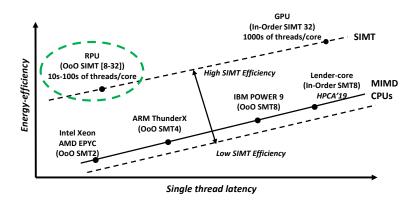

| 4.1  | Conceptual energy-efficiency vs. single thread latency for different compute<br>unit design points                                                                           | 86  |

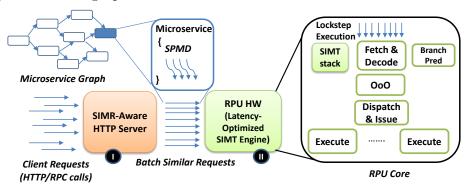

| 4.2  | High level view of our SIMR system.                                                                                                                                          | 86  |

| 4.3  | Social network microservice graph studied in this work, similar to $[27]$                                                                                                    | 88  |

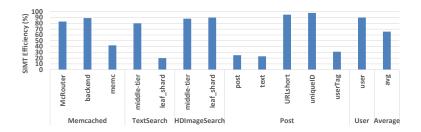

| 4.4  | SIMT control efficiency of naive batching for some microservices                                                                                                             | 89  |

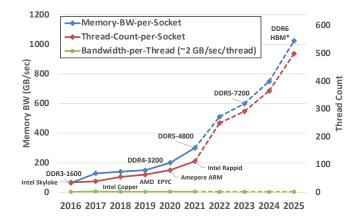

| 4.5  | Off-chip DRAM BW and Thread per socket scaling.                                                                                                                              | 90  |

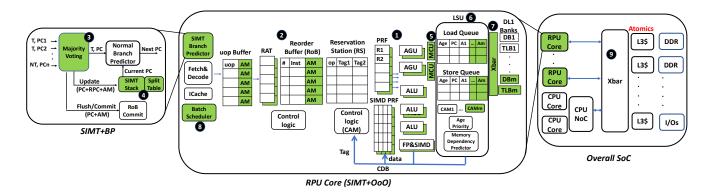

| 4.6  | RPU hardware overview. Changes to the OoO core needed to support SIMR execution are highlighted in green                                                                     | 91  |

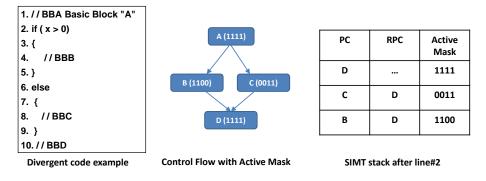

| 4.7  | IPDOM analysis with HW SIMT stack                                                                                                                                            | 92  |

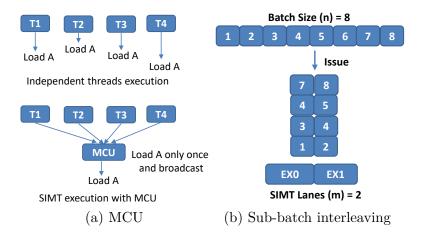

| 4.8  | MCU and sub-batch interleaving to improve memory efficiency and hiding front-end latency respectively                                                                        | 94  |

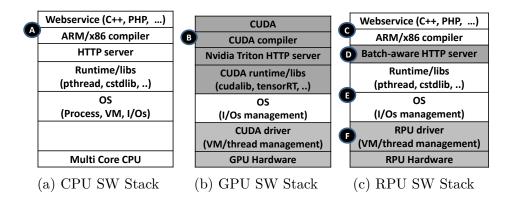

| 4.9  | Hardware/Software Stack of CPU vs GPU vs RPU for microservices program-<br>ming                                                                                              | 98  |

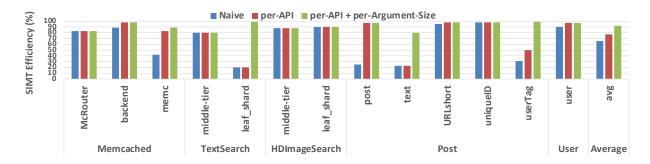

| 4.10 | SIMT control flow efficiency with different request batching policies (Batch Size = $32$ )                                                                                   | 99  |

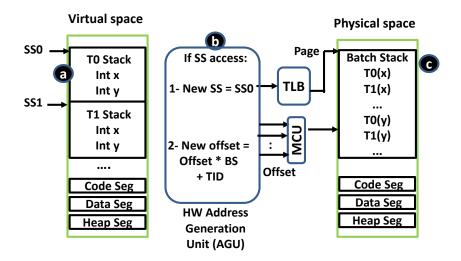

| 4.11 | Stack Segment (SS) coalescing (physical stack page size = virtual page size * batch size) with 4-byte interleaving.                                                          | 101 |

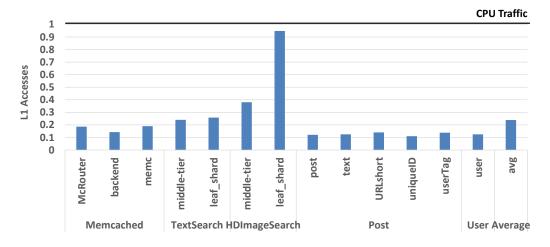

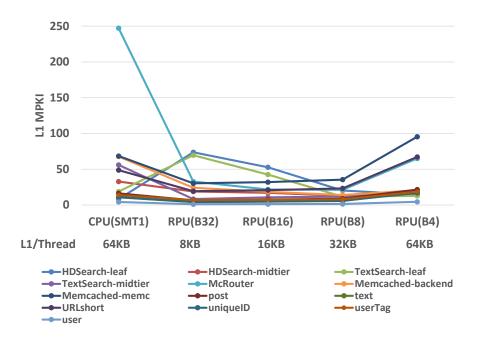

| 4.12 | RPU L1 accesses, normalized to CPU accesses                                                                                                                                  | 102 |

| 4.13 | L1 MPKI of a single threaded CPU vs RPU with different batch sizes (32, 16, 8, 4)                                                                                            | 103 |

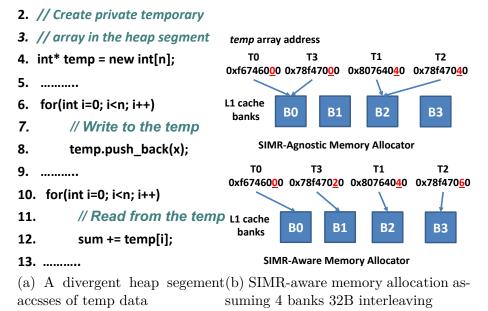

| 4.14 | SIMR-aware memory allocator.                                                                                                                                                 | 104 |

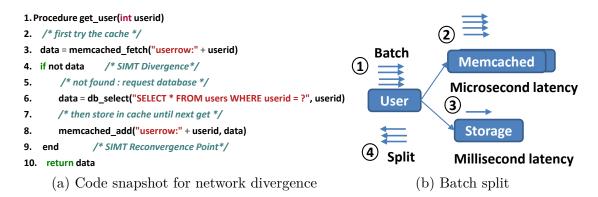

| 4.15 | Batch split technique for control flow divergence when a path contains long network/storage blocking event. | 105 |

|------|-------------------------------------------------------------------------------------------------------------|-----|

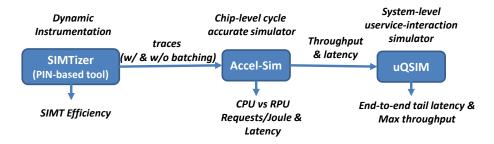

| 4.16 | End-to-End Experimental Setup                                                                               | 107 |

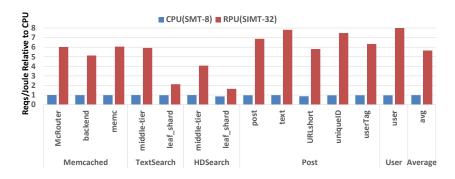

| 4.17 | RPU and CPU-SMT8 energy efficiency (Requests/Joule) relative to single threaded CPU (higher is better)      | 111 |

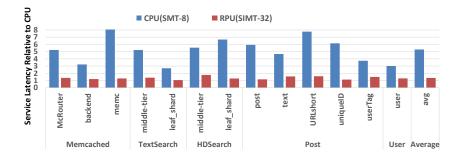

| 4.18 | RPU and CPU-SMT8 service latency relative to single threaded CPU (lower is better)                          | 111 |

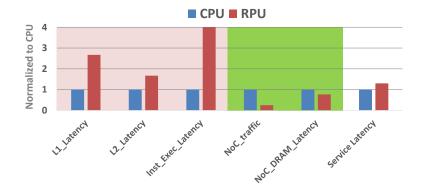

| 4.19 | Metrics that contribute to total service latency.                                                           | 113 |

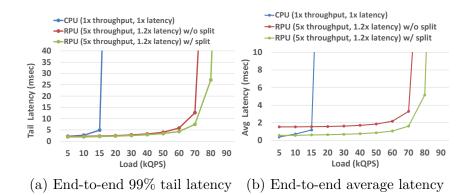

| 4.20 | End-to-end tail and average latency for CPU-based system vs RPU-based system with and without batch split.  | 114 |

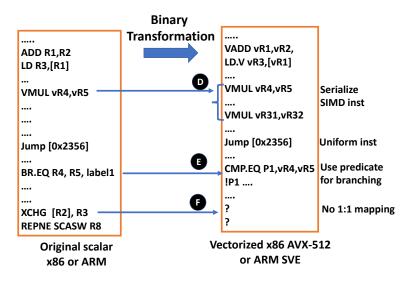

| 4.21 | Potential binary transformation of a scalar binary to a vector version                                      | 115 |

# ABBREVIATIONS

| GPU                  | Graphics Processing Unit                    |

|----------------------|---------------------------------------------|

| GPGPU                | General Purpose on Graphics Processing Unit |

| LADM                 | Locality Aware Data Management              |

| SIMT                 | Single Instruction, Multiple Thread         |

| SIMR                 | Single Instruction, Multiple Request        |

| MIMD                 | Multiple-Instruction, Multiple-Data         |

| SIMD                 | Single-Instruction, Multiple-Data           |

| SMT                  | Simultaneous MultiThreading                 |

| RPU                  | Request Processing Unit                     |

| CPU                  | Central Processing Unit                     |

| HPC                  | High Performance Computing                  |

| ML                   | Machine Learning                            |

| DL                   | Deep Learning                               |

| AI                   | Artificial Intelligence                     |

| IoT                  | Internat of Things                          |

| NUMA                 | Non Uniform Memory Access                   |

| SM                   | Streaming Multiprocessor                    |

| L1                   | Level One                                   |

| L2                   | Level Two                                   |

| L3                   | Level Three                                 |

| L1D                  | Level One Data                              |

| MSHR                 | Miss Status Holding Register                |

| GDDR                 | Graphic Dual Data Rate                      |

| DRAM                 | Dynamic Random Access Memory                |

| HBM                  | High Bandwidth Memory                       |

| BW                   | Bandwidth                                   |

| $\operatorname{CSR}$ | Compressed Sparse Row                       |

| PDOM                 | Post Dominator                              |

- API Application Programming Interface

- TDP Thermal Design Point

- FLOPS Floating point Operations Per Second

- GB/sec Giga Byte Per Second

- QoS Quality of Service

## ABSTRACT

Moore's law is dead. The physical and economic principles that enabled an exponential rise in transistors per chip have reached their breaking point. As a result, High-Performance Computing (HPC) domain and cloud data centers are encountering significant energy, cost, and environmental hurdles that have led them to embrace custom hardware/software solutions. Single Instruction Multiple Thread (SIMT) accelerators, like Graphics Processing Units (GPUs), are compelling solutions to achieve considerable *energy efficiency* while still preserving *programmability* in the twilight of Moore's Law.

In the HPC and deep learning (DL) domain, the death of single-chip GPU performance scaling will usher in a renaissance in multi-chip Non-Uniform Memory Access (NUMA) scaling. Advances in silicon interposers and other inter-chip signaling technology will enable single-package systems, composed of multiple chiplets that continue to scale even as per-chip transistors do not. Given this evolving, massively parallel NUMA landscape, the placement of data on each chiplet, or discrete GPU card, and the scheduling of the threads that use that data is a critical factor in system performance and power consumption.

Aside from the supercomputer space, general-purpose compute units are still the main driver of data center's total cost of ownership (TCO). CPUs consume 60% of the total data center power budget, half of which comes from the CPU pipeline's frontend. Coupled with the hardware efficiency crisis is an increased desire for programmer productivity, flexible scalability, and nimble software updates that have led to the rise of software microservices. Consequently, single servers are now packed with many threads executing the same, relatively small task on different data.

In this dissertation, I discuss these new paradigm shifts, addressing the following concerns: (1) how do we overcome the non-uniform memory access overhead for next-generation multi-chiplet GPUs in the era of DL-driven workloads?; (2) how can we improve the energy efficiency of data center's CPUs in the light of microservices evolution and request similarity?; and (3) how to study such rapidly-evolving systems with an accurate and extensible SIMT performance modeling? To this end, I propose three different frameworks and systems to address these challenges. First, to improve the quality of GPU research produced by the academic community, I have developed, *Accel-Sim*, a new GPU simulation framework to help solve the problem of keeping simulators up-to-date with contemporary designs. Using a counter-by-counter validation of the GPU memory system, Accel-Sim decreases cycle error from 94% in state-of-the-art simulation to 15%.

Second, to maintain GPU performance scalability in the twilight of Moore's Law, I propose a programmer-transparent Locality-Aware Data Management (LADM) system designed to operate on massive logical GPUs composed of multiple discrete devices, which are themselves composed of chiplets. LADM has two key components: a threadblock-centric compiler-assisted index analysis, and runtime system that performs adaptive data placement, threadblock scheduling and cache insertion policy. Compared to state-of-the-art multi-GPU scheduling, LADM reduces inter-chip memory traffic by  $4 \times$  and capturing 82% of the unbuildable monolithic chip performance.

Third, to exploit the similarity in contemporary microservices, I propose a new class of computing hardware, the Request Processing Unit (RPU), which modifies out-of-order CPU cores to execute microservices using a Single Instruction Multiple Request (SIMR) execution model. Our solution leverages the CPU's programmability and latency optimizations while still exploiting the GPUs' SIMT efficiency and memory model scalability. By using the lock-step execution of concurrent requests, RPU reduces the size and access frequency to the out-of-order frontend and memory system. Our resulting RPU system processes  $5.6 \times$  more Requests/Joule than multi-core CPUs while maintaining acceptable service latency and keeping the traditional microservices software stack unchanged.

## 1. INTRODUCTION

Single Instruction Multiple Thread (SIMT) hardware, like Graphics Processing Units (GPUs), has been widely adopted in many areas, including graphics, High-Performance Computing (HPC), and Deep Learning (DL). The Single Program Multiple Data (SPMD) pattern available in these workloads makes them amenable to lock-step execution on SIMT hardware, as threads execute the same program code and exhibit similar control flow. Moreover, these workloads show regular memory behavior, which increases memory coalescing opportunities. These program characteristics have led to significant performance and energy efficiency gains when they are ported to SIMT-based hardware, like GPUs. Thus, there is no wonder that a large portion of supercomputers found in the Top500 list relies on GPUs [1], [2]. *However, GPU performance scalability is at risk!* Building a larger GPU with dozens of GPU cores in one monolithic chip may not be possible due to low manufacture yield and high cost of building huge chips at small technology nodes [3].

Aside from supercomputer and HPC space, modern data centers exhibit massive degrees of *similar* request-level parallelism in which they receive a significant amount of independent requests from millions of users running the same service code. Further, the shift toward microservice and nanoservice-based architecture makes the control flow among these requests less divergent and reduces the cache footprint per node. Current CPUs run these requests independently on multi-core and do not exploit this similarity and finer granularity of microservices. These microservice requests follow the Single Program Multiple Data pattern with rich inter-request data sharing that can be efficiently leveraged on SIMT hardware. However, current SIMT hardware, like GPUs, is unsuitable for microservice as they optimize throughput over latency, making them ill-suited to meet the QoS requirement, and force the programmer to rewrite the microservices in GPGPU programming language (e.g., CUDA/OpenCL), hindering software productivity. Therefore, I argue for a new class of SIMT hardware that can take advantage of the latency-optimizations and programmability of the CPUs while still exploiting the SIMT efficiency and memory model scalability of the GPUs. In other words: "*Let's bring the SIMT Efficiency to the CPU world!*".

#### 1.1 Challenges

In this dissertation, I aim to address the following three challenges.

#### 1.1.1 Inaccurate Out-of-date Academic Simulators

In computer architecture, significant innovation frequently comes from industry. However, the simulation tools used by industry are often not released for open use, and even when they are, the exact details of industrial designs are not disclosed. As a result, research in the architecture space must ensure that assumptions about contemporary processor design remain true. Figure 1.1 illustrates, simulation inaccuracy can lead to the retention of design proposals with overestimated benefits, or the rejection of design proposals with underestimated benefits. In one scenario promising ideas are throw out prematurely leading to less optimal solutions. In the other scenario, ineffective ideas are retained longer than necessary, leading to wasted time and effort during the architecture design process. Therefore, research cannot look ahead, if its baseline assumptions are too far behind.

To keep up with industry, state-of-the-art academic and public research must both be aware of and adapt to changes in contemporary designs. In the computer architecture space, keeping up with proprietary industrial machines is a challenge. This is a problem in all segments of the processor industry, but perhaps a more acute challenge in the programmable SIMT accelerator space, where the rapid scaling of parallelism, introduction of new processing pipelines (i.e. Tensor Cores [4]) and undocumented changes to both the microarchitecture and *Instruction Set Architecture* (ISA) are commonplace in each new product generation. GPU architectures have widely embraced the use of a virtual ISA (vISA), which provides hardware vendors with tremendous flexibility to make machine ISA (mISA) changes while still maintaining binary compatibility. Vendors like NVIDIA keep the operation of these ISAs private, while others like AMD document each new machine ISA, but freely make drastic changes which open-source simulators must then implement.

This situation presents three separate, but related challenges: (1) How do academic researchers quickly simulate a new, often undocumented ISA every year and a half? (2) Once functionally correct, how are changes to the architecture detected and modeled? (3)

**Figure 1.1.** The architecture design and simulation process represented as a collection of good and ineffective ideas. As the level of simulation detail increases, the space of effective ideas shrinks and potentially moves.

What is a sustainable, rigorous validation mechanism to ensure that new baselines are still tracking industrial designs?

#### 1.1.2 Post-Moore Multi-GPU Multi-Chiplet Scaling

GPU accelerated workloads are commonly used in deep learning and exascale HPC computing systems [5], [6]. These workloads exhibit high levels of implicit parallelism, which transparently enables performance scalability, but only if GPUs can continue to scale their hardware resources into the future. Over the past decade GPUs have more than quadrupled the number of Streaming Multiprocessors (SMs) in their designs, while simultaneously increasing their on-chip transistors by an order of magnitude. Figure 1.2 shows the anticipated performance of balanced GPU resource scaling (Streaming Multiprocessor (SM), SM-interconnect bandwidth, registers, caches, and DRAM bandwidth) if all components can be equally scaled into the future. While the expected performance is appealing, building a GPU with hundreds of SMs in a single monolithic GPU will not be possible due to low manufacturing yields and the high cost of building large chips at small technology nodes [3], [7].

To overcome these problems and enable continuous performance scaling beyond the bounds of Moore's law [8], [9], researchers have proposed increasing GPU transistor count by both aggregating multiple GPUs together (coordinated as a single virtual GPU), as well as dissagregating single-GPUs into scalable multi-chip-module designs [3], [10]. In both ap-

**Figure 1.2.** Performance of GPU workloads in a hypothetical monolithic GPU, where all resources scale proportionally.

proaches, to maintain the existing single GPU programming model and support transparent scaling for current CUDA programs, the architecture and runtime systems must coordinate to hide the fact that a single programmer visible GPU may be comprised of several different GPU NUMA domains. Maintaining this illusion enables rapid software development on small local GPU resources while enabling scalable performance on larger and more complex GPU interconnect topologies. Consequently, transparently overcoming NUMA effects will be one of the largest problems facing GPUs in both these integration domains over the next decade.

#### 1.1.3 Data Center Energy Efficiency Crisis and Microservices Evolution

The growth of hyperscale data centers has steadily increased in the last decade, and is expected to continue in the coming era of Artificial Intelligence and the Internet of Things [14]. However, the slowing of Moore's Law [9] has resulted in energy [15], environmental [16], [17] and supply chain [18] issues. It is anticipated that, by 2030, the data centers will consume about 10% of the total electricity demand [19]. These all have lead data centers to embrace custom hardware/software solutions [20], [21].

While improving Deep Learning (DL) inference has received significant attention [20], [22], general purpose compute units are still the main driver of a data center's total cost

Figure 1.3. Data center power consumption breakdown. Source: [11]–[13]

of ownership (TCO). Figure 1.3 demonstrates that CPUs consume 60% of the data center power budget [11], half of which comes from the pipeline's frontend (i.e. fetch, decode and Out-of-Order (OoO) structures) [12], [13], [23]–[25]. Therefore; 30% of the data-center's total energy is spent on CPU instruction supply.

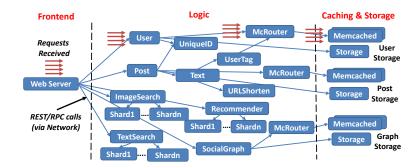

Coupled with the hardware efficiency crisis is an increased desire for programmer productivity, flexible scalability and nimble software updates that has lead to the rise of software microservices. Monolithic server software has been largely replaced with a collection of micro and nanoservices that interact via the network [26]–[28]. Compared to monolithic services, microservices spend much more time in network processing [27], [29], have a smaller instruction and data footprint [27], and can suffer from excessive context switching due to frequent network blocking [26], [30]–[32]. Microsecond scale network latencies cannot be hidden by course-grained OS context switching [33], requiring more threads on each core to support higher throughput [34], [35], under tight single-thread latency constraints.

#### 1.2 My Approach

In this subsection, I discuss my proposed approaches to overcome and solve the previous hurdles.

## 1.2.1 Building for Flexibility and Modularity: An Accurate and Extensible Simulation Framework

To help bridge the gap between opaque industrial innovation and public research, I introduce three mechanisms that make it much easier for GPU simulators to keep up with industry. First, I introduce a new GPU simulator frontend that minimizes the effort required to simulate different machine ISAs through trace-driven simulation of NVIDIA's native machine ISA, while still supporting execution-driven simulation of the virtual ISA. Second, I extensively modify GPGPU-Sim's performance model to increase the level of detail, configurability and make hardware validation easier. Along with the detailed statistics available in simulation, the updated model outputs a set of performance counters that have 1:1 analogs with profiling data generated by contemporary GPU profilers. Finally, surrounding the new simulator and flexible performance model is an infrastructure that enables quick, detailed validation. A comprehensive set of microbenchmarks and automated correlation plotting make performance model validation an automated process.

I use these three new mechanisms to build *Accel-Sim*, an accurate, detailed simulator capable of modeling the performance of contemporary GPUs with 80.2% less error than state-of-the-art, open-source simulators over a wide range of 78 workloads, consisting of 2221 kernel instances. I further demonstrate that Accel-Sim is able to simulate benchmark suites that no other open-source simulator can. In particular, I demonstrate Accel-sim's ability to execute 27 workloads, comprised of 2328 kernel instances, from the machine learning benchmark suite Deepbench. Deepbench makes use of closed-source, hand-tuned kernels with no virtual ISA implementation. To demonstrate Accel-Sim's flexibility and extensibility, I model and validate Accel-Sim against four different NVIDIA GPU generations. Accel-Sim is the only open-source simulator to support contemporary SASS simulation.

Finally, to highlight the effects of falling behind industry, this thesis presents two casestudies that demonstrate how incorrect baseline assumptions can hide new areas of opportunity and lead to potentially incorrect design decisions.

# 1.2.2 Optimizing for Locality: Transparent Multi-GPU Scaling for DL and HPC Workloads

In order to maintain GPU performance scalability for deep learning and HPC workloads, I propose a programmer-transparent *Locality-Aware Data Management* (LADM) system designed to operate on massive logical GPUs composed of multiple discrete devices, which are themselves composed of chiplets. LADM has three key components: a threadblock-centric index analysis, a runtime system that performs data placement and threadblock scheduling, and an adaptive cache insertion policy. The runtime combines information from the static analysis with topology information to proactively optimize data placement, threadblock scheduling, and remote data caching, minimizing off-chip traffic. Compared to state-ofthe-art multi-GPU scheduling, LADM reduces inter-chip memory traffic by  $4\times$  and improves system performance by  $1.8\times$  on a future multi-GPU system.

## 1.2.3 Exploiting Microservices Similarity and Eliminate Redundancy: Single Instruction Multiple Request Processing

Contemporary data center servers process thousands of similar, independent requests per minute. In the interest of programmer productivity and ease of scaling, workloads in data centers have shifted from single monolithic processes on each node toward a micro and nanoservice software architecture. As a result, single servers are now packed with many threads executing the same, relatively small task on different data.

State-of-the-art data centers run these microservices on multi-core CPUs. However, the flexibility offered by traditional CPUs comes at an energy-efficiency cost. The Multiple Instruction Multiple Data execution model misses opportunities to aggregate the similarity in contemporary microservices. I observe that the Single Instruction Multiple Thread execution model, employed by GPUs, provides better thread scaling and has the potential to reduce frontend and memory system energy consumption. However, contemporary GPUs are illsuited for the latency-sensitive microservice space.

To exploit the similarity in contemporary microservices, while maintaining acceptable latency, I propose the Request Processing Unit (RPU). The RPU combines elements of traditional out-of-order CPUs with lockstep thread aggregation mechanisms found in GPUs to execute microservices in a Single Instruction Multiple Request (SIMR) fashion. To complement the RPU, I also propose a SIMR-aware software stack that uses novel mechanisms to batch requests based on their predicted control-flow, split batches based on predicted latency divergence and map per-request memory allocations to maximize coalescing opportunities. My resulting RPU system processes  $5.6 \times$  more Requests/Joule than multi-core CPUs, while maintaining acceptable service latency

#### **1.3** Thesis Statement

My thesis statement, hence, is as follows:

SIMT-based accelerators, like GPUs and my proposed RPUs, are promising solutions to achieve significant energy efficiency while still preserving programmability in the twilight of Moore's Law. I propose three approaches to build next-generation scalable and energy-efficient SIMT systems: (1) detect and optimize for each type of locality exist in the DL and HPC workloads to overcome NUMA effects and reduce off-chip communication between multichiplet GPUs, (2) exploit microservices execution similarity and eliminate redundancy to improve data center energy efficiency, and (3) build extensible and validated SIMT simulation tools to keep-up with industrial changes.

#### 1.4 Contributions

This dissertation makes the following contributions:

It introduces Accel-Sim, a simulation framework explicitly designed to make modeling and validating future GPUs easier. By utilizing a flexible frontend, capable of switching between execution-driven vISA simulation and trace-driven mISA simulation, I am able to simulate hand-tuned machine code from NVIDIA binaries without giving up the option to perform execution-driven simulation when appropriate. I demonstrate Accel-Sim's flexibility by modeling GPUs from Kepler to Turing.

- It performs a rigorous, counter-by-counter comparison of my new performance model against state-of-the-art simulation when modeling an NVIDIA Volta card, reducing error by 79 percentage points. Through this analysis, we uncover and model several previously undocumented architectural features in contemporary GPUs.

- It introduces a comprehensive set of validation infrastructure that includes: a set of targeted GPU microbenchmarks, an automated parameter tuner and an automatic correlation visualizer, useful for adapting Accel-Sim to model new designs quickly.

- It performs a set of case-studies to concretely demonstrate the effects of falling behind industry and uses Accel-Sim to suggest future areas of new research for GPUs.

- It performs a detailed analysis of the locality types present in GPU programs and show that no state-of-the-art NUMA-GPU system can exploit them all. I propose LADM, which uses static index analysis to inform runtime data placement, threadblock scheduling, and remote caching decisions by exploiting a new logical abstraction called the *GPU datablock*.

- It leverages this automatic analysis to perform threadblock and datablock co-placement within hierarchical GPUs. By pre-calculating an optimized data layout in the compiler, LADM can orchestrate prefetching that negates on-demand page-faulting effects and adjust the threadblock schedule based on dynamic data structure sizes.

- Building on my program analysis, I architect a novel compiler-informed cache organization that selectively inserts requests into each L2 cache partition based on the memory request's origin relative to the data's home node and its likelihood for reuse. By understanding the expected reuse patterns for datablocks, LADM's cache hierarchy minimizes both inter-GPU and inter-chiplet bandwidth, the primary factor influencing the scalability of future GPUs.

- It performs the first SIMT-efficiency characterization of microservices using their native CPU binaries. I demonstrate that, given the right batching mechanisms, microservices execute efficiently on SIMT hardware.

- It proposes a new hardware architecture, the Request Processing Unit (RPU). The RPU improves the energy-efficiency and thread-density of contemporary OoO CPU cores by exploiting the similarity between concurrent microservice requests. With a high SIMT efficiency, the RPU captures the single-threaded advantages of OoO CPUs, while increasing Requests/Joule.

- It proposes a novel software stack, co-designed with the RPU hardware that introduces SIMR-aware mechanisms to compose/split batches, tune SIMT width, and allocate memory to maximize coalescing.

- On a diverse set of 13 CPU microservices, I demonstrate that the RPU improves Requests/Joule by an average of 5.6x versus OoO single threaded and SMT CPU cores, while maintaining acceptable end-to-end latency.

#### 1.5 Organization

The rest of this dissertation is organized as follows:

- Chapter 2 introduces Accel-Sim, a new GPU simulation framework that helps solve the problem of keeping simulators up-to-date with contemporary designs. I show how the proposed simularot is extensible, accurate and validated to various GPU generation found today in the market.

- Chapter 3 details, Locality-Aware Data Management (LADM), a transparent and scalable system designed to operate on massive logical GPUs composed of multiple discrete devices, which are themselves composed of chiplets.

- Chapter 4 performs SIMT-efficiency characterization of microservices and proposes Single Instruction Multiple Request system, a hardware-software co-design to exploit request similarity in the data centers.

- Chapter 5 discusses related work.

- Chapter 6 concludes the dissertation and discusses directions for potential future work.

# 2. ACCEL-SIM: AN EXTENSIBLE SIMULATION FRAMEWORK FOR VALIDATED GPU MODELING

In computer architecture, significant innovation frequently comes from industry. However, the simulation tools used by industry are often not released for open use, and even when they are, the exact details of industrial designs are not disclosed. As a result, research in the architecture space must ensure that assumptions about contemporary processor design remain true. We present a new simulation framework, Accel-Sim, that is designed to address this challenge.

Accel-Sim introduces a flexible frontend, that enables it to operate in either trace- or execution-driven mode. Accel-Sim includes a trace-generation tool (built using the NVBit [36] binary instrumentation tool), that produces machine ISA instruction traces from any CUDA binary, including those that use closed-source libraries, like cuDNN [37]. These machine ISA traces are then converted into an ISA-independent intermediate representation that is input to the performance model. The trace-driven frontend allows Accel-Sim to simulate the machine ISA in new cards without implementing the ISA's functional model and increases the accuracy of the simulator over executing the virtual ISA. However, trace-based simulation has its drawbacks. Evaluating new designs that rely on the data values stored in registers or memory [38] and global synchronization mechanisms [39] are either not possible or very difficult to study without emulation-based execution-driven simulation. Since Accel-Sim is based on an ISA-independent performance model, it is also capable of running emulation-based execution-driven simulations using NVIDIA's relatively stable, well documented virtual ISA, PTX. Accel-Sim is the first academic simulation framework to support contemporary CUDA applications, modern Source and ASSembly (SASS) machine ISAs and simulate hand-tuned assembly in closed-source GPU binaries.

Shifting the focus from implementing an undocumented functional model enables Accel-Sim to focus on the performance model. We extensively modify GPGPU-Sim's performance model (which we release as part of GPGPU-Sim 4.0) to increase its level of detail, configurability and accuracy. To facilitate rigorous validation, the performance model outputs a set of counters that have 1:1 equivalents with hardware data emitted by NVIDIA profilers, in addition to the detailed statistics that can only be provided by simulation. These counter values are then fed into an automated tuning framework that generates correlation plots and modifies the simulator's configuration files, making it easier to create a validated performance model for a new GPU.

Using our new frontend and validation infrastructure, we perform an extensive modeling effort that builds on GPGPU-Sim's [40] performance model to create a more flexible, extensible GPU simulator. Through careful counter-by-counter validation, we expose several changes to contemporary GPU hardware. We demonstrate Accel-Sim's flexibility and accuracy by validating it against four generations of NVIDIA GPUs ranging from Kepler to Turing, performing an extensive side-by-side comparison of Accel-Sim and GPGPU-Sim 3.x modeling a Volta V100 [41].

During the course of this analysis we uncover a number of interesting insights into how contemporary hardware works. We utilized every publicly available resource to construct the performance model, capturing the details of what others have either disclosed or discovered [42]–[45]. In the process of correlating the memory system we discover and model several undocumented features, such as: details of the streaming, adaptive L1 data cache, sectoring of both the L1 and L2, a sub-warp, sector-centric memory coalescing policy, and an L2 write policy that conserves memory bandwidth in the presence of sub-sector reads.

Finally, this work performs two case-studies to highlight new research opportunities on contemporary GPUs and to demonstrate pitfalls that are alleviated by having a simulation infrastructure that is easier to validate. In particular, we demonstrate that out-of-order memory access scheduling, which appears relatively ineffective using an older model, yields a significant performance improvement when the level of detail in the memory system is increased to more closely match hardware. We also demonstrate that the L1 cache throughput bottleneck present in GPUs no longer exists in contemporary hardware, decreasing the effectiveness of techniques that selectively bypass the L1 for throughput reasons.

|                                                   | GPGPU-<br>Sim 3.x [40] | Gem5-<br>APU [48], [49] | MGPU-<br>Sim [50]  | MacSim<br>[51], [52] | Multi2-<br>Sim [53], [54]           | Accel-Sim                              |

|---------------------------------------------------|------------------------|-------------------------|--------------------|----------------------|-------------------------------------|----------------------------------------|

| ISA                                               | vISA +<br>mISA GT200   | vISA +<br>AMD mISA      | vISA +<br>AMD mISA | vISA +<br>Intel mISA | vISA +<br>mISA Kepler +<br>mISA AMD | vISA + NVBit<br>generated [36] mISA    |

| Front-end                                         | Execution              | Execution               | Execution          | Trace                | Execution                           | Trace- and<br>Execution-driven         |

| Validated perf. model                             | Fermi                  | AMD                     | AMD                | Fermi                | Kepler                              | Kepler, Pascal, Volta,<br>Turing       |

| Validated Workloads                               | 14                     | 10                      | 7                  | N/A                  | 24                                  | 80                                     |

| Reported Accuracy (error %)                       | 35% [46]               | 42% [49]                | 5.5% [50]          | N/A                  | 19% [53]                            | 15%                                    |

| Simulation rate (KIPS)                            | 3                      | N/A                     | 28 [50]            | N/A                  | 0.8 [50]                            | 12.5 (Trace-driven)<br>6 (Exec-driven) |

| Multi-threaded simulation                         | X                      | ×                       | 1                  | X                    | X                                   | ×                                      |

| Hand-tuned NVIDIA libraries<br>(i.e. Volta cuDNN) | ×                      | ×                       | ×                  | ×                    | ×                                   | 1                                      |

**Table 2.1.** Landscape of open-source GPU simulation. Accuracy numbers are taken from each simulator's respective publication.

#### 2.1 Background

In contemporary computer architecture research, simulation is commonly used to estimate the effectiveness of a new architectural design idea. High-level simulators enable architects to rapidly evaluate ideas at the expense of less accurate simulation results. Ideas that do not show promise in simulation are discarded while those that do show promise are refined in an iterative process.

Our work focuses on the simulation of massively parallel architectures, in particular GPUs. GPUs have witnessed rapid change and a widespread increase in their adoption with the rise of GPGPU computing and machine learning. In academia, the design of programmable accelerators is mostly carried out through modeling new techniques in high level GPU simulators. Over the past four years, there have been approximately 20 papers per year focusing on GPU-design at the top architecture conferences. 80% of those papers have used today's most popular open-source GPU simulator, GPGPU-Sim [46]. The relative popularity of GPGPU-Sim can be attributed to several factors, but it's most appealing aspect is perhaps the accuracy with which it models modern GPUs (relative to other open-source solutions). Such accuracy should provide a solid baseline for studying important architectural ideas that are relevant to future machines. Recent work on validating GPGPU-Sim [47] has demonstrated that there are several areas where a lack of detail in the performance model creates a a major source of error. However, the bulk of the error comes from the modeling of the memory system.

Table 2.1 presents a survey of the open-source GPU simulation space. Over the last decade, several GPU simulators have been developed, each serving a different purpose. Mac-Sim [51] is an early GPU simulator that performs trace-based simulation of NVIDIA's virtual ISA and includes a Fermi-like microarchitecture model. Recent work on MacSim has extended the simulator to execute traces for Intel GPUs [52]. Multi2-Sim is a versatile GPU simulator that has emulation-based functional simulation for both the virtual ISA and a subset of older machine ISAs from both AMD and NVIDIA. GPGPU-Sim [40] is a CUDA-centric simulator capable of functionally executing NVIDIA's virtual ISA and a subset of an older machine ISA. More recently, Gem5 has been augmented to support an APU performance model for AMD's virtual and machine ISAs [48]. MGPU-Sim [50] is a parallel GPU simulator for AMD's virtual and machine ISAs. One of the primary drawbacks with all the simulators that support execution-driven machine ISAs is the challenge of keeping up with changes to the mISA's functional model. As a result, only a limited subset of the instruction set (and hence applications) are ever fully supported. This is especially important for supporting optimized libraries that often use exotic, hand-tuned machine code to improve performance, such as NVIDIA's cuDNN. Although recent work has augmented GPGPU-Sim [55] to enable virtual ISA execution of these libraries, the functionality only works in pre-Volta GPUs. For Volta and Turing, cuDNN executes hand-tuned SASS kernels for which there is no virtual ISA implementation. Accel-Sim's support for machine ISA traces bypasses all of these issues. In addition, existing GPU simulation frameworks lack a systematic methodology to validate and model new architectural designs quickly.

#### 2.2 Accel-Sim Simulation Framework

Figure 2.1 depicts an overview of our new simulation framework. Accel-Sim is composed of: (1) a flexible frontend that supports execution-driven simulation of NVIDIA's virtual ISA and trace-driven simulation of contemporary machine ISAs, (2) a flexible and detailed performance model, (3) a correlation generation tool, and (4) a microbenchmarks-based configuration tuner. Together, the four components reduce the effort required to model contemporary and future GPUs.

Figure 2.1. Accel-Sim's end-to-end flow.

**Table 2.2.** Example demonstrating how mISA instruction traces and vISA instructions translate into the ISA-independent intermediate representation used by the performance model. In traces, the mapping between opcode and execution unit is provided by the *ISA def* file in Figure 2.1.\* *indicates these values are computed using emulation*.

| Execution Mode |                   | Example Instruction        | ISA-independent representation |                |                           |             |                            |                   |  |

|----------------|-------------------|----------------------------|--------------------------------|----------------|---------------------------|-------------|----------------------------|-------------------|--|

|                |                   | Example instruction        | $\mathbf{PC}$                  | Active<br>mask | Reg info:<br>(dsts, srcs) | Exec. unit  | Memory<br>addresses, width | Memory scope      |  |

| [Ti            | race] Kepler mISA | LD.E R4, [R6]              | 0x78                           | 0xFFFF         | R4, R6                    | Memory unit | 0x2000,, 4                 | global, L1 cached |  |

| [Ti            | race] Volta mISA  | LDG.E.U32.SYS R4, [R6]     | 0x32                           | 0x00FF         | R4, R6                    | Memory unit | 0x4000,, 4                 | global, L1 cached |  |

| [Tı            | race] Pascal mISA | IADD.X R7,R7,R0            | 0x12                           | 0x00EF         | R7, R0                    | INT unit    | -                          | -                 |  |

| [E:            | xec] PTX vISA     | ld.global.cg.b32 r1, [r0]; | *                              | *              | R1, R0                    | Memory unit | *                          | global, L2 cached |  |

#### 2.2.1 Flexible Frontend

Our new frontend supports both vISA (PTX) execution-driven and mISA (SASS) tracedriven simulation. In trace-driven mode, mISA traces are converted into an ISA-independent intermediate representation, that has a 1:1 correspondence to the original SASS instructions. Table 2.2 depicts an example of how SASS instructions from different machine generations and the virtual instructions from PTX are translated into the ISA-independent representation used by the performance model. The intermediate format is integrated into GPGPU-Sim 4.0 and represents the interface between the frontend and the performance model. The format includes all the information necessary to perform timing simulation, in particular: (1) the instruction's control flow (PC and active mask), (2) the instruction's datapath information (registers accessed and execution unit) and (3) memory addresses for ld/st instructions. In execution-driven mode, the active mask and memory addresses are computed by emulating the PTX instructions, whereas these values are embedded in the trace when executing the machine ISA.

We generate the traces from NVIDIA GPUs using Accel-Sim's tracer tool that is built on top of NVbit [36]. We use base+stride compression for the memory traces to keep the trace sizes within an acceptable range. When a new SASS ISA is released, users provide the frontend with an *ISA Def* file that specifies where each instruction should be executed. This is a relatively simple mapping that can be derived from publicly available information on NVIDIA's machine ISA [56].

By not emulating hundreds of scalar threads each cycle, Accel-Sim's trace-driven mode improves simulation speed versus execution-driven mode. Prior work [47], [49] demonstrates that executing GPU vISAs may not be an accurate representation of some workloads. The mISA representation of the program includes register allocation and other compiler optimizations, whereas the vISA assumes an infinite register space and has naive instruction scheduling. Further, supporting SASS gives researchers the ability to simulate closed-source, optimized libraries, such as cuDNN [37], which are written in hand-tuned SASS.

#### 2.2.2 Flexible and Detailed Performance Model

To accurately model contemporary GPUs, we make extensive modifications to GPGPU-Sim 3.x's performance model. This new performance model is released as part of GPGPU-Sim 4.0 and can be used, independent of Accel-Sim, for PTX simulation. Accel-Sim utilizes our GPGPU-Sim 4.0 performance model, interfacing with it through the ISA-independent instruction representation.

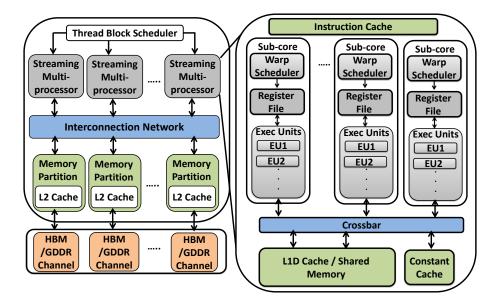

Figure 2.2 depicts an overview of the performance model. Streaming multiprocessors (SMs) are composed of multiple warp schedulers. Each warp scheduler has a dedicated register file (RF) and its own execution units (EUs). A warp scheduler with its dedicated RF and EUs is called a sub-core [4], [57]. Sub-cores are isolated, sharing only the instruction cache and the memory subsystem. The memory coalescing unit is designed to support sub-warp coalescing on every consecutive group of N threads. Our performance model is capable of simulating both separate and unified L1D cache and shared memory scratchpad [58].

Figure 2.2. Updated GPGPU-Sim 4.0 performance model.

Contemporary GPU architectures make use of an *adaptive cache* mechanism, in which the device driver transparently configures the shared memory capacity and L1D capacity on a per-kernel basis. Using the adaptive cache, if a kernel does not utilize shared memory, all the on-chip storage will be assigned to the L1D cache [59].

With the slowing growth of Moore's law, domain-specific processing pipelines continue to be introduced in GPUs (i.e. Tensor cores in Volta [41]). To ensure extensibility with this trend, Accel-Sim supports adding simple execution units from the configuration file, without the need to update the codebase. To add a new specialized unit, the user declares the new unit in the configuration file and maps the machine ISA op codes that use this unit in the *ISA def* file, as described in Figure 2.1. If execution-driven PTX support is required, then the user must also implement the code to emulate the new instruction's functionality. To determine the latency and throughput of the new unit, the user specifies a sequence of instructions that can be measured by the microbenchmark tuning framework (described in Section 2.2.3). We follow this process to model Volta and Turing's Tensor Cores.

Our GPU cache model supports a throughput-oriented, banked, and sectored cache design [60], [61]. The cache is flexible enough to model GPUs from Kepler through Turing. We also model the CPU-GPU memory copy engine, since all DRAM accesses go through the L2, including CPU-GPU memory copies [62]. To reduce unbalanced memory accesses across

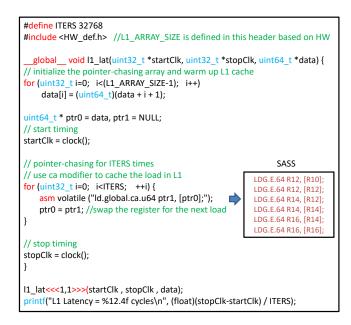

Figure 2.3. L1 latency microbenchmark

L2 memory partitions, which we refer to as partition camping [63], [64], we add advanced partition indexing that xors the L2 bank bits with randomly selected bits from the page row bits using a Galois-based irreducible polynomial (IPOLY) interleaving mechanism [65]. Partition camping is a major problem in contemporary GPUs that have  $2^n$  memory partitions, like High Bandwidth Memory (HBM) [66] which has 8 channels per stack [64], [67]. IPOLY hashing is guaranteed to be conflict-free for all  $2^n$  strides, which are common in GPGPU applications, and also shows reasonable, deterministic performance for other strides [65].

In the memory system, we model new advances in HBM and GDDR6 [66], [67]. This includes the dual-bus interface to launch row and column commands simultaneously, increasing bank parallelism [67], and detailed HBM timing. Further, we implement well-known memory optimization techniques such as advanced xor-based bank indexing and separate read/write buffers, to reduce memory bank conflicts and read-write interference [68]–[70].

## 2.2.3 Tuner and Targeted Microbenchmarks

Accel-Sim includes a microbenchmark suite to pinpoint latency, bandwidth and geometry changes to known hardware structures from one generation to another. When new hardware is released, the user provides a *hardware def* header file to the tuner, as shown in Figure 2.1. The file is used by the microbenchamrks to help discover non-public configuration parameters. The def file enumerates a minimal amount of information (such as number of SMs, warp size, etc.) that can be derived from publicly available documents [41].

In total, we have 38 microbenchmarks that span from L1/L2/shared memory latency and attained bandwidth, cache write policy, cache configuration, access/sector granularity, number of cache banks, memory coalescing policy, cache streaming behavior, execution unit latency/throughput and DRAM latency/bandwidth for different data elements: float, double and 128-bit vector. To illustrate the general configuration of the microbenchmarks, Figure 2.3 lists the code for our L1 latency microbenchmark that uses pointer chasing [44], [71] to create data dependencies with minimal overhead. The microbenchmark is written such that the kernel's execution time is dominated by the L1 latency. After execution, the tuner reads the microbenchmark's output and generates a configuration file for the performance model.

For other parameters that cannot be directly determined by our microbenchmarks (such as warp scheduling, memory scheduling, the L2 cache interleaving granularity and the L2 cache hashing function), Accel-Sim simulates each possible combination of these four parameters on a set of memory bandwidth microbenchmarks (l1-bw, l2-bw, shd-bw and mem-bw). The combination with the highest average hardware correlation is chosen by the tuner.

#### 2.2.4 Correlator

An automated configuration tuner does not capture more drastic architectural changes in different generations. Manual effort is required to model such changes. However, the magnitude of the effort can be lessened with quickly generated, targeted information on inaccuracy. Accel-Sim's correlation tool automates the process of generating counter-by-counter correlation data for different architectures. The tool generates graphs and data that serve as correlation guidance to pin-point workloads and metrics where the simulator is not well correlated to hardware. Using insights from the correlation of various performance counters over different realistic workloads and microbenchmarks, performance bugs or misrepresentations in the simulator are identified and corrected.

#### 2.2.5 Simulation Rate