# SELF-HEATING EFFECT ALLEVIATION FOR POST-MOORE ERA CHANNEL MATERIALS

by

**Pai-Ying Liao**

### **A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Electrical and Computer Engineering West Lafayette, Indiana December 2022

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Peide D. Ye, Chair

Elmore Family School of Electrical & Computer Engineering

### Dr. David B. Janes

Elmore Family School of Electrical & Computer Engineering

## Dr. Haiyan Wang

School of Materials Engineering

### Dr. Xianfan Xu

School of Mechanical Engineering

## Approved by:

Dr. Dimitrios Peroulis

Dedicated to Meng-Ling and my parents

## ACKNOWLEDGMENTS

First, I would like to thank my Ph. D. advisor, Prof. Peide Ye, for supporting and guiding me kindly and patiently throughout these years. I knew nothing about research when I initiated this journey which brings profound impacts to my life. Prof. Ye gave me the chance to take a glance at the respectful world of research where plenty of researchers dedicate themselves to keeping broadening the human knowledge.

Besides, I am very grateful for all my committee members. I took Prof. David Janes' fabrication lab course in my first semester at Purdue in which I started to learn the useful experimental skills in cleanroom. Besides, I received many assistances from Prof. Xianfan Xu and Prof. Haiyan Wang's students and postdocs. Dr. Shouyuan Huang in Prof. Xu's group trained me to employ the great, home-build Raman spectroscopy, and Dr. Jie Jian, Dr. Xing Sun, and Dr. Xuejing Wang in Prof. Wang's group helped me to take numerous TEM photos.

I would also like to thank current and former group members in Prof. Ye' group especially Dr. Mengwei Si for giving me countless suggestions when I encountered difficulties and Dr. Jingkai Qin for bringing me together to complete an amazing work of tellurium encapsulated in nanotubes. I appreciate many other supports from Dr. Gang Qiu, Dr. Adam Charnas, Zhuocheng Zhang, Dr. Jinhyun Noh, Dongqi Zheng, Zehao Lin, Dr. Zhizhong Chen, Chang Niu, Xiao Lyu, Dr. Wonil Chung, Dr. Sami Alghamdi, Dr. Hagyoul Bae, Dr. Jie Zhang, Jian-Yu Lin, Dr. Junkang Li, and Dr. Yiming Qu. Moreover, I would also like to thank Dr. Sami Alajlouni and Prof. Ali Shakouri for helping me on the thermo-reflectance measurement.

Moreover, I am grateful to Dr. Sami Alajlouni and Prof. Ali Shakouri for training me and providing me with the high-resolution thermo-reflectance imaging system to measure the self-heating effect of top-gated indium oxide transistors, which is a significant part of this thesis.

Besides, I am grateful for the staffs at Birck Nanotechnology Center for training me to utilize the exceptional instruments and keeping them operational: Dr. Justin Wirth, Bill Rowe, Dr. Joon Hyeong Park, Francis Manfred, Richard Hosler, Dave Lubelski, and Kenny Schwartz.

Last but not least, I would like to express my sincere thank to Meng-Ling Shih and Kai Wang for their mental support along the way and the depth of my gratitude to my parents for raising me and being my eternal and secure backing.

4

## TABLE OF CONTENTS

| LIST OF T | TABLES                                           |    |

|-----------|--------------------------------------------------|----|

| LIST OF F | FIGURES                                          | 9  |

| SYMBOL    | S                                                | 14 |

| ABBREVI   | IATIONS                                          |    |

| NOMENC    | LATURE                                           |    |

| ABSTRAC   | CT                                               |    |

| 1. INTR   | ODUCTION                                         |    |

| 1.1 Ov    | erview                                           |    |

| 1.1.1     | Motivations                                      |    |

| 1.1.2     | Graphene                                         |    |

| 1.1.3     | Transition Metal Dichalcogenides                 |    |

| 1.1.4     | Black Phosphorus                                 |    |

| 1.2 Tel   | llurium                                          |    |

| 1.2.1     | Introduction to Tellurium                        |    |

| 1.2.2     | Synthesis Methods                                |    |

| 1.2.3     | Physical Properties                              |    |

| 1.3 Ind   | lium Oxide                                       |    |

| 1.3.1     | Introduction to Indium Oxide                     |    |

| 1.3.2     | Thin-Film Growth through Atomic Layer Deposition |    |

| 2. TELL   | URIUM NANOWIRE WITH HIGH CURRENT DENSITY         |    |

| 2.1 Intr  | roduction to Tellurium Nanowire                  |    |

| 2.2 Tel   | llurium Nanowire in Carbon Nanotube              |    |

| 2.2.1     | Synthesis Method                                 |    |

| 2.2.2     | TEM Characterization                             |    |

| 2.2.3     | Raman Response                                   |    |

| 2.3 Tel   | llurium Nanowire in Boron Nitride Nanotube       |    |

| 2.3.1     | Synthesis Method                                 |    |

| 2.3.2     | TEM Characterization                             | 47 |

| 2.3.3     | Raman Response                                   |    |

| 2.   | 2.3.4 Electrical Performance                                                           | 50       |

|------|----------------------------------------------------------------------------------------|----------|

| 3. S | SELF-HEATING EFFECT ALLEVIATION ON ALD INDIUM OXIDE T                                  | HROUGH   |

| SUBS | STRATE SUBSTITUTION                                                                    | 61       |

| 3.1  | Introduction to ALD In <sub>2</sub> O <sub>3</sub> Transistors                         | 61       |

| 3.2  | Device Fabrication                                                                     | 64       |

| 3.3  | High Current Density and Low Contact Resistance                                        | 65       |

| 3.4  | Thermal Engineering with Highly Resistive Silicon Substrate                            |          |

| 4. S | ELF-HEATING EFFECT VISUALIZATION THROUGH THERMO-REFLI                                  | ECTANCE  |

| IMAC | GING TECHNIQUE                                                                         | 76       |

| 4.1  | Motivations                                                                            | 76       |

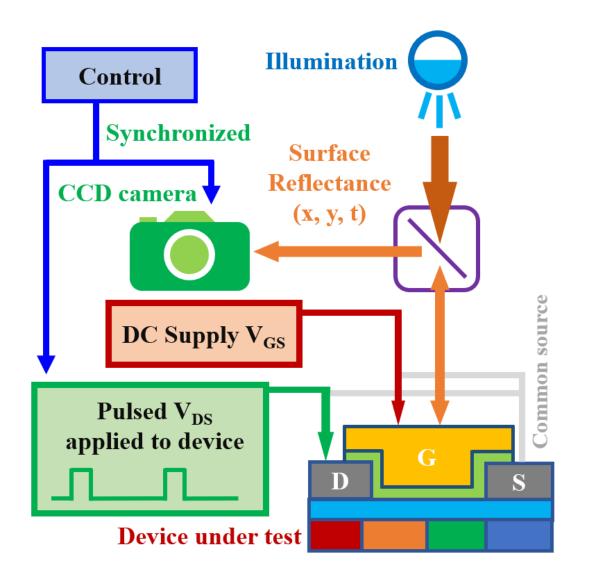

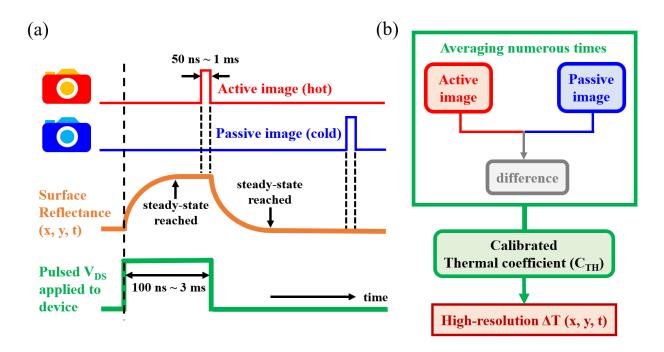

| 4.2  | Equipment Setup and Mechanism                                                          | 76       |

| 4.3  | Thermo-Reflectance Measurement                                                         | 79       |

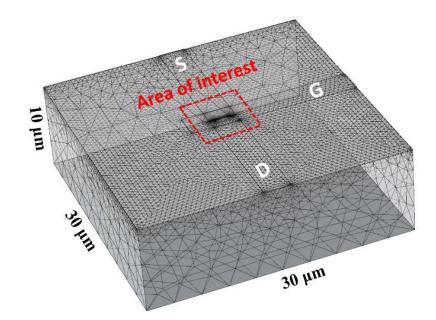

| 4.4  | Heat Transfer Simulation                                                               | 81       |

| 4.5  | Contact Resistance Engineering                                                         | 83       |

| 5. T | TRANSIENT THERMAL AND ELECTRICAL CO-OPTIMIZATION OF ALL                                | ) INDIUM |

| OXID | DE TRANSISTORS                                                                         | 85       |

| 5.1  | Motivations                                                                            | 85       |

| 5.2  | Substrate Substitution with Variant Thermally Conductive Substrates                    | 85       |

| 5.3  | Transient Thermal Property Exploration                                                 |          |

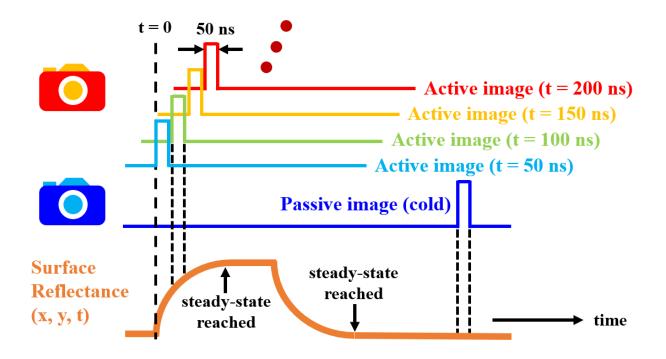

| 5.   | 5.3.1 Equipment Setup and Mechanism                                                    |          |

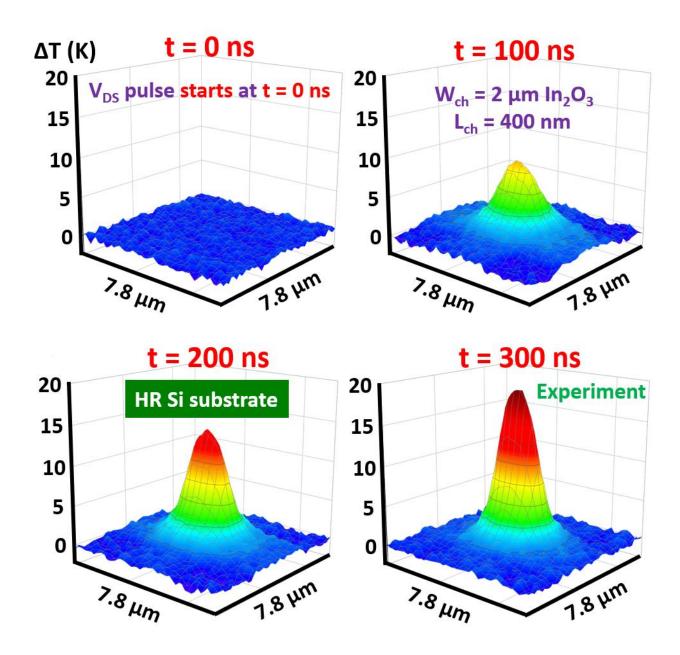

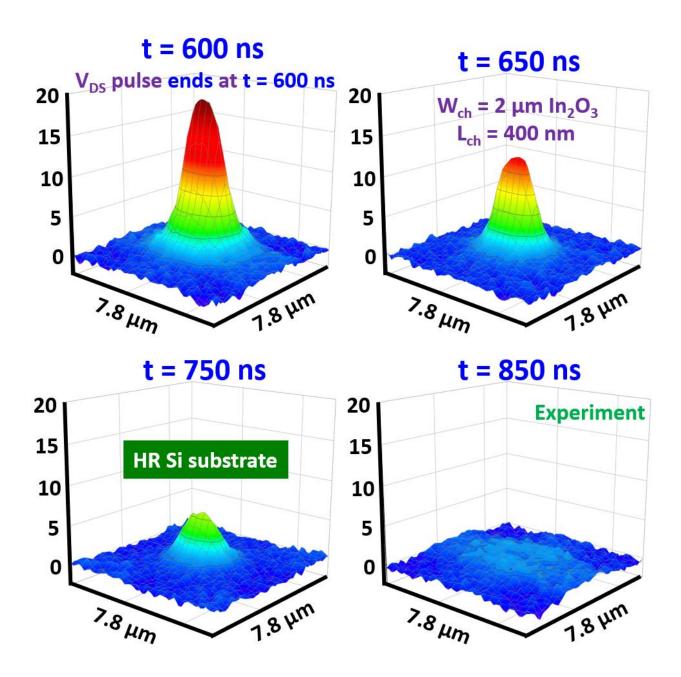

| 5.   | 5.3.2 Transient Thermal Behaviors of TG ALD In <sub>2</sub> O <sub>3</sub> Transistors |          |

| 5.4  | Self-Heating Effect Avoidance with Short-Pulse Measurement                             |          |

| 6. S | SELF-HEATING EFFECT ALLEVIATION ON ALD INDIUM OXIDE T                                  | HROUGH   |

| INTR | ERFACE ENGINEERING                                                                     |          |

| 6.1  | Motivations                                                                            |          |

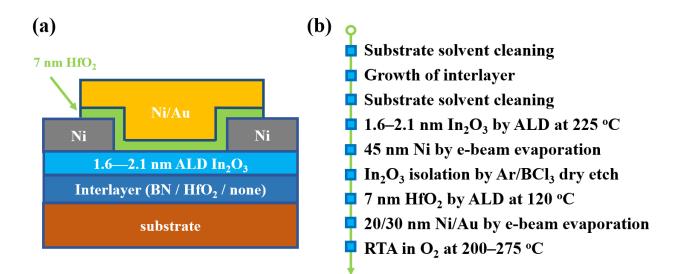

| 6.2  | Device Structure and Fabrication                                                       | 100      |

| 6.3  | Self-Heating Effect Comparison                                                         | 101      |

| 6    | 5.3.1 Thermo-Reflectance Imaging Observation                                           | 101      |

| 6.   | 5.3.2 Thermal Boundary Conductance Extraction                                          |          |

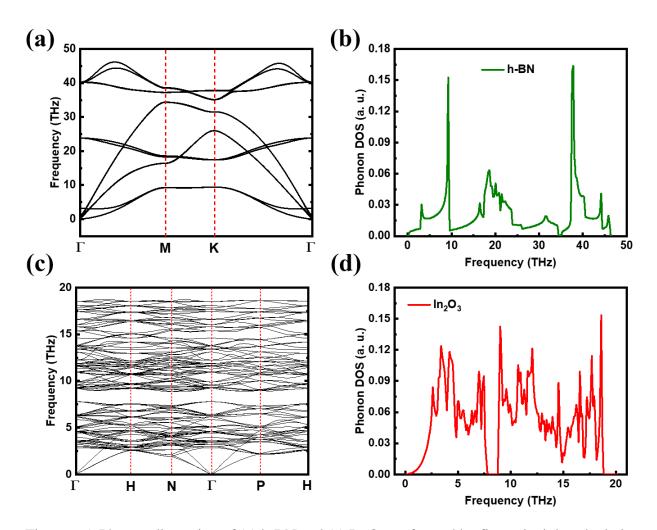

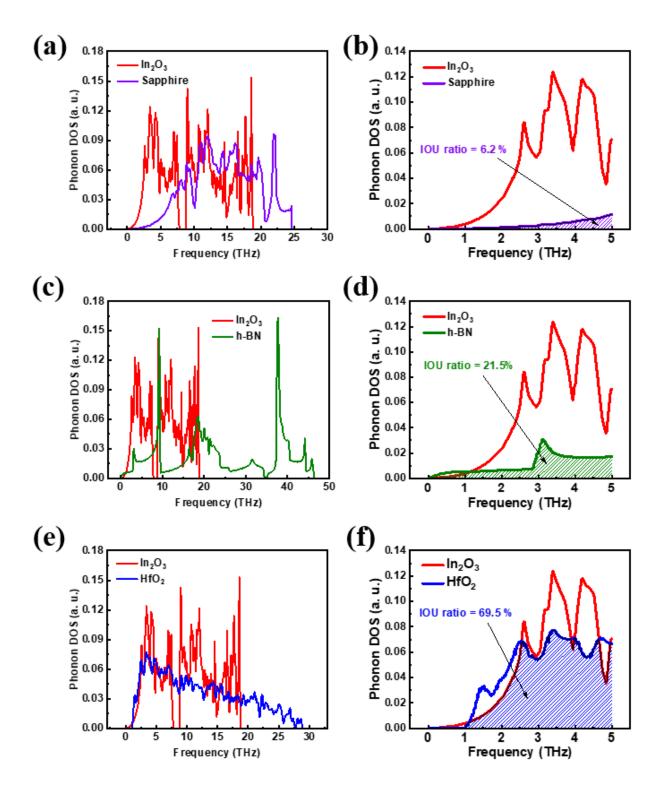

| 6.4  | Phonon Density of States                                                               |          |

| 6.   | 5.4.1 Calculations                                                                     | 106      |

|     | 6.4.2 Analysis      | 108 |

|-----|---------------------|-----|

|     | SUMMARY AND OUTLOOK |     |

| REF | FERENCES            | 118 |

| VIT | `A                  | 134 |

| PUE | BLICATIONS          | 135 |

## LIST OF TABLES

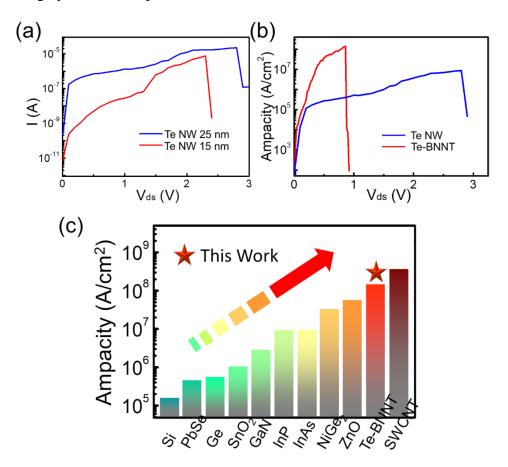

| Table 2.1. Com | parison of am | pacity of devices | based on semicond | ducting nanov | wires 53 |

|----------------|---------------|-------------------|-------------------|---------------|----------|

|----------------|---------------|-------------------|-------------------|---------------|----------|

## LIST OF FIGURES

| Figure 1.1. Schematic illustration of the atomic structure of tellurium. (a) Top view and (b) side view of a hexagonal crystal structure                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2. Typical Raman spectroscopy of bulk Te samples. (a) Schematic illustration and (b) an experimental Raman response showing 3 first-order Raman active modes                                                                                                                                                                                                                                                                                                  |

| Figure 1.3. As-grown 2D tellurium through PVT. (a) Hexagonal van der Waals 2D Te flakes grown on the inner wall of the sealed ampoule and (b) sidewalls on the SiO <sub>2</sub> /Si substrate (c) TEM image and the inset shows the corresponding FFT image of the area squared by the purple dashed lines.                                                                                                                                                            |

| Figure 1.4. AFM image of a typical 2D Te flake with a thickness of 25.1 nm grown by PVT. The scale bar is 1 $\mu$ m                                                                                                                                                                                                                                                                                                                                                    |

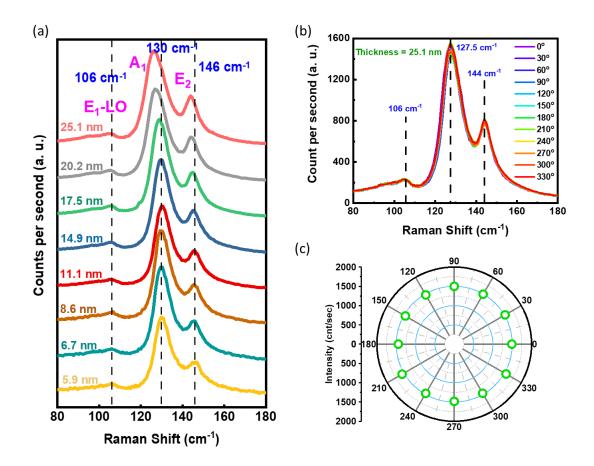

| Figure 1.5. Raman spectroscopy of polycrystalline Te thin film. (a) Thickness dependence of Raman spectroscopy on 2D Te flakes and (b, c) angle-resolved (between crystal orientation and incident laser polarization) Raman spectra for the 2D Te flake                                                                                                                                                                                                               |

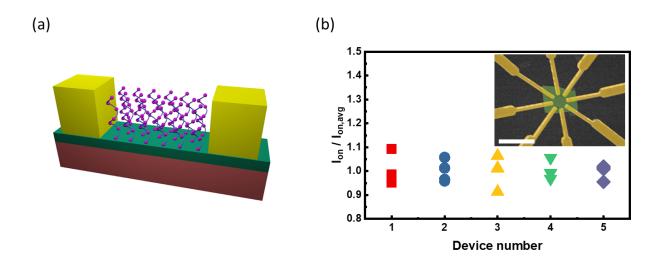

| Figure 1.6. (a) Visualization of the designed device structure and (b) the isotropy of electric transport performance. The inset is the a false-colored SEM image of a measured device with the scale bar to be 3 $\mu$ m. 34                                                                                                                                                                                                                                          |

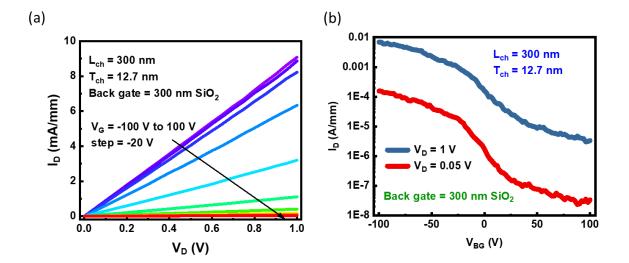

| Figure 1.7. Electrical measurement of 2D Te short channel devices. (a) Output characteristic and (b) transfer characteristic of a device with 300 nm channel length and 12.7 nm channel thickness.                                                                                                                                                                                                                                                                     |

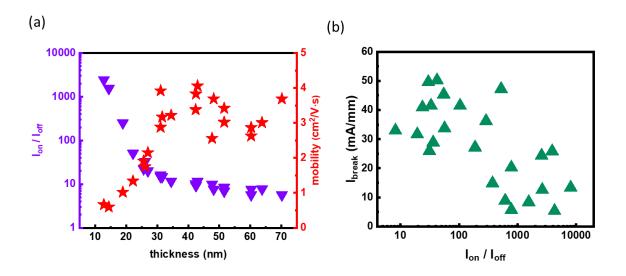

| Figure 1.8. Statistical plot of (a) relation between on-current and ON–OFF ratio and (b) relation between ON-current and ON–OFF ratio                                                                                                                                                                                                                                                                                                                                  |

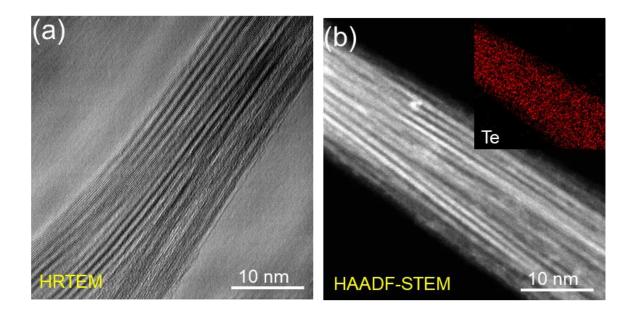

| Figure 2.1. TEM characterization of Te chains in SWCNTs. (a) HRTEM image and (b) HAADF-<br>STEM image. Inset shows the corresponding EDX mapping image                                                                                                                                                                                                                                                                                                                 |

| Figure 2.2. Single Te atomic chain in CNTs with ID of 0.8 nm exhibiting 3-fold structure 41                                                                                                                                                                                                                                                                                                                                                                            |

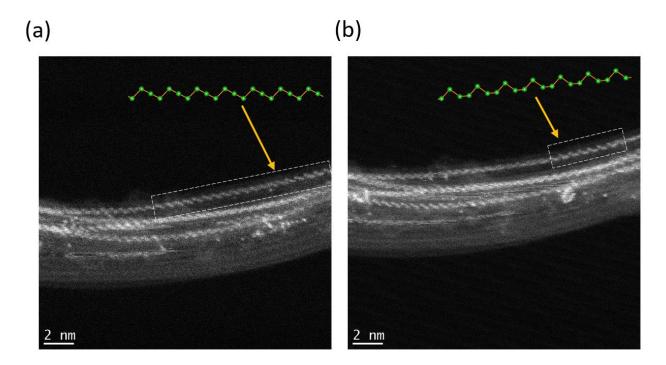

| Figure 2.3. HRTEM images of the (a) single, (b) double, (c) triple, and (d) 19 chains of Te shielded by CNTs. Inset: schematic structure diagrams                                                                                                                                                                                                                                                                                                                      |

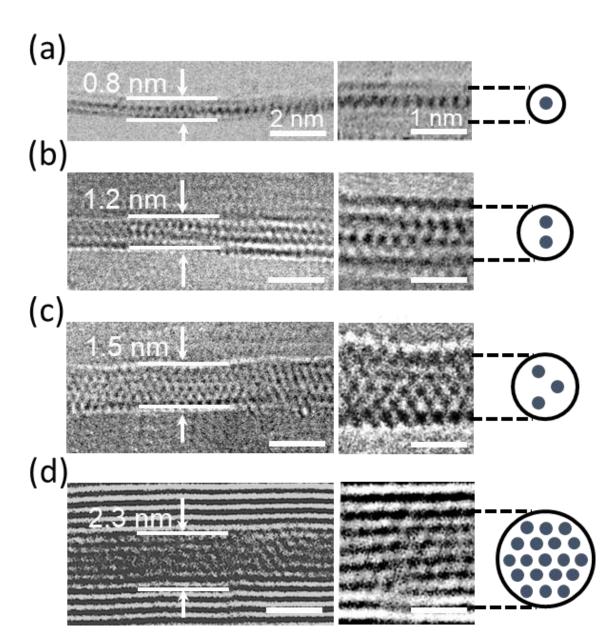

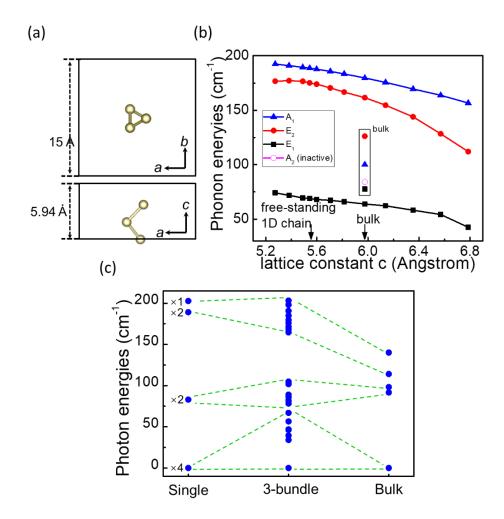

| Figure 2.4. The photon energy calculation of Te atomic chains. (a) Atomistic structure of the Te atomic chain. (b) Phonon energies of a single atomic Te chain with dependence of lattice constant. (c) Phonon energies for a single Te atomic chain and bulk Te. In 3-bundle case, the interaction between chains would split the Raman vibration modes and result into the increase of modes, while these modes are degenerated in single chain case or in bulk form |

| Figure 2.5. (a) Raman spectrum evolution of Te NWs with CNTs of different ID. (b) Dependence of the shifts in Raman peak frequency on CNT ID                                                                                                                                                                                                                                                                                                                           |

| Figure 2.6. Experimental setup for the CVD growth of BNNTs                                                                                                                                                                                                                                                                                                                                                                                                             |

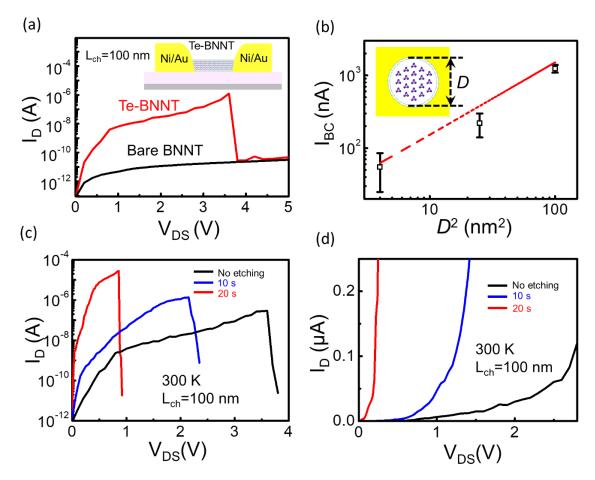

Figure 2.12. Current-carrying capability of Te NWs encapsulated in BNNTs. (a) I-V curves up to breakdown of a Te-BNNT device with a 100 nm channel length and an empty BNNT device. (b) Breakdown current (BC) versus  $D^2$  with all channel lengths of 100 nm. (c) Logarithmic scale and (d) linear scale plot of I-V characteristics in Te-BNNT devices with different etching time. ..... 51

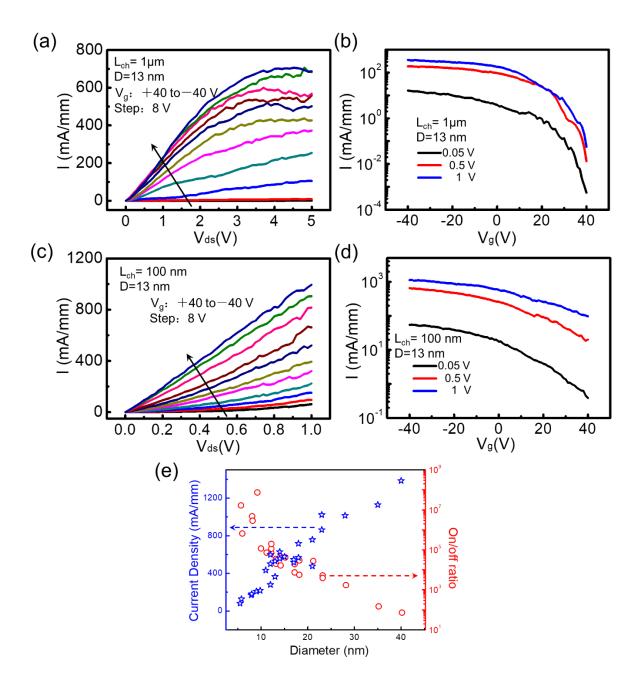

Figure 2.16. Electrical performance of a Te NW transistor. (a) Output characteristics of a typical p-type Te NW transistor with a diameter of 13 nm. (b) Corresponding transfer curves of the same device. (c) Output curves and (d) transfer curves of the device with a short channel of 100 nm. 56

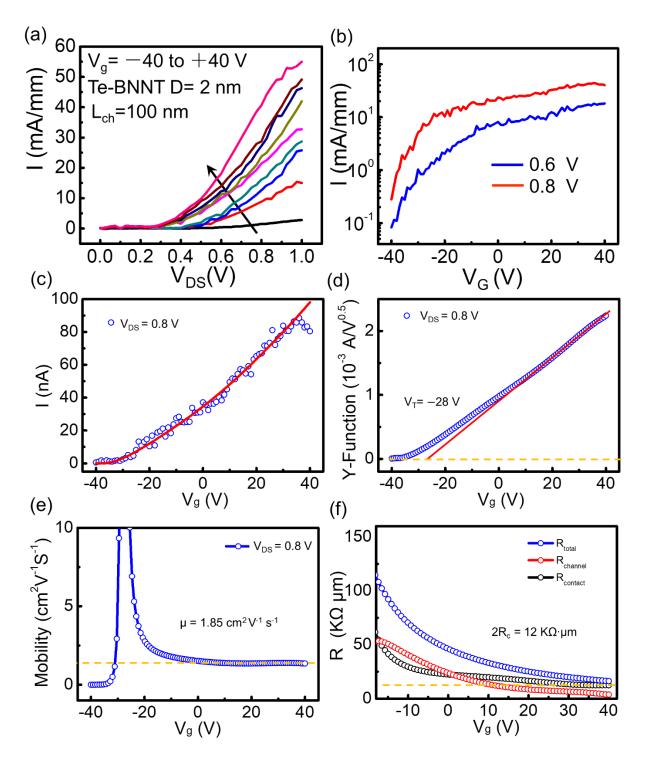

Figure 2.17. Electrical performance of a 2 nm Te-BNNT transistor. (a) Output and (b) transfer curves of the same device. (c) Linear scale of the transfer curve at  $V_{DS}$ =0.8 V. (d) Y-function plots of the device. (e) The calculated intrinsic carrier mobility of the Te atomic chains. (f) The gate dependent resistance of the device. 59

Figure 2.18. Comparison of electrical performance between Te-BNNT and bare Te NW FETs. (a) ON–OFF ratio (b) current density at  $V_{ds}=1$  V and (c) carrier mobility of Te-BNNTs and Te NWs short-channel FETs. The solid signs represent Te-BNNT NW devices and the empty signs represent bare Te NW devices. 60

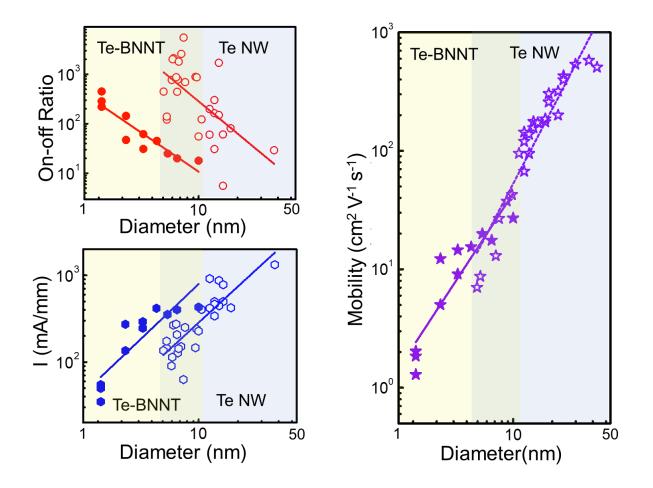

Figure 3.1. (a) A TEM image demonstrating ALD  $In_2O_3$  and  $HfO_2$  grown on uneven surfaces. (b, c) EDX mapping of In and Hf with HAADF STEM, showing conformal growth by ALD. ...... 62

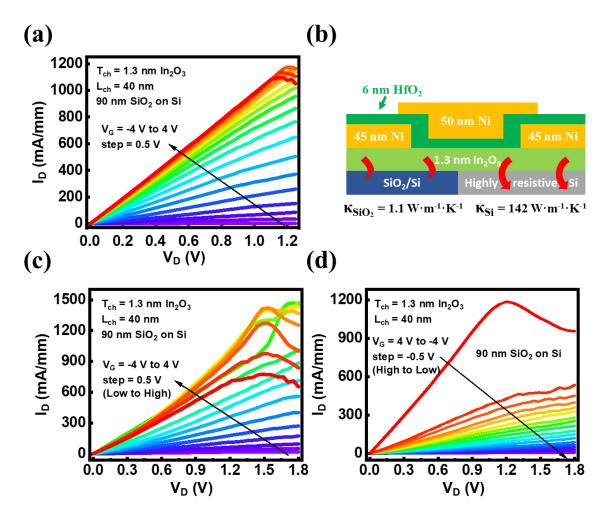

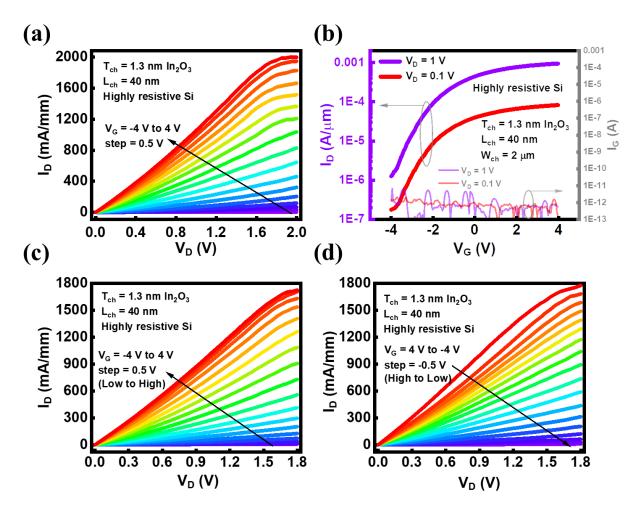

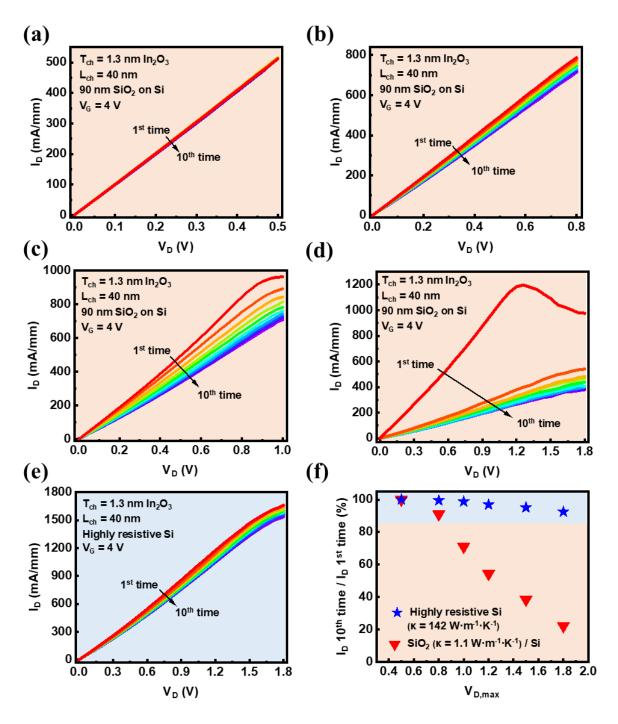

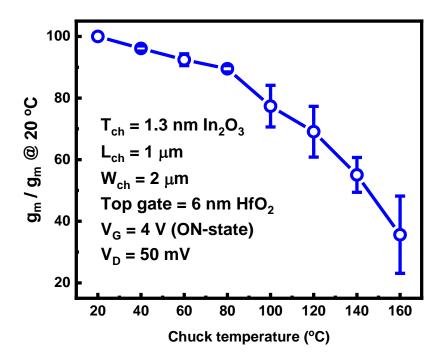

Figure 3.7. (a) Degraded I<sub>D</sub> curves of a TG In<sub>2</sub>O<sub>3</sub> transistor with SiO<sub>2</sub>/Si substrate and a large V<sub>D</sub> up to 1.25 V, revealing the SHE. (b) Cross-sectional exhibition of the heat dissipation of In<sub>2</sub>O<sub>3</sub> devices with different substrates. Silicon with around 100 times higher thermal conductivity is able to passivate the generated thermal energy much more efficiently. Drastically degenerated and extremely chaotic I<sub>D</sub>–V<sub>D</sub> curves with VG sweeping (c) from low to high and (d) from high to low. The totally different behaviors imply that SHE is dominating over the transport performance... 69

| Figure 4.2. (a) Working mechanism of the high-resolution TR imaging equipment in time domain. |  |

|-----------------------------------------------------------------------------------------------|--|

| (b) Transformation from TR signal to a temperature scale79                                    |  |

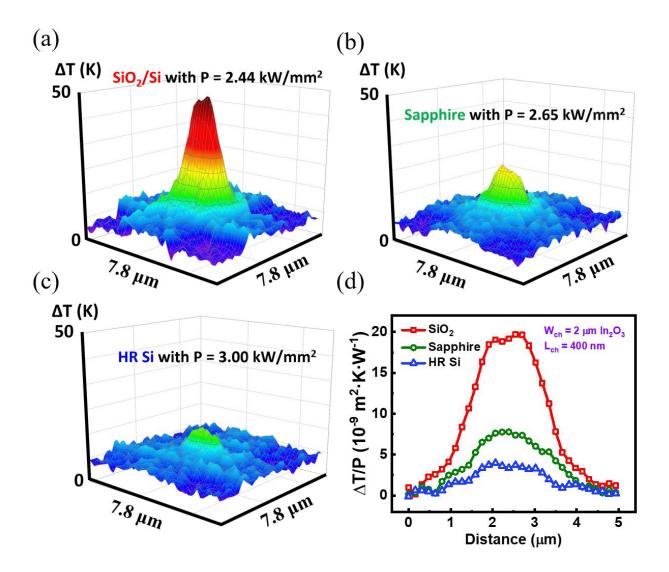

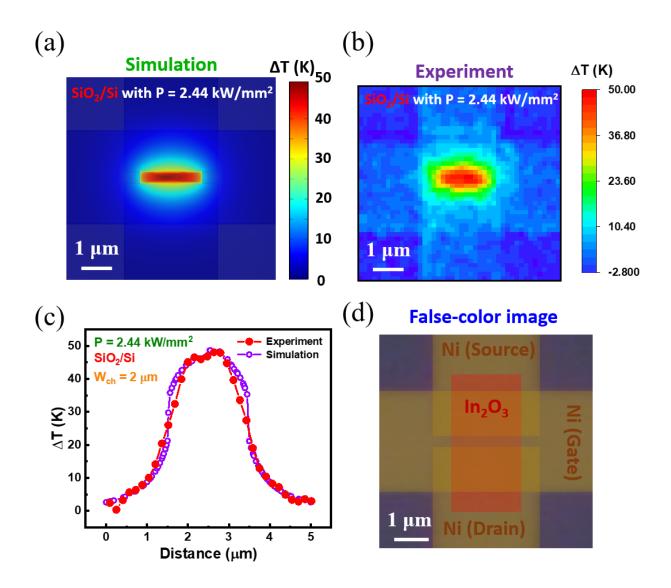

Figure 4.3. Temperature increase of a TG  $In_2O_3$  transistor with (a) SiO<sub>2</sub>/Si, (b) sapphire, and (c) HR Si substrate and power density of (a) 2.44, (b) 2.65, and (c) 3.00 kW/mm<sup>2</sup>.....80

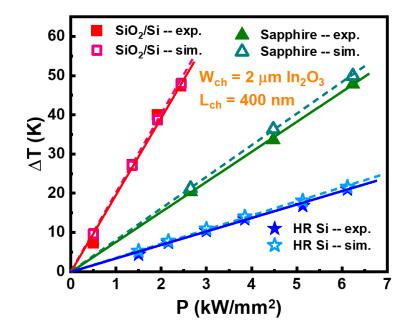

Figure 4.6. Temperature increase of TG In<sub>2</sub>O<sub>3</sub> device with different substrates and power density.

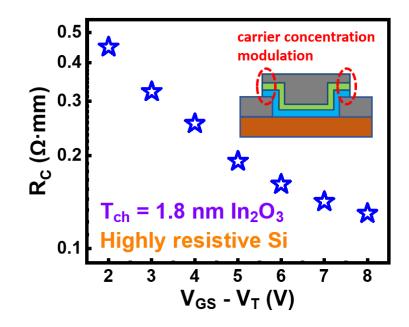

Figure 4.7. Contact resistance decrease with increasing  $V_{GS}$ - $V_T$  due to carrier concentration modulation.

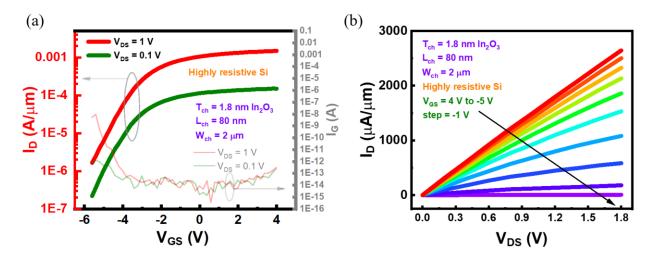

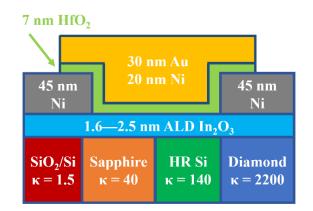

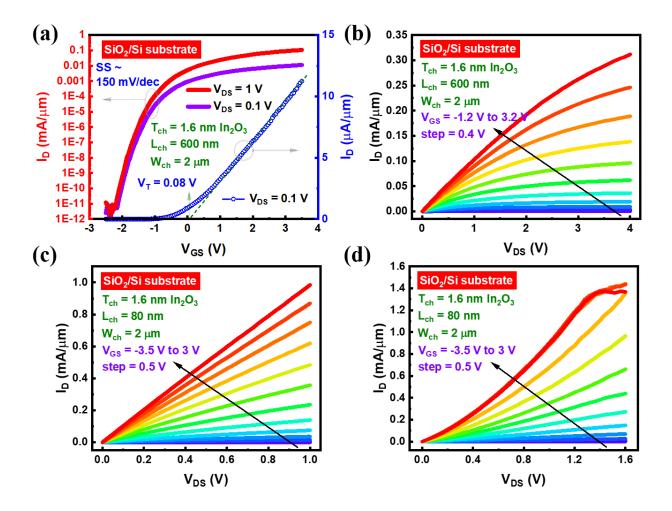

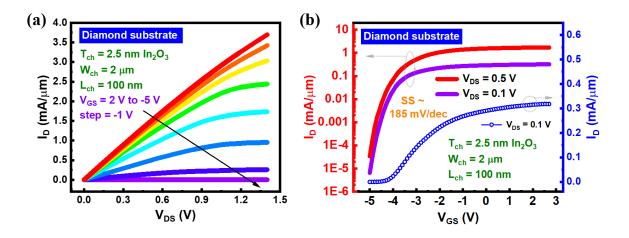

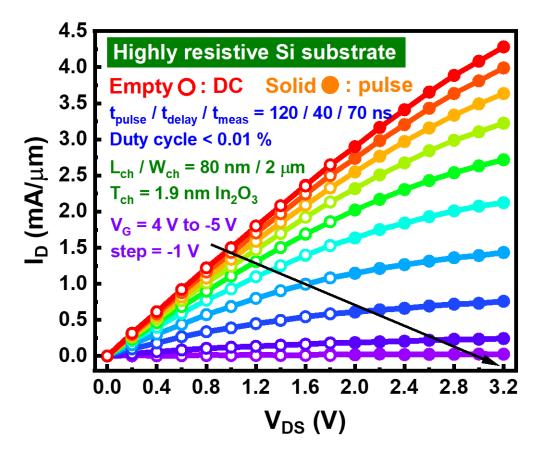

Figure 5.2. (a) Transfer and (b) output characteristics of a TG  $In_2O_3$  transistor with  $T_{ch}$  of 1.6 nm and long  $L_{ch}$  of 600 nm on a SiO<sub>2</sub>/Si substrate operated at enhancement-mode (E-mode). (c) Output characteristics of a TG ALD  $In_2O_3$  FET with short  $L_{ch}$  of 80 nm on a SiO<sub>2</sub>/Si substrate. (d) Severe SHE deteriorates the device performance of a TG ALD  $In_2O_3$  FET with high power density. ... 87

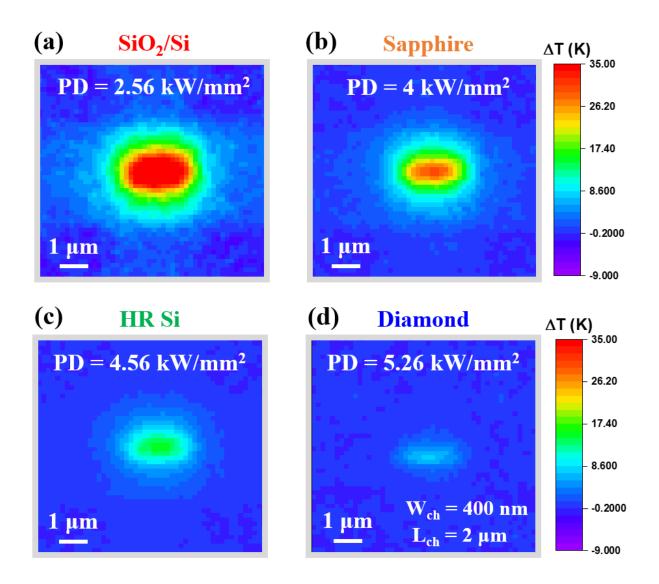

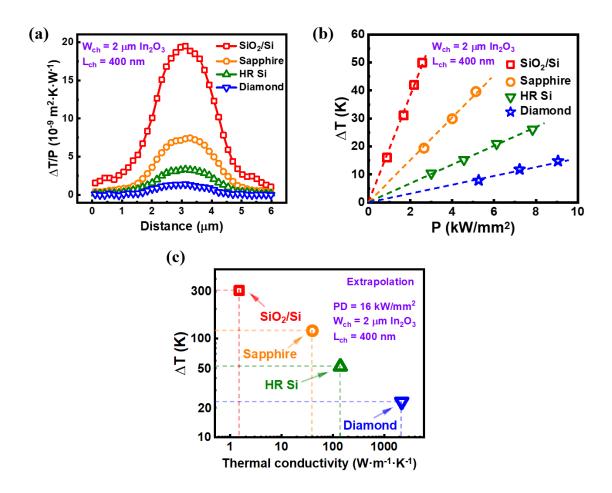

Figure 5.3. SHE visualization of  $In_2O_3$  FETs in experiments with substrates of (a) SiO<sub>2</sub>/Si, (b) sapphire, (c) highly resistive silicon, and (d) diamond substrate with various power density. .... 88

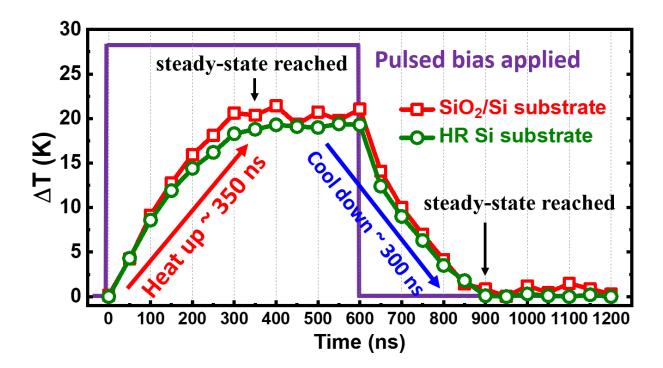

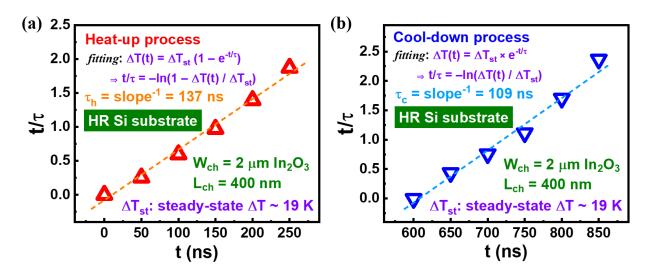

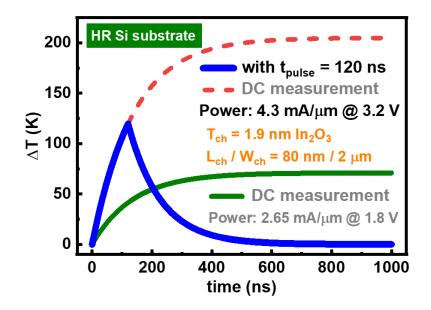

Figure 5.13. Transient  $\Delta T$  calculation of DC and pulse measurements under respective highest PD in Figure 5.12. 98

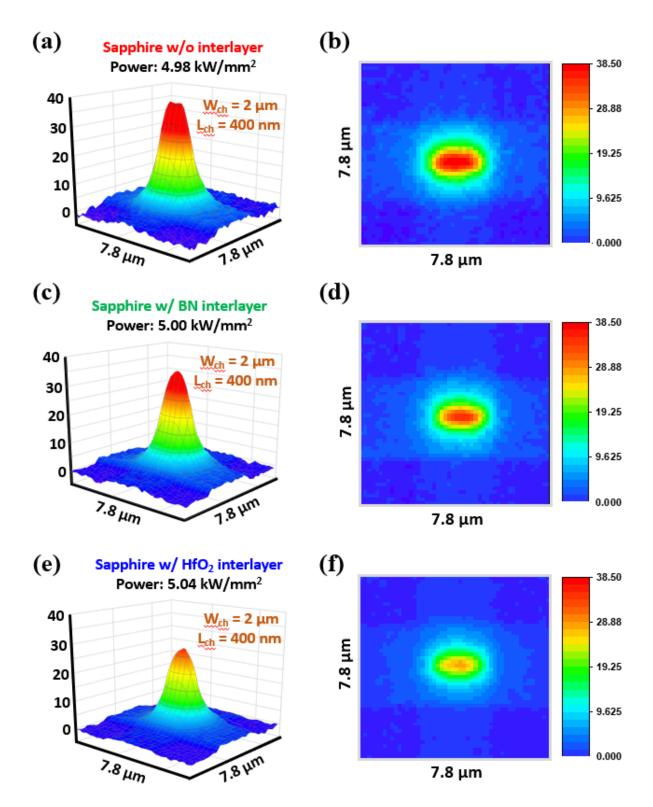

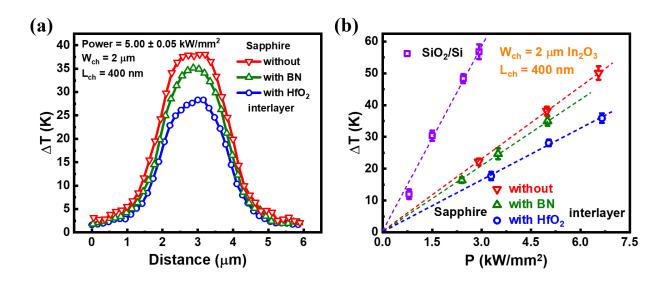

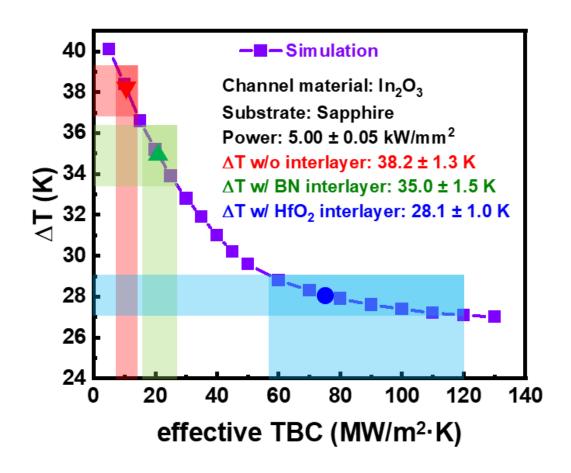

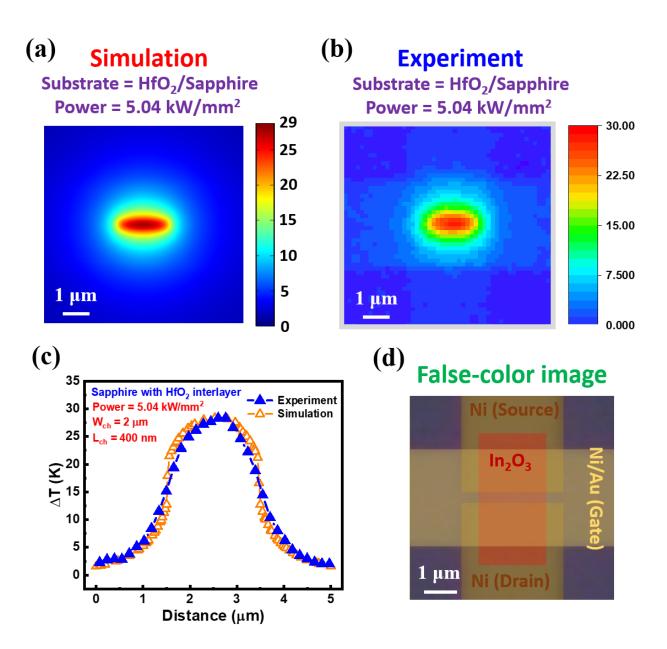

Figure 6.2. A  $\Delta T$  (a) 3D plot and (b) heat map of a TG In<sub>2</sub>O<sub>3</sub> transistor with W<sub>ch</sub> of 2 µm, L<sub>ch</sub> of 400 nm, no interlayer on a sapphire substrate at PD of roughly 5 kW/mm<sup>2</sup> imaged by the TR measurement system. The corresponding plots of the devices with the same structure, dimensions, but a thermal adhesion layer of (c, d) 2L h-BN and (e, f) 4 nm HfO<sub>2</sub> at similar PD...... 103

Figure 6.3. (a) Cross-sections of the three  $\Delta T$  plots along the direction of channel width, showing 9 or 27 % alleviation of the SHE by inserting a thermal adhesion layer of h-BN or HfO<sub>2</sub>, respectively. (b) Comparison between devices with different substrates and interlayers and variant PD. Great linearity is agreed in all cases. 104

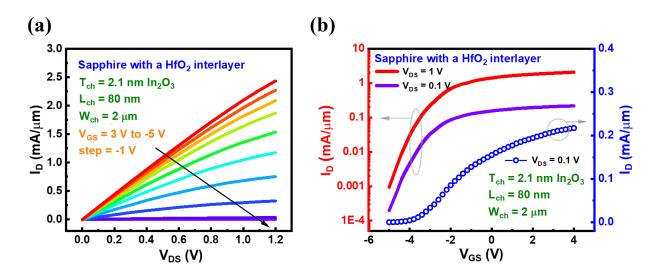

Figure 6.8. (a) Output and (b) transfer characteristics of a 2.1-nm-thick TG  $In_2O_3$  transistor with  $L_{ch}$  of 80 nm and  $W_{ch}$  of 2  $\mu$ m on a sapphire substrate with a HfO<sub>2</sub> thermal adhesion layer. Due to the great heat transfer properties of the substrate, SHE is negligible, and maximum  $I_D$  of 2.4 mA/ $\mu$ m is achieved at  $V_{DS}$  of 1.2 V. The ON–OFF ratio is roughly 4 orders of magnitude...... 113

## SYMBOLS

| As                                                 | Surface area                        |

|----------------------------------------------------|-------------------------------------|

| Cox                                                | Oxide capacitance per unit area     |

| C <sub>p</sub>                                     | Specific heat                       |

| D                                                  | Diameter                            |

| F                                                  | Outward heat flux                   |

| gm, G                                              | Transconductance                    |

| h                                                  | Heat transfer coefficient           |

| I <sub>BC</sub>                                    | Breakdown current                   |

| I <sub>D</sub> , I <sub>DS</sub> , I <sub>ds</sub> | Drain current                       |

| IG                                                 | Gate leakage current                |

| I <sub>max</sub>                                   | Maximum current                     |

| Ion                                                | On current                          |

| $\mathbf{I}_{\mathrm{off}}$                        | Off current                         |

| κ                                                  | Thermal conductivity                |

| k                                                  | Dielectric constant                 |

| L <sub>ch</sub>                                    | Channel length                      |

| μ <sub>e</sub>                                     | Effective mobility in linear regime |

| $\mu_0$                                            | Intrinsic mobility                  |

| $\mu_{\mathrm{FE}}$                                | Field-effect mobility               |

| R <sub>C</sub>                                     | Contact resistance                  |

| ρ                                                  | Mass density                        |

| R <sub>sh</sub>                                    | Sheet resistance                    |

| R <sub>total</sub>                                 | Total resistance                    |

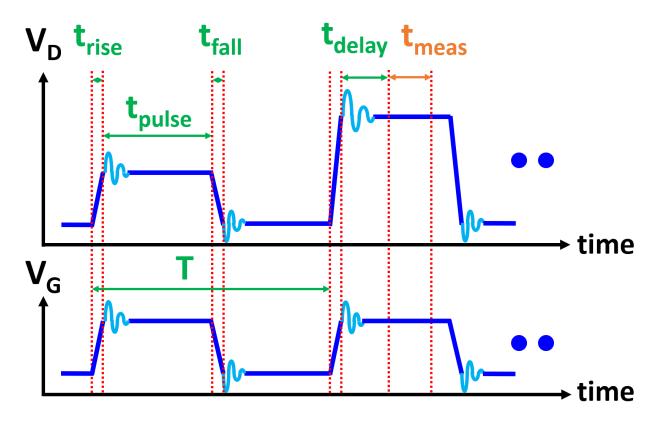

| t <sub>delay</sub>                                 | Delaying time                       |

| t <sub>fall</sub>                                  | Falling time                        |

| t <sub>meas</sub>                                  | Measuring time                      |

| t <sub>pulse</sub>                                 | Pulse width                         |

| t <sub>rise</sub>                                  | Rising time                         |

| Т                                                  | Period                              |

| Ta                    | Ambient temperature                          |

|-----------------------|----------------------------------------------|

| τ                     | Time constant                                |

| T(t)                  | Temperature at time <i>t</i>                 |

| $T_{ch}$              | Channel thickness                            |

| θ                     | Mobility attenuation coefficient             |

| $\theta_{c}$          | Mobility attenuation factor from the contact |

| $\theta_{ch}$         | Mobility attenuation factor from the channel |

| V                     | Volume                                       |

| V <sub>BG</sub>       | Back-gate-to-source bias voltage             |

| $V_D, V_{DS}, V_{ds}$ | Drain-to-source bias voltage                 |

| V <sub>D, max</sub>   | Maximum drain-to-source bias voltage         |

| $V_G, V_{GS}, V_g$    | Gate-to-source bias voltage                  |

| V <sub>max</sub>      | Maximum voltage                              |

| $V_T$ , $V_{th}$      | Threshold voltage                            |

| $W_{ch}$              | Channel width                                |

## **ABBREVIATIONS**

| 1D       | One-dimensional                                  |

|----------|--------------------------------------------------|

| 2D       | Two-dimensional                                  |

| 3D       | Three-dimensional                                |

| AFM      | Atomic force microscope                          |

| ALD      | Atomic layer deposition                          |

| BEOL     | Back-end-of-line                                 |

| BG       | Back-gate                                        |

| BN       | Boron nitride                                    |

| BNNT     | Boron nitride nanotube                           |

| BOE      | Buffered oxide etchant                           |

| BP       | Black phosphorus                                 |

| CNT      | Carbon nanotube                                  |

| CVD      | Chemical vapor deposition                        |

| DC       | Direct current                                   |

| DFT      | Density functional theory                        |

| DI       | De-ionized                                       |

| EBL      | Electron-beam lithography                        |

| EDS, EDX | Energy-dispersive X-ray spectroscopy             |

| FET      | Field-effect transistor                          |

| FFT      | Fast Fourier transform                           |

| GVT      | Growth vapor trapping                            |

| HAADF    | High-angle annular dark-field                    |

| h-BN     | Hexagonal boron nitride                          |

| HOPG     | Highly oriented pyrolytic graphite               |

| HRTEM    | High-resolution transmission electron microscope |

| IC       | Integrated circuit                               |

| ID       | Inner diameter                                   |

| LPE      | Liquid-phase exfoliation                         |

| MIS      | Metal-insulator-semiconductor                    |

| MS     | Metal-semiconductor                       |

|--------|-------------------------------------------|

| MWCNT  | Multi-walled carbon nanotube              |

| NW     | Nanowire                                  |

| PLD    | Pulsed laser deposition                   |

| PMMA   | Polymethyl methacrylate                   |

| PVP    | Polyvinylpyrrolidone                      |

| PVT    | Physical vapor transport                  |

| RTA    | Rapid thermal annealing                   |

| SAED   | Selected area electron diffraction        |

| SEM    | Scanning electron microscope              |

| SHE    | Self-heating effect                       |

| SS     | Subthreshold swing                        |

| STEM   | Scanning transmission electron microscope |

| SWCNT  | Single-walled carbon nanotube             |

| TDMAHf | Tetrakis(dimethylamido)hafnium(IV)        |

| TEM    | Transmission electron microscope          |

| TG     | Top-gate                                  |

| TLM    | Transfer length method                    |

| TMD    | Transition metal dichalcogenide           |

| TMIn   | Trimethylindium                           |

| TR     | Thermo-reflectance                        |

| vdW    | van der Waals                             |

| vdWE   | van der Waals epitaxy                     |

| YFM    | Y-function method                         |

|        |                                           |

## NOMENCLATURE

| [(CH <sub>3</sub> ) <sub>2</sub> N] <sub>4</sub> Hf | Tetrakis(dimethylamido)hafnium(IV) |

|-----------------------------------------------------|------------------------------------|

| Al <sub>2</sub> O <sub>3</sub>                      | Aluminum oxide                     |

| Ar                                                  | Argon                              |

| Au                                                  | Gold                               |

| В                                                   | Boron                              |

| BN                                                  | Boron nitride                      |

| CdS                                                 | Cadmium sulfide                    |

| CdTe                                                | Cadmium telluride                  |

| CuInP <sub>2</sub> S <sub>6</sub>                   | Copper indium thiophosphate        |

| FeO                                                 | Iron(II) oxide                     |

| GaN                                                 | Gallium nitride                    |

| Ge                                                  | Germanium                          |

| HfO <sub>2</sub>                                    | Hafnium oxide                      |

| I <sub>2</sub>                                      | Iodine                             |

| In(CH <sub>3</sub> ) <sub>3</sub>                   | Trimethylindium                    |

| In <sub>2</sub> O <sub>3</sub>                      | Indium oxide                       |

| $In_2Se_3$                                          | Indium selenide                    |

| InAs                                                | Indium arsenide                    |

| InP                                                 | Indium phosphide                   |

| MgO                                                 | Magnesium oxide                    |

| MgCl <sub>2</sub>                                   | Magnesium chloride                 |

| Mo                                                  | Molybdenum                         |

| $MoS_2$                                             | Molybdenum disulfide               |

| MoSe <sub>2</sub>                                   | Molybdenum diselenide              |

| MoTe <sub>2</sub>                                   | Molybdenum ditelluride             |

| $N_2H_4$                                            | Hydrazine hydrate                  |

| Na <sub>2</sub> TeO <sub>3</sub>                    | Sodium tellurite                   |

| NaOH                                                | Sodium hydroxide                   |

| NH <sub>3</sub>                                     | Ammonia                            |

|                                                     |                                    |

| Ni                | Nickel                 |

|-------------------|------------------------|

| NiGe <sub>2</sub> | Nickel germanide       |

| PbSe              | Lead selenide          |

| S                 | Sulfur                 |

| Se                | Selenium               |

| $SF_6$            | Sulfur hexafluoride    |

| Si                | Silicon                |

| SiO <sub>2</sub>  | Silicon dioxide        |

| $SnO_2$           | Tin(IV) oxide          |

| TaSe <sub>3</sub> | Tantalum triselenide   |

| Te                | Tellurium              |

| W                 | Tungsten               |

| $WS_2$            | Tungsten disulfide     |

| WSe <sub>2</sub>  | Tungsten diselenide    |

| ZnO               | Zinc oxide             |

| ZrTe <sub>3</sub> | Zirconium tritelluride |

## ABSTRACT

As the miniaturization of the transistors in integrated circuits approaches the atomic scale limit, novel materials with exceptional performance are desired. Moreover, to conduct enough current with an ultrathin and small-scale body, high drain current density is preferably required. Nevertheless, devices may suffer seriously from self-heating effect (SHE) with high drain bias and current if the generated heat cannot be dissipated efficiently. In this thesis, we introduce two material systems and several techniques to accomplish the demand without SHE. Tellurium, as a van der Waals material composed by atomic helical chains, is able to realize its one-dimensional structure. We illustrate that the cross-sectional current density of 150 MA/cm<sup>2</sup> is achieved through boron nitride nanotube (BNNT) encapsulation without SHE due to the superior thermal conductivity of BN. With the nanotube encapsulation technique applied, one-dimensional tellurium nanowire transistors with diameter down to 2 nm are realized as well, and single tellurium atomic chain is isolated. Furthermore, atomic-layer-deposited indium oxide  $(In_2O_3)$  as thin-film transistors exhibit even better current carrying capacity. Through co-optimization of their electrical and thermal performance, drain current up to 4.3 mA/µm is achieved with a 1.9-nm-thick body without SHE. The alleviation of SHE is due to a) the high thermal conductivity of the substrate assisting on efficiently dissipating the generated thermal energy, b) SHE avoidance with short-pulse measurement, and c) interface engineering between the channel stack and the substrate. These two material systems may be the solid solution to the desire of high current density transistors in the post-Moore era.

## 1. INTRODUCTION

#### 1.1 Overview

#### 1.1.1 Motivations

Transistors are the working unit on an integrated circuit (IC) which is the operational center and one of the most important components of our cellphones and laptops. To make these electronic devices achieve better performance and more efficient task processing capability, more transistors are required to be integrated together per unit area. That is to say, efforts are made to increase the transistor density by miniaturizing their physical size as the well-known Moore's Law [1] predicted. In the recent years, the leading semiconductor corporations dedicate themselves to developing 7-nm, 5-nm, even 3-nm technology nodes. However, this trend cannot be eternal since not only it is approaching the atomic scale limit but we are losing electrostatic control so that the transistors can hardly be turned off. Moreover, as we downsize the transistor dimension, it requires higher current density to conduct enough current. Therefore, material candidates which can plausibly be considered in the post-silicon era beyond Moore's Law are widely investigated.

In this chapter, some of these potential materials including graphene, transition metal dichalcogenide (TMD), black phosphorus (BP), tellurium (Te), and indium oxide ( $In_2O_3$ ) will be discussed. More details will be covered with the last two since they are more comprising in many aspects. At the last part of this chapter, self-heating effect (SHE) will be introduced as a challenge of employing  $In_2O_3$  as the channel material in high-current transistor applications.

#### 1.1.2 Graphene

Graphene is few layers or even one layer of graphite possessing a layered structure where has van der Waals interaction between layers and  $sp^2$ -hybrized covalent bonds within a single layer. Mechanical exfoliation method can be applied as the van der Waals interaction is much weaker than covalent bonds, and it turns out that graphene became the first 2D material that realized single layer structure.

Since the discovery of graphene in 2004, global attention has been attracted due to its superb properties [2]–[5]. Monolayer graphene, as a semi-metallic 2D material, exhibits extremely

high mobility of  $2.5 \times 10^5$  cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> at room temperature [6]. The electric transport of graphene is governed by Dirac's relativistic equation since its charge carriers are massless Dirac fermions [7]. On the other hand, despite of the excellent physical properties of graphene, the lack of bandgap appears as a crucial fundamental challenge in its electronic applications. Without a bandgap, graphene has poor electrostatic control. Consequently, more attention was attracted by another layered 2D material family, TMDs, to overcome the downside and further explore the transistor technology.

#### **1.1.3** Transition Metal Dichalcogenides

The TMD family, including molybdenum disulfide (MoS<sub>2</sub>), molybdenum diselenide (MoSe<sub>2</sub>), molybdenum ditelluride (MoTe<sub>2</sub>), tungsten disulfide (WS<sub>2</sub>), tungsten diselenide (WSe<sub>2</sub>), and more, is a group of materials which share similar chemical formula of MX<sub>2</sub> where M represents transition metal such as molybdenum (Mo), tungsten (W) and X stands for chalcogen such as sulfur (S), selenium (Se), and tellurium (Te). Typically, a single layer of TMD consists of one layer of transition metal atoms sandwiched and covalently bonded by two layers of chalcogen atoms. As alternative layered 2D materials, they are widely studied after graphene especially on their electrical properties and applications [8]–[12].

The first realization of transistors based on TMDs can be tracked back to 2007 where molybdenum disulfide (MoS<sub>2</sub>) was employed [8]. MoS<sub>2</sub> has an indirect bandgap of 1.2 eV in the bulk form and a direct bandgap of 1.8 eV in monolayers [13]. The existence of bandgap makes the TMD material system fundamentally different from graphene and able to be applied to a variety of fields including field-effect transistors, integrated circuits, and photonic detectors [10], [12], [14]–[16]. Decent device performance of MoS<sub>2</sub> transistors was accordingly reported: drain current being as high as several hundred mA/mm, ON–OFF current ratio being up to over 8 orders of magnitude, and subthreshold swing (SS) down to 74 mV/dec [9], [17], [18].

Nevertheless, a serious drawback of TMDs is that the carrier mobility is reasonably low mainly due to the large effective mass of carriers, which restrains this material system on competitiveness with some other 2D material possessing at least one order higher of mobility such as black phosphorus (BP) and tellurium.

## 1.1.4 Black Phosphorus

Black phosphorus (BP) is an elemental material with layered 2D structure similar to graphene and TMDs. The realization of single layer BP and its transport behavior was reported in 2014 through mechanical exfoliation technique [19], [20]. BP has a narrower bandgap (0.3 eV in bulk form) and reveals much higher hole mobility up to approximately  $300 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  [19].

In spite of the excellent transport properties and application potentials of BP, the instability of phosphorene (few-layer BP) turns out to be a significant drawback in terms of realistic applications. It was reported that the electrical performance of BP field-effect transistor (FET) starts to degrade in tens of minutes upon exposure in ambient environment due to its strong affinity for moisture [21]. In order to further explore new electronic materials for beyond Moore's law device applications, researchers are looking for other novel material systems which master all the aforementioned downsides.

#### 1.2 Tellurium

#### **1.2.1** Introduction to Tellurium

Tellurium (Te) is a chalcogen group-VI element and well known as low-dimensional and anisotropic elemental semiconductor materials. It presents attracting properties including piezoelectricity [22]–[24], photoconductivity [25], and thermoelectricity [26], [27]. Besides, Te has a small band gap (0.35 eV in bulk form) under room temperature and performs exceptionally high field-effect mobility (around  $10^3 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ ) [28], which makes it more intriguing for electronic applications. Moreover, unlike graphene which has zero bandgap, TMDs which show relatively low carrier mobilities, and BP which is unstable in ambient environment, Te is free of these drawbacks and therefore becoming a more promising nanomaterials showing strong potential in electric applications.

Despite of the outstanding physical properties, synthesis method of high-quality thin films and nanowires are rarely reported. In recent years, we proposed a solution-based and substratefree strategy of growing 2D Te (tellurene) [28] and a physical vapor transport method with nanotube encapsulation of synthesizing controllable number of atomic Te chains [29]. These steady synthetic methods of tellurene and Te nanowires (NWs) provide reliable access to the materials and broaden the way to studying its intrinsic physical properties and developing technological applications. More details will be introduced in chapter 2.

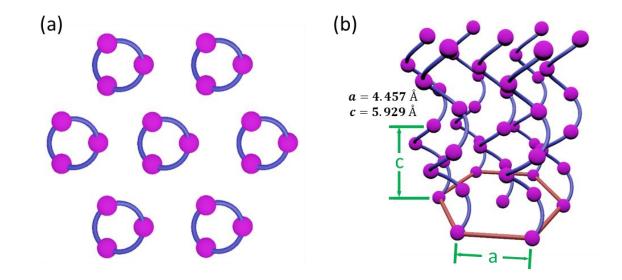

In the atomic structure of crystalline, Te as a chalcogen has a one-dimensional (1D) spiral chain structure. Figure 1.1(a) and 1.1(b) show the atomic structure of the top-view and side-view of Te lattice, respectively. Each tellurium atom is covalently bonded with the two nearest adjacent atoms along the *c*-axis forming helical chain structure, and different chains stack with each other by van der Waals force forming a hexagonal crystal structure on the projection of basal plane.

Figure 1.1. Schematic illustration of the atomic structure of tellurium. (a) Top view and (b) side view of a hexagonal crystal structure.

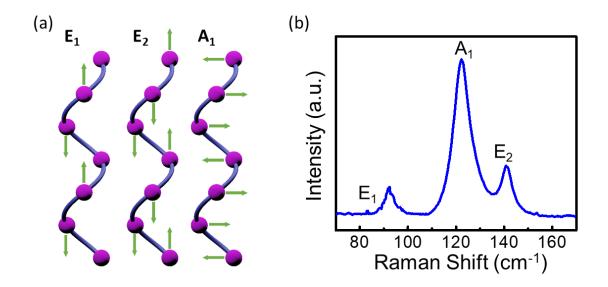

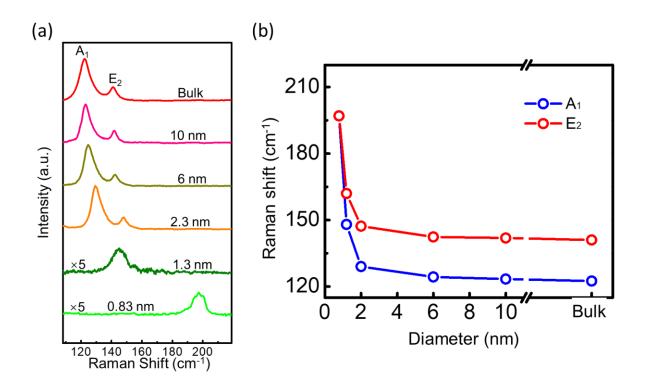

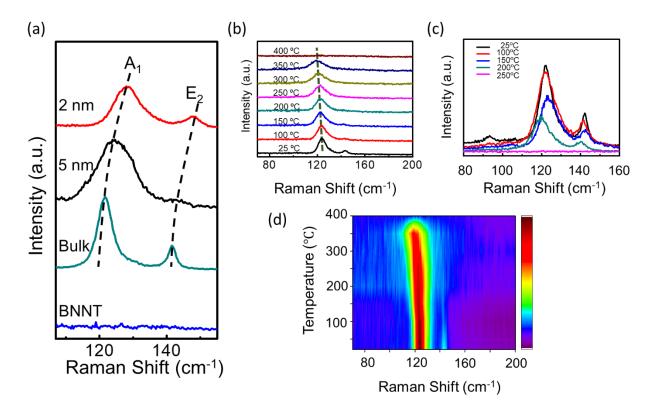

As a powerful nondestructive characterization tool, Raman spectroscopy has been widely used to investigate material properties and layer-to-layer even chain-to-chain interactions, through lattice vibrations [30]. Figure 1.2(a) illustrates the vibration pattern of Raman modes. The A<sub>1</sub> mode is caused by the chain expansion where each atom moves in the basal plane, whereas the E<sub>1</sub> and E<sub>2</sub> modes represent the bond-bending and bond-stretching with larger admixture, respectively [31]. Figure 1.2(b) exhibits a typical Raman spectroscopy of bulk Te crystal with three first-order Raman active modes E<sub>1</sub>, A<sub>1</sub>, and E<sub>2</sub> located at 92 cm<sup>-1</sup>, 123 cm<sup>-1</sup> and 140 cm<sup>-1</sup>, respectively, which experimental results are in great agreement with theoretical analysis [31], [32].

Figure 1.2. Typical Raman spectroscopy of bulk Te samples. (a) Schematic illustration and (b) an experimental Raman response showing 3 first-order Raman active modes.

#### 1.2.2 Synthesis Methods

There are many different synthesizing strategies reported to grow 2D Te with advantages and disadvantages. In this section, we will introduce several methods either in literature or proposed by ourselves.

#### **Pulsed Laser Deposition**

A significant challenge for the growth of Te thin film is scalability. Being applicable for mass productivity, synthesis methods providing large-area growth of 2D thin films are more preferable in a variety of realistic applications. Pulsed laser deposition (PLD) was reported to achieve centimeter-scalability of 2D Te deposition with thickness ranging from 2.7 to 6 nm on single crystalline magnesium oxide (MgO) substrate under room temperature and vacuum environment [33]. The thickness of the deposited Te films could be controlled by tuning the number of pulses applied. MgO was considered as a satisfactory growth substrate due to its affordability and chemical inertness. It is further shown that Te could grow vertically with the *c*-axis perpendicular to the MgO (100) surface through another scalable approach, magnetron sputtering [34], which will be discussed in the next sub-section.

Since the intra-chain covalent bonds between adjacent Te atoms along *c*-axis are much stronger than the inter-chain vdW interactions along *a*-axis, the surface free energy of basal plane is three times higher than other planes in the growth intermediate [35]. As a result, large-area Te thin film deposition tends to establish thicker flakes rather than ultrathin films. In PLD method, 248 nm laser was utilized to provide high kinetic energy to the Te source, and the atoms and ions in the plasma plume deposited on the lying substrate. PLD therefore is able to provide a growth route for tellurene with thickness as thin as 2.7 nm.

#### **Physical Vapor Deposition**

Although PLD technique indicates a scalable approach of depositing large-area Te thin films, ultrathin films are desirable as 2D materials usually manifest intriguing physical properties such as monolayer graphene [27]. PVD delivers an alternative procedure to grow thinner 2D Te films down to 0.85 nm, corresponding to three layers of Te atoms [33]. A two-zone furnace was used to provide temperature gradient during the process: Te source was placed at the hot end at 650 °C and silicon with 300 nm silicon oxide (SiO<sub>2</sub>/Si) substrate was positioned at the cold end (room temperature) and downstream. Argon with 15 % hydrogen was chosen as the carrying gas to deliver tellurium vapor from the source to the substrate. The dimension of the flakes is typically around 10–100  $\mu$ m.

SiO<sub>2</sub>/Si is a widely used substrate due to its high commercial availability and affordability. However, the surface cleanness and the lack of dangling bonds make it a challenge to be applied as an outstanding template for tellurene growth. Crystal nucleus are required for the formation of ultrathin 2D Te films in PVD method, which brings uncertainties to the synthetic strategy.

On the other hand, the aforementioned attributes conduct some advantages in some situations. Van der Waals epitaxy (vdWE), a novel growing strategy, makes use of chemically inert substrates such as fluorophlogopite mica [36] to synthesize a variety of materials including graphene [37], indium selenide (In<sub>2</sub>Se<sub>3</sub>) [38], and TMD flakes [39]. This method with mica as the growth substrate was applied to synthesize hexagonal 2D Te films [40] as it not only tolerates larger lattice mismatch but also eases the relocation of Te adatoms along the substrate surface. In this method, Te source and mechanically cleaved fluorophlogopite mica sheets were placed in a sealed quartz tube which was evacuated to provide oxygen-free environments. A horizontal furnace was utilized to carry out the reaction by heating the source side at 750 °C and the cooling

side at 500 °C for 1 hour. The resulting tellurene flakes on mica appear in hexagonal shapes with typical lateral length in micrometer range and thickness being 30–80 nm. With mica as a mechanically flexible growth substrate, vdWE reveals great application potential in wearable devices.

#### **Magnetron Sputtering**

With its chain-based crystal structure, Te is an anisotropic elemental material. Therefore, the controllability of orientation becomes an interesting topic in material growth and property measurement. It was described that the orientation of Te atomic chains could be managed in a magneton sputtering method through selecting variant substrates as growing templates [34]. Besides, the sputtering is scalable in centimeter range, and the thickness of 2D Te films is down to 2.5–20 nm. This novel sputtering approach widens the avenues for the study of orientation controllability of this material system.

In this method, a home-built external electromagnet (magnetic field up to 500 G perpendicular to the substrate surface) was employed to grow 2D Te films on highly oriented pyrolytic graphite (HOPG), MgO (100), and hexagonal boron nitride (h-BN) substrate. The Te source was sputtered by Ar with a power of 14 W. The sputtered Te thin films express contrasting orientation on the substrates: HOPG and h-BN have the *c*-axis parallel to the surface whereas MgO has it perpendicular to the surface. The directionality of the standing Te helical chains on MgO surface is relatively rare to be reported.

#### Liquid Phase Exfoliation

Due to the relatively weak vdW interactions between adjacent atomic layers in layered 2D material systems, mechanical exfoliation is widely used as a simple technique to obtain thinner 2D flakes [41]–[44]. Liquid-phase exfoliation (LPE), on the other hand, utilizes organic solvent such as IPA to break the vdW interactions and exfoliate the materials into smaller pieces and is applied to a variety of material systems [45]–[48]. Tellurene flakes obtained by LPE was reported as well [49]. In this method, bulk Te powder was ground with IPA for 30 minutes to squash the larger particles into smaller ones, and the materials along with the solvent were treated sequentially with probe sonication in Ar environments for 5 hours, bath sonication for 8 hours, centrifugation under 1000 g and 6000 g for 30 minutes each, and dried in a vacuum oven at room temperature for 6

hours. The thickness and the lateral length of the obtained 2D Te flakes were 5.1–6.4 nm and 41.5–177.5 nm, respectively.

#### **Thermal Evaporation**

The report of Te transistors based on evaporation can be tracked back to 1961 which grows Te thin films down to 50 nm with Hall mobility being around  $10 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  [50]. After more than half century, high-performance FETs with great switching characteristics based on evaporated Te thin films were achieved [51]. With the substrate temperature down to -80 °C by cooled nitrogen gas flow, the average domain area of the polycrystalline Te thin films on the substrate becomes as large as around 25  $\mu$ m<sup>2</sup>. The average grain size of the thin films increases as the substrate temperature decreases from room temperature and saturates at around -80 °C. Polarized light microscopy was manipulated to exhibit the domains due to the absorption dependence of the angle between the light polarization and Te helical chains. The thickness of the thin films was controllable and can be down to 4 nm.

#### **Solution-Based Growth**

In order to gain insights on electrical device technology, the following attributes are desirable for tellurene synthesis methods: large scalability, high reproducibility, substrate independence, thinner films achievability, and excellent electric transport performance. In 2018, we proposed a solution-based, substrate-free method that satisfies these properties [28], which provides a reliable production of tellurene flakes down to monolayer for the exploration of 2D material technology. In this method, hydrazine hydrate (N<sub>2</sub>H<sub>4</sub>) was used to reduce sodium tellurite (Na<sub>2</sub>TeO<sub>3</sub>), with polyvinylpyrrolidone (PVP) as crystal-face-blocking ligands, in alkaline solution under 160–200 °C. The resultant 2D Te flakes in the solution are typically around 50-100  $\mu$ m in lateral dimension and transferrable through a Langmuir-Blodgett process [52] or an ink-jet printing method [53].

The mole ratio of  $Na_2TeO_3$  to PVP plays a significant role in the synthesis of tellurene. The productivity increases as reaction time passes and gradually saturates after a period of 30 hours. By detailed observations on the relationships between the mole ratio and productivity growing curves, it is distinguishable that it takes a longer time for the tellurene flakes to appear when the ratio of PVP is larger. On the other hand, smaller mole ratios of PVP develop lower ultimate

productivity. Regardless of PVP concentration, the preliminary products are dominant by tellurium nanowires. The intermediate between 1D and 2D form emerges after a period of time, and tellurene flakes show up as final products. On account of the growing mechanism, this synthesis method provides reliable routes to not only 2D tellurene flakes but also 1D Te nanowires. The diameter of the nanowires can be down to 6 nm or thinner [28]. FET based on its 1D NWs will be exhibited in chapter 2.

Moreover, tellurene flakes from monolayer to 10 nm thickness are derivable by a solventassisted post-growth thinning process as follows: a certain ratio of tellurene solution, sodium hydroxide (NaOH) solution, and acetone were mixed and placed in ambience under room temperature for 2–10 hours, followed by a centrifugation process at 5000 rpm for 5 minutes. Thinner tellurene flakes could be obtained for a longer period of time. Due to the absence of PVP shielding, the alkaline solution reacts with the tellurene flakes.

#### **Physical Vapor Transport**

Polycrystalline materials, composed by many crystal grains with different orientation, are used in a variety of applications since they are more economically efficient and easier to be grown into large area. For instance, most of the current commercially available solar panels, due to these advantages, are utilizing thin film polycrystalline materials including silicon [54], cadmium sulfide [55], cadmium telluride [56], copper indium gallium selenide [57], and more.

Similar to layered two-dimensional (2D) materials which can be mechanically exfoliated by scotch-tape method to obtain thinner flakes, thin films of Te with 2D atomic structure can be realized through the same methodology. Even though Te has exhibited many attracting capabilities in a variety of fields and many methods of growing single crystalline Te have widely been reported [28], [58]–[60], the synthesis and property exploration of polycrystalline thin films are relatively deficient [61]–[63]. We synthesized mm-scale hexagonal polycrystalline Te thin film by PVT under high-vacuumed environment (10<sup>-5</sup> torr). Interestingly, the material forms in hexagonal shapes even being polycrystalline microscopically. The Raman response, surface roughness, and electrical transport properties of its thin films with variant thickness are studied. Polycrystalline Te shows little thickness-dependence compared to single crystal. Moreover, both electrical transport measurement and phonon response show strong isotropy in polycrystalline Te which is very different from single crystal. On the other hand, polycrystalline Te performs clear thickness dependence on mobility and ON–OFF ratio measurements, where the latter is similar to single crystal but the former is lower. The 2D Te thin films can be mechanically exfoliated to achieve sub 10-nm thickness, and the surface roughness of the resultant Te flakes is almost the same as layered 2D materials such as graphene.

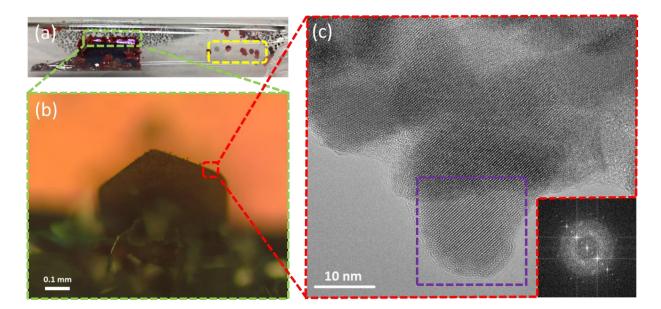

We demonstrate the synthesis of high quality polycrystalline Te in mm scale, as Figure 1.3(a) shows, by PVT method. 144 mg of Te powder (Sigma-Aldrich, 99.99 %) and a 6 mm by 20 mm silicon substrate with 300 nm SiO<sub>2</sub> were placed in separate regions and sealed under high vacuum ( $10^{-5}$  mbar) in a quartz ampoule. The whole system was then heated rapidly at a rate of 10 °C/min to 900 °C (source) / 800 °C (sink) and kept for 24 hours. Tellurium atoms were vaporized in the high temperature environment and moving around in the sealed quartz ampoule. Due to the temperature gradient, they tend to crystallize at the other end of the ampoule. Consequently, hexagonal polycrystalline Te films in mm scale were grown on both sidewalls of substrate and inner wall of the sealed ampoule after the furnace is cooled naturally back to room temperature. Figure 1.3(b) which was taken by optical microscopy shows that a hexagonal shape can be clearly observed even though it is grown on the sidewall of the SiO<sub>2</sub>/Si substrate.

Figure 1.3. As-grown 2D tellurium through PVT. (a) Hexagonal van der Waals 2D Te flakes grown on the inner wall of the sealed ampoule and (b) sidewalls on the SiO<sub>2</sub>/Si substrate (c) TEM image and the inset shows the corresponding FFT image of the area squared by the purple dashed lines.

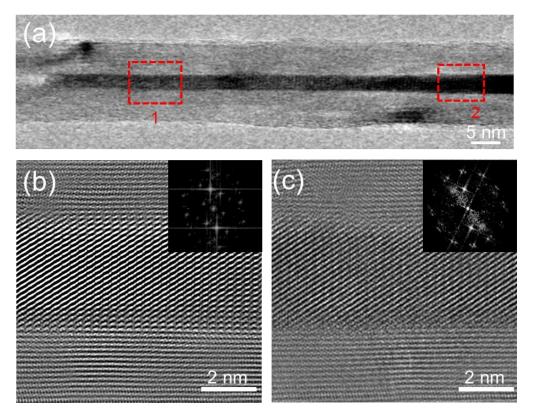

As a powerful tool to realize the material structure in atomic scale, high resolution transmission electron microscopy (HRTEM) was utilized to confirm the atomic structure of the synthesized polycrystalline Te. Sample preparation of HRTEM was realized by a wet-transfer method: As grown polycrystalline Te films were mechanically exfoliated by scotch-tape method and transferred onto SiO<sub>2</sub>/Si substrate. PMMA was spin-coated onto the substrate with 2500 rpm, followed by baking at 180 °C for 2 minutes. The substrate with exfoliated Te flakes and PMMA was soaked in buffered oxide etchant (BOE) for 6 hours to thoroughly etch silicon dioxide, and the thin film of PMMA with materials was separated with the substrate and floated on BOE. A copper grid with lacey carbon support film (Agar Scientific) was utilized to fish up the floating PMMA film. The grid with the film was cleaned by DI water, baked dry at 150 °C, soaked in acetone for 15 minutes to dissolve PMMA, and baked dry again at 150 °C for 30 minutes.

HRTEM was performed with FEI Talos F200x operated at 200 kV of electron acceleration voltage. The images of the materials are shown in Figure 1.3(c), and the inset of each TEM is the fast Fourier transform (FFT) pattern of the area squared by purple dashed lines. We can clearly observe single grains on the edge and in the middle of the Te films.

#### **1.2.3** Physical Properties

#### **Optical Properties**

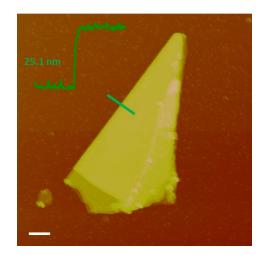

Due to the non-destructive property, Raman spectroscopy has been widely utilized to explore the structure of materials through lattice vibration and deformation. As grown polycrystalline Te films were mechanically exfoliated by scotch-tape method and transferred onto SiO<sub>2</sub>/Si substrate. Raman measurements were performed using a Horiba LabRAM HR800 Raman spectrometer with a He-Ne excitation laser of 633 nm wavelength. In order to investigate the thickness dependence, mechanically exfoliated Te flakes with variant thickness were obtained by scotch-tape method and transferred onto SiO<sub>2</sub>/Si substrate for Raman spectroscopy characterization. Figure 1.4 shows a representative flake with thickness of 25.1 nm confirmed by atomic force microscope (AFM). The thickness dependence and anisotropy of Raman spectrum of single crystal Te synthesized by a substrate-free solution process have been studied and reported [28]. Nevertheless, we found both of these characteristics to be obviously different in polycrystalline Te as shown in Figure 1.5(a). The E<sub>1</sub>-TO peaks at around 94 cm<sup>-1</sup> disappear

regardless of thickness here. Furthermore, the pick shift caused by thickness variance of polycrystal Te is much more immune than single crystal films. For instance, the blueshift in  $A_1$  mode from thickness of ~25 nm to ~6 nm is 9.4 cm<sup>-1</sup> in single crystal but only 3.7 cm<sup>-1</sup> for polycrystal. We further studied the isotropy of the flake by Raman spectroscopy with different incidental polarization. The phonon response was collected every 30 degrees, and the 12 resultant patterns, as Figure 1.5(b) shows, almost perfectly coincide with each other throughout the whole measured range. The representative peak value of  $A_1$  of the curves were extracted and plotted into a circular system in Figure 1.5(c). The difference between the maximum and minimum is less than 5 % for all of the obtained data.

Figure 1.4. AFM image of a typical 2D Te flake with a thickness of 25.1 nm grown by PVT. The scale bar is 1 µm.

#### **Electrical Properties**

In order to study the electric transport properties, angle-resolved two-terminal devices with 1  $\mu$ m channel length on a silicon wafer with 300 nm thermally grown SiO<sub>2</sub> as the gate dielectric were fabricated. Metal electrodes of source and drain regions were patterned by electron beam lithography (EBL) and grown by electron beam evaporation of 20 nm Ni and 50 nm Au, followed by a lift-off process. The devices were measured with a probe station connected to semiconductor characterization system (4200SCS, Keithley) at room temperature. The metal electrodes were designed to be Ni/Au with thickness of 20/50 nm.

The designed device structure is visualized in Figure 1.6(a). To further confirm the isotropy of the polycrystalline material, angle-resolved DC conductance measurements were performed by patterning metal electrodes with variant angles on the same flake with the same channel length of 3  $\mu$ m. The values of on-state current were extracted and arranged to Figure 1.6(b), and the inset is a false-colored SEM image of a representative device. It is clear that regardless of the orientation of measurement, the on-state current value consistently falls in a small range, confirming the isotropy in electric transport properties.

Figure 1.5. Raman spectroscopy of polycrystalline Te thin film. (a) Thickness dependence of Raman spectroscopy on 2D Te flakes and (b, c) angle-resolved (between crystal orientation and incident laser polarization) Raman spectra for the 2D Te flake.

Figure 1.6. (a) Visualization of the designed device structure and (b) the isotropy of electric transport performance. The inset is the a false-colored SEM image of a measured device with the scale bar to be 3  $\mu$ m.

To further study the transport performance, we designed short channel devices with 300 nm channel length and 300 nm SiO<sub>2</sub> as the gate dielectric. Figure 1.7(a) and (b) show the output and transfer characteristic of a polycrystalline Te device, respectively. The on-state current reaches approximately 10 mA/mm at  $V_{DS} = 1$  V.

Figure 1.7. Electrical measurement of 2D Te short channel devices. (a) Output characteristic and (b) transfer characteristic of a device with 300 nm channel length and 12.7 nm channel thickness.

We investigated more than 20 devices with different thickness of the films, extracted the ON–OFF ratio and intrinsic mobility, and plotted the results in Figure 1.8(a). As a small-bandgap semiconductor material, the ON–OFF ratio is as expected and consistent with single crystal Te grown by solution-based method [28]. On the other hand, the measured hole mobility is lower than single crystal Te since a single flake of polycrystalline Te is composed of small grains. Both the variant orientation of the grains and junctions between the grains of the polycrystal contributed to the low mobility of the device performance. Besides, the trade-off of two key parameters, on-state current and ON–OFF ratio, was statistically arranged into Fig. 1.8(b). Clear dependence which is consistent with expectations of negative slope is observed.

Figure 1.8. Statistical plot of (a) relation between on-current and ON–OFF ratio and (b) relation between ON-current and ON–OFF ratio.

### 1.3 Indium Oxide

#### **1.3.1** Introduction to Indium Oxide

Being widely applied as channel materials for thin-film transistors (TFT) and potentially for back-end-of-line (BEOL) compatible monolithic three-dimensional (3D) integration, oxide semiconductors have received extensive attention and been broadly explored in the past years [64]–[72]. Among them, indium oxide (In<sub>2</sub>O<sub>3</sub>) [64]–[66] and doped indium oxides [67]–[70] are

even of great interests because of their exceptional properties including high growth scalability and reproducibility to enable mass production, atomically smooth roughness to guarantee the surface quality, ambient stability to achieve little material degradation in air, and low thermal budget to be well suited with BEOL technologies.

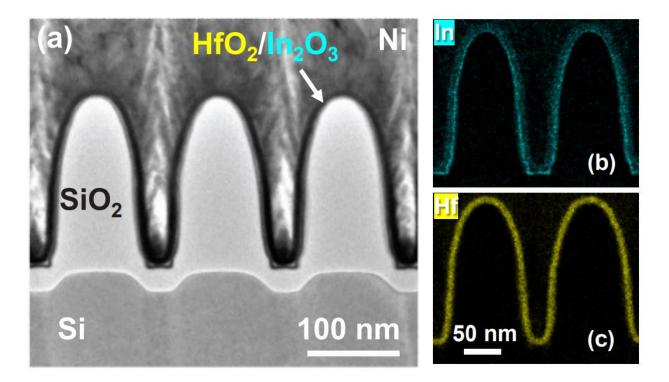

Given its roughly 2.7 eV bandgap [72],  $In_2O_3$  as an oxide semiconductor has attracted revived attention as a promising channel material. Especially, the conformal growth of the atomiclayer-deposited (ALD)  $In_2O_3$  enables it to form on uneven surfaces including side walls and deep trenches, which dramatically benefits the monolithic 3D integration [64], [65], [73]–[76]. Moreover, as the physical size of transistors in integrated circuits becomes smaller according to Moore's law, it requires higher current density for a single device to conduct enough current. It has been reported that scaled back-gate (BG)  $In_2O_3$  transistors accomplish channel thickness (T<sub>ch</sub>) down to 0.7 nm [64] and drain current (I<sub>D</sub>) up to 2.2 A/mm in enhancement mode as 1.5-nm-thick  $In_2O_3$  acts as the channel [66], [77].

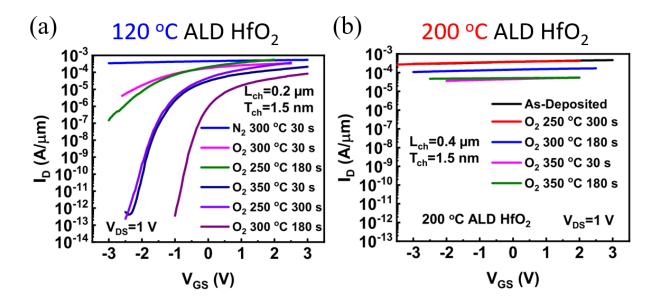

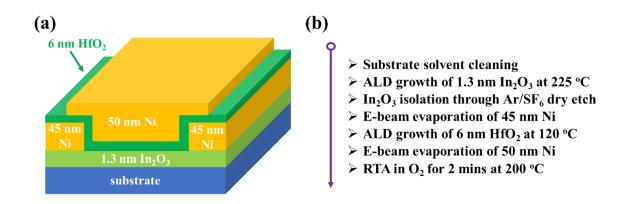

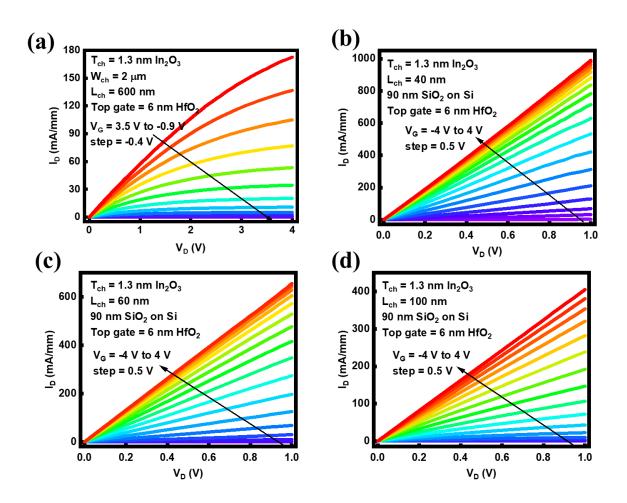

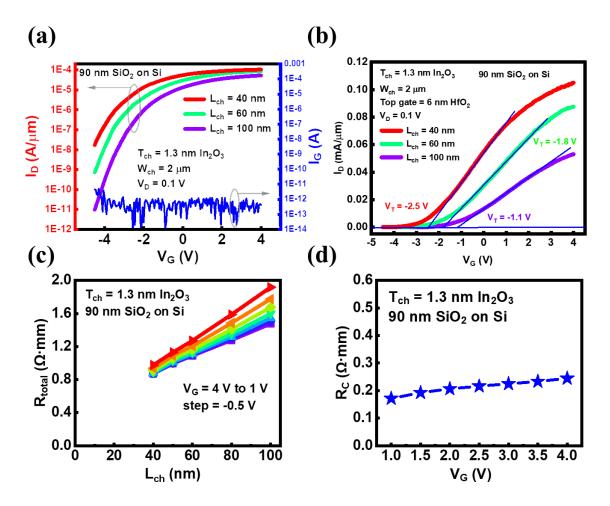

Nevertheless, the investigations of the  $In_2O_3$  devices mostly focus on BG structure [64]– [66]. Top gate (TG)  $In_2O_3$  transistors are rarely explored, even though TG devices are particularly demanded in many practical integration applications. The challenges for top-gate devices are due to a) the performance degradation of  $In_2O_3$  channel after the growth of the high- $\kappa$  oxide gate dielectric and b) the drastic self-heating effect (SHE) as the current density becomes higher under high voltage biases. For the former, it is proposed that the oxygen atoms in the  $In_2O_3$  layer are lost and taken away as the ALD hafnium oxide (HfO<sub>2</sub>) is formed, which intensely generates more oxygen vacancies in the  $In_2O_3$  channel and increases the OFF-state current value [78]. Fortunately, this is resolvable by lowering the growth temperature of HfO<sub>2</sub> from 200 °C to 120 °C followed by a low-temperature RTA treatment in O<sub>2</sub> environment. However, the latter remains as a bottleneck for its TG transistor applications. In order to address the thermal issues, several techniques will be discussed and demonstrated in great details in chapter 3 to chapter 5.

#### **1.3.2** Thin-Film Growth through Atomic Layer Deposition

Atomic layer deposition (ALD) is a significant and useful thin-film deposition technique which will be employed to grow  $In_2O_3$  as the ultra-thin semiconducting channel and hafnium oxide (HfO<sub>2</sub>) as the high-*k* dielectric layer (where *k* represents dielectric constant) in chapter 3 to 6.

In a typical process of ALD, the chamber is vacuumed and maintained at a certain growth temperature (generally lower than 250–300 °C) where the substrate surface is exposed. After the pressure and temperature of the environment is stabilized, gaseous precursors flow into the chamber in a sequential and alternative manner. The precursor bottles are kept at a desired and stable temperature as well so that the vapor pressure is well controlled, and the precursor reactants are skillfully chosen or designed to adsorb on the substrate surface, react but self-limit to only leave a layer of the target element atoms on the surface. An exposure of both precursors (or more in relatively few cases) is regarded as one ALD cycle, and the more cycles are executed, the thicker the resultant film is. Therefore, by appropriately choosing the number of ALD cycle, the thickness of the synthesized thin-film can be precisely controlled even down to angstrom order with a stable ALD system. The In<sub>2</sub>O<sub>3</sub> thin films in this dissertation are all grown by ALD, and more details will be covered in the following chapters.

# 2. TELLURIUM NANOWIRE WITH HIGH CURRENT DENSITY

# 2.1 Introduction to Tellurium Nanowire

Given the chain-based crystal structure, Te is a one-dimensional (1D) van der Waals (vdW) material. Naturally, a Te atom covalently bonds with its two neighboring atoms and forms a helical atomic chain parallel to the [0001] direction (c-axis), and the atomic chains pack with each other by van der Waals (vdW) interactions to form a hexagonal lattice structure.

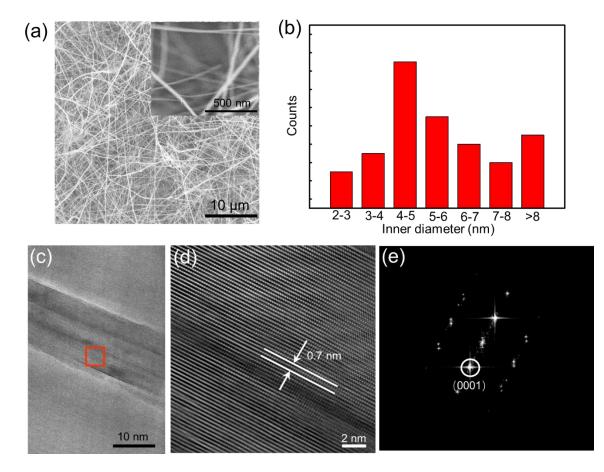

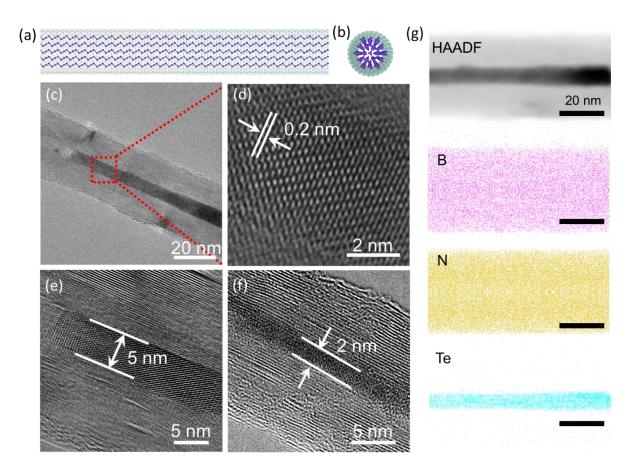

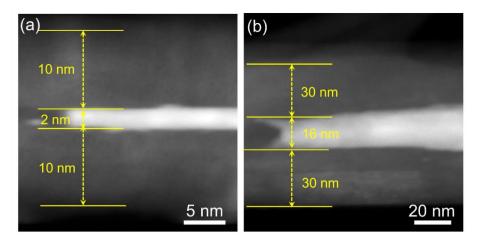

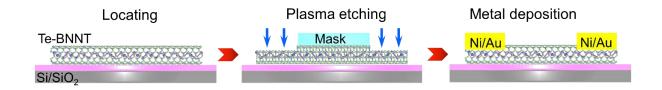

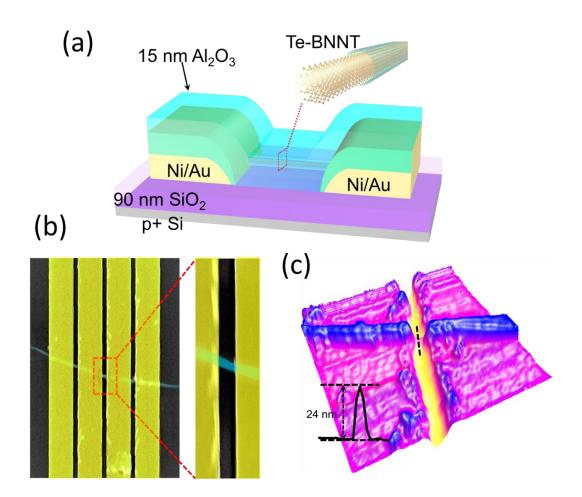

Even though 2D thin films of them are stable in ambience, it is relatively difficult to realize 1D free-standing chains. In order to study the physical properties of its 1D form, nanotube encapsulation is helpful for isolating Te helical chains [29], [79], [80]. Te atomic chains can be isolated through the encapsulation of carbon nanotubes (CNTs) and boron nitride nanotubes (BNNTs). Due to the spatial confinement of the cavities of nanotubes, the number of atomic chains accommodated in the hosting tubes are tunable. It was reported that the formation of crystal structure of Te is not preferable when the inner diameter (ID) of the nanotube is less than 1.7-2.0 nm [79]. Instead, free standing atomic chains are filled inside. The atomic structure of single Te chain was clearly observed through high resolution transmission electronic microscopy (HR-TEM) and scanning transmission electronic microscopy (STEM), and the optical and electric transport responses of the atomic chains in BNNTs down to 2 nm limit were characterized and reported as well [29].

We reported the synthesis of Te NWs down to a single atomic chain and few-chain limit by filling the cavities of CNTs and BNNTs, respectively, using a physical vapor transport (PVT) technique. By controlling the inner diameter (ID) of CNTs, few-chain and single-chain Te NWs are isolated. We find that the frequency of Raman peaks of the samples varies monotonically with the number of Te atomic chains. Due to the excellent transport properties of Te and high thermal conductivity of BNNTs, the current-carrying capacity of BNNT-shielded Te NWs exceeds that of most semiconductor nanowires, reaching up to  $1.5 \times 10^8$  A/cm<sup>2</sup>, which is only slightly smaller than the semiconducting SWCNTs value of  $4.3 \times 10^8$  A/cm<sup>2</sup> [85, 86] Due to the shielding and isolation provided by the BNNTs, Te NW at the few-chain limit could stably exist in ambient, and the short-channel Te NW FETs exhibit decent electrical performance even with a diameter of only 2 nm.

### 2.2 Tellurium Nanowire in Carbon Nanotube

Since the discovery of carbon nanotubes (CNTs) in 1991 [83], this novel 1D material has contributed to the development in the fundamental investigations and research fields [84]–[88]. Beside applied as a conducting or semiconducting 1D materials, CNTs are utilized as a growth templates to have other nano-materials coated outside [89], [90]. Moreover, CNTs being a hollow 1D structure are employed as a natural growing shell for controllable 1D material synthesis as well [79], [91]–[93]. Therefore, Te with a 1D chain-based vdW structure is suitable for this growing strategy [29], [79]. Because of the physical confinement and limited accommodation in the cavities of CNTs, the number of Te helical chains can be accordingly controlled by choosing CNTs with appropriate diameters.

### 2.2.1 Synthesis Method

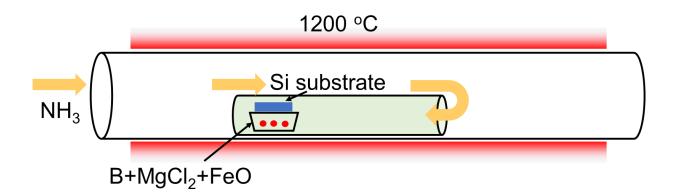

Physical vapor transport (PVT) is an important material synthesis technique which is utilized here to grow 1D tellurium. In a typical process of PVT, a precursor is put in an ampoule which is employed as a reacting chamber. In amount of cases, a transport agent such as iodine (I<sub>2</sub>) is mixed with the precursor to assist on vapor transportation. After locating the precursors in the ampoule, the ampoule will be vacuumed (usually lower than 1 mTorr) and sealed by a propane-oxygen or acetylene-oxygen torch so that the precursor is in a vacuumed, enclosed environment. Next, the sealed ampoule will be put into a furnace which provides the desired growing temperature and the temperature gradient along the ampoule. The precursor will be vaporized under high temperature, and the vapor will be restricted in space of the vacuumed ampoule. Due to the designed temperature gradient, the precursor will gradually grow on the other end of the ampoule and/or somewhere in between.

A variety of CNTs with different inner diameters were purchased from Sigma-Aldrich. Before filling, 26 mg of CNTs were heated at 420 °C for 1h in ambient to open the ends of tubes. Cap-opened CNTs and 70 mg of Te (Sigma-Aldrich, 99.8% trace metals) were sealed under vacuum ( $10^{-5}$  mbar) in a quartz tube and heated at 439 °C for 4 days. Under such pressure and temperature, tellurium is vaporized and transporting within the space of the sealed ampoule. Chances are that they can possibly fill into the cavity of the cap-opened CNTs and form crystallized

or free-standing atomic chains there. After the growth, as-prepared Te-CNTs were dispersed ultrasonically into methanol for subsequent characterization.

# 2.2.2 TEM Characterization

A variety of CNTs with different ID were taken as templates, and in a given batch more than 90% of the SWCNTs are successfully filled with Te atomic as shown in Figure 2.1. The Highangle annular dark-field scanning TEM (HAADF-STEM) and high-resolution TEM (HRTEM) images demonstrate that a single Te atomic chain can exist in ambient using a 0.8 nm SWCNT as a container, where the individual Te atoms can also be distinctively resolved with a clear 3-foldsymmetry helical structure (Figure 2.2). The successful realization of a single atomic chain is ascribed to the unique 1D vdW nature of Te. Since a single Te atom tends to covalently bond only with its two neighboring atoms in a chain, a single atomic chain of Te can be isolated through the spatial confinement from a SWCNT.

Figure 2.1. TEM characterization of Te chains in SWCNTs. (a) HRTEM image and (b) HAADF-STEM image. Inset shows the corresponding EDX mapping image.

Figure 2.2. Single Te atomic chain in CNTs with ID of 0.8 nm exhibiting 3-fold structure.

SWCNTs with an inner diameter of 1.2 and 1.5 nm increase the number of confined Te atomic chains to 2 and 3, respectively, and a larger-diameter multi-wall CNT (MWCNT) of 2.3 nm results in a wider Te NW with ~19 Te atomic chains (Figure 2.3). The results suggest that by carefully selecting the inner diameter of CNTs, controlled growth of ultra-narrow Te NWs with few-number of atomic chains can be realized.

Figure 2.3. HRTEM images of the (a) single, (b) double, (c) triple, and (d) 19 chains of Te shielded by CNTs. Inset: schematic structure diagrams.

### 2.2.3 Raman Response

As illustrated in Figure 2.4, free-standing single atomic Te chain was fully relaxed to obtain its photon energies [94]–[96]. DFT-relaxed structures give the frequency of  $E_1$ ,  $E_2$  and  $A_1$  modes to be 68, 178 and 192 cm<sup>-1</sup>, respectively. With the increase of chains, both the  $A_1$  and  $E_2$  would move toward the low-frequency direction, while the  $E_1$  mode shows the opposite tendency, which are well matched with experiments. The DFT results suggest that vdW interaction between the Te chain and CNT is very weak and the CNT encapsulation keeps the free-standing structure of Te atomic chain.

Figure 2.4. The photon energy calculation of Te atomic chains. (a) Atomistic structure of the Te atomic chain. (b) Phonon energies of a single atomic Te chain with dependence of lattice constant. (c) Phonon energies for a single Te atomic chain and bulk Te. In 3-bundle case, the interaction between chains would split the Raman vibration modes and result into the increase of modes, while these modes are degenerated in single chain case or in bulk form

In 2D materials, the Raman frequency is very sensitive to the number of layers, since the vdW interaction can strongly affect the electron-phonon coupling resulting in changed phonon modes [39]. Therefore, the Raman technique can also be used to evaluate the vdW interaction in Te NW crystal and identify the number of atomic chains. For a single Te atomic chain confined in a 0.8 nm SWCNT, the A<sub>1</sub> mode exhibits a large shift towards higher frequency at 196 cm<sup>-1</sup>, while the E<sub>1</sub> and E<sub>2</sub> modes are too weak to be detected. This result is in good agreement with our theoretical calculations for the free-standing single Te chain. This suggests that the vdW interaction between the single Te atomic chain and the SWCNT inner wall is very weak and the Te chain could be fully relaxed in the SWCNT and exist stably in the form of a 3-fold-symmetry helical coil.

Figure 2.5(a) and (b) present the evolution of Raman peak frequency with the diameter of Te NWs. As the number of Te atomic chains increases from two toward bulk (ID of CNT increases from 1.3 nm to >10 nm), clear redshifts of the A<sub>1</sub> and E<sub>2</sub> modes can be observed. For example, the A<sub>1</sub> peak is significantly shifted from 148 cm<sup>-1</sup> for 1.3 nm to 123.1 cm<sup>-1</sup> for bulk.

Figure 2.5. (a) Raman spectrum evolution of Te NWs with CNTs of different ID. (b) Dependence of the shifts in Raman peak frequency on CNT ID.

Similar to the previously reported results on few-layer tellurene [28], the unique chiral structure of Te causes the weakening of intra-chain covalent atomic bonding and the enhancement of inter-chain vdW interactions as the number of layers increases. Therefore, Te atoms could more easily restore back in bulk form, resulting in Raman frequency reduction of the  $A_1$  vibration mode. On the contrary, long-range Coulomb interactions dominate the vibration mode of individual Te atomic chains in few-chain samples and lead to the hardening of intra-chain E vibration modes [97].

### 2.3 Tellurium Nanowire in Boron Nitride Nanotube