# INCREMENTAL TEST PATTERN GENERATION FOR STRUCTURALLY SIMILAR CIRCUITS

by

Jerin Joe

A Dissertation

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

Doctor of Philosophy

School of Electrical and Computer Engineering West Lafayette, Indiana May 2023

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

## Dr. Irith Pomeranz, Chair

School of Electrical and Computer Engineering

# Dr. Cheng-Kok Koh

School of Electrical and Computer Engineering

# Dr. Milind Kulkarni

School of Electrical and Computer Engineering

# Dr. T. N. Vijaykumar

School of Electrical and Computer Engineering

# Approved by:

Dr. Dimitrios Peroulis

To my parents and to Jom, for their unconditional love and support.

# ACKNOWLEDGMENTS

First and foremost, I would like to express my sincere gratitude to my advisor, Dr. Irith Pomeranz, for her unwavering support, patience, encouragement, and her willingness to share her enormous expertise. Her prompt suggestions, meticulous scrutiny, and scientific approach have helped me to a great extent. This work would not have been accomplished without her guidance.

I would also like to thank Dr. Janusz Rajski and Dr. Nilanjan Mukherjee, my advisors at Siemens Digital Industries Software, for providing funding and suggesting ideas for this thesis. Their exceptional patience, guidance, and encouragement have helped me during my studies and research.

I would like to thank Dr. Cheng-Kok Koh, Dr. Milind Kulkarni, and Dr. T.N. Vijaykumar for serving on my advisory committee.

I would like to extend my gratitude to Dr. Chen Wang, and Dr. Yingdi Liu at Siemens Digital Industries Software for going above and beyond to help me whenever I needed one.

I am deeply grateful to my friend, Dr. Binod Kumar, for his insightful comments and unwavering support throughout my research.

Lastly, I would like to mention my sincere gratitude to Jom. Without his continuous support and motivation, this Ph.D. journey would not have been possible.

# TABLE OF CONTENTS

| L        | LIST OF TABLES  |        |                                                                           |   |  |  |  |

|----------|-----------------|--------|---------------------------------------------------------------------------|---|--|--|--|

| L]       | LIST OF FIGURES |        |                                                                           |   |  |  |  |

| ABSTRACT |                 |        |                                                                           |   |  |  |  |

| 1        | INT             | RODU   | CTION                                                                     | 3 |  |  |  |

|          | 1.1             | VLSI   | Design Flow                                                               | 3 |  |  |  |

|          | 1.2             | Desig  | n for Testability 1                                                       | 5 |  |  |  |

|          |                 | 1.2.1  | Scan Design                                                               | 6 |  |  |  |

|          |                 | 1.2.2  | Built-In-Self-Test (BIST)                                                 | 7 |  |  |  |

|          |                 | 1.2.3  | Boundary Scan                                                             | 7 |  |  |  |

|          | 1.3             | Fault  | $Models  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 8 |  |  |  |

|          |                 | 1.3.1  | Stuck-At Fault                                                            | 8 |  |  |  |

|          |                 | 1.3.2  | Transition Fault                                                          | 9 |  |  |  |

|          |                 | 1.3.3  | Path Delay Fault                                                          | 0 |  |  |  |

|          |                 | 1.3.4  | Bridging fault                                                            | 1 |  |  |  |

|          | 1.4             | Previo | ous Works                                                                 | 1 |  |  |  |

|          |                 | 1.4.1  | Incremental Test Pattern Generation                                       | 1 |  |  |  |

|          |                 | 1.4.2  | Incremental Logic synthesis using structural similarity                   | 3 |  |  |  |

|          |                 | 1.4.3  | Structural similarity during Place & Route                                | 5 |  |  |  |

|          | 1.5             | Contr  | ibution $\ldots$ $\ldots$ $\ldots$ $\ldots$ $2$                           | 5 |  |  |  |

|   | 1.6 | Thesi  | s Overview                                           | 27               |

|---|-----|--------|------------------------------------------------------|------------------|

| 2 | FAS | T TEST | Γ GENERATION FOR STRUCTURALLY SIMILAR CIRUITS        | 28               |

|   | 2.1 | Introd | uction                                               | 28               |

|   | 2.2 | Test C | Generation Process                                   | 31               |

|   |     | 2.2.1  | Overview                                             | 31               |

|   |     | 2.2.2  | Signature Computation                                | 32               |

|   |     | 2.2.3  | Mapping between circuit1 and circuit2                | 38               |

|   |     | 2.2.4  | Transforming the Pattern File                        | 40               |

|   |     | 2.2.5  | Incremental ATPG                                     | 41               |

|   | 2.3 | Exper  | imental Setup and Results                            | 41               |

|   |     | 2.3.1  | Experimental Study on Signature Aliasing             | 41               |

|   |     | 2.3.2  | Logic changes                                        | 43               |

|   |     | 2.3.3  | Sequential changes                                   | 47               |

|   | 2.4 | Conclu | usion                                                | 49               |

| 3 | TES | T GEN  | ERATION FOR AN ITERATIVE DESIGN FLOW WITH RTL CHANGE | $\mathrm{ES}$ 50 |

|   | 3.1 | Introd | uction                                               | 50               |

|   | 3.2 | Motiva | ation and Background                                 | 53               |

|   |     | 3.2.1  | Review                                               | 53               |

|   |     | 3.2.2  | Mapping between two versions of a circuit            | 54               |

|   |     | 3.2.3  | Mapping between two versions of a circuit            | 55               |

|   |     | 3.2.4  | Pattern Transformation and Fault Simulation          | 55 |

|---|-----|--------|------------------------------------------------------|----|

|   |     | 3.2.5  | Examples of different types of RTL changes           | 56 |

|   | 3.3 | Propo  | sed Methodology                                      | 59 |

|   |     | 3.3.1  | Overview                                             | 59 |

|   |     | 3.3.2  | Unique Signature Mapping Illustration                | 60 |

|   |     | 3.3.3  | Mapping Based on Unique Signature Pairs              | 62 |

|   |     | 3.3.4  | Mapping Common Signature Pairs                       | 64 |

|   |     | 3.3.5  | Mapping for the Remaining Unmapped Outputs           | 65 |

|   | 3.4 | Exper  | iment and Results                                    | 66 |

|   | 3.5 | Concl  | usion                                                | 71 |

| 4 | GEN | VERAT  | ION OF TWO-CYCLE TESTS FOR STRUCTURALLY SIMILAR CIR- |    |

|   | CUI | TS     |                                                      | 72 |

|   | 4.1 | Introd | luction                                              | 72 |

|   | 4.2 | Motiv  | ation for two-cycle signatures                       | 76 |

|   | 4.3 | Two-c  | ycle Signature Computation                           | 79 |

|   | 4.4 | Test C | Generation Procedure                                 | 83 |

|   |     | 4.4.1  | Mapping of Inputs and Outputs                        | 83 |

|   |     | 4.4.2  | Transformation of Patterns                           | 86 |

|   |     | 4.4.3  | Fault Simulation and Incremental ATPG                | 88 |

|   | 4.5 | Exper  | imental Results                                      | 88 |

|   |      | 4.5.1  | RTL changes                  | 89  |

|---|------|--------|------------------------------|-----|

|   |      | 4.5.2  | Gate-level changes           | 92  |

|   |      | 4.5.3  | Discussion                   | 95  |

|   | 4.6  | Conclu | usion                        | 95  |

| 5 | CON  | ICLUSI | ON                           | 97  |

| R | EFER | ENCES  | 5                            | 98  |

| А | ADI  | DITION | AL EXPERIMENTS FOR CHAPTER-1 | 105 |

|   | A.1  | Single | Changes                      | 105 |

|   | A.2  | Cumul  | lative changes               | 109 |

# LIST OF TABLES

| 2.1 | Categories of Gate Type and Prime Number Used as Mask                              | 34  |

|-----|------------------------------------------------------------------------------------|-----|

| 2.2 | Output signature for different configurations                                      | 42  |

| 2.3 | Experimental Result for Logic Changes                                              | 45  |

| 2.4 | Experimental Result for Sequential Changes                                         | 48  |

| 3.1 | Input and Output Signatures for Figure 3.6                                         | 60  |

| 3.2 | Average Combinational and Sequential Changes                                       | 67  |

| 3.3 | Experimental Result for Circuits Modified at RTL                                   | 68  |

| 4.1 | Input and Output Signatures for Figure 4.4                                         | 85  |

| 4.2 | Pattern Transformation for LOC Tests                                               | 87  |

| 4.3 | Experimental Result for Circuits modified at RTL                                   | 90  |

| 4.4 | Experimental Result for Gate-level Combinational Changes                           | 93  |

| 4.5 | Experimental Result for Gate-level Sequential Changes                              | 94  |

| A.1 | Experimental Result for Single Changes                                             | 106 |

| A.2 | Results of Runtime Gain and Test Pattern Increase for Table A.1 $\ldots$           | 107 |

| A.3 | Results for Individual Runs for 10 Versions of Circuit 7 from Table A.1 $\ldots$ . | 108 |

| A.4 | Experimental Result for Cumulative Changes                                         | 110 |

| A.5 | Results of Runtime Gain and Test Pattern Increase for Table A.4                    | 111 |

# LIST OF FIGURES

| 1.1  | VLSI Design Flow [4]                                                             | 14 |

|------|----------------------------------------------------------------------------------|----|

| 1.2  | Basic Principle of Testing of Digital Circuits [10]                              | 15 |

| 1.3  | Scan Flip Flop [13]                                                              | 16 |

| 1.4  | Scan Based Design [13]                                                           | 17 |

| 1.5  | Built-In-Self-Test [13]                                                          | 18 |

| 1.6  | Stuck-At-Fault                                                                   | 19 |

| 1.7  | Slow-to-Fall                                                                     | 20 |

| 1.8  | Test Pattern for Input A s-a-1 Fault                                             | 22 |

| 1.9  | Test Pattern for Input B s-a-1 Fault Using Inherited Values                      | 23 |

| 1.10 | DeltaSyn Method From [29]                                                        | 24 |

| 1.11 | Overview of ATPG flow in the thesis                                              | 26 |

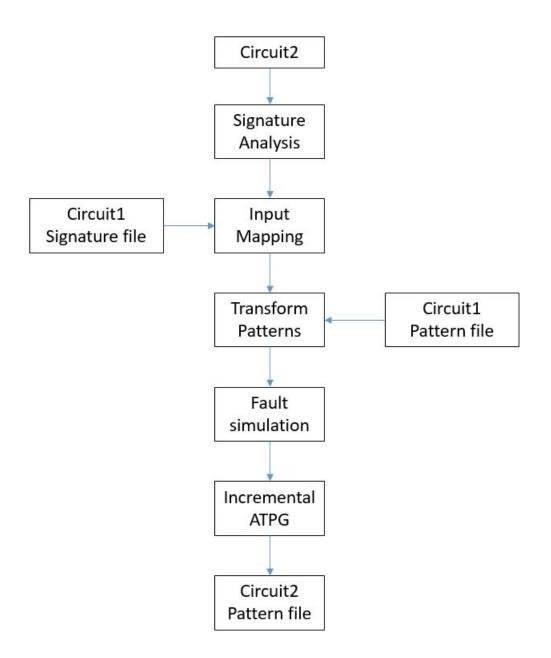

| 2.1  | ATPG Flow of Circuit1                                                            | 32 |

| 2.2  | ATPG Flow of Circuit2                                                            | 33 |

| 2.3  | An Example of Output Signature Computation for a Logic Circuit                   | 35 |

| 2.4  | A Logic Circuit with Modification                                                | 40 |

| 2.5  | 4-level AND-OR gate connection                                                   | 42 |

| 2.6  | The minimum of deviation in logarithmic scale (base 10) $\ldots \ldots \ldots$   | 43 |

| 3.1  | VLSI Design Flow [56],[57], [58]                                                 | 51 |

| 3.2  | Overview of ATPG flow                                                            | 54 |

| 3.3  | Transformation of a pattern                                                      | 56 |

| 3.4  | RTL code snippet for two versions of the circuit                                 | 57 |

| 3.5  | An example of a portion of a synthesized circuit before and after a modification | 58 |

| 3.6  | An example to illustrate unique signature mapping                                | 61 |

| 3.7  | Mapping information for different iterations in MAP                              | 62 |

| 3.8  | Runtime gain as a function of the number of changes                              | 70 |

| 4.1  | VLSI Design Flow [56],[57], [58]                                                 | 74 |

| 4.2  | Overview of the ATPG Flow [59],[68]                                              | 75 |

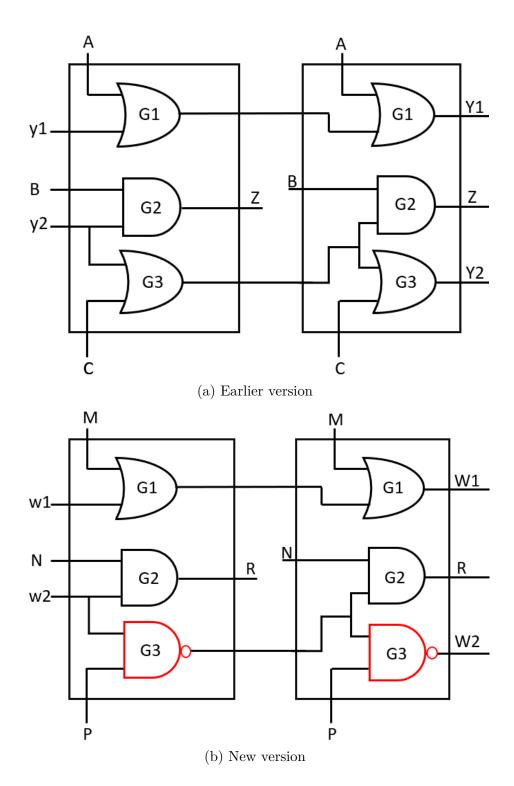

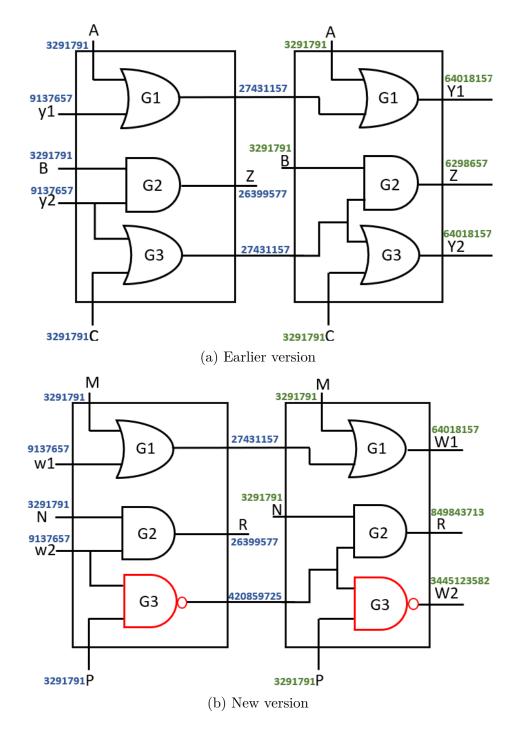

| 4.3  | Two versions of a circuit                                                        | 77 |

| 4.4 | Two time-frame expansion                                              | <br> | 78 |

|-----|-----------------------------------------------------------------------|------|----|

| 4.5 | Example of output signature computation over two time-frames $\ldots$ | <br> | 81 |

# ABSTRACT

The advancement of semiconductor technology has resulted in the development of devices that are fast, cost-effective, low-power, and high-performance. To achieve this, many gates are integrated into smaller areas, resulting in increased complexity of digital circuits. Increased size and complexity result in a large number of faults, which increases the time taken to test the circuit. However, as the size of the digital designs increases, they also exhibit structural similarities. This thesis describes a test generation process that utilizes structural similarity to speed up the test generation process. The property of structural similarity can be seen in circuits that are subjected to engineering change order (ECO), circuits that are modified during place and route, circuits subjected to retiming, circuits with multiple cores such as central processing units (CPUs), graphics processing units (GPUs), and artificial intelligence (AI) chips. The goal of the thesis is to determine the testability of a circuit (circuit2) given a test set for a structurally similar circuit (circuit1). This is achieved by transforming a test set generated for circuit1 into a test set for circuit2 without repeating the entire test generation process. The process described in the thesis starts with a structural analysis of circuit1 and circuit2 that captures their structural properties using an integer-arithmetic based computation called signatures. The signatures are used to obtain a partial mapping between the inputs and outputs of the two circuits. The mapping is used for transforming test patterns for circuit1 into test patterns for circuit2. The first chapter looks into similar circuits obtained after modifying the gate-level netlist. In the next chapter, structurally similar circuits were obtained by modifying the RTL, and the gate-level was resynthesized. This chapter proposed a mapping methodology to accommodate the changes introduced during the resynthesis of a netlist. Lastly, the thesis described a test generation methodology where transition faults are considered, which required two-cycle tests to be detected.

# 1. INTRODUCTION

Advancing growth in semiconductor technology has led to the development of fast, costeffective, low-power, and high-performance devices [1], [2]. Complex circuits consist of a large number of gates that are integrated into small-sized chips, which increases the complexity of integrated circuits. A decrease in size and an increase in complexity results in an increased number of faults to be tested [2]. With complex and dense ICs, the time taken to test, debug and verify the circuit becomes the bottleneck for chip design. [3].

The physical design flow [4] is iterative to fix errors, improve performance and solve power issues. In order to meet the circuit specifications, designers make changes in the circuit [5], [6]. The required changes are performed incrementally so that they would have less impact on the existing design. Such changes are known as Engineering Change Orders (ECO). Testability bottlenecks are addressed by performing test generation early in the design flow. The generated test sets remain valid as long as the modifications do not alter the gate-level description of the circuit. Every time a modification changes the gate-level description, the test patterns for the original design become invalid, and new test patterns need to be generated for the modified design. This visibly increases the overall test generation time and time-to-market for the chip.

The solution explored in this thesis is to exploit structural similarity prevalent in the current designs to speed up the test generation process. The thesis provides a solution for incremental test generation for similar circuits obtained by modifying gate-level netlists and the RTL when stuck-at and transition faults are considered.

This chapter presents the basics of design for test (DFT), its techniques, a few of the fault models involved in the study and review of the previous works.

### 1.1 VLSI Design Flow

The VLSI chip density is expanding exponentially as transistor feature sizes continue to shrink. As a result, the current and future VLSI technology are extremely complicated. In order to meet the current demand, billions of transistors are integrated on a single chip. In addition, every manufactured chip must be reliable and should be thoroughly tested. A robust VLSI design and test flow which results in the production of reliable chips is reviewed in this section.

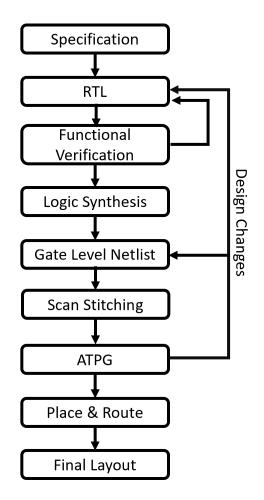

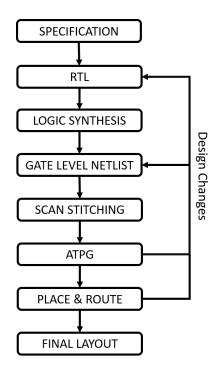

Figure 1.1. VLSI Design Flow [4]

Figure 1.1 shows a flow diagram for the VLSI design. The initial stage of the VLSI design flow is to defining the specifications of the circuit. The specifications define the necessary power, area, timing constraints that needs to be met for the design. the behavioral aspect of the circuit is defined using a hardware description language (HDL)[7], [8]. Every time, before moving on to the next level, a verification step is performed.

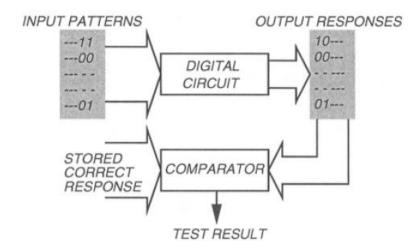

Functional verification [9] is performed before synthesizing the RTL description to ensure the design is done according to the specifications. After the verification, the RTL is converted into a gate-level netlist using a synthesis tool. To ensure that the gate-level netlist meets all the circuit requirements, the design needs to be tested. Automatic Test Pattern Generation (ATPG) is performed on the circuit to determine the fault coverage achieved. Binary test patterns are generated and applied to the circuit under test (CUT) to excite the faults in the functional modules in the design[10]. This is shown in figure 1.2. The output is compared to the desired response of the circuit. If the response from the applied test pattern does not match the desired response, the test pattern has detected a fault. These test patterns are used to test the designs for any defects. The quality of the test patterns is determined by the number of faults detected during automatic test pattern generation (ATPG). If these patterns does not detect a reasonable number of faults, design needs to be incrementally modified in order to meet the circuit requirements.

Figure 1.2. Basic Principle of Testing of Digital Circuits [10]

The final stage is the placement of the synthesized modules. The functional modules need to be placed in precise locations within a chip to get an optimized design. After the placement, the functional modules are connected using wires.

## 1.2 Design for Testability

A large, complex design consists of combinational and sequential logic. The circuit with sequential logic is difficult to test as test patterns need to be applied over multiple cycles to obtain the response at the output of the design. This increases the test volume and test application time. With the increase in complexity of a design, digital circuits need to be designed by taking into account the time taken for testing. Design for testability (DFT) [11] techniques improve the testability of the circuit by adding more hardware in the CUT. Using the DFT techniques, the difficulty of testing sequential circuits is minimized. Some of the DFT techniques involved are scan design, Built-in-self-test (BIST), boundary scan.

## 1.2.1 Scan Design

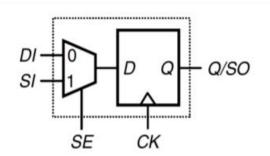

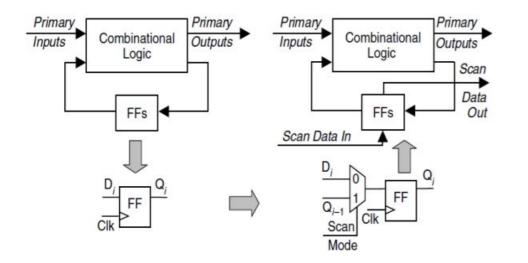

Scan based [12] DFT technique is one of the widely used techniques. In this DFT technique, the flip flop in the design is modified by adding a test mode to the design, as shown in the figure. This makes the flip flop easier to test by making it controllable and observable.

Figure 1.3. Scan Flip Flop [13]

The scan structure has an extra input known as scan-in (SI), which is fed to the flip flop through a two-input multiplexer. The multiplexer is controlled using a scan enable (SE) pin, which selects the data path (D input) or scan input path (SI input) as per the test mode.

One or more shift registers are formed by connecting the scan cells together, as shown in Figure 1.4. Each scan cell is made observable and controllable, thus gaining access to the internal modules in the circuit. The scan structure can be set to any desired value during the test mode by shifting the value in the shift registers. Combinational logic in the design can be tested by assigning values to the scan cells. The responses to the applied stimuli will be captured in the scan cells. By shifting out of the registers, the values in the scan structure can be observed.

Figure 1.4. Scan Based Design [13]

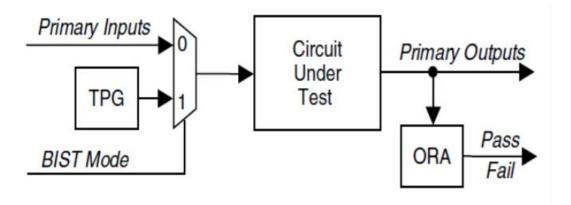

### 1.2.2 Built-In-Self-Test (BIST)

BIST [14] was introduced to test the circuit by itself at the operating speed of the design. This DFT technique uses additional hardware such as an internal test pattern generator (TPG), an output response compacter, a comparator, and a ROM, as shown in Figure 1.5. A TPG is integrated within the design to generate the test patterns internally. Next, the output responses of the CUT are sent through a data compacter. Finally, the compacted value is compared with the reference value stored in the ROM to verify the correctness of the design.

# 1.2.3 Boundary Scan

A boundary scan [15] enhances the access to test the components that are embedded within the design. In this technique, a register with additional circuitry is placed at each of the input/output (I/O) pins. These cells at the periphery are serially connected to form a boundary-scan. The test stimuli can be serially shifted through the boundary scan during the test mode. The cells in the boundary scan can either force the data onto the CUT or

Figure 1.5. Built-In-Self-Test [13]

capture the response. With direct access to I/O pins, the interconnects in the circuit can also be tested separately, in addition to testing the logic of the circuit.

## 1.3 Fault Models

During the manufacturing, development, or operation of the design, a defect like short or open can occur within a design. With the increasing size and shrinking feature size of an integrated circuit, the number of physical defects can be enormous. A fault model is a way to depict the behavior of the defects in the design accurately. Some of the basic fault models are described in the following sub-section.

### 1.3.1 Stuck-At Fault

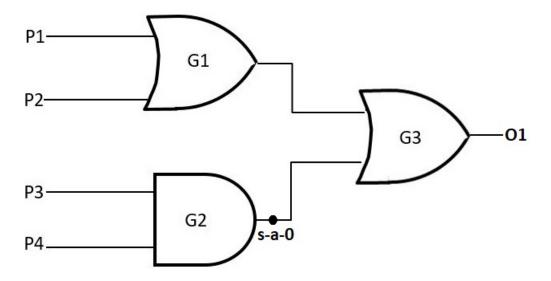

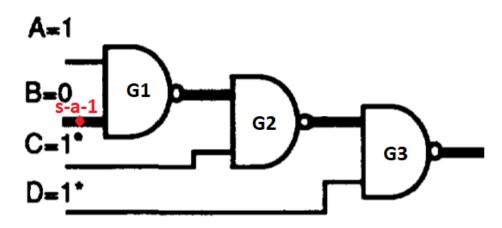

Stuck-At-fault [16] describes the faulty behavior of the signal line connecting the gates within the design. The line can be tied to logic 1, which is called stuck-at-1 (s-a-1), or tied to logic 0, which is called stuck-at-0 (s-a-0). Figure 1.6 shows an example of stuck-at-fault.

In Figure 1.6, the output line of gate G2 is stuck at logic value '0'. By applying the test vector '0011' on the primary inputs, it can be seen that the fault-free output of gate G2 should be 1, but the faulty circuit will produce a 0. This effect of the stuck-at fault at the output of gate G2 can be propagated to the primary output by setting the primary inputs

Figure 1.6. Stuck-At-Fault

P1 and P2 to 0. Thus, we get the test vector '0011', for which the output response of faulty and fault-free circuits differ at the primary output. Hence, the test vector '0011' detects the s-a-0 fault at the output of gate G2.

#### **1.3.2** Transition Fault

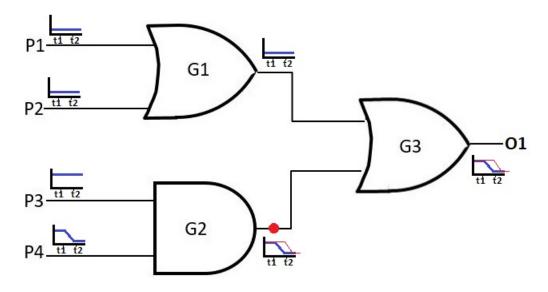

The defects in the circuit can induce improper timing behaviors. These defects can cause the circuit to fail when operated at the normal speed of operation. Such defects are modeled by delay faults. The transition fault model [17], [18] is one of the most extensively used delay fault models. A transition fault increases the time taken for a signal on a line to change. Transition faults can be categorized into two: slow-to-rise and slow-to-fall faults. When a signal takes a long time to change from 0 to 1, we see a slow-to-rise fault. Similarly, a slow-to-fall fault can be observed when a signal takes a long time to transition from 1 to 0.

In order to detect the fault, we have to create a transition on the line. Two patterns are required to excite a transition fault and be observed at the output. The first pattern initializes the circuit to a stable state and the second pattern creates the necessary transition to detect the fault. For example, for a slow-to-fall(rise) fault, the line first needs to be set to 1 (0), which is done using the first pattern. Then using the second pattern, the signal on the line is transitioned to 0 (1). As the line is faulty, the signal will take more time to change to logic value 0 (1), and this effect can be propagated to the primary output or a scan cell. This is shown in the Figure. 1.7.

Figure 1.7. Slow-to-Fall

There is a slow-to-fall fault at the output line of gate G2. The first pattern is applied at time t1, which sets the output line of G2 to 1. Once the outputs are stable, the second pattern is applied at time t2, creating a transition that forces the output line of gate G2 to fall to logic 0 slower than the normal speed of operation. Due to the slow-to-fall fault, the output remains at logic 1 at time t2 instead of logic 0, and the fault gets detected.

### 1.3.3 Path Delay Fault

Path delay faults [19] occur when the cumulative delay of a combinational path exceeds the clock period due to the defects in the circuit. A combinational path consists of a primary input or a scan cell connected to a primary output or scan cell via few combinational gates. Similar to the transition faults, there are two types of faults associated with each path in the circuit: rising path delay and falling path delay. The number of path delay faults increases exponentially with the size of the circuit.

### 1.3.4 Bridging fault

Two interconnect wires can be placed close to one another during fabrication. Such wires can unintentionally get shorted to each other. Such faults are modelled by bridge faults [20], [21]. If two interconnect lines are bridged, then the fault on these lines can be excited when the two lines have different logic values. There are various types of bridging fault: wired-OR, wired-AND, and Dominant. When there is a wired-OR (AND) fault, a logic 1 (0) on any line will force the other line to logic 1 (0). A dominant bridging fault will force the value of the dominating line onto the other wire.

#### 1.4 Previous Works

There are many different ways in the literature [22], [23], [24], [25], [26] where the test generation effort is being improved. These methods help in reducing the overall test generation time, which is usually performed before moving on to the next stage of the design flow. However, there is no framework to our knowledge that utilizes the test generated for a circuit and transforms it into a test for another structurally similar circuit.

The concept of incremental test generation was introduced in [26] for a different context that considered a single version of a design. This is reviewed in Section 1.4.1. The concept of incrementally modifying the flow has been explored in different fields like the synthesis of a design, place and route. In these works, the knowledge from a structurally similar design helps in reducing the effort for another structurally similar design. The following sections review incremental changes done in synthesis [27], [28],[29] (Section 1.4.2), and place and route [30] (Section 1.4.3).

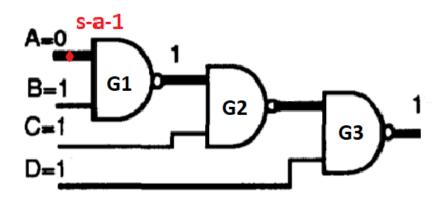

#### 1.4.1 Incremental Test Pattern Generation

The state-of-the-art test generation tools are fault-oriented. First, these tools generate tests for a targeted fault. Once the targeted fault has been detected or considered unde-tectable, the tool selects another fault and generates tests for it. The expectation in [26] is that starting from a test generated for one fault, it is possible to modify the test into a test

for another fault more quickly than starting from an all-unspecified test. This is illustrated next.

Figure 1.8. Test Pattern for Input A s-a-1 Fault

Figure 1.8 shows a circuit whose input A has an s-a-1 fault. To generate the test for input A s-a-1, the fault needs to be excited. Therefore, all inputs are unspecified, and input A is assigned logic value 0. In order to propagate this fault effect to the output, non-controlling values are assigned to the gates along the output path.

After the test vector detects the s-a-1 fault at input A, another undetected fault is picked, say s-a-1 at input B. In traditional tools, all the inputs are unspecified when a new fault is picked. Whereas [26] reuses the line justifications used for detecting the earlier fault. In order to excite the fault, input B is set to logic value 0, and input A is set to logic value 1, which is the non-controlling value of the AND gate. With the help of inherited values for the fault s-a-1 at input A, the injected faulty signal can be propagated to the output. This is shown in Figure 1.9.

In Figure 1.9, on the value shows that the value on the line was determined from the previous justification. Thus, in this example, for finding a test vector for the fault s-a-1 at input B, the earlier test vector helped to reduce the number of justifications by 2, which helps to speed up the test generation process.

Figure 1.9. Test Pattern for Input B s-a-1 Fault Using Inherited Values

#### 1.4.2 Incremental Logic synthesis using structural similarity

Design is modified when the circuit does not meet the design requirements. A minor modification can result in a different optimization when synthesizing the modified netlist during logic synthesis. The literature shows that the effort and time spent synthesizing the modified circuit can be reduced by incremental synthesis where gates are reused from the previous implementation.

In [27], a method is proposed to identify the correspondence between gates and pins of the baseline and the modified circuits. First, the correspondence between the circuits is computed by creating an identification index for every gate based on the name of the primary input/output (IO) lines, type of gate, number of fanins, and number of fanouts. Then, a gate matrix is created using this index that includes every pair of gates in the baseline and the modified circuits. The algorithm identifies gates that are structurally compatible in the baseline and the modified circuits based on the gate matrix. Using the compatible gates, the procedure of [27] generates a synthesized circuit by retaining a maximum number of gates from the synthesized baseline circuit. This method identifies the logic gate components that must be modified due to the functional changes in the design and thus reduces the effort required for synthesis from the beginning. The procedure of [28] first checks for isomorphic cones in the circuit, as all gates in such cones are structurally equivalent. By identifying such isomorphic cones, the algorithm can retain the implementation of all these cones during incremental synthesis. Next, the algorithm evaluates every gate in both circuits to check the type of gate and the nets these gates are connected. Using these two steps, the algorithm determines the structurally similar gates. After the structural and functional equivalence is established between the baseline and the modified circuits, a mapping is established between the circuits, which is used to guide the synthesis process to generate a synthesized circuit with minimal change from the baseline circuit.

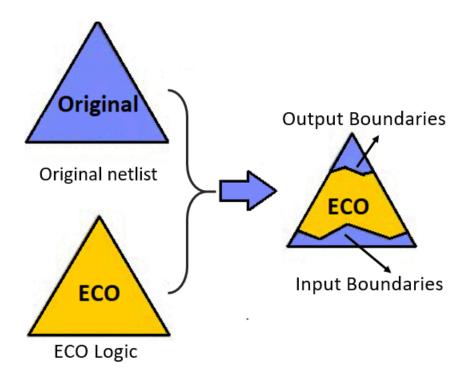

Figure 1.10. DeltaSyn Method From [29]

The paper [29] introduces a two-phase flow approach. The steps involve identifying the input and output boundaries of the modifications. The gates within these boundaries are the ones that need to be replaced due to ECO. First, identification of the input boundary is made using the structural and functional information to identify signals in the circuit that are functionally equivalent. Then, using these signals, the input side boundary is determined with the help of forward-sweeping algorithms. [31].

The output side boundaries are identified in the second step. This is done using a Boolean matching algorithm [32]. A recursive backward traversal is done from the primary outputs to obtain the logic equivalency. The output boundary is defined every time the circuit is matched from the output side. The synthesis tool can reuse all the gates that are outside the input and output boundary. This reduces the time taken for synthesis as the majority of the synthesized circuit has been reused.

### 1.4.3 Structural similarity during Place & Route

In [30], an ordering technique is proposed for all gate instances in the design. This technique is invariant to the changes in the circuit due to Engineering Change Order. For the ordering, a value is obtained for each gate instance by a linear combination of the type of the gate, number of fan-in gates, number of fanout gates, and terminal node name of the gate instances. In addition, the terminal node name of the connected fan-in and fanout gates are also used. This value is defined as a signature in [30]. After assigning signature values to all gate instances, a traversal is done in the input and output cones to obtain the updated signature values of the gate instances by linearly combining the signature of the fanout and fan-in gates in the cone, respectively. Thus, the ordering of gate instances based on the computed signature values guarantees a minimal change in the gate instance order even if the ECO process changes the ordering of the gate instances.

### 1.5 Contribution

The state-of-the-art test generation tools do not take advantage of the structural similarity in the circuits. Every time the gate-level is modified, the test generation must be done from the beginning discarding all the patterns generated earlier.

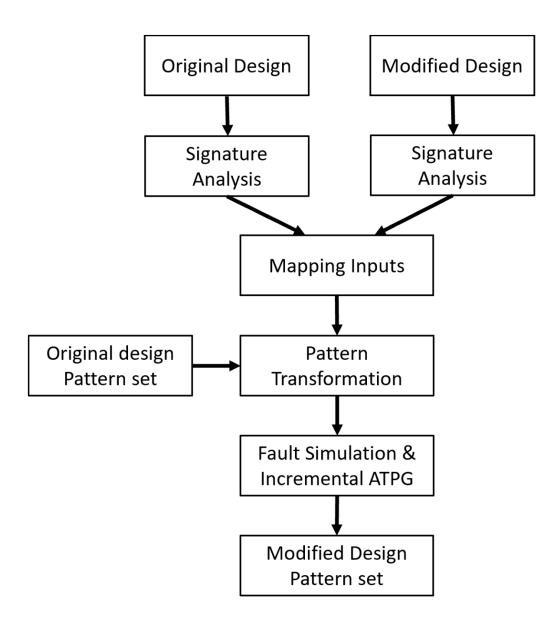

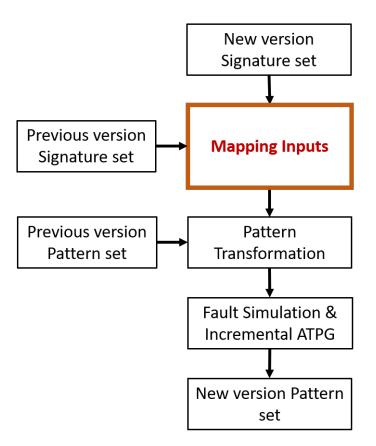

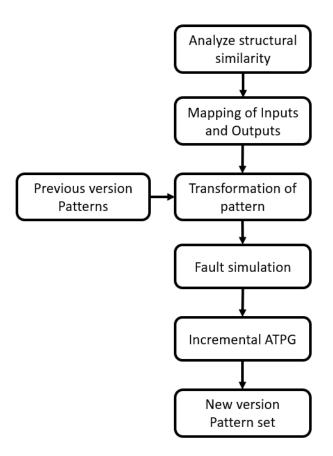

This thesis provides a novel test generation procedure whose overview is shown in Figure 1.11 and is described next.

In both original and modified designs, an integer arithmetic-based computation is performed on each gate. This computed value is called the signature. The signature sets from the original and modified designs are compared to find structural similarity between the ver-

Figure 1.11. Overview of ATPG flow in the thesis

sions. This comparison is used to map the inputs and outputs between both designs. Using the mapping information, the generated test patterns for the original circuit are transformed into test patterns for the modified circuit. Transformed test patterns are fault simulated, and test patterns are generated incrementally for the remaining faults from the modified portion of the design. The overall procedure can be applied to any structurally similar design and any fault model. Identifying structural similarity and reusing of existing patterns speeds up the test generation procedure compared to generating patterns from the beginning.

## 1.6 Thesis Overview

The thesis explores the aspect of accelerating the test generation for various structurally similar circuits. This is done by transforming the test generated for one circuit into a test pattern for another structurally similar circuit. The thesis is organized as follows.

Chapter 2 describes a fast test generation process for structurally similar circuits obtained by modifying the gate-level netlist. Chapter 3 describes an iterative flow when designs are modified at RTL. Chapter 4 explores a methodology when two-cycle tests are used to detect faults in a structurally similar circuits. Finally, chapter 5 gives the summary of the thesis.

# 2. FAST TEST GENERATION FOR STRUCTURALLY SIMILAR CIRUITS

©2022 Reprinted with permission from IEEE: J.Joe, N.Mukherjee, I.Pomeranz, and J.Rajski, "Fast Test Generation for Structurally Similar Circuits" 2022 VLSI Test Symposium (VTS), San diego, USA, 2022

This chapter describes a fast test generation process for digital circuits that exhibit extensive structural similarity. The property of structural similarity can be seen in circuits that are subjected to engineering change order (ECO), circuits that are modified during place and route, circuits subjected to retiming, and circuits with multiple similar cores. The goal of this chapter is to determine the testability of a circuit (circuit2) given a test set for a structurally similar circuit (circuit1). This is achieved by transforming a test set generated for circuit1 into a test set for circuit2 as efficiently as possible, without repeating the entire test generation process. The process described in this chapter starts with a structural analysis of circuit1 and circuit2 to obtain a mapping between their inputs and outputs. The mapping is used for transforming test patterns from circuit1 into test patterns for circuit2. The experiments conducted on industrial designs show an average of more than 10-fold reduction in runtime, compared with running the entire test generation process for circuit2.

#### 2.1 Introduction

The digital revolution has led to a steep increase in the complexity and density of Integrated Circuits (IC) [33]. Multiple cores are integrated within a chip to increase its throughput. For complex and dense ICs, the time to test, debug and verify the circuit becomes the bottleneck for chip design [34], [35], [36].

State-of-the-art synthesis flows are iterative to accommodate the need to fix bugs, and address performance and power constraints [37], [38]. Test generation [39], [40], [41], [42] is performed early in the design flow to identify testability issues that cannot be identified using approximations such as testability measures [43], [44]. The test set obtained at an early

stage of the design process does not need to be optimized, and the speed of test generation is essential to the fast convergence of the design process. This chapter presents a novel approach for fast test generation by observing that structural similarity is prevalent with the current synthesis flow and state-of-the-art designs, as discussed next.

A large number of similar cores can be seen in conventional, gaming, and graphical processors. ICs like CPUs, GPUs, and AI chips show structural similarity within cores [45], [46], [47]. Moreover, a new design that reuses the same cores shows significant structural similarity to a previous design. Netlists before and after place and route, and circuits subjected to engineering change order (ECO) [38], [27], [48], [28], [49], or retiming [50], [51], also exhibit significant structural similarity.

The property of structural similarity between circuits is not utilized in the current test generation tools. As a result, test generation has to be run in its entirety after every change that may affect the testability of a circuit. This chapter aims to analyze the testability of a circuit (circuit2), which is structurally similar to another circuit (circuit1), by efficiently transforming the test set generated for circuit1 into a test set for circuit2 without repeating the entire test generation process. This is achieved through a process that uses incremental test generation.

The concept of incremental test generation was introduced in [52] for a different context that considered a single version of a design. The expectation in [52] is that starting from a test generated for one fault, it is possible to transform the current test into a test for another fault in the same design more quickly than starting from an all-unspecified test. In this chapter, the goal is to accommodate the fact that two circuits are structurally similar. Reusing an existing test set for circuit1 would significantly reduce the run time compared to running test-pattern generation from the beginning for circuit2.

Among the variations that may occur between similar circuits, circuit1 and circuit2, is a change in the order of the inputs or outputs. In this case, simply simulating an existing test set of circuit1 on circuit2 may not result in the detection of a significant number of faults. An incremental test generation solution needs to be independent of the order of the inputs and outputs. It also needs to accommodate the fact that state-of-the-art CPU, GPU, or AI chips have large numbers of identical logic blocks within them [46]. This creates more options by

which inputs and outputs of structurally similar circuits can be matched. An incremental test generation approach suitable for this context is developed in this chapter. As a part of the procedure described in this chapter, a structural correspondence is established between circuit1 and circuit2.

Structural correspondence is also considered in [27], [28] and [30]. In [27] and [28], structural similarity is used to determine the gates that can be re-used in synthesis after ECO. In [30], structural similarity of the circuit before and after ECO is exploited in the context of place and route.

In [30], an ordering technique is proposed for all gate instances. This technique is invariant to the changes in the circuit due to ECO. For the ordering, an integer value is calculated for each gate instance by a linear combination of the type of the gate, number of fan-in gates, number of fan-out gates, and terminal node name of the gate instance. In addition, the terminal node names of the connected fan-in and fan-out gates are also used. The value assigned to a gate instance is defined as its signature in [30]. After assigning signature values to all gate instances, a forward traversal is done from inputs to outputs to obtain updated signature values for the gate instances. This is achieved by linearly combining the signatures of the fan-in gates for each gate instance. The ordering of gate instances based on the computed signature values guarantees a minimal change in the gate instance order even if the ECO process changes the ordering of the gate instances.

An approach based on signatures is also followed in this chapter to determine the structural similarity between circuit1 and circuit2. The distinguishing feature in this chapter is that the signature values are computed based on properties of the gates and are not dependent on the predefined names of the gates. This is important because names may not be preserved between circuit1 and circuit2. In addition, the procedure proposed in [30] for signature computation traverses the circuit only once from inputs to outputs. In this chapter, a forward traversal is done from inputs to outputs to calculate output signature values. Using these values, a backward traversal is done from outputs to inputs to compute input signature values. In this way, the input signature captures the structural difference in the circuit even when the difference is not in the input cone of logic. This method of forward and then backward traversal is done to embed the properties of the output and input cones into the input signature. The mapping between the inputs of the two circuits is established using these unique values on the input and output pins, and the input-output list of a logic cone.

This chapter focuses on the application where a circuit is subjected to ECO or layout changes that result in modifications in the combinational or sequential logic of the circuit. These modifications change the netlist by the addition/removal of modules or modifying the logic in the circuit. In these contexts, designers change the circuit incrementally to impact only a small part of the design [53], [54]. The effectiveness of the proposed algorithm depends on the two circuits being structurally similar, and on the accuracy of the mapping of the circuit inputs. Synthesis can affect both of these properties. Hence to verify the algorithm, structurally similar netlists were obtained by making changes to the gate-level netlist so that the circuit before the change (circuit1) is structurally similar to the circuit after the change (circuit2).

This chapter is organized as followsSection II details the test generation methodology. Section III presents results for industrial designs followed by conclusions in Section IV.

### 2.2 Test Generation Process

### 2.2.1 Overview

The methodology we propose has three main steps. In the first step, we establish a mapping between the inputs and outputs of circuit1 and circuit2 based on structural equivalence [27],[28],[30]. We use input and output signatures for this purpose. A signature is defined by an integer-arithmetic based computation done on each gate of a logic cone to produce a unique value that captures the structure of the cone. If the circuits are structurally equivalent, the input and output signatures of circuit1 and circuit2 will allow us to find a perfect match between them. Due to the variations between the circuits, the matching is not perfect and some of the inputs and outputs remain unmatched. The corresponding input and output cones are where circuit2 is expected to be structurally different from circuit1.

In the second step, we transform a test set  $T_1$  generated for circuit1 into a test set  $T_2$  for circuit2. We use the mapping identified in Step 1 to copy values of matching inputs from  $T_1$

to  $T_2$ , leaving unmatched inputs unspecified. The unspecified inputs are assigned random values and then simulated to determine the faults detected using the test set  $T_2$ .

In the third step, we carry out incremental test generation to detect faults in circuit2 that have not been detected. These patterns are appended to  $T_2$ .

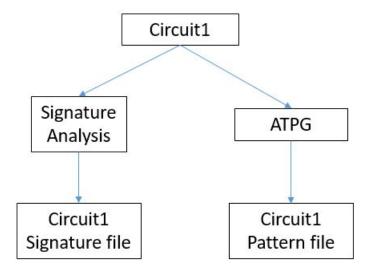

Figure 2.1. ATPG Flow of Circuit1

Figure 2.1 describes the computations performed for circuit1, including test generation to produce a test set for circuit1, and signature analysis to produce input and output signatures.

Figure 4.2 describes the computations performed for circuit2, including signature analysis to produce input and output signatures, input mapping based on the signatures computed for circuit1 and circuit2, computation of the test set  $T_2$  and incremental test generation to extend  $T_2$ .

In the next sections, we describe each of these steps in more detail.

## 2.2.2 Signature Computation

This section describes the computation of the input and output signatures. We first compute output signatures and then input signatures. A dictionary is created, where for every output signature (referred to as a key), we store vectors of inputs that drive outputs with a signature equal to the key. The dictionary is used for mapping inputs from circuit1

Figure 2.2. ATPG Flow of Circuit2

to circuit2. The input signatures and the dictionary are written to a file for later processing. We experimented with different approaches to computing the signatures and concluded that the one discussed next produces accurate results.

A signature needs to capture the structure of the design. To embed the gate types into the signature, each type of gate was assigned a unique prime number. A large number is chosen to reduce the probability of the same signature being obtained for different structures (aliasing). Furthermore, the level of a gate is captured by rotating the computed value during the traversal of the circuit. Rotation multiplies a number by two, causing larger numbers to be obtained with more levels. Using this approach to signature computation, the aliasing of signatures was not seen in the experiments performed.

For signature computation, the gate types are grouped into five categories. Each category is assigned a unique prime number randomly selected in the range between 1 - 15 million. This is called the mask for the group. The grouping of the gates and an example of the masks used for each group are shown in Table 2.1.

|   | Gate Types       | Prime Number (Mask) |

|---|------------------|---------------------|

| 1 | AND, NAND        | $1,\!540,\!681$     |

| 2 | WIRE, BUS        | $2,\!572,\!261$     |

| 3 | OR, NOR          | 4,980,727           |

| 4 | XOR, XNOR        | 5,210,099           |

| 5 | BUFFER, INVERTER | 9,137,657           |

**Table 2.1.** Categories of Gate Type and Prime Number Used as Mask

A variable called "Output\_Invert" is used during the signature computation to distinguish gate types in each category as shown in Table 2.1. "Output\_Invert" is set to false for OR, AND, BUFFER, XOR, and WIRE gate types, whereas it is set to true for NOR, NAND, INVERTER, XNOR, and BUS gate types. When the "Output\_Invert" is true, the bitwise complement of the computed value is stored as the signature of the gate.

For output signature computation, the inputs are initialized to a prime number randomly chosen between 1-15 million. The signatures are computed by traversing the circuit from inputs to outputs. The output signature of a gate is computed by an equation that takes into account the signatures of the gate inputs and the mask of the gate. The equation for gate types AND, WIRE, OR, XOR, and BUFFER is shown below in equation (2.1).

$$\begin{array}{l} {\rm Output \ Signature \ of \ a \ Gate_i} = \\ {\rm Rotate} \left( {\sum\limits_i {\rm (Rotate \ (Output \ signature \ of \ fan\_in \ } \\ {\rm of \ Gate_i} \right) + {\rm Group \ Gate \ Mask \ of \ Gate_i} } \right) \end{array} \tag{2.1}$$

The equation for gate types NAND, BUS, NOR, XNOR, and INVERTER is shown below in equation (2.2).

Output Signature of a Gate<sub>i</sub> =

$$\left( \text{Rotate} \left( \sum_{i} (\text{Rotate (Output signature of fan_in} \\ \text{of Gate_i}) + \text{Group Gate Mask of Gate_i} \right) \right)^C$$

(2.2)

The addition operations in equations (2.1) and (2.2) are done with carry. The C in equation (2.2) stands for the bitwise complement. Rotate refers to a rotate left operation. Output signature computation is illustrated in Fig. 2.3.

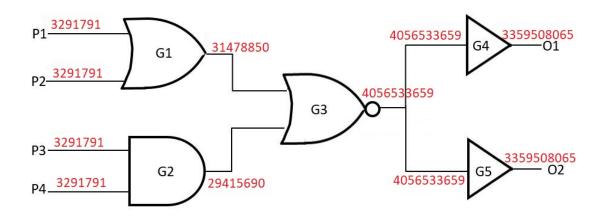

Figure 2.3. An Example of Output Signature Computation for a Logic Circuit

Output signature computation is illustrated in Figure 2.3. The circuit in Figure 2.3 has four inputs (P1, P2, P3, P4), two outputs (O1, O2), one AND gate (G2), one OR gate (G1), one NOR gate (G3), and two BUFFER gates (G4, G5). The output signature computation of gate G1 is discussed next.

Gate G1 is an OR gate and belongs to group 2. The inputs of G1 are P1 and P2, whose output signatures are initialized to 3,291,791. First, the output signatures of the inputs P1 and P2 are rotated to obtain 6,583,582. Next, the rotated output signatures of P1 and P2 are added along with the group gate mask of 2,572,261. This result is rotated, and the value obtained is 31,478,850. This value is stored as the output signature of G1.

The output signatures of gates G2, G4, and G5 are computed in the same way by equation (2.1), and for G3, the output signature is the bitwise complement of the value computed using equation (2.1). The value 4,056,533,659 is obtained assuming 32-bit integers. The output signatures of all the gates are shown in Figure 2.3.

For the input signature computation of the logic circuit in Fig. 2.3, the input signature of the outputs O1 and O2 are initialized to their output signatures. The algorithm traverses the circuit from outputs to inputs.

The equation for the computation of the input signature for gate types AND, WIRE, OR, XOR, and BUFFER is shown below in equation (2.3)

Input Signature of a Gate<sub>i</sub> =

Rotate

$$\left(\sum_{j} \text{Rotate (Input signature of fan_out_j)}\right)$$

of Gate<sub>i</sub>) + Group Gate Mask of Gate<sub>i</sub>)

(2.3)

The equation for the computation of the input signature for gate types NAND, BUS, NOR, XNOR, and INVERTER is shown below in equation (2.4)

Input Signature of a  $Gate_i =$

$$\left( \text{Rotate} \left( \sum_{j} \text{Rotate} \left( \text{Input signature of fan\_out}_{j} \right) \right)^{C} \right)$$

of Gate<sub>i</sub> + Group Gate Mask of Gate<sub>i</sub> )

The addition operations in equations (2.3) and (2.4) are done with carry. The input signatures of gates G2, G4, and G5 are computed as shown in equation (2.3), and G3 is computed as shown in equation (2.4).

Algorithm 1 Signature computation for a circuit

## Input: Design

Output: Output signatures, Input signatures, Dictionary

- 1: Initialization :

- 2: For every gate, assign its output and input signatures to 0

- 3: Initialize all output signatures of primary inputs to prime-number1 randomly chosen between 1-15 million.

- 4: Initialize all output signatures of pseudo primary inputs to prime-number2 randomly chosen between 1-15 million.

- 5: Assign different prime numbers as masks for each type of gate

- 6: Output Signature

- 7: for each gate<sub>i</sub> from inputs to outputs do

- 8: Rotate the output signature at the inputs of gate<sub>i</sub> and add

- 9: Add mask of gate<sub>i</sub> to the result in step 8

- 10: Rotate the output signature obtained in step 9

- 11: end for

- 12: if Output\_Invert is true then

- 13: Complement the signature

- 14: end if

- 15: Input Signature

- 16: Initialize all input signatures of primary outputs and pseudo-primary outputs to their output signatures

- 17: for each gate<sub>i</sub> from outputs to inputs do

- 18: for each fanout of  $gate_i$  do

- 19: Rotate the input signature

- 20: EXOR result in Step 19 with the mask of the gate<sub>i</sub>

- 21: **end for**

- 22: Add signatures after Step 20

- 23: end for

- 24: if Output\_Invert is true then

- 25: Complement the signature

- 26: end if

- 27: Dictionary

- 28: for  $gate_i$  that is an observation point do

- 29: Store the inputs driving the output in a vector

- 30: For each output signature, insert a vector of inputs driving the output cone.

- 31: end for

Algorithm 1 outlines the signature analysis done for a given design. The signature computation is done on both circuit1 and circuit2 to compute all input and output signatures. This generates two dictionaries: dict<sub>1</sub> and dict<sub>2</sub> pertaining to circuit1 and circuit2, respectively. A dictionary contains output signatures as the key value. Each key is linked to a set of vectors that correspond to the inputs driving the output whose signature is equal to the key. All output cones with equivalent structures will have the same signature but possibly different vectors of inputs. Using the generated dictionaries, a set of input vectors from a cone in circuit1 is mapped to a set of input vectors of an identical cone in circuit2.

## 2.2.3 Mapping between circuit1 and circuit2

In this step, the goal is to establish a correspondence between circuit1 and circuit2 based on the computed signatures. This step reads the dictionaries  $dict_1$  and  $dict_2$ . For every key in dict<sub>1</sub> and dict<sub>2</sub>, a mapping is done when the input signatures of the input vector in dict<sub>1</sub> match the input signatures of the input vector in dict<sub>2</sub>.

#### Algorithm 2 Comparing signatures from circuit1 and circuit2

**Input:** Input signatures,  $dict_1$ ,  $dict_2$

**Output:** Mapping Information

1: Mark all vectors in  $dict_1$  and  $dict_2$  as unselected

2: for each key in dict<sub>1</sub> do

3: **if** key in dict<sub>2</sub> **then**

| 4:  | for every unselected vector <sub>1</sub> in dict <sub>1</sub> (key) do                          |

|-----|-------------------------------------------------------------------------------------------------|

| 5:  | for every unselected vector <sub>2</sub> in $dict_2(key)$ do                                    |

| 6:  | <b>if</b> input signatures of vector <sub>1</sub> and vector <sub>2</sub> are equal <b>then</b> |

| 7:  | Map the inputs in the vectors according to the input signatures                                 |

| 8:  | Mark vector <sub>1</sub> and vector <sub>2</sub> as selected                                    |

| 9:  | end if                                                                                          |

| 10: | end for                                                                                         |

| 11: | end for                                                                                         |

| 12: | end if                                                                                          |

|     |                                                                                                 |

## 13: end for

In Algorithm 2, input signatures, dict<sub>1</sub> and dict<sub>2</sub> are given as inputs. The keys of these dictionaries are the output signatures. The algorithm finds the output signatures common in dict<sub>1</sub> and dict<sub>2</sub> and iterates through the input vectors to find ones that have the same input signatures in dict<sub>1</sub> and dict<sub>2</sub>. Once a vector in dict<sub>1</sub> is matched with a vector in dict<sub>2</sub>, these vectors are not considered in further mapping. In this way, inputs are mapped from circuit1 to circuit2 in those parts of the circuit where input and output cones are structurally identical. In all the experiments done on industrial circuits, the mapping algorithm accurately identified cones that were identical in circuit1 and circuit2.

#### 2.2.4 Transforming the Pattern File

In circuit1, ATPG produces the set of patterns  $T_1$ . Considering circuit2, the values of inputs in circuit2 that have a match in circuit1 are copied from  $T_1$  to a new test set  $T_2$ . Random values are assigned in  $T_2$  to inputs that do not have a match in circuit1. Circuit2 is fault simulated using  $T_2$  as the set of test patterns. This transformation helps detect faults from the output cones of circuit2 which are structurally identical to the output cones of circuit1. A structurally identical cone will have the same input and output signatures in both circuits. All the faults from such input and output cones of circuit2 are detected by  $T_2$ .

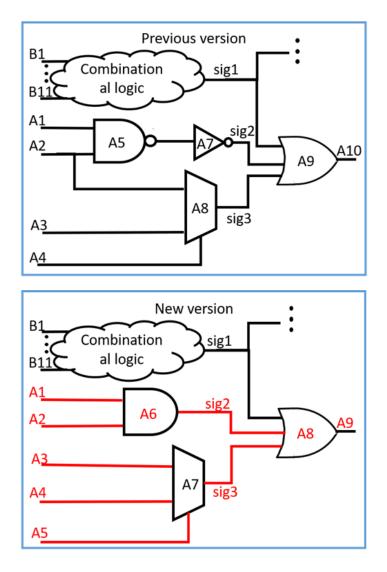

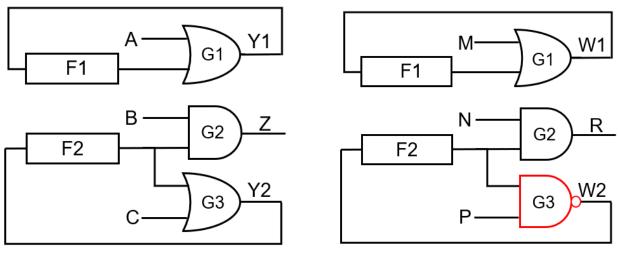

The transformed test set may not detect faults from a cone that does not have a match in circuit1. In addition, it may not detect faults in a cone of circuit2 that shares inputs with a cone that is structurally different in circuit1. This is illustrated next.

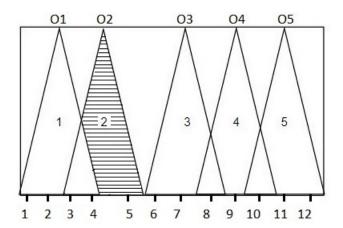

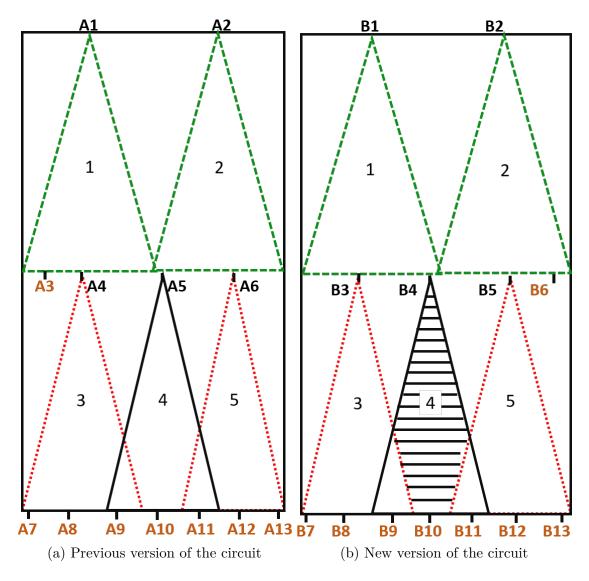

Figure 2.4. A Logic Circuit with Modification

Fig. 2.4 shows a logic circuit with five logic cones whose outputs are labeled as O1-O5 and inputs are labeled as 1-12. This circuit (circuit2) differs from another circuit (circuit1) at the shaded region in cone 2, such that cone 1, cone 3, cone 4, and cone 5 are structurally identical in both circuits. The output of cone 2 is O2 and its inputs are 3, 4, and 5. The structural difference causes the output and input signatures of cone 2 to be different in circuit1 and circuit2. In contrast, the output signatures of O1, O3, O4, and O5 would remain the same. Fig. 2.4 shows that some of the inputs of cone 2 are shared by cone 1 (inputs 3 and 4).

Hence, in cone 1, the signatures of inputs 3 and 4 would be different in circuit2 compared to circuit1. After mapping of test patterns and fault simulation, the simulated test patterns are guaranteed to detect all the faults from the structurally equivalent cones 3, 4, and 5 (all the input and output signatures of these cones remain the same), whereas only some of the faults are detected from cones 1 and 2. We accept this effect on cone 1 to ensure that the mapping between inputs is accurate. Without computing input signatures, it would not be possible to avoid matching inputs of cones that were structurally different in both circuits.

## 2.2.5 Incremental ATPG

The undetected faults of circuit2 are obtained after the fault simulation of  $T_2$ . Using the reduced fault set, test pattern generation is carried out to detect the remaining faults. The patterns generated are appended to  $T_2$  to obtain the complete test pattern set for circuit2.

#### 2.3 Experimental Setup and Results

Several experiments were performed to determine the accuracy of the proposed signature computation method, and to evaluate the test generation procedure. In Section A, three experiments are described to demonstrate the effectiveness of the signature computation method. Sections B and C evaluate the test generation procedure on 11 industrial circuits. These experiments consist of logical (Section B) and sequential (Section C) changes. Single stuck-at faults were used for the evaluation, and a compacted test pattern set was computed for circuit1 using a commercial ATPG tool.

## 2.3.1 Experimental Study on Signature Aliasing

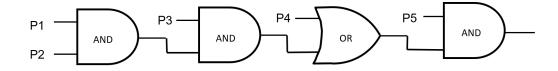

The goal of the experiments reported in this section is to verify experimentally whether aliasing, which refers to obtaining the same signature for structurally different cones, occurs in the circuits. This is important since the mapping algorithm relies on identical signatures to identify identical cones. If two different cones produce the same signatures, the mapping algorithm may result in an incorrect mapping of their inputs. The first experiment considered a 4-level AND-OR gate connection, as shown in Figure 2.5. The experiment considered the 16 possible gate combinations, as well as the addition of an input to each gate.

Figure 2.5. 4-level AND-OR gate connection

|    | Level 1  | Level 2   | Level 3   | Output     |

|----|----------|-----------|-----------|------------|

| 1  |          |           | 551893670 | 2223823206 |

| 2  |          | 133911286 | 001090070 | 2225886366 |

| 3  |          | 155911260 | 552056920 | 2232075846 |

| 4  | 29415690 |           | 553956830 | 2234139006 |

| 5  | 29410090 |           | 560146310 | 2256833766 |

| 6  |          | 135974446 | 300140310 | 2258896926 |

| 7  |          | 155974440 | 562200470 | 2265086406 |

| 8  |          |           | 562209470 | 2267149566 |

| 9  |          |           | 584904230 | 2355865446 |

| 10 |          | 142163926 | 564904250 | 2357928606 |

| 11 |          | 142103520 | 586967390 | 2364118086 |

| 12 | 31478850 |           | 000001000 | 2366181246 |

| 13 | 51478850 |           | 593156870 | 2388876006 |

| 14 |          | 144227086 | 090100010 | 2390939166 |

| 15 |          | 144227080 | 595220030 | 2397128646 |

| 16 |          |           | 393220030 | 2399191806 |

| 17 | 42582854 | 186579942 | 762568294 | 3066521702 |

| 18 | 29415690 | 147078450 | 604562326 | 2434497830 |

| 19 | 29415690 | 133911286 | 565060834 | 2276491862 |

| 20 | 29415690 | 133911286 | 551893670 | 2236990370 |

Table 2.2. Output signature for different configurations

The first 16 rows of the Table 2.2 show the output signature of all 16 possible combinations of AND and OR gates, in the order AND-AND-AND-AND-AND-AND-AND-OR, ..., OR-OR-OR-OR and the last four rows of Table 2.2 show the four cases of adding a single input to one of the gates of AND-AND-AND-AND configuration. All the configurations resulted in unique output signatures. The use of a different mask for each type of gate resulted in a distinct signature at each level. Furthermore, the rotate operation captures the level of each gate during the gate traversal. This experiment also shows that replacing a 2-input AND gate with a 3-input AND gate results in distinct output signatures. For the next two experiments, 100 logic cones were chosen from 11 industrial designs. The first experiment conducted exhaustive single gate changes where a single gate type is changed into every other gate type. In the second experiment, the number of gates to be changed (between 1-8) in a single modification was randomly chosen. Then, the chosen gates were randomly changed to another gate type. In each case, the difference between the output signatures of the baseline and modified cones was found. Its absolute value is referred to as the deviation.

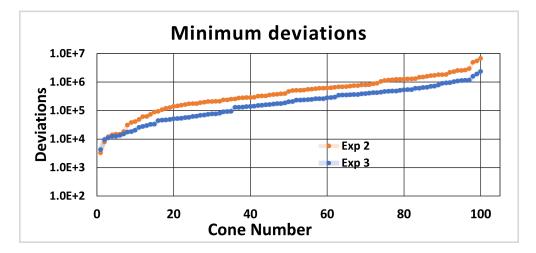

Figure 2.6. The minimum of deviation in logarithmic scale (base 10)

Figure 2.6 shows the minimum deviation for the two experiments. Both experiments together compared output signatures of 1.1 million modifications to the output signature of the baseline cone. The results showed that aliasing was not seen in these circuits, i.e., two different structures produced distinct signatures, and it is very unlikely for two different structures to have identical signatures.

## 2.3.2 Logic changes

A combinational logic change consists of changing the type of a gate, e.g., from AND to OR, and adding or removing inputs from a multi-input gate. Similar designs are obtained by introducing one change at a time, as well as a small number of changes simultaneously. Such modified versions of a circuit represent designs that are very similar to one another, or minor changes introduced due to ECO or after place and route. We experimented with versions obtained by introducing a large number of changes and found that the test generation procedure is also effective in these cases.

The experiment discussed next introduces one gate type change at a time and performs test generation to study the effectiveness of the incremental test generation procedure. Then, for each circuit, ten different versions are generated by introducing a single change at a random location in each of the versions. The results for logic changes are tabulated in Table 3.3. The first part of Table 3.3 represents changing the gate type, and the second part represents the addition or removal of inputs from multi-input gates.

|             |             |             | Table 2.5 | 3. Experi            | mental               | Table 2.3. Experimental Result for Logic Changes | Logic C               | hanges               |       |                      |                   |

|-------------|-------------|-------------|-----------|----------------------|----------------------|--------------------------------------------------|-----------------------|----------------------|-------|----------------------|-------------------|

|             |             | Tot Cone    | Diff      | RunT                 | RunTime (seconds)    | econds)                                          | Test                  | t Patterns           | erns  | Fault                | Fault Coverage(%) |

|             | Size        | in Base     | Cones     | $\mathbf{Base}$      | $\operatorname{Mod}$ | Gain                                             | $\operatorname{Base}$ | $\operatorname{Mod}$ | Incr  | $\mathbf{Base}$      | Mod               |

|             |             | Cir         | in Mod    | $\operatorname{Cir}$ | Cir                  | (Ratio)                                          | $\operatorname{Cir}$  | Cir                  | (%)   | $\operatorname{Cir}$ | Cir               |

| d1          | 8,611,749   | 429,708     | 1,262     | 7,020                | 506                  | 13.87                                            | 2,334                 | 2,842                | 21.76 | 97.06                | 90.76             |

| d2          | 3,435,493   | 276,462     | 367       | 622                  | 66                   | 6.28                                             | $1,\!459$             | 1,565                | 7.27  | 92.9                 | 92.91             |

| d3          | 4,833,052   | 334,108     | 4,218     | 1,568                | 123                  | 12.74                                            | 1,408                 | 1,509                | 7.17  | 92.08                | 92.08             |

| d4          | 10,213,281  | 601, 469    | 20,548    | 9,300                | 994                  | 9.35                                             | 7,424                 | 8,022                | 8.05  | 90.85                | 90.87             |

| d5          | 15,102,044  | 1,215,337   | 5,461     | 13,740               | 1,177                | 11.67                                            | 4,544                 | 5,067                | 11.5  | 94.46                | 94.47             |

| d6          | 3,048,599   | 174,505     | 1,151     | 1,260                | 128                  | 9.84                                             | 2,944                 | 3,198                | 8.62  | 91.92                | 91.92             |

| d7          | 3,519,135   | $219,\!280$ | 3,043     | 5,103                | 405                  | 12.6                                             | 5,155                 | 5,780                | 12.12 | 97.02                | 97.03             |

| d8          | 6, 389, 260 | 302,540     | 2,741     | 1,777                | 244                  | 7.28                                             | 2,520                 | 2,649                | 5.11  | 90.83                | 90.86             |

| $^{\rm d9}$ | 12,167,308  | 440,540     | 12,063    | 6,446                | 843                  | 7.64                                             | 7,168                 | 7,297                | 1.79  | 91.65                | 91.70             |

| d10         | 1,203,568   | 45, 345     | 1,361     | 484                  | 26                   | 18.61                                            | 1,811                 | 2,046                | 12.97 | 88.58                | 88.58             |

| d11         | 1,699,509   | 89,908      | 5,328     | 10,168               | 459                  | 22.15                                            | 2,163                 | 2,891                | 33.65 | 97.62                | 97.71             |

| d10         | 1,203,568   | 45, 345     | 861       | 484                  | 23                   | 21.04                                            | 1,811                 | 1,895                | 4.63  | 88.58                | 88.58             |

| d11         | 1,699,509   | 89,908      | 4,828     | 10,168               | 521                  | 19.51                                            | 2,163                 | 2,952                | 36.47 | 97.62                | 97.65             |

| Changes     |  |

|-------------|--|

| Logic       |  |

| for ]       |  |

| Result      |  |

| xperimental |  |

| Experin     |  |

| 2.3.        |  |

| Θ           |  |

In Table 3.3, each row corresponds to one of the 11 industrial circuits. The row shows the average of each one of several parameters for all the ten versions of the circuit. These results are shown under the sub-column Mod Cir. Sub-column Base Cir shows the results for the baseline circuit in the respective categories. The first column, "size" gives the total number of gates in each circuit. Column "Tot Cone in Base Cir" shows the total number of output cones in the baseline circuit. Column "Diff Cones in Mod" shows the number of output cones that changed in the modified circuit compared to the baseline circuit. Column Run Time shows the overall time taken in seconds for test pattern generation. For a modified circuit, the total runtime includes the time taken for signature computation, mapping, fault simulation, and incremental test generation. Sub-column "Gain" is the ratio of the runtime of the baseline circuit to the average of the runtime of the modified circuits. Column Test Patterns shows the total number of test patterns after test generation. The sub-column "Incr (%)" gives the percentage increase in the number of test patterns. The last column, Fault coverage, shows the fault coverage achieved in the baseline circuit and the average fault coverage seen in the different versions of the modified circuits.

From column "Diff Cones in Mod" in Table 3.3, it can be seen that introducing a single change can affect between 0.13% to 5.9% of the total number of output cones for the 11 industrial circuits. Within the 10 different versions of a circuit, an average of 11% variation is seen between the minimum and the maximum number of cones that are affected. The number of output cones different in the modified circuit compared to the baseline circuit directly affects the time taken for the incremental test generation. The lower the number of different cones, the higher the number of matched inputs, resulting in a larger number of faults being detected in the modified circuit after mapping of test patterns. By transforming the test set from  $T_1$  to  $T_2$  and then fault simulating, faults from cones that are structurally identical in the modified and baseline circuits are detected. The transformation of test patterns results in an improvement in the total runtime of the modified circuit. The improvement in runtime is observed because only a small subset of the total faults require test generation. This translates to an average of 13-fold gain in runtime to achieve the same fault coverage in the modified circuit compared to the baseline circuit for all the different industrial circuits. The gain in runtime depends on the circuit and varies from 6 to 22-fold. This shows that the test generation time can be considerably reduced by utilizing the structural similarity between the circuits for various changes.

The algorithm proposed in this chapter focuses on determining the testability of a circuit given a test set for another structurally identical circuit and does not optimize the number of test patterns. As a result, there is an average of 13% increase in the number of test patterns in circuit2 compared to circuit1. This can be mitigated by rerunning test pattern generation after the design converges or when the number of patterns increases significantly.

## Multiple changes within a circuit

Multiple changes in the range of 10 to 10,000 were introduced in a circuit at random locations to see how the test generation procedure performs in the presence of multiple changes. The procedure was able to determine the changed cones, and faults in the circuit were detected in less than 25% of the total runtime of the baseline circuit. The proposed method took more time to detect all the faults as the number of changes in the circuit increased. It should be noted that these numbers of changes are not realistic, and they were considered only for the purpose of verifying the performance of the test generation procedure.

#### 2.3.3 Sequential changes

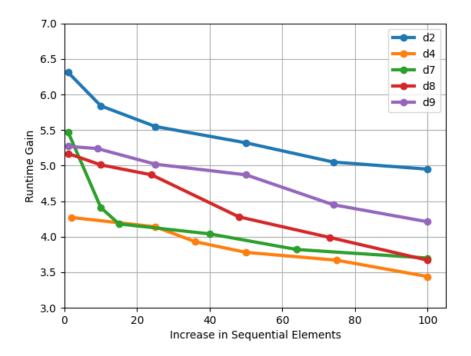

The second experiment considers sequential changes in a circuit. Basic steps of forward and backward retiming are done where registers are moved forward or backward in the combinational blocks. This changes the total number of scan cells in the modified circuit compared to the baseline circuit. The results for sequential changes are tabulated in Table 2.4.

Column "# of Mod SC" in Table 2.4 gives the average of the number of scan cells added or removed in 10 modified versions of each circuit. Column "Test Pat Inc (%)" gives the percentage increase in the number of test patterns. The change in the number of scan cells in the modified circuit varies from 3-11 compared to the baseline circuit. Table 2.4 shows an average of 11-fold gain in runtime to achieve the same fault coverage in the modified circuit

|     | Diff      | # of          | Run       | ſime (s | econds) | Test    |

|-----|-----------|---------------|-----------|---------|---------|---------|

|     | Cones     | Mod           | Base      | Mod     | Gain    | Pat Inc |

|     | in Mod    | $\mathbf{SC}$ | Cir       | Cir     | (Ratio) | (%)     |

| d1  | 3,418     | 7             | 7,020     | 685     | 10.25   | 19.66   |

| d2  | 721       | 6             | 622       | 79      | 7.87    | 2.6     |

| d3  | 1,282     | 6             | 1,568     | 141     | 11.12   | 19.38   |

| d4  | 2,335     | 7             | 9,300     | 821     | 11.33   | 2.35    |

| d5  | $2,\!104$ | 6             | 13,740    | 975     | 14.09   | 7.54    |

| d6  | 920       | 5             | $1,\!260$ | 130     | 9.7     | 3.34    |

| d7  | 2,593     | 6             | $5,\!103$ | 328     | 15.6    | 13.13   |

| d8  | 2,785     | 7             | 484       | 51      | 9.49    | 32.21   |

| d9  | $1,\!355$ | 5             | 10,168    | 391     | 26.0    | 20.29   |

| d10 | 981       | 6             | 1,777     | 278     | 6.39    | 5.9     |

| d11 | 21,043    | 6             | 6,446     | 899     | 7.17    | 3.29    |

Table 2.4. Experimental Result for Sequential Changes